Изобретение относится к радиоэлектронике, технике связи, измерительной технике, а также к другим областям науки и техники, где возникает необходимость в прецизионной задержке импульсных сигналов, радиосигналов и аналоговых сигналов,

Целью изобретения является уменьшение погрешности и расширение диапазона задания задержки,

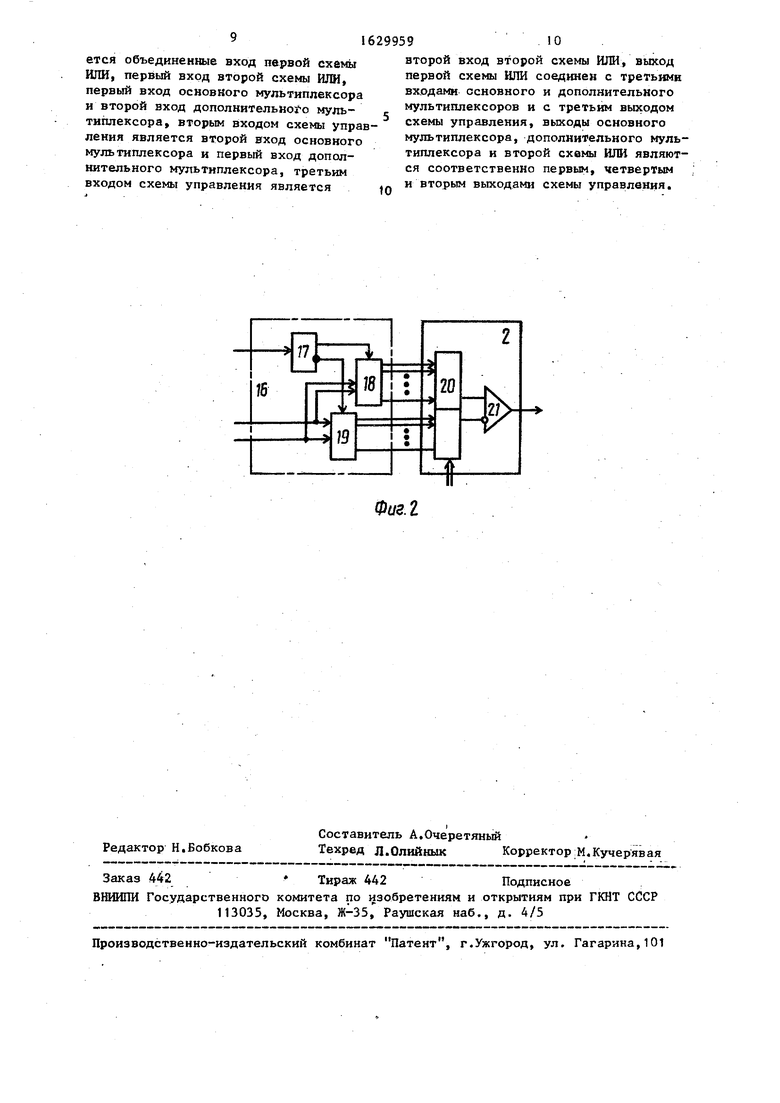

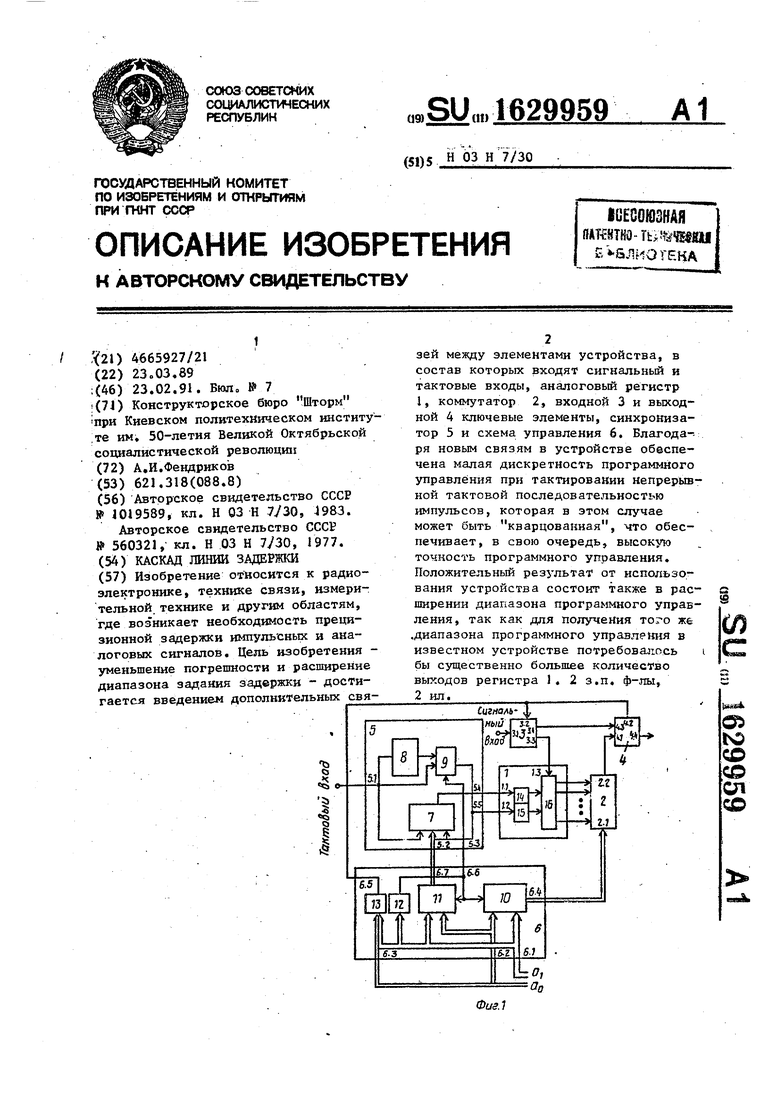

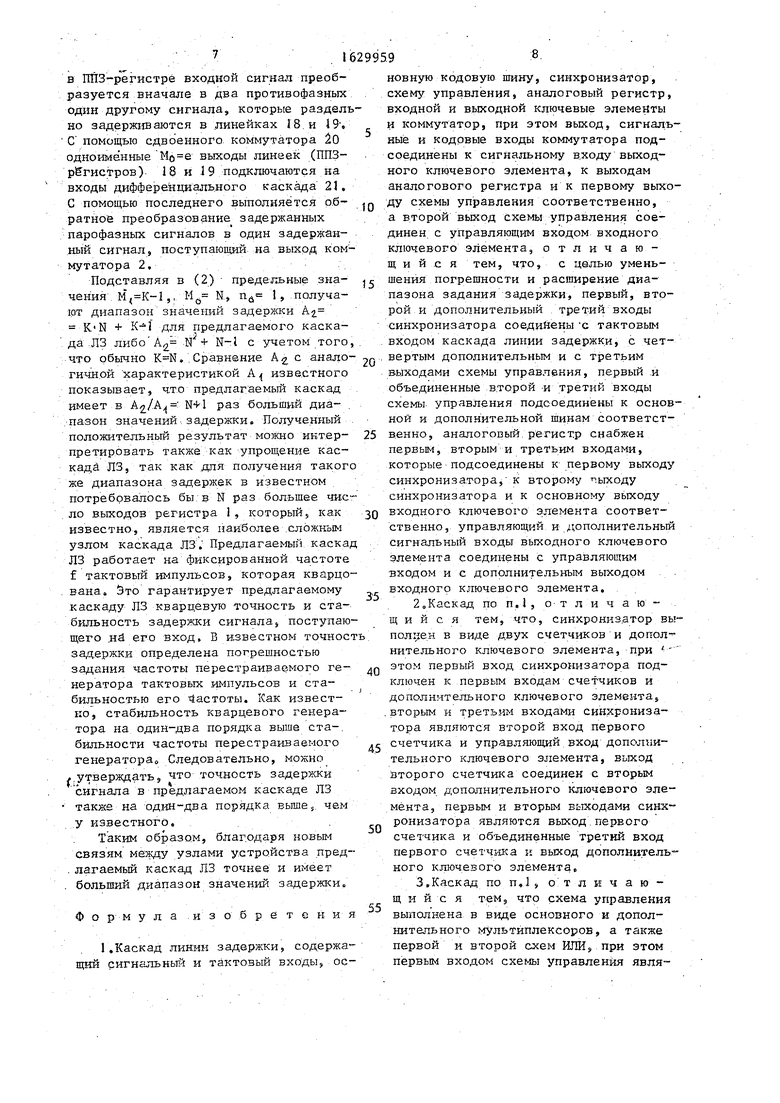

На фиг приведена структурно- функциональная схема каскада; на фиг г 2 - двухканальный вариант выполнения аналогового регистра и коммутатора,,

Каскад линии задержки (ЛЗ) содержит аналоговый регистр 1э коммутатор 2, входной ключевой элемент (КлЭ) 3, выходной КлЭ 4, синхронизатор 5 и схему 6 управления (СУ), Синхронизатор 5 имеет первый 5,1, второй 5.2 и третий 5,3 входы и выходы 5.4 и 5 о 5, Су 6 имеет парвый 6.4, второй 6.2 и третий 6,3 входы и первый 6.4, второй 6.5, третий б„6 и четвертью 6,7 выходы. Регистр имеет первый 1.1, второй 1,2 и третий 1,3 входы и выходы. Коммутатор 2 имеет сигнальный и кодовый входы 2.1 и выход 2.2 о Входной КлЭ 3 сигнальный 301 н управляющий 3.2 :ходы и основной 3.3 и дополнительный 3.4 выходы. Выходной клЭ 4 имеет сигнальный основной 4.J, управляющий 4„2 и сигнальный дополнительный 4.3 входы и выход 4 4.

Узлы соединены следующим образом Вход 5 „ 1 соединен с тактовым входом каскада задержки, вход 5,2 - с выходом 6.7, выход 6.6 с входом 5,35 выход 6.5 - с управляющими входами КлЭ 3 и 4S выходы 5.4 и 5,5 - с входами 1,1 и 1о2 соответственно, вход 3.1 -с сигнальным входом каскада ЛЗ вход 4.3 - с выходом 3,4, вход 1 .3 - с выходом 3,3, вход 4.1 - выходом 2,2, вход 2,1 - с выходом 6С45 вход 6,1 с основной кодовой шиной (шиной старших разрядов) каскада ЛЗ, а объединенные входы 6,2 и 6.3 - с дополнительной кодовой шиной (шиной младших разрядов).

Синхронизатор 5 содержит первый .7 и второй 8 счетчики, дополнительный КлЭ 9f первые входы счетчиков и КлЭ 9 соединены с входом 5.1, выход счетчика 8 - с вторым входом КлЭ 9, выход КлЭ 9 - с объединенными

5

0

5

0

5

0

5

0

5

третьим входом счетчика 7 и выходами 5.5, а второй вход счетчика 7 - с входом 5.2.

СУ содержит основной 40 и дополнительный 1J мультиплексоры, первую 12 и вторую 13 схемы ИЛИ. Вторая схема ИЛИ имеет две группы входов. Первая группа входов объединена с группой входов первой схемы ИЛИ, с вторым входом (второй группой входов) мультиплексора 1, с первым входом (первой группой входов) мультиплексора 10 и подсоединена к входу 6., Вторая группа входов (второй вход) схемы ИЛИ 13 является входом 6.3 СУ. Выходы мультиплексоров соединены с выходами 6.4 и б«7 соответственно. Выход схемы ИЛИ 13 соединен с выходом 6.5, а выход схемы 12 - с общей точкой соединения выхода б.Ь и управляющих входов обоих1 мультиплексоров. Регистр 1 содеришт усилители-формирователи 14 и 5 и ППЗ-регнстр 16 (регистр на поибо- рах с переносом заряда). Узлы 4 и 15 включены между входами 1.1 и 1,2 и тактовыми входами ППЗ-регистра 16, сигнальный вход последнего является входом 1.3, а выходы являются выходами регистра 1« При двухкацальном исполнении ППЗ-регистр 16 (фиг„2) содержит парофазный каскад 17 (ПК) и две линейки 18 и 19 приборов с переносом заряда. ПК 17 включен на сигнальных входах линеек 18 и 19. Тактовые входы линеек объединены. При двух- ханальном исполнении коммутатор 2 содержит последовательно-соединенные двойной коммутатор 20 и дифференциальный каскад 23.

Каскад ЛЗ работает следующим образом

Сигнал U(t), подлежащий-задержке, поступает с сигнального входа каскада ЛЗ на входной КлЭ 3. Тактовый сигнал в виде импульсов, следующих с частотой f с тактового входа каскада ЛЗ поступают па вход 5.1 синхронизатора, в котором она п помощью счетчи ка 8 делится в К раз до частоты f f/K. На кодовый вход каскада ЛЗ (на кодовые иины каскада ЛЗ) поступает число Л, которым задана требуемая задержка ft сигнала lir tM, Число А представлено в виде А -- а0 где a и ао - числа, отражающие собой значения соответственно старших и младших разрядов двоичного кода числа А, а К единицы старших,

разрядов. Число а (число а0) поступает с основной (дополнительной) шины кодового входа на входы 6.1 (6.2, 6.3) СУ 6. В СУ 6 с помощью схем ИЛИ 12 и 13 числа А и а, анализируются на предмет отличия их от нуляС При этом на входах схем ИЛИ формируются логические сигналы, которые управляют работой мультиплексоров и КлЭ 3 и 4. Если А 0, тогда КлЭ 3 и 4 устанавливаются в такое положение, при котором сигнал с входа каскада ЛЗ поступает (через КлЭ) на его выход, минуя аналоговый регистр 1 и коммутатор 2, что соответствует нулевой задержке, т.е. С П. Если А 0, тогда с помощью КлЭ 3 и 4 вход регистра 1 подключается на вхо каскада ЛЗ, а выход ком гутатора 2 - на выход каскада ЛЗ. В этом случае задержка сигнала определяется числом М0, поступающим на кодовый вход коммутатора с выхода 6.4, частотой f импупьсов записи (поступающих на вход 2.2 регистра) и временным сдвигом t, , импульсов считывания (поступающих на вход 2Л) по отношению к импульсам записи. Частота f и сдвиг t, задаются с помощью синхронизатора 5 под действием числа М и логического сигнала К, поступающих на входы соответственно 5.2 и 5.3 синхронизатора с выходов СУ 6. Если число а,, О (число а, 0), то на выходе схемы ИЛИ 12 формируется сигнал Б О (). Под его действием в СУ 6 мультиплексор 10 передает с входов на выход 6.4 число Mfl а 0 (М Q а ), мультиплексор 11 передает с входов на выход 6.7 число М а(), а КлЭ 9 передает на ъыход 5.4 синхронизатора импульсы записи, следующие с частотой f f(f -f t). Временной сдвиг t формируется с помощью счетчика 7, работающего в режиме вычитания. Под действием каждого импульса с выхода КлЭ 9 в счетчик 7 записывается число М., которое затем начинает уменьшаться под действием импульсов частоты f ( , поступающих на, его первый вход с входа 5.1. Как только число М уменьшается до нуля, на выходе счетчика 7 формируется импульс, запаздывающий относительно записи на время t Мд/f.

Таким образом, с помощью синхронизатора 5 и СУ 6 формируются последовательность импульсов записи и последовательнЪсть импульсов счнтыва- , ния, которые, поступая на входы 3„1 и 1.2, управляют задержкой сигнала в регистре 1. В последнем указанные импульсы после формирования и усиления в усилителях 14 и 15 поступают на тактовые входы ППЗ-регистра-16 (фиг.2). Под действием импульсов за- писи в ЩТЗ-регистре 16 сигнал U(t) дискретизируется, его мгновенные значения преобразуются в зарядовые пакеты, которые продвигаются по приборам с переносом заряда (ячейкам 5 динамической памяти) по направлению к выходам ППЗ-регистра 16. Достигая выходов ППЗ-регистра заряды преобразуются в пропорциональные уровни (ступеньки) напряжения под действием 0 последовательности импульсов считывания, С помощью коммутатора 2 под действием числа Мо, поступающего на его кодовый вход с выхода 6.4 СУ, на его выход (и далее на выход каскада ЛЗ) 5 передается сигнал с выхода ППЗ-регистра 1бо

С учетом временного сдвига tj- - М,|/Ј, импульсов считывания относительно импульсов записи сигнал, сни- 0 маемый с Мо-го выхода ППЗ-регистра, оказывается задержанным на время

Ј n.0K0/fy + Mj/f, (1) либо с учетом того, что f f/K

Ј ( + M{)/f, (2) где п .- число ячеек памяти мезаду любыми соседними выходами ППЗ-регистра; V, 0,1,2,...,К-1; М0 0,lj2,.0,N (N -число выхо- Q дов ППЗ-регистра).

Пример. Пусть ППЗ-регнстр имеет выходов, число nfl- ячеек памяти между соседними выходами, коэффициент деления счетчика 8S за- 5 держка задана числом в двоичном коде (т.е. код 001100), которому соответствуют числа (код 001) и (код 100) . Числа а,, и ао поступают на шины основную (старших 0 разрядов) и дополнительную (младших разрядов) соответственно. Поскольку а 0, то , 1, М., f f/K f/8. Подставляя эти значения в (1),получают значение задерж- 5 ки Ј 12/f, которое равно требуемо му.

Если ППЗ-сегистр 46 и коммутатор 2 выполнить согласно фиг.2, то работа каскада ЛЗ не изменяется. Однако

10

15

25

71629959

в ППЗ-регистре входной сигнал преобразуется вначале в два противофазных один другому сигнала, которые раздельно задерживаются в линейках 18 и 19, С помощью сдвоенного коммутатора 20 одноимённые выходы линеек (ППЗ- рёгистров) 18 и 19 подключаются на входы дифференциального каскада 21, С помощью последнего выполняется обратное преобразование задержанных парофазных сигналов в один задержанный сигнал, поступающий на выход коммутатора 2,

Подставляя в (2) предельные значения ,, MO N, пй 1, получают диапазон значений задержки А K N + К-4 для предлагаемого каскада ЛЗ либо АЈ N + N-1 с учетом того, что обычно . Сравнение АЈ с анало- JQ гичной характеристикой А известного показывает, что предлагаемый каскад имеет в АЈ/А N-H раз больший диапазон значений задержки. Полученный положительный результат можно интерпретировать также как упрощение каскада ЛЗ, так как для получения такого же диапазона задержек в известном потребовалось бы в N раз большее число выходов регистра 1, который; как известно, является наиболее сложным узлом каскада ЛЗ. Предлагаемый каскад ЛЗ работает на фиксированной частоте f тактовый импульсов, которая кварцо- вана 5то гарантирует предлагаемому каскаду ЛЗ кварцевую точность и стабильность задержки cnrHanas поступающего ни его вход, В известном точность задержки определена погрешностью задания частоты перестраиваемого генератора тактовых импульсов и стабильностью его частоты. Как известно, стабильность кварцевого генератора на один-два порядка выше стабильности частоты перестраиваемого генератора Следовательно, можно утверждать, что точность задержки сигнала в предлагаемом каскаде ЛЗ также на один-два порядка выше., чем у известного.

Таким образом, благодаря новым связям между узлами устройства пред1 лагаемьш каскад ЛЗ точнее и имеет больший диапазон значений задержки.

30

35

40

45

50

но сх вх и ны с но ан ду а ди кл щ ш п р си вх ве в о сх но ве пе к с си вх с с эл в в

щ п н э кл д в т с т в в м

Формула изобретения

1.Каскад линии задержки, содержащий сигнальным и тактовый входы, ос

5

0

5

0

5

0

5

новную кодовую шину, синхронизатор, схему управления, аналоговый регистр, входной и выходной ключевые элементы и коммутатор, при этом выход, сигнальные и кодовые входы коммутатора подсоединены к сигнальному входу выходного ключевого элемента, к выходам аналогового регистра и к первому выходу схемы управления соответственно, а второй выход схемы управления соединен с управляющим входом входного ключевого элемента, отличающийся тем, что, с целью уменьшения погрешности и расширение диапазона задания задержки, первый, второй и дополнительный третий входы синхронизатора соединены с тактовым входом каскада линии задержки, с четвертым дополнительным и с третьим выходами схемы управления, первый и объединенные второй и третий входы схемы управления подсоединены к основной и дополнительной шинам соответственно, аналоговый регистр снабжен первым, вторым и третьим входами, которые подсоединены к первому выходу синхронизатора, к второму ыходу синхронизатора и к основному выходу входного ключевого элемента соответственно, управляющий и дополнительный сигнальный входы выходного ключевого элемента соединены с управляющим входом и с дополнительным выходом входного ключевого элемента,

2„Каскад по п.1, отличающийся тем, что, синхронизатор выполнен в виде двух счетчиков и дополнительного ключевого элемента, при L этом первый вход синхронизатора подключен к первым входам счетчиков и дополнительного ключевого элемента, вторым и третьим входами синхронизатора являются второй вход первого счетчика и управляющий вход дополнительного ключевого элемента, выход второго счетчика соединен с вторым входом дополнительного ключевого элемента, первым и вторым выходами синхронизатора являются выход первого счетчика и объединенные третий вход первого счетчика и выход дополнительного ключевого элемента

3.Каскад по п,1 , отличающийся темэ что схема управления выполнена в виде основного и дополнительного мультиплексоров, а также первой и второй схем ИЛИ, при этом первым входом схемы управления является объединенные вход первой схемы ИЛИ, первый вход второй схемы ИЛИ, первый вход основного мультиплексора и второй вход дополнительного мультиплексора, вторым входом схемы управления является второй вход основного мультиплексора и первый вход дополнительного мультиплексора, третьим входом схемы управления является ю

второй вход второй схемы ИЛИ, выход первой схемы ИЛИ соединен с третьими входами основного и дополнительного мультиплексоров и с третьим выходом схемы управления, выходы основного мультиплексора, дополнительного мультиплексора и второй схемы ИЛИ являются соответственно первым, четвертым и вторым выходами схемы управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ОПОЗНАВАНИЯ "СВОЙ-ЧУЖОЙ" | 2001 |

|

RU2191403C1 |

| СИСТЕМА ОБНАРУЖЕНИЯ И СОПРОВОЖДЕНИЯ СУДОВ В АКВАТОРИИ ПОГРАНИЧНОЙ ЗОНЫ | 2019 |

|

RU2714614C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1998 |

|

RU2124221C1 |

| Программируемая линия задержки | 1988 |

|

SU1638790A1 |

| Цифровой компенсационный фазометр | 1988 |

|

SU1597766A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Устройство для исправления ошибок в волоконно-оптических системах передачи информации | 1990 |

|

SU1809534A1 |

| Генератор кодовых последовательностей импульсов | 1987 |

|

SU1531080A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

Изобретение откосится к радиоэлектронике, технике связи, измерительной технике и другим областям, где возникает необходимость прецизионной задержки импульсных и аналоговых сигналов. Цель изобретения - уменьшение погрешности и расширение диапазона задания задержки - достигается введением дополнительных связей между элементами устройства, в состав которых входят сигнальный и тактовые входы, аналоговый регистр 1, коммутатор 2, входной 3 и выходной 4 ключевые элементы, синхронизатор 5 и схема управления 6. Благодаря новым связям в устройстве обеспечена малая дискретность программного управления при тактировании непрерывной тактовой последовательностью импульсов, которая в этом случае может быть кварцоваиная, что обеспечивает, в свою очередь, высокую точность программного управления. Положительный результат от использования устройства состоит также в расширении диапазона программного управления, так как для получения того же .диапазона программного управления в известном устройстве потребовалась i бы существенно большее количество выходов регистра 1. 2 з.п. ф-лы, 2 ил, оэ to со со ел со

Фиг. 2

| Авторское свидетельство СССР 4019589, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для задержки аналоговых сигналов | 1975 |

|

SU560321A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-02-23—Публикация

1989-03-23—Подача