Изобретение относится к вычислительной технике и может быть использовано для исправления ошибок в волоконно-оптических системах передачи информации.

Целью изобретения является повышение быстродействия устройства.

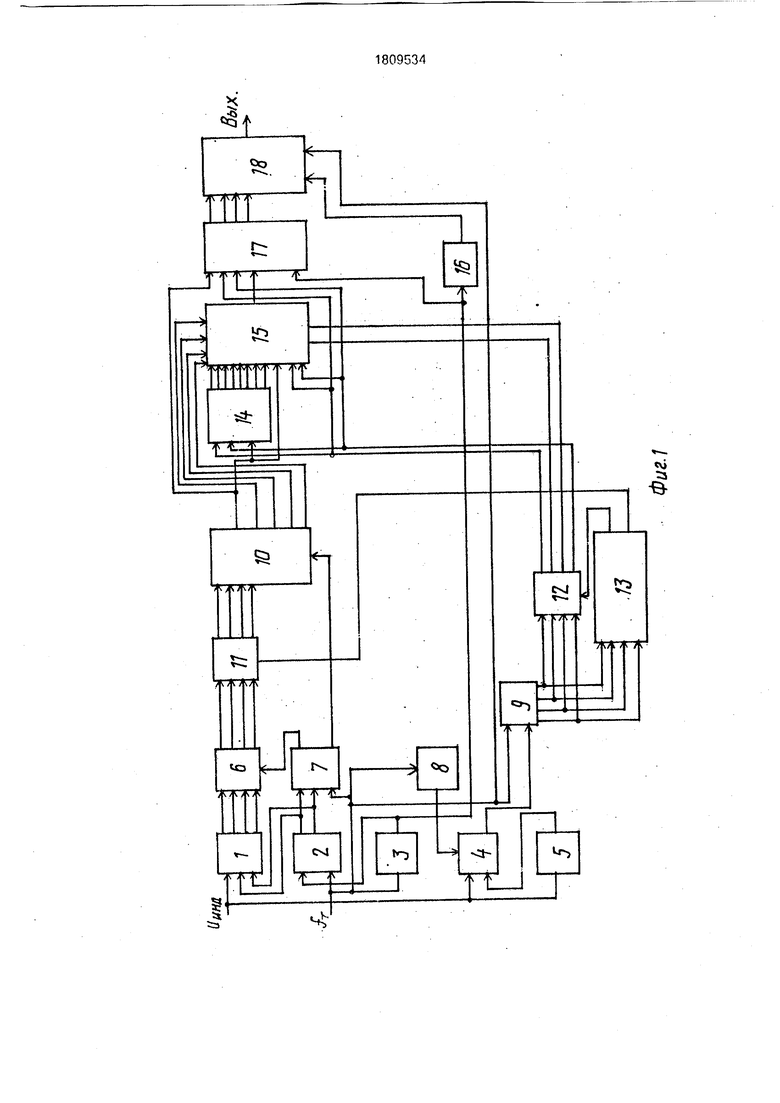

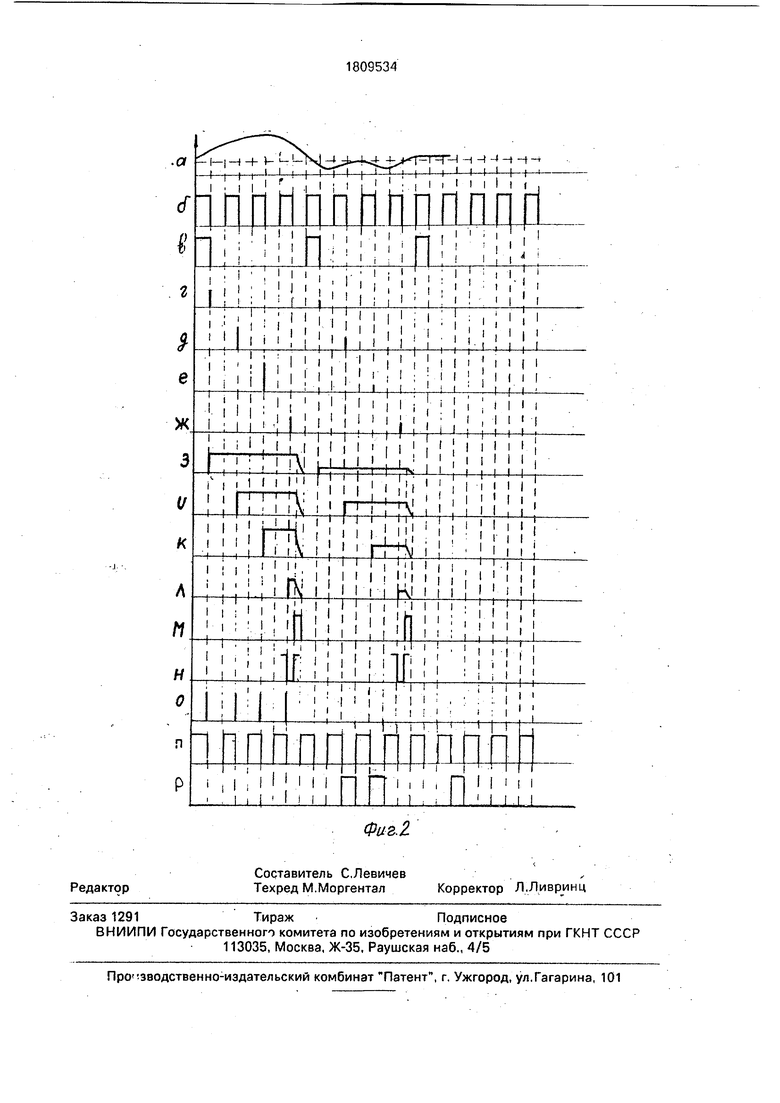

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 - эпюры напряжений в различных точках устройства.

Устройство содержит мультиплексор 1, счетчик 2, синхронизатор 3, компаратор 4, пороговый элемент 5, блок 6 пиковых детекторов, блок 7 формирования стробирующих импульсов, два элемента задержки 8 и 16, регистр 9 сдвига, блок 10 сравнения, два ключа 11 и 12, блок 13 управления режимами работы, дешифратор 14, коммутатор 15, блок 17 памяти, преобразователь 18 параллельного кода в последовательный.

Устройство работает следующим образом.

Пусть для передач информации в волоконно-оптической цифровой системе передачи используется код ЭВ-4В, который трем двоичным символам ставит в соответствие блок из четырех двоичных символов, причем, минимальное кодовое расстояние 1. На информационный вход устройства поступают сигналы, искаженные помехой. Входной сигнал (фиг.2а) поступает на вход мультиплексора 1, который управляется счетчиком 2. Счетчик 2 срабатывает по импульсам тактовой частоты (фиг,2б) и синхронизируется импульсно-блочной частоты (фиг.2в), вырабатываемой синхронизатором 3, На первом выходе мультиплексора 1 формируется сигнал (фиг.2г), соответствующий отсчету первого разряда Xi, принятого кодового слова X, на втором выходе мультиплексора 1 формируется сигнал (фиг.2д) соответствующий отсчету второго разряда Ха принятого сигнала X и т.д. (фиг.2е и фиг.2ж). Таким образом, на вход устройства поступает вектор сигналов - Xi, Ха, Хз, X/j.

Синхронизатор 3 формирует сигналы блочной синхронизации, соответствующие началу кодового слова. С выхода мультиСО

С

00

о ю ел со

N

плексора 1 принятый сигнал в параллель-, ном коде поступает на соответствующие входы блока, пиковых детекторов, управляемых сигналом с выхода блока 7 формирования стробирующих импульсов (фиг,2м). Блок 6 пиковых детекторов выбирает макси- мальное значение сигнала на входе (фиг.2г,д,е,ж) и запоминает его до конца кодового слова (фиг.2з,и,к,л). Блок 7 формирования етробирующих импульсов 7 генерирует импульсы с длительностью, равной 0,25 периода тактовой частоты и только в -те моменты, когда на его первых двух входах присутствуют сигналы логической 1, а на третьем входе отрицательный пе- репад напряжения, что соответствует середине четвертого тактового интервала, т.е. четвертого разряда принятого кодового слова, при этом сигнал с неинвертирующего выхода проходит через элемент задержки на 0,25 такта, находящийся внутри блока 7 формирования стробирующих импульсов (фиг,2м), а сигнал с инвертирующего выхода (фиг.2н)поступает на выход без задержки. Таким образом, сброс блоков пиковых де- текторов происходит после того, как на нем запомнится максимальное значение принятого кодового слова. Входной сигнал X (фиг.2а) поступает также на вход компаратора 4, на второй вход которого поступает сигнал с выхода порогового элемента 5, а на управляющий вход компаратора поступает сигнал тактовой частоты компаратор открывается уровнем логического О.

. В моменты времени, задаваемые отри- цательным перепадом тактовой частоты и. соответствующие середине тактового интервала, компаратор 4 осуществляет сравнение принятого сигнала со значением порога, и, если сигнал превышает порог, то на выходе компаратора 4 формируется сигнал логической 1. В противном случае сигнал логического О (фиг.2о). Фактически, в компараторе 4 формируются оценки жесткого решения. Величина порога (фиг.2а) вы- бирается равной половине амплитуды принятого сигнала. С выхода компаратора 4 вектор оценки жесткого решения поступает на второй вход регистра сдвига 9, на первый вход которого поступает сигнал тактовой ча- стоты с задержкой. На выходе регистра 9 формируются четыре оценки жесткого решения в параллельном коде, поступающие на вход блока управления режимами работы.

Блок управления режимами работы сравнивает результаты жесткого решения со всеми возможными разрешенными словами. Если оценки жесткого решения совпадают с каким-либо разрешенным кодовым

словом, то замыкается второй ключ 12, и размыкается первый ключ 11, т.е. приниматся только жесткое решение. Если же оценки жесткого решения не, совпадают ни с дним из разрешенных кодовых слов, то амыкается первый ключ 11 и размыкается второй ключ 12 и информация поступает на лок сравнения и т.д., по схеме, т.е. приниается мягкое решение. Таким образом, ягкое решение производится не для всех кодовых слов, а только для запрещенных, то дает возможность повысить скорость бработки информации в декодере.

Блок сравнения 10 осуществляет следующие сравнения: Xi Х2; Х2 Хз; Хз Хз; Х2 .

В случае, выполнения неравенства на соответствующих выходах блока сравнений 10 формируется сигнал логической 1, а в случае невыполнения - сигнал логический О.

Сигнал с первого выхода блока сравнений 10 поступает на третий адресный вход ешифратора 14, на первые два адресных входа которого поступают сигналы с четвертого и первого выхода регистра 9. Все эти три сигнала являются адресом для дешифратора 14 и в соответствии с пришедшей воичной комбинацией активизируется соответствующий выход дешифратора 14. Выходы дешифратора 14 подключены к информационным входам коммутатора 15. Вышеприведенные адресные сигналы дешифратора 14 поступают так же и на седьмой, восьмой и девятый управляющий входы коммутатора 15 и на первые три информационные входы блока памяти 14. Коммутатор 15 пропускает на выход только один соответствующий результат сравнения в каждом конкретном случае, задаваемом сигналами управления.

Выход коммутатора 15 подключен к пятому информационному входу блока памяти 17, в который заранее записаны необходимые кодовые слова по соответствующему адресу. Каждый поступающей комбинации блок памяти 17 ставит в соответствие одно кодовое слово, т.е. происходит восстановление (регенерация) принятого кодового слова. Полученный на выходе блока памяти 17 четырехразрядный параллельный код (фиг.2р) поступает на преобразователь параллельного кода в последовательный 18, на первый управляющий вход которого поступает сигнал от синхронизатора 3 через второй элемент задержки 16, и на второй управляющий вход поступает тактовая час: тота, с помощью которой осуществляется сдвиг информации. Таким образом, полное восстановление N-ro кодового слова ироисходит в (N+1) такте и в последовательном коде передается в линию связи.

Таким образом, в предлагаемом устройстве, за счет того что мягкое решение производится не для всех кодовых слов, а только для запрещенных, происходит значительное сокращение времени обработки информации в декодере, и, следовательно, повышение скорости обработки информации.

Формула изобретения Устройство для исправления ошибок в волоконно-оптических системах передачи информации, содержащее мультиплексор, первый вход которого соединен с входом порогового элемента, первым входом компаратора и является информационным входом устройства, выходы,мультиплексора соединены с соответствующим информационными входами блока пиковых детекторов, счетчик импульсов, первый вход которого соединен с входом синхронизатора, первым входом формирователя стробирующих импульсов, первым управляющим входом преобразователя, параллельного кода в последовательный и является входом синхронизации устройства, первый и второй выходы счетчика импульсов соединены соответственно с вторыми и третьими входами мультиплексора и формирователя стробирующих импульсов, первый и второй выходы формирователя стробирующих импульсов соединены соответственно с управ- ляющими входами блока пиковых детекторов и блока сравнения, выход синхронизатора соединен с вторым входом счетчика импульсов, управляющим входом блока памяти и через первый элемент задержки с вторым управляющим входом преобразователя параллельного когда в последовательный, выход порогового элемента соединен с вторым входом компаратора, выход которого соединен с первым

входом регистра сдвига, первый, второй, третий и четвертый выходы блока сравнения соединены с соответствующими управляющими входами коммутатора, пятый выход 5 блока сравнения соединен с первым информационным входом блока памяти, пятым управляющим входом коммутатора и первым входом дешифратора, выходы которого подключены к соответствующим информацион0 ным входам коммутатора, выход которого соединен с вторым информационным входом блока памяти, выходы которого соединены с. соответствующими информационными входами преобразователя параллельного ко& да в последовательный, выход которого является выходом устройства, второй элемент задержки, отличающееся тем, что, с целью повышения быстродействия устройст- . ва, в него введены первый, второй ключи и

0 блок управления режимами работы, выходы блока пиковых детекторов соединены с соответствующими информационными входами первого ключа, выходы которого соединены с соответствующими информационными вхо5 дами блока сравнения, второй вход регистра сдвига объединен с входом второго элемента задержки и подключен к входу синхронизации устройства, выходы регистра сдвига сое- диненыс соответствующими

0 информационными входами второго ключа и блока управления режимами работы, первый и второй выходы которого подключены к управляющим входам соответственно первого и второго ключей, первый и второй выходы

5 второго ключа соединены соответственно с вторым и третьим входами дешифратора, шестым и седьмым управляющими входами коммутатора, третьим и четвертым информационными входами блока памяти, третий

0 и четвертый выходы второго ключа соединены соответственно с восьмым и девятым управляющими входами коммутатора, выход второго элемента задержки подключен к третьему входу компаратора.

«; fv

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в волоконно-оптических цифровых системах передачи информации | 1989 |

|

SU1608730A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| МНОГОКАНАЛЬНЫЙ ПАНОРАМНЫЙ ПРИЕМНИК | 1996 |

|

RU2115997C1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Устройство для декодирования сверточного кода | 1991 |

|

SU1839281A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

Изобретение относится к вычислительной технике и может быть использовано для исправления ошибок в волоконно-оптических системах передачи информации. Целью изобретения является повышение быстродействия устройства. Устройство содержит мультиплексор, счетчик, синхронизатор, компаратор, пороговый элемент, блок пиковых детекторов, блок 7 формирования стробирующих импульсов, два элемента задержки, регистр сдвига, блок сравнения, два ключа, блок управления режимами работы, дешифратор, коммутатор, блок памяти, преобразователь параллельного кода в последовательный. 2 ил.

№$Ш1

-I-MH - i-iSJ- pM Ltx -l H -1 н -t - -t -t - .1 I j | ГТТ I 4 | I I I I j | +-t

: ; i i r, i i i ;i i i i i i i i i,

ДПППППШШ1ДД

| Сигнализационный аппарат для охраны касс | 1924 |

|

SU1367A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для исправления ошибок в волоконно-оптических цифровых системах передачи информации | 1989 |

|

SU1608730A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-04-15—Публикация

1990-06-28—Подача