о со оо i

до

ства входят сигнальный вход 1, кодовый 1-разрядный вход 2, I идентичных каскадов задержки, а каждый каскад задержки Содержит элемент 3 задерж- ки и ключевой элемент 4. Введенные отличия обеспечивают режим работы устройства, когда любой каскад задержки нагружен лишь на один вход последующего каскада. Благодаря па- раллельно-последовательному способу

соединения каскадов задержки,обеспечиваемому введением преобразователя кода, снабжению ключевых элементов дополнительными входами, объединению одноименных выходов всех каскадов, , а последнего 1-го выхода - непосредственно с выходом устройства последнее имеет точность более высокую,чем устройство-прототип, не менее чем на порядок. 2 з.п. ф-лы, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Каскад линии задержки | 1989 |

|

SU1629959A1 |

| Устройство для измерения амплитуды одиночных импульсных сигналов | 1982 |

|

SU1112301A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Цифро-аналоговый многофункциональный преобразователь | 1982 |

|

SU1062732A2 |

| Вычислительный преобразователь информации | 1985 |

|

SU1330642A1 |

| Преобразователь код-момент времени | 1982 |

|

SU1034176A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Адаптивное устройство для приема информации с рассредоточенных объектов | 1991 |

|

SU1807509A1 |

Изобретение относится к радиотехнике и может быть использовано в измерительной технике и других областях, где возникает необходимость в прецизионной регулируемой задержке аналоговых сигналов. Цель изобретения - повышение точности задержки путем стабилизации нагрузки каждого каскада задержки - достигается за счет введения в каждый каскад задержки преобразователя 5 кода и новых связей. Кроме того, в состав устрой

Изобретение относится к радиотехнике и может быть использовано в измерительной технике и других областях науки и техники при необходимости прецизионной задержки сигнала, регулируемой кодом.

Цель изобретения - повышение точности задержки путем стабилизации нагрузки каждого каскада задержки.

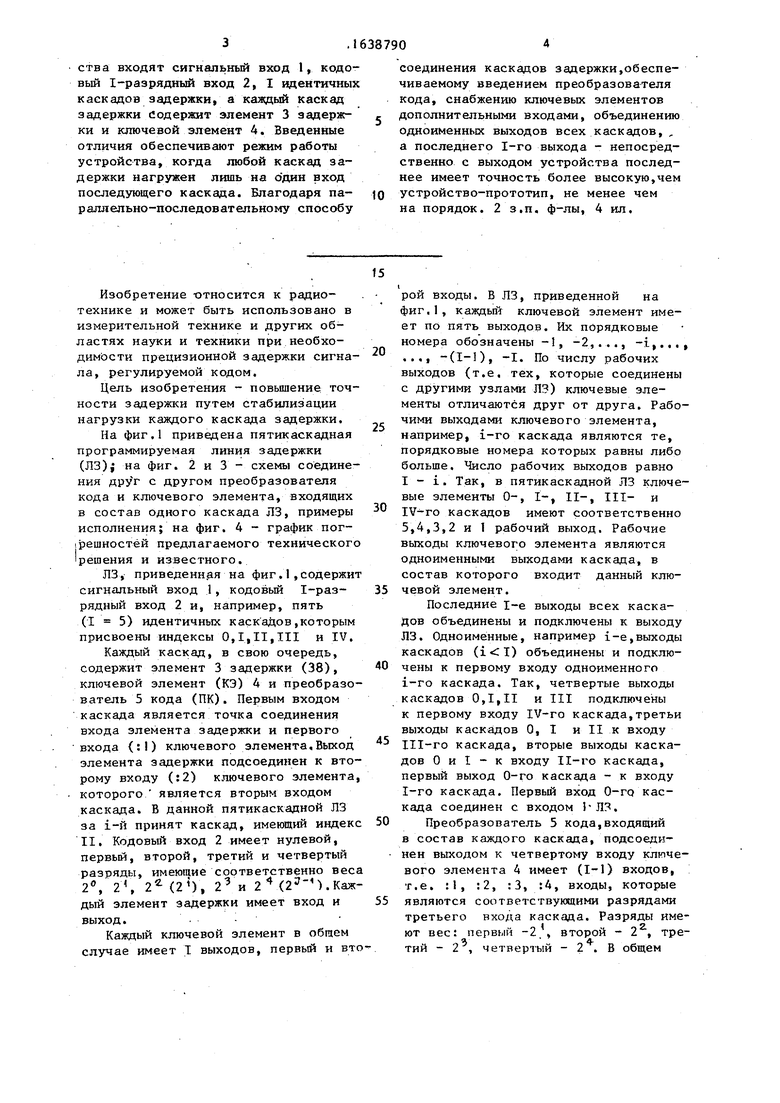

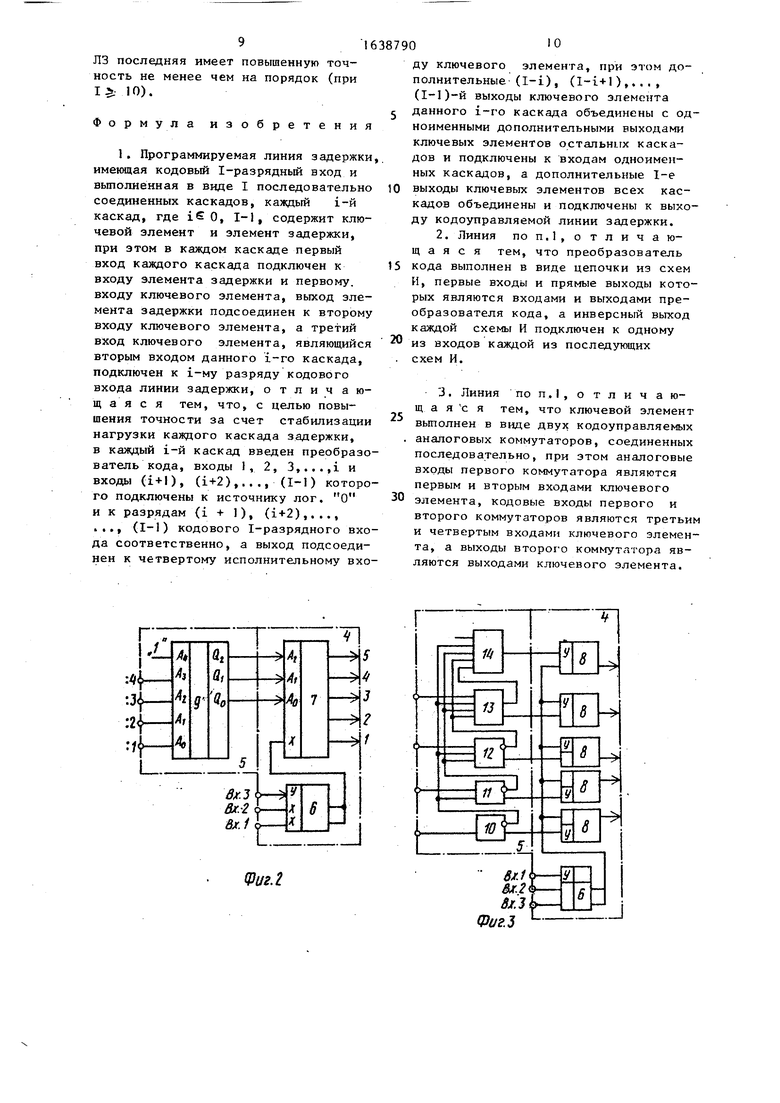

На фиг.1 приведена пятикаскадная программируемая линия задержки (ЛЗ); на фиг. 2 и 3 - схемы соединения друг с другом преобразователя кода и ключевого элемента, входящих в состав одного каскада ЛЗ, примеры исполнения; на фиг, 4 - график пог- фешностей предлагаемого технического решения и известного.

ЛЗ, приведенная на фиг.1,содержит сигнальный вход 1, кодовый 1-разрядный вход 2 и, например, пять (I 5) идентичных каскадов,которым присвоены индексы 0,1,11,111 и IV.

Каждый каскад, в свою очередь, содержит элемент 3 задержки (38), ключевой элемент (КЭ) 4 и преобразователь 5 кода (ПК). Первым входом каскада является точка соединения входа элемента задержки и первого входа (:) ключевого элемента,Выход элемента задержки подсоединен к второму входу (:2) ключевого элемента, которого является вторым входом каскада. В данной пятикаскадной ЛЗ за i-й принят каскад, имеющий индекс II. Кодовый вход 2 имеет нулевой, первый, второй, третий и четвертый разряды, имеющие соответственно веса 2°, 2 2 (2), 23 и 2 4 (231). Каждый элемент задержки имеет вход и выход.

Каждый ключевой элемент в общем случае имеет I выходов, первый и вто

i рой входы. В ЛЗ, приведенной на

фиг.1, каждый ключевой элемент имеет по пять выходов. Их порядковые номера обозначены -1, -2,..., -i,..., ..., -(1-1), -I. По числу рабочих выходов (т.е. тех, которые соединены с другими узлами Л) ключевые элементы отличаются друг от друга. Рабо- чими выходами ключевого элемента, например, i-го каскада являются те, порядковые номера которых равны либо больше. Число рабочих выходов равно I - i. Так, в пятикаскадной ЛЗ ключевые элементы 0-, I-, II-, III- и

IV-ro каскадов имеют соответственно

5,4,3,2 и 1 рабочий выход. Рабочие выходы ключевого элемента являются одноименными выходами каскада, в состав которого входит данный ключевой элемент.

Последние 1-е выходы всех каскадов объединены и подключены к выходу ЛЗ. Одноименные, например 1-е,выходы каскадов (i«CI) объединены и подключены к первому входу одноименного 1-го каскада. Так, четвертые выходы каскадов 0,1,11 и III подключены к первому входу IV-ro каскада,третьи выходы каскадов О, I и II к входу

III-го каскада, вторые выходы каскадов 0 и I - к входу 11-го каскада, первый выход 0-го каскада - к входу 1-го каскада. Первый вход 0-го каскада соединен с входом 1-ЛЗ.

Преобразователь 5 кода,входящий

в состав каждого каскада, подсоединен выходом к четвертому входу ключевого элемента 4 имеет (1-1) входов, т.е. :1, :2, :3, :4, входы, которые

являются соответствующими разрядами третьего входа каскада. Разряды име10

ют вес: первый -2., второй - 2 , третий - 2 , четвертый - 2 . В общем

случае вес 1-го разряда равен 2.Разряды третьего входа каскада,порядковые номера которых больше номера данного каскада, являются рабочими. Каскады различаются по числу рабочих разрядов третьего входа, например i-й каскад имеет (I-i-1) рабочих разрядов. Одноименные рабочие разряды третьих входов всех каскадов объединены и подключены к одноименному разряду кодового входа 2 ЛЗ: первый разряд третьего входа 0-го каскада подключен к первому разряду входа,второй разряд - к второму и т.д. Второй вход каждого каскада подключен к тому разряду входа 2 ЛЗ, порядковый номер которого совпадает с порядковым номером каскада: нулевой разряд входа 2 подключен к второму входу 0-го каскада, 1-й разряд - к второму входу 1-го каскада и т.д. Каждый из нерабочих разрядов третьего входа каждого каскада подключён к источнику лог. О (на фиг.1 не показан) .

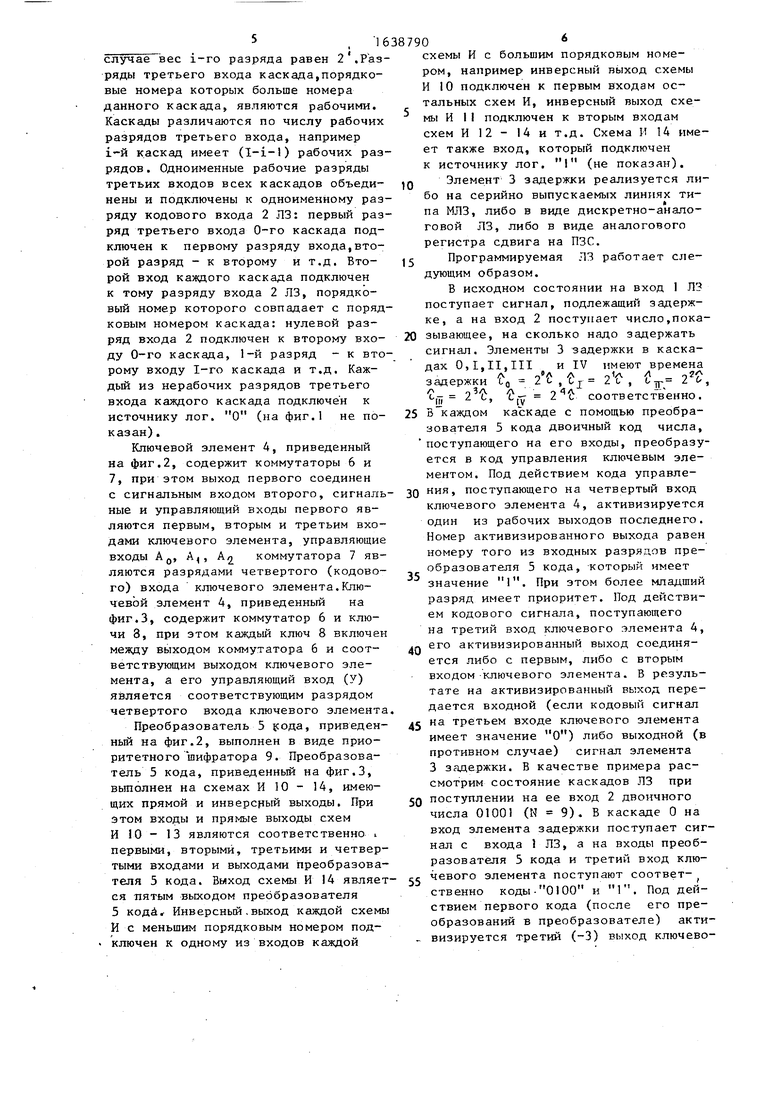

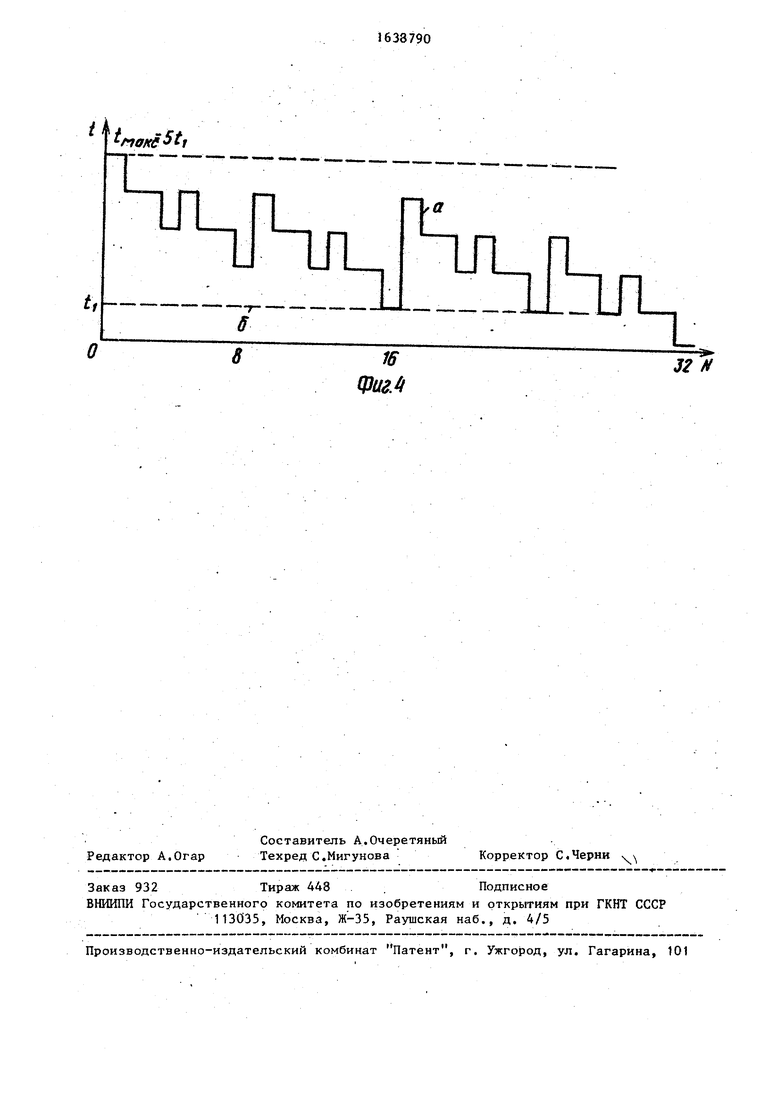

Ключевой элемент 4, приведенный на фиг.2, содержит коммутаторы 6 и 7, при этом выход первого соединен

с сигнальным входом второго, сигналь- 30 ния поступающего на четвертый вход

ключевого элемента 4, активизируется один из рабочих выходов последнего. Номер активизированного выхода равен номеру того из входных разрядов преобразователя 5 кода, который имеет значение 1. При этом более младший разряд имеет приоритет. Под действием кодового сигнала, поступающего на третий вход ключевого элемента 4, его активизированный выход соединяется либо с первым, либо с вторым входом ключевого элемента. В результате на активизированный выход передается входной (если кодовый сигнал на третьем входе ключевого элемента имеет значение О) либо выходной (в противном случае) сигнал элемента 3 задержки. В качестве примера рассмотрим состояние каскадов ЛЗ при поступлении на ее вход 2 двоичного числа 01001 (N 9). В каскаде 0 на вход элемента задержки поступает сиг нал с входа 1 ЛЗ, а на входы преобразователя 5 кода и третий вход ключевого элемента поступают соответ- ( ственно коды- 0100 и 1. Под действием первого кода (после его преобразований в преобразователе) акти визируется третий (-3) выход ключево

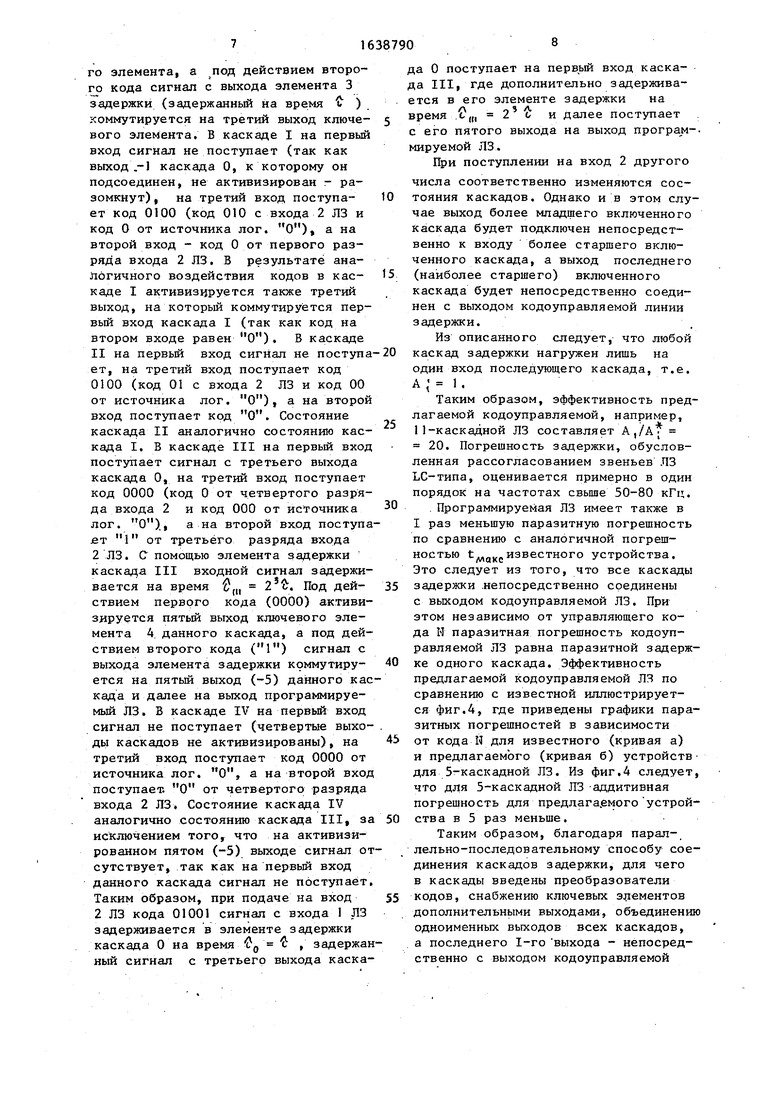

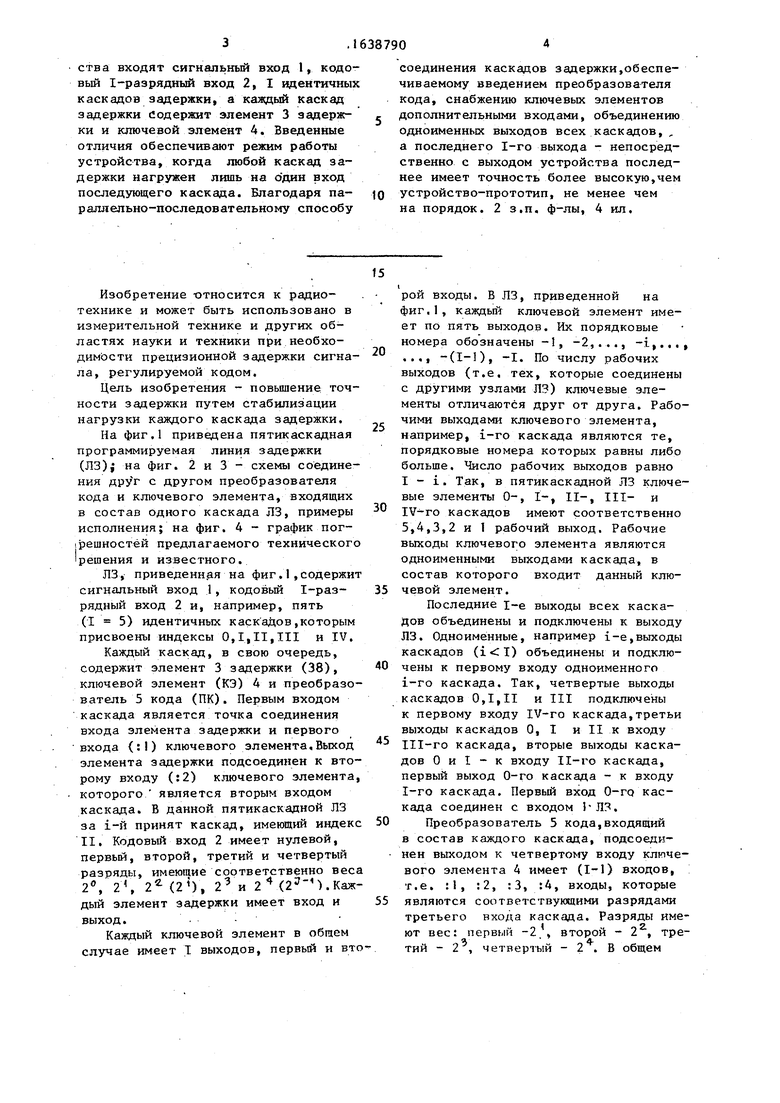

ные и управляющий входы первого являются первым, вторым и третьим входами ключевого элемента, управляющие входы АО, А,, А коммутатора 7 являются разрядами четвертого (кодового) входа ключевого элемента.Ключевой элемент 4, приведенный на фиг.З, содержит коммутатор 6 и ключи 3, при этом каждый ключ 8 включен между выходом коммутатора б и соответствующим выходом ключевого элемента, а его управляющий вход (У) является соответствующим разрядом четвертого входа ключевого элемента Преобразователь 5 кода, приведенный на фиг.2, выполнен в виде приоритетного шифратора 9. Преобразователь 5 кода, приведенный на фиг.З, выполнен на схемах И 10 - 14, имеющих прямой и инверсный выходы. При этом входы и прямые выходы схем И 10 - 13 являются соответственно i первыми, вторыми, третьими и четвертыми входами и выходами преобразователя 5 кода. Выход схемы И 14 является пятым выходом преобразователя 5 кода Инверсный.выход каждой схемы И с меньшим порядковым номером подключен к одному из входов каждой

5

0

схемы И с большим порядковым номером, например инверсный выход схемы И 10 подключен к первым входам остальных схем И, инверсный выход схемы И 1 1 подключен к вторым входам схем И 12 - 14 и т.д. Схема И 14 имеет также вход, который подключен к источнику лог. 1 (не показан).

Элемент 3 задержки реализуется либо на серийно выпускаемых линиях типа МЛЗ, либо в виде дискретно-аналоговой ЛЗ, либо в виде аналогового регистра сдвига на ПЗС.

Программируемая ЛЗ работает следующим образом.

В исходном состоянии на вход 1 ЛЗ поступает сигнал, подлежащий задержке, а на вход 2 поступает число,показывающее, на сколько надо задержать сигнал. Элементы 3 задержки в каскадах 0,1,11,111 и IV имеют времена

Л т Л

О Т - Ј. Ь

2

5

задержки V0 2 t:, tj , tlr 2 С-, с|1; 23Ј, tfi соответственно. В каждом каскаде с помощью преобразователя 5 кода двоичный код числа, поступающего на его входы, преобразуется в код управления ключевым элементом. Под действием кода управле0 ния поступающего на четвертый вход

5

0

5

0

5

ключевого элемента 4, активизируется один из рабочих выходов последнего. Номер активизированного выхода равен номеру того из входных разрядов преобразователя 5 кода, который имеет значение 1. При этом более младший разряд имеет приоритет. Под действием кодового сигнала, поступающего на третий вход ключевого элемента 4, его активизированный выход соединяется либо с первым, либо с вторым входом ключевого элемента. В результате на активизированный выход передается входной (если кодовый сигнал на третьем входе ключевого элемента имеет значение О) либо выходной (в противном случае) сигнал элемента 3 задержки. В качестве примера рассмотрим состояние каскадов ЛЗ при поступлении на ее вход 2 двоичного числа 01001 (N 9). В каскаде 0 на вход элемента задержки поступает сигнал с входа 1 ЛЗ, а на входы преобразователя 5 кода и третий вход ключевого элемента поступают соответ- ( ственно коды- 0100 и 1. Под действием первого кода (после его преобразований в преобразователе) активизируется третий (-3) выход ключево

го элемента, а ,под действием второго кода сигнал с выхода элемента 3 задержки (задержанный на время С ) коммутируется на третий выход ключе- вого элемента. В каскаде I на первый вход сигнал не поступает (так как выход .-1 каскада 0, к которому он подсоединен, не активизирован - разомкнут), на третий вход поступа- ет код 0100 (код 010 с входа 2 ЛЗ и код О от источника лог. О), а на второй вход - код 0 от первого разряда входа 2 ЛЗ. В результате аналогичного воздействия кодов в кас- каде I активизируется также третий выход, на который коммутируется первый вход каскада I (так как код на втором входе равен О). В каскаде II на первьй вход сигнал не поступает, на третий вход поступает код 0100 (код 01 с входа 2 ЛЗ и код 00 от источника лог. О), а на второй вход поступает код О. Состояние каскада II аналогично состоянию каскада I. В каскаде III на первый вход поступает сигнал с третьего выхода каскада 0, на третий вход поступает код 0000 (код 0 от четвертого разряда входа 2 и код 000 от источника лог. О), а на второй вход поступает 1 от третьего разряда входа 2 ЛЗ. С помощью элемента задержки каскада III входной сигнал задерживается на время Ј(1( 2 Ј. Под дей- ствием первого кода (0000) активизируется пятый выход ключевого элемента 4 данного каскада, а под действием второго кода (1) сигнал с выхода элемента задержки коммутиру- ется на пятый выход (-5) данного каскада и далее на выход программируемый ЛЗ. В каскаде IV на первьй вход сигнал не поступает (четвертые выходы каскадов не активизированы), на третий вход поступает код 0000 от источника лог. О, а на второй вход поступает. О от четвертого разряда входа 2 ЛЗ. Состояние каскада IV аналогично состоянию каскада III, за исключением того, что на активизированном пятом (-5) выходе сигнал отсутствует, так как на первый вход данного каскада сигнал не поступает. Таким образом, при подаче на вход 2 ЛЗ кода 01001 сигнал с входа 1 ЛЗ задерживается в элементе задержки каскада 0 на время Ј0 Ј , задержанный сигнал с третьего выхода каска

да 0 поступает на первый вход каскада III, где дополнительно задерживана

ется в его элементе задержки время С„, 2 Ј и далее поступает с его пятого выхода на выход програм-- мируемой ЛЗ.

При поступлении на вход 2 другого

числа соответственно изменяются состояния каскадов. Однако и в этом случае выход более младшего включенного каскада будет подключен непосредственно к входу более старшего включенного каскада, а выход последнего (наиболее старшего) включенного каскада будет непосредственно соединен с выходом кодоуправляемой линии задержки.

Из описанного следует, что любой каскад задержки нагружен лишь на один вход последующего каскада, т.е. А 1,

Таким образом, эффективность предлагаемой кодоуправляемой, например, 11-каскадной ЛЗ составляет А,/А 20. Погрешность задержки, обусловленная рассогласованием звеньев ЛЗ LC-типа, оценивается примерно в один порядок на частотах свыше 50-80 кГц.

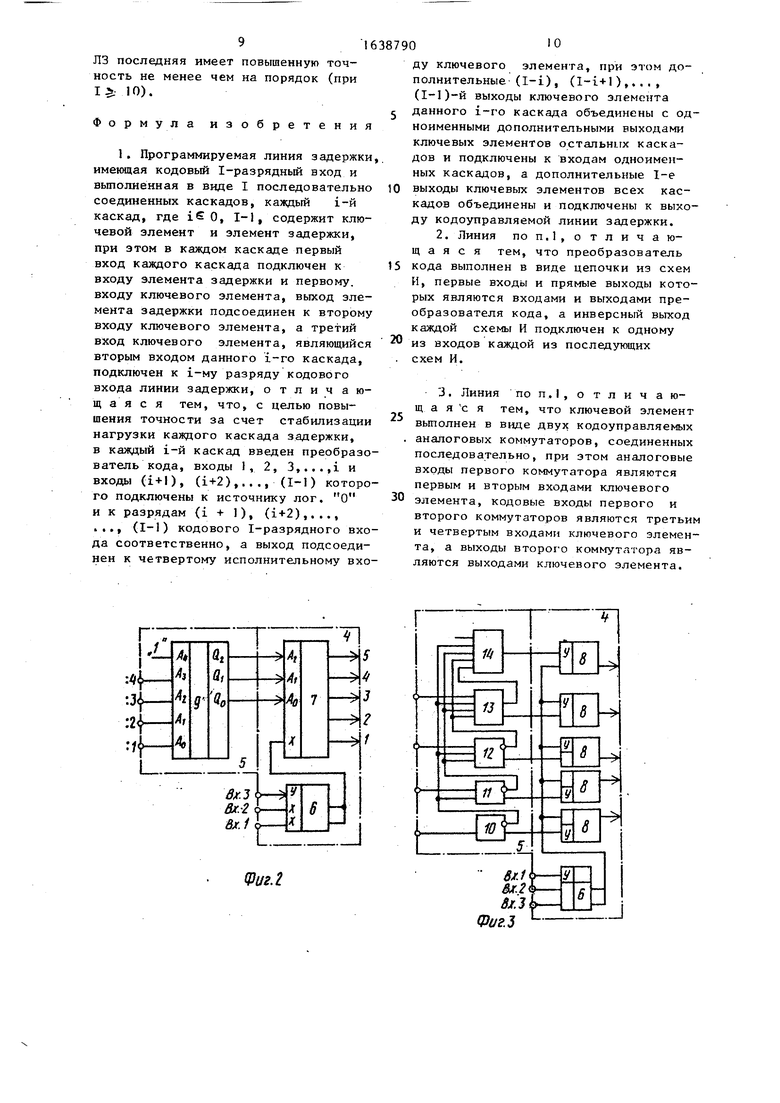

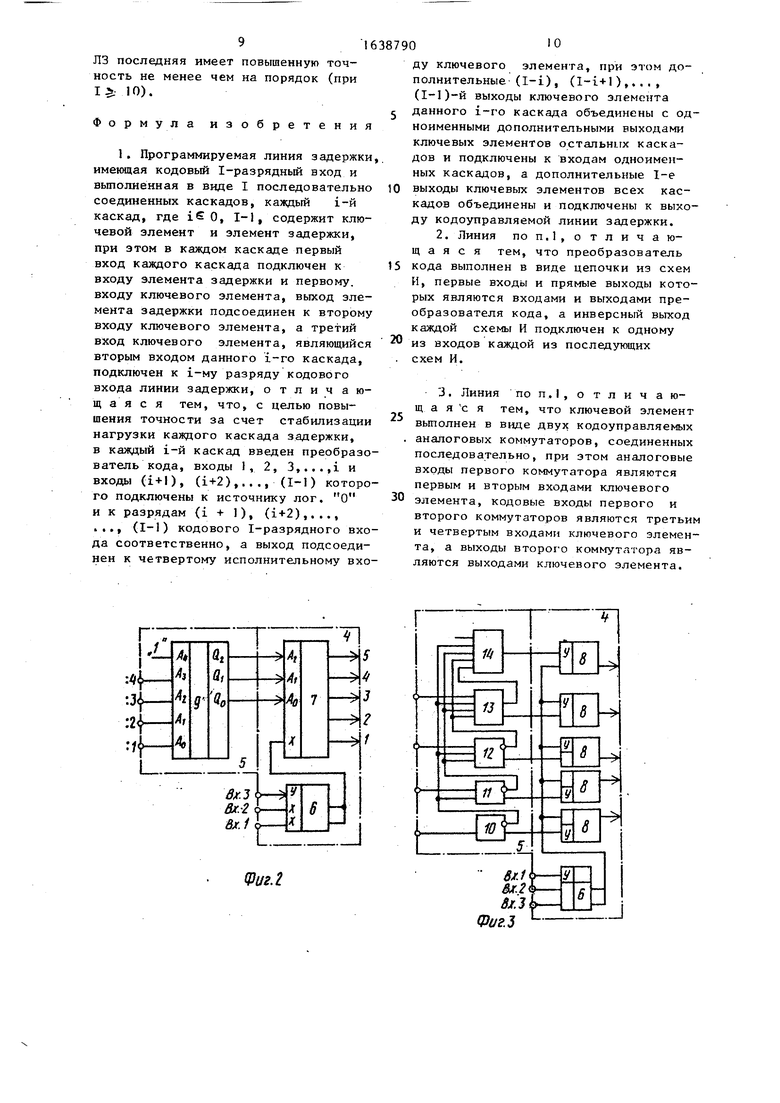

Программируемая ЛЗ имеет также в I раз меньшую паразитную погрешность по сравнению с аналогичной погрешностью t

макс

известного устройства.

Это следует из того, что все каскады задержки непосредственно соединены с выходом кодоуправляемой ЛЗ. При этом независимо от управляющего кода Н паразитная погрешность кодоуправляемой ЛЗ равна паразитной задержке одного каскада. Эффективность предлагаемой кодоуправляемой ЛЗ по сравнению с известной иллюстрируется фиг.4, где приведены графики паразитных погрешностей в зависимости от кода N для известного (кривая а) и предлагаемого (кривая б) устройств для 5-каскадной ЛЗ. Из фиг.4 следует, что для 5-каскадной ЛЗ аддитивная погрешность для предлагаемого устройства в 5 раз меньше.

Таким образом, благодаря парал-. лельно-последовательному способу соединения каскадов задержки, для чего в каскады введены преобразователи кодов, снабжению ключевых элементов дополнительными выходами, объединению одноименных выходов всех каскадов, а последнего 1-го выхода - непосредственно с выходом кодоуправляемой

ЛЗ последняя имеет повышенную точность не менее чем на порядок (при 1$. Ю).

Формула изобретения

1, Программируемая линия задержки, имеющая кодовый I-разрядный вход и

выполненная в виде I последовательно соединенных каскадов, каждый 1-й каскад, где IS 0, 1-1, содержит ключевой элемент и элемент задержки, при этом в каждом каскаде первый вход каждого каскада подключен к входу элемента задержки и первому. входу ключевого элемента, выход элемента задержки подсоединен к второму входу ключевого элемента, а третий вход ключевого элемента, являющийся вторым входом данного 1-го каскада, подключен к i-му разряду кодового входа линии задержки, о т л и ч а ю- щ а я с я тем, что, с целью повышения точности за счет стабилизации нагрузки каждого каскада задержки, в каждый i-й каскад введен преобразователь кода, входы ), 2, 3,...,i и входы (i-H), (i+2),..., (1-1) которого подключены к источнику лог. О и к разрядам (i + 1), (i+2),..., ..., (1-1) кодового 1-разрядного входа соответственно, а выход подсоединен к четвертому исполнительному вхо,

10

3879010

ду ключевого элемента, при этом дополнительные (I-i), (l-i+1),..., (1-1)-й выходы ключевого элемента ; данного 1-го каскада объединены с одноименными дополнительными выходами ключевых элементов остальных каскадов и подключены к входам одноименных каскадов, а дополнительные 1-е выходы ключевых элементов всех каскадов объединены и подключены к выходу кодоуправляемой линии задержки.

15

20

t

/vff/irf5ff

Tff

и N

| Дискретно-аналоговая линия задержки | 1982 |

|

SU1115230A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для защиты сборных шин электрических станций и подстанций | 1982 |

|

SU1019539A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-03-30—Публикация

1988-12-27—Подача