(Г,

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для счета единиц подвижного состава | 1988 |

|

SU1623903A1 |

| Система управления транспортным конвейером | 1988 |

|

SU1627472A1 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1988 |

|

SU1518905A2 |

| Генератор синусоидальных функций | 1989 |

|

SU1624432A1 |

| Устройство для обнаружения патологических образований в легких | 1989 |

|

SU1623619A1 |

| Устройство для встроенного контроля логических блоков | 1986 |

|

SU1392569A1 |

| Устройство для определения дисбаланса роторов | 1988 |

|

SU1534349A1 |

| Устройство для фиксации неустойчивых сбоев | 1986 |

|

SU1392567A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1392566A1 |

| Устройство управления электронной игрой | 1986 |

|

SU1400626A1 |

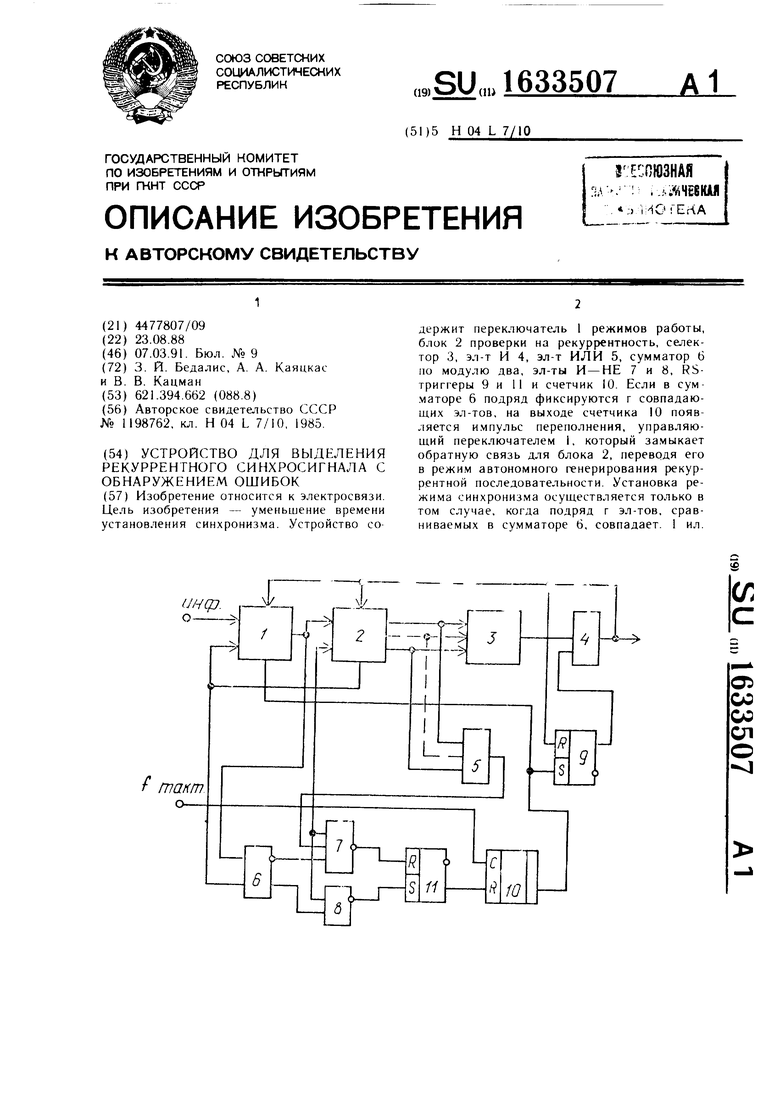

Изобретение относится к электросвязи Цель изобретения - уменьшение времени установления синхронизма. Устройство со держит переключатель 1 режимов работы, блок 2 проверки на рекуррентность, селектор 3, эл-т И 4, эл-т ИЛИ 5, сумматор 6 по модулю два, эл-ты И-НЕ 7 и 8, RS- триггеры 9 и 11 и счетчик 10 Если в сумматоре 6 подряд фиксируются г совпадающих эл-тов, на выходе счетчика 10 появляется импульс переполнения, управляющий переключателем 1, который замыкает обратную связь для блока 2, переводя его в режим автономного генерирования рекуррентной последовательности Установка режима синхронизма осуществляется только в том случае, когда подряд г эл-тов, сравниваемых в сумматоре 6, совпадает 1 ил

О5

ее ее ел

Июбрегение относится к теыросвнзи и может бьпь испотьювана дня цик ювой синхронизации в системах передачи чвоич ной информации

1 U ью и юбрс гения яв тяетс я у меныпение времени установ гения синхронизма

На чертеже тфс тл тав тена сгрхктурная : ie кт ричеек JH ма Vc i оие i ва i тя выде те ния peKyppt нтно о е инхрое игна ia e обнару жением ошибок

cipoHeiBO i 1Я вы и тения рекчррснгно ю еинхрои iна та i оонар жением ошибок соиржит IK ре к юча тс ть 1 режимов работы б юк 2 проверки на рек ррен i нос i ь CCICK гор } sic мент И 4 die мент И 1И г сумматор b но мо iv IKJ два первый 7 и BIO рои 8 iievtmbi И НЕ:, первпи RSTpm iep Ч ечетчик 1(1 и нгорои RS ipmiep I1

N е троне i во paooi at т с те n ющим обра шм

Принимаемая твоичн )я пое кмовате ть ноеть синхрск ш на ia ape i перек початеть I поступает на те мен г И 4 который coiep жит рем neip e 1вта на k рафядов е точка ми с тема на с у иматорс h в е согнете I вии многочнчюм I (х) гы peineipa e IBM i а б юка 2 похкпочены шпотни i e тьно па pa i ie 1ьно к нхотлм ее it мора 3 и э темен ia И 1И ) Информационный е инхроеш на т с мерек тгоча ге тя I также тнкт v пает на первый вхо i сумматора b на вго рои вхо i котрок) тост ie сит на т e вы xo ia о юка 2

HiBneTHO TO KOI Id В О ЮКС 2 ЫПИ

сано А1 бемошибочных eleven гов пое ie ю вагсмьности i e нернр ющии потином которой vinoiO4ien 1 (х| на выхоте г е на о юка 2 формир екя значение / 1 ю j it мента пое it 1,ова ie и

KOI la в б юке marine duo k ле ментов, на ei о выхо i,e формирч/екя на 1ение ю j юмента которое Bevvmarope ьеравнивает ея е поег ыюшим на вхо i б кжа А. +1 м 1ементом принимаемым с них роет на том На инверсном выхоте е чматора b четанаши вается выеокий чронень кома ти jievitu ты eoBiiaiarai Это ошачаег что в б ток 2 ыпиеаны э к менты пое те дователыше и и что пое гмшвшии 1емент также яв1Ж1ея 1ементом той VI пое leioea eibHoein На выходе :мемента И 1И 5 е мнав шваеге я е иничныи ровень ее in хотя оы один j ie менг in записанных в б юк 2 имеет tua чение единицы и тем (.аиым иеК1ЮЧ1е ея срабатывание, схемы KOI ia принимаемый cm на i состой i и синих nv ICH KOI id it менты сравнивнмые в VMMaropeb сов на ыют ш с шпатами ею выхо юв откры вас ге я nepibiH к ннг И HF 7 и 5 тира е тс я вюрои -ticMeur И HL 8 Тамовыи UMIIV ibc iidcT пивший черем открьпыи пер вый пимент И НЕ 7 VCT анав швает RS триггер II в HV ICBOC еостояние и ни ким ровнем е прямою luixoia второй) RS ipunepa II е ганав шваетея ечегныи режим ечегчик Н) коюрыи по кчнтывае г такты he ти в сумматоре ь по 1;тя i афикеировакы

5

г совпа1ающих элементов, на выходе счет чика 10 появляетея импульс переполнения, который пое на управляющий вход Переключа гатя 1 режимов работы и устанав швает первый тртгер 9 в единичное со

еюяние который отключает первый инфор мационныи вход переключателя 1 от его вы xo ui и по1Л1ючает второй информацией ныи вход на выход переключателя 1, (амыкая тем самым обраТн ю связь для

б юка 2 и переводит нос 1едний в режим автономною генерирования рекуррентной по- с 1едовагс 1ьности еогласно многочлену F(x) Вхош сумматора b соединяются это озна чает что на ею инверсном выходе устанав швастся единичный ровень и счетчик 10 формирует импульсы переполнения которые мо11верж1аюг единичное состояние первого RS триггера 9 ИМПУЛЬС перепотнения ста нав швает пое 1еднии в ечиничное состояние, кменг И 4 отпирается и при достиже

0 нии в ее гскторе i селектируемой комби нации на его выходе формируется им nv ibc который поступает на выход уст pcnuiBd а также на первый управляю шип вход перектючагеля 1 и на вход пер вою RS триггера Q 11од действием этого nvii 1ы а первый RS триггер 9 и переклю чаи 1Ь 1 опрокидываются в исходное состоя ние размыкая обратную связь для блока 2 lono житетьно сигнапом е выхода элемента И 4 сбрасывается в нулевое состояние блок 2 сiponciво начинает новый цикл приема Е с ш в процессе приема появляются ошиб т и на прямом выходе сумматора 6 уста нав шваегся высокий уровень который отпи рает второй лемент И - НЬ 8 и тактовым HMTIV тьсом счетчик 10 устанавтивается в еди ничное состояние тем самым сбрасывая счетчик К) в исходное состояние

cianoBKd режима синхронизма осущест впяеня в том случае когда подряд i змеменгов сравниваемых в сумматоре, о(совпа;ает Импупьс переполнения на выхо

0 le ечетчика 10 формируется топько в том е и чае ког ia эпементов принято о синх рост на та явтяются э тементами VA постедо ваге ibHoeiH генерирующим по шномом кото рои явтяется многом ien E (х) Сети принять, т i о с мкость счетчика 10 бтоком2исум

магорем b проверено Hd рекуррентность 2k i к ме i тов принимаемой пое 1ет.овательноети

5

0

5

Форчуш июирегения

с тройство д т рекуррентно го инхросигната е обнаружением ошибок, еотержащее нос 1етоватетьно соединенные пе- )t к 1ючате ть режимов бток проверки на ре ре КУ ррен гноеть (Ы1Р) ссмектор и элемент И а также цемент ИЛИ счетчик и пер ши R гример Bbixoi которого подклю чен к второму вхо 1У леменга И выход которою явтяется выхоюм устройства и ао1К1ючсн к R вхо i первою KS триггера и к первым управ тяюшим входам Ы1Р

и переключателя режимов, первый информационный вход которого является информационным входом устройства, а второй информационный вход подключен к информационному выходу БПР, сигнальные выходы которого подключены к входам элемента ИЛИ, отличающееся тем, что, с целью уменьшения времени установления синхронизма, введены последовательно соединенные сумматор по модулю два, первый элемент И-НЕ и второй RS-трнггер, а также второй элемент И-НЕ, первый и второй входы которого подключены соответственно к прямому выходу сумматора по модулю два

и к соединенным между собой тактовым входам первого элемента И-НЕ, счетчика и БПР и являются тактовым входом устройства, выход элемента ИЛИ подключен к сигнальному входу первого элемента И-НЕ, вы ход второго элемента И-НЕ через второй / 5-триггер подключен к управляющему входу счетчика, выход которого подключен к 5-входу первого / 5-триггера и второму управляющему входу переключателя режимов, выход и второй информационный вход которого подключены соответственно к первому и второму входам сумматора по модулю два.

| Авторское свидетельство СССР № 1198762, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-03-07—Публикация

1988-08-23—Подача