Изобретение относится к технике электрических измерений параметров вращения и может быть использовано для измерения соотношения скоростей (отношения, относительной разности вращения валов и осей

различных машин, например осей ведущих и свободнокатящихся колес магистрального электровоза при регулировании силы тяги асинхронных тяговых двигателей.

Целью изобретения является повышение точности измерения соотношения скоростей путем уменьшения длительности цикла преобразования.

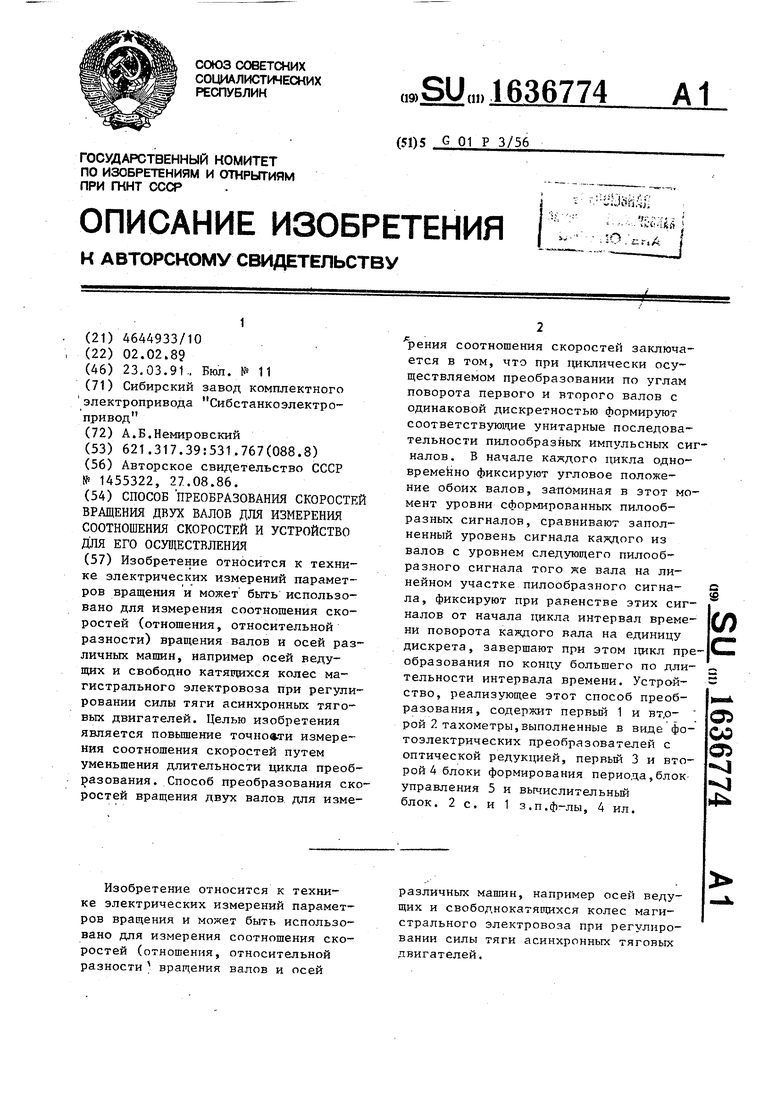

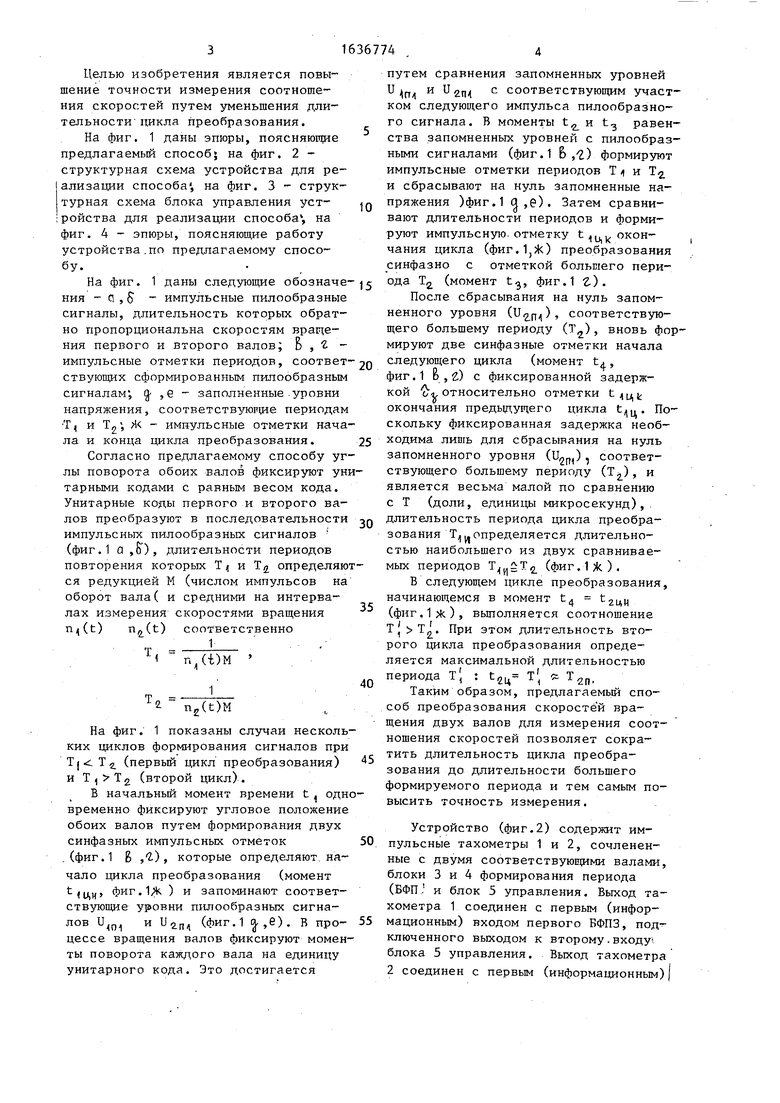

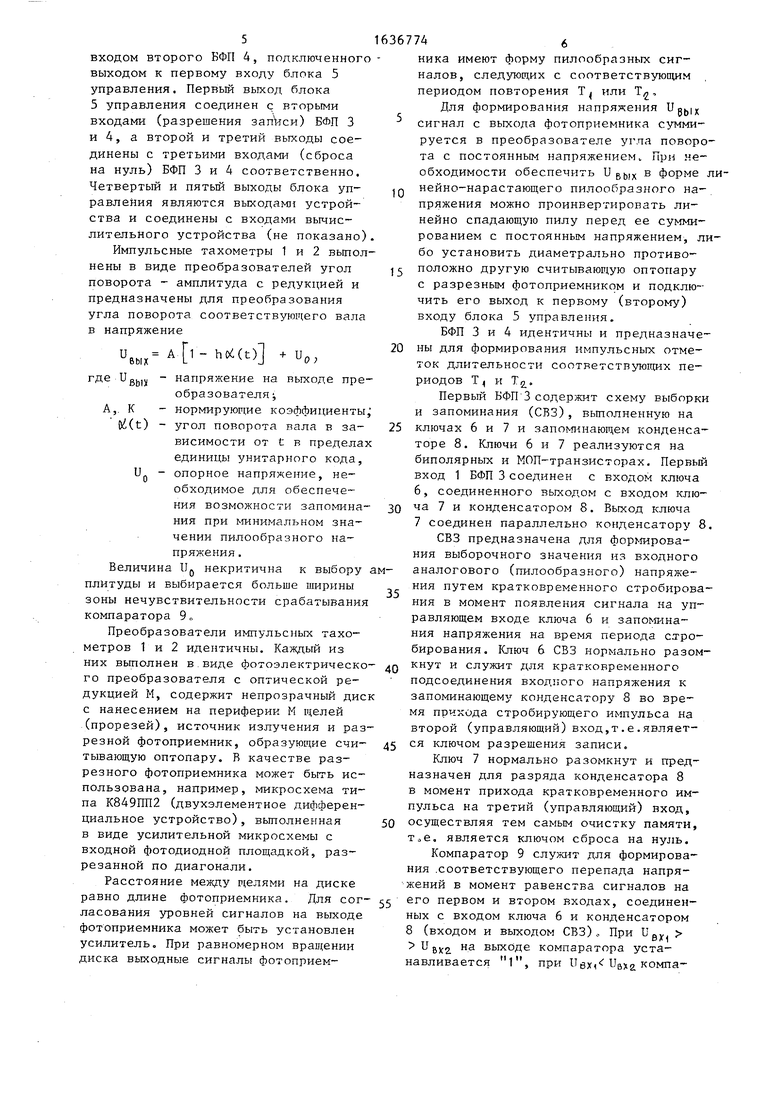

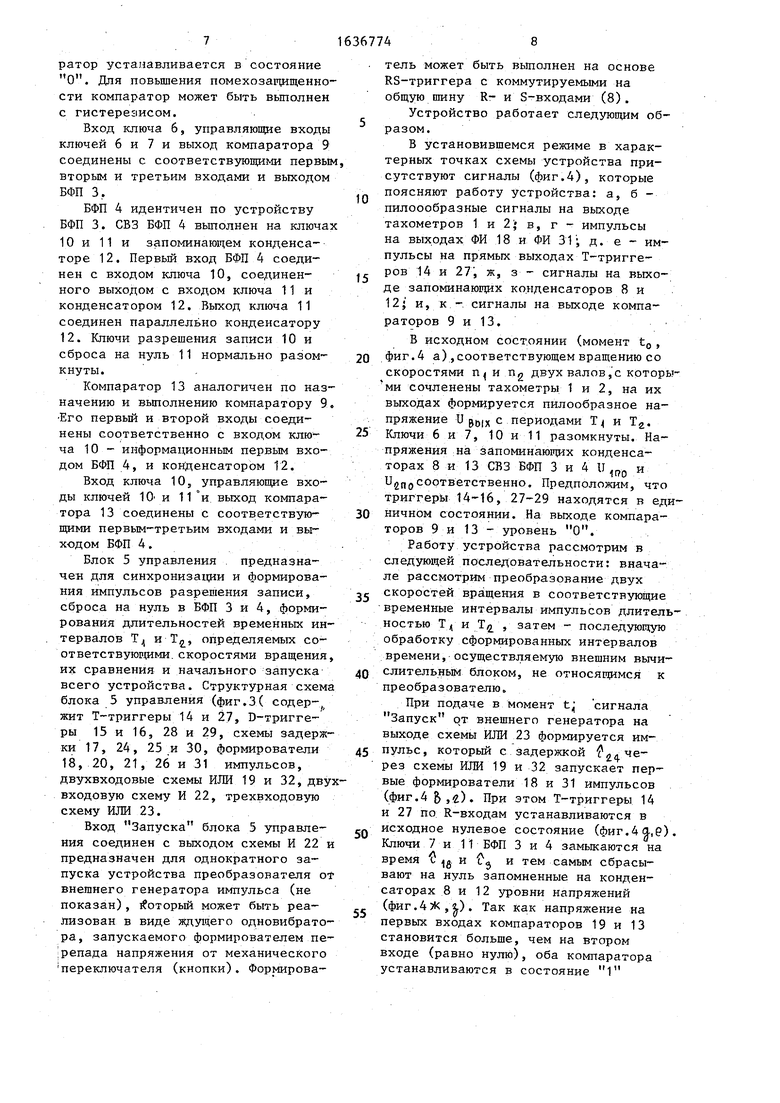

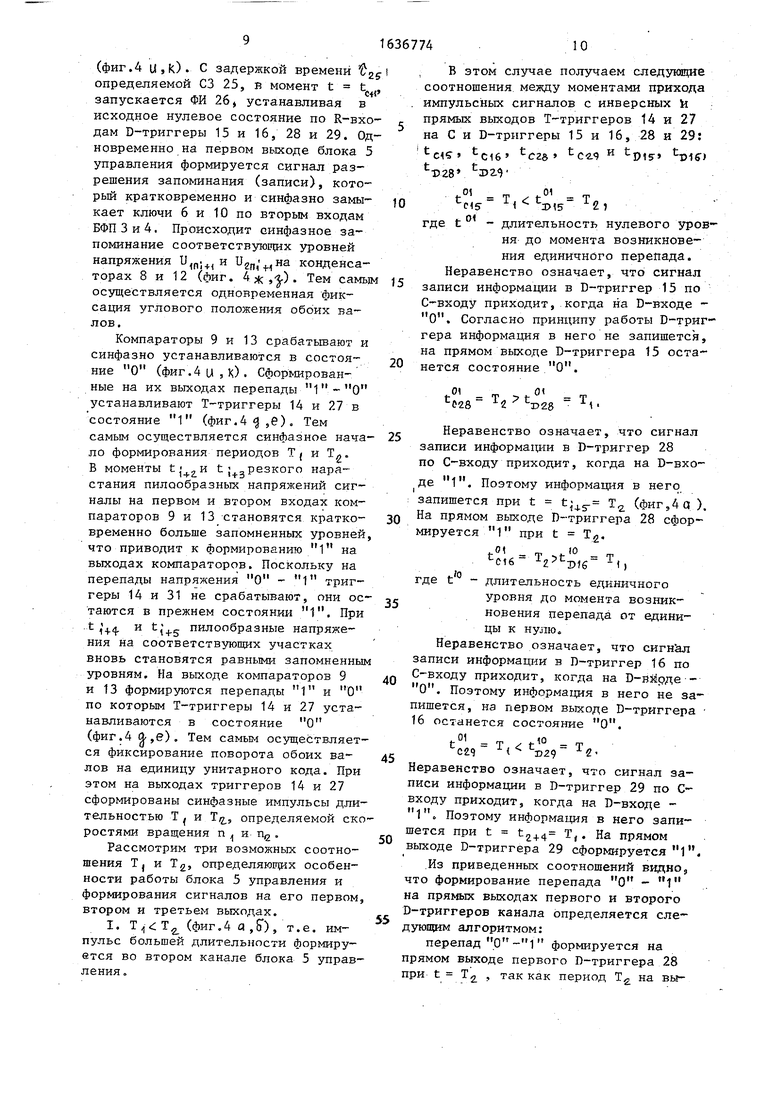

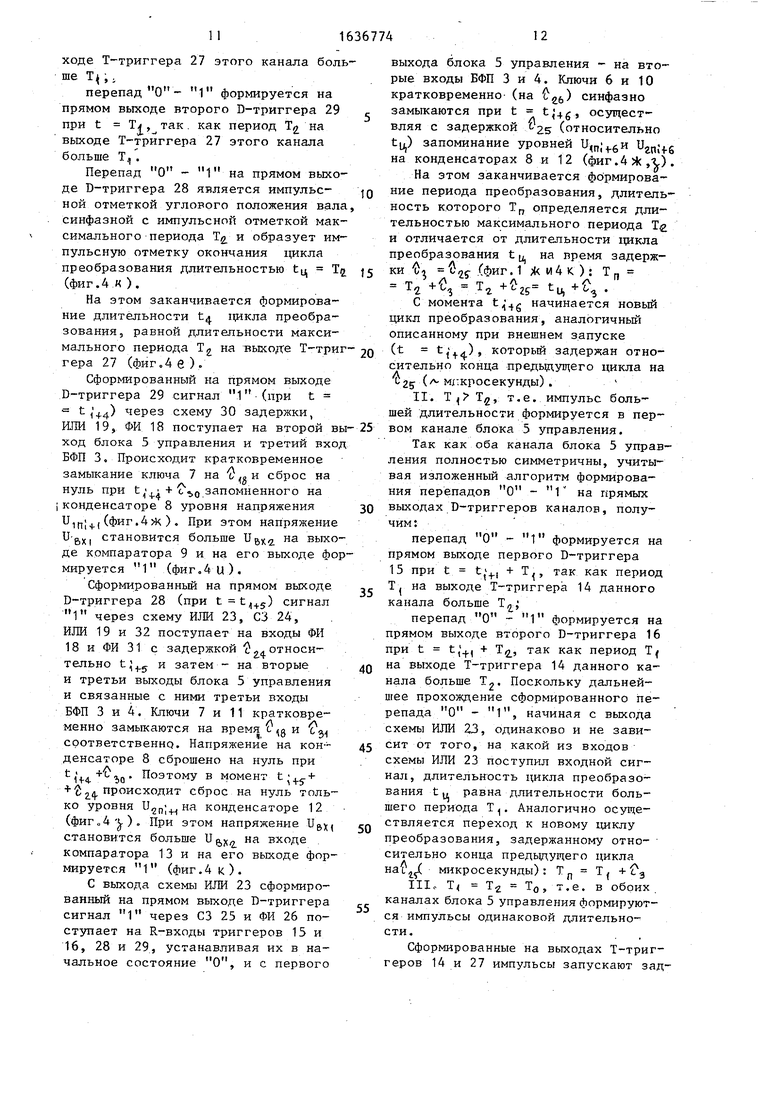

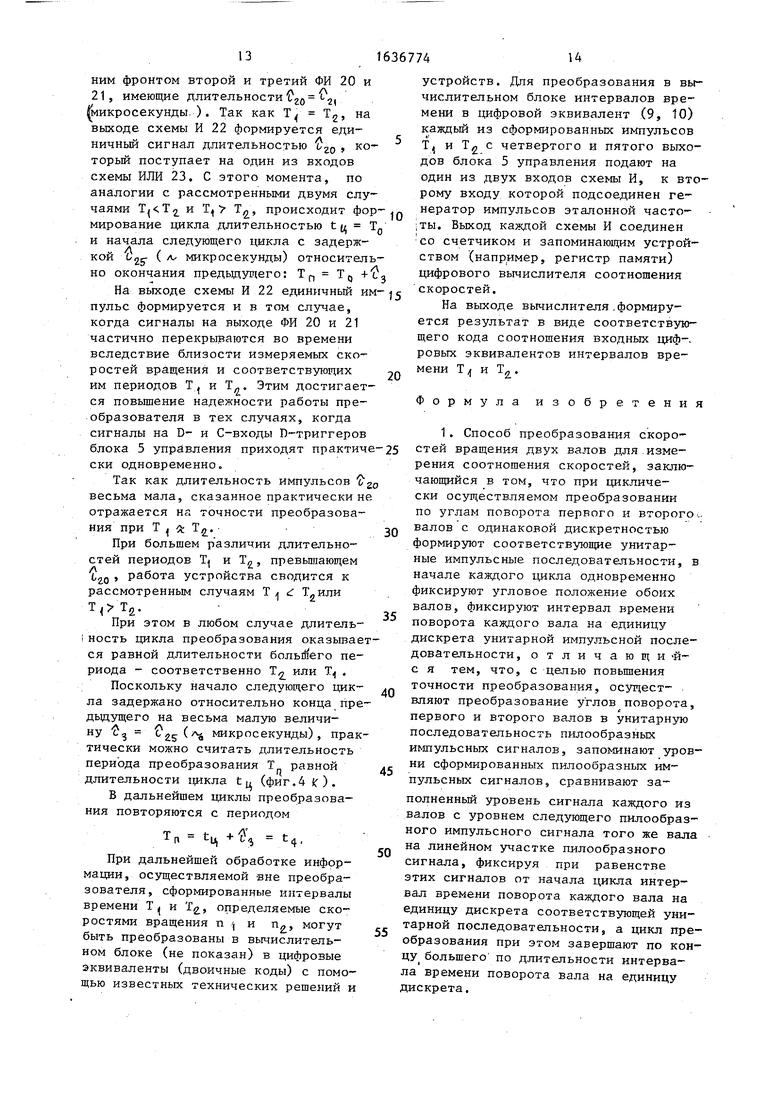

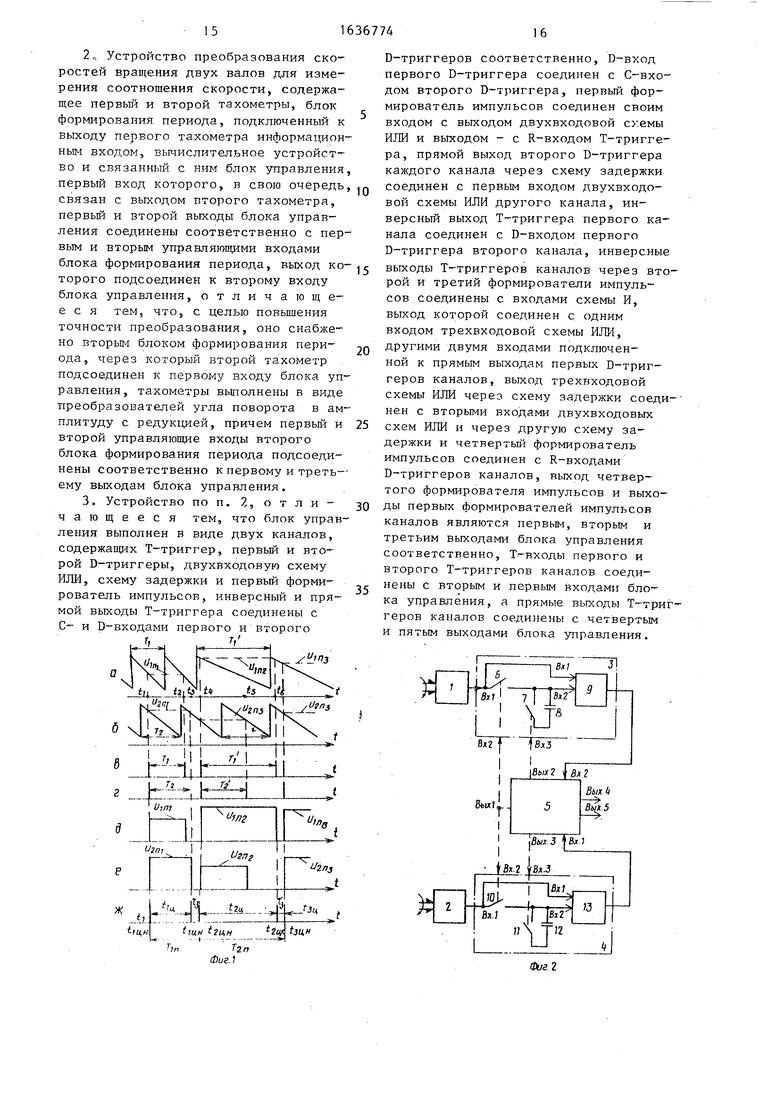

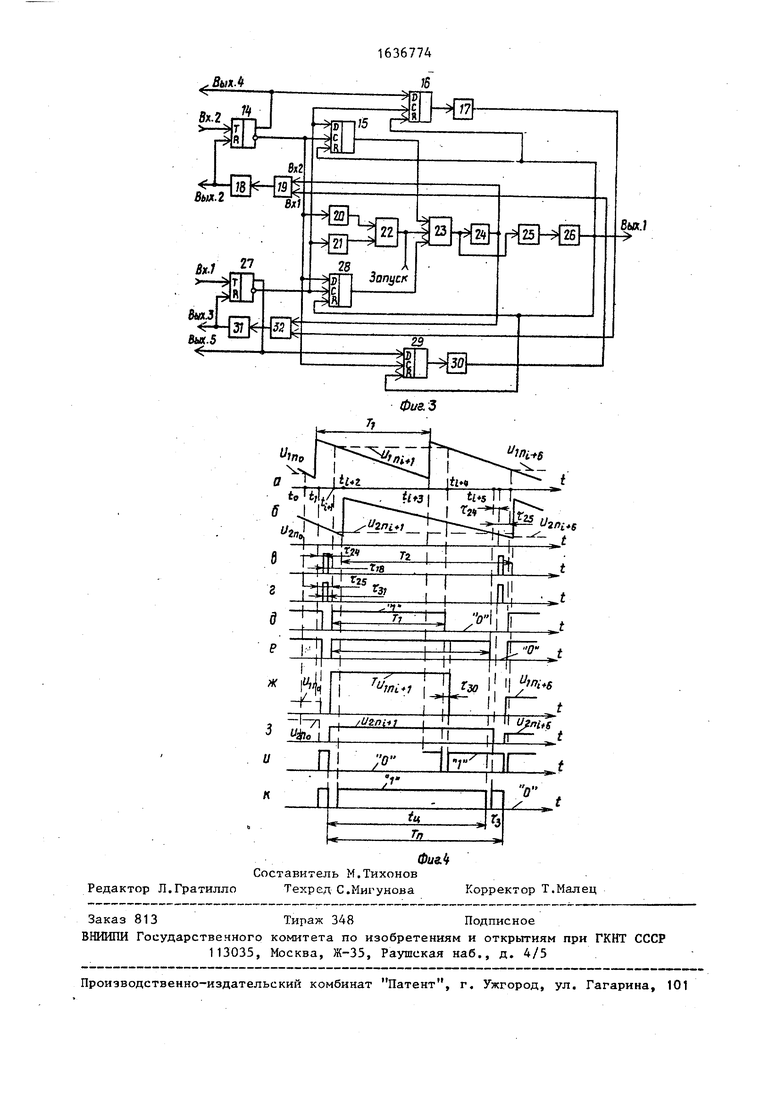

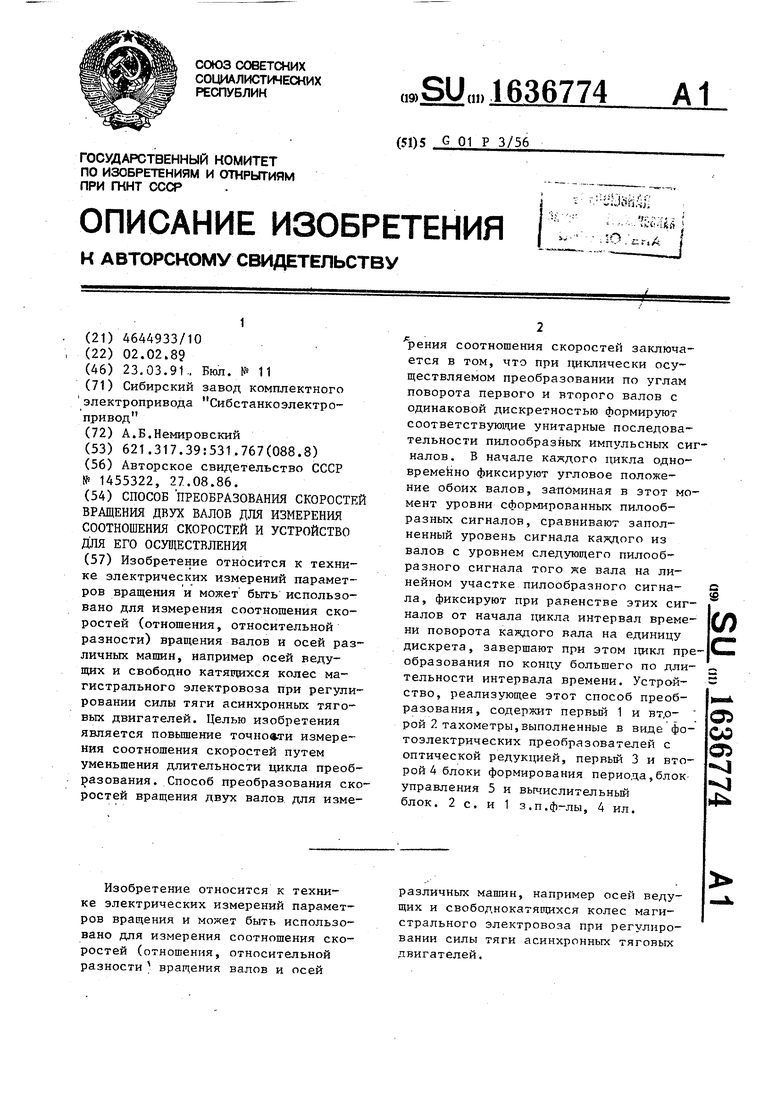

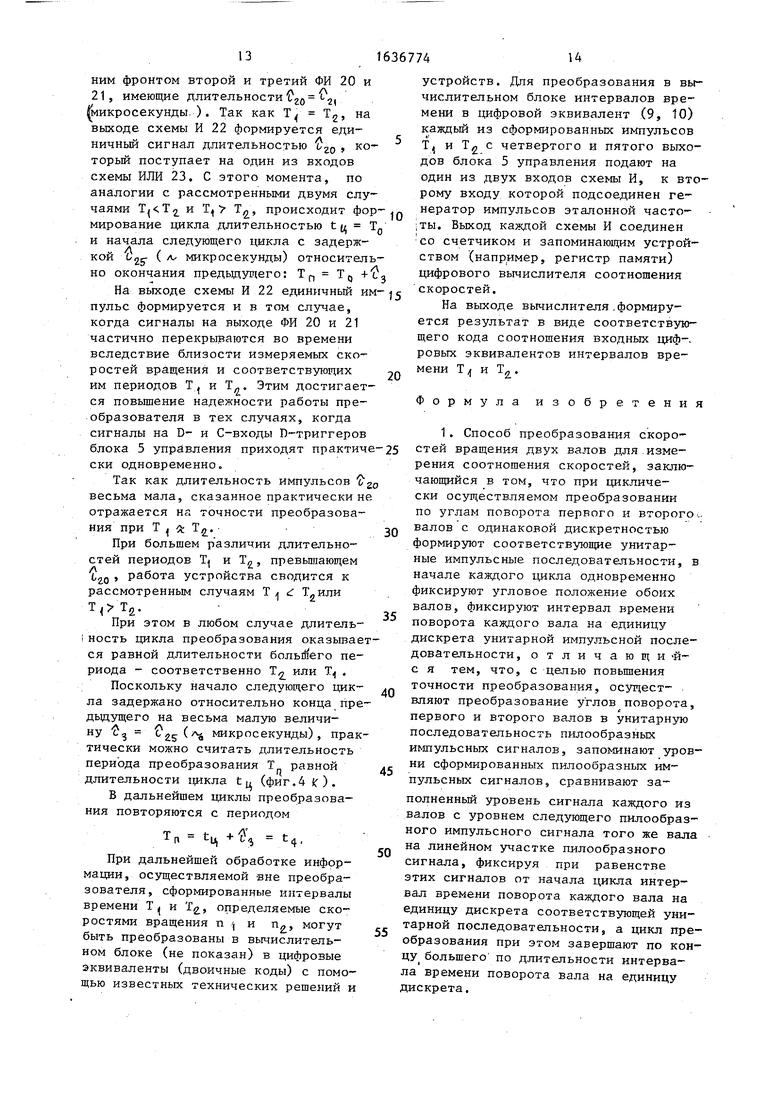

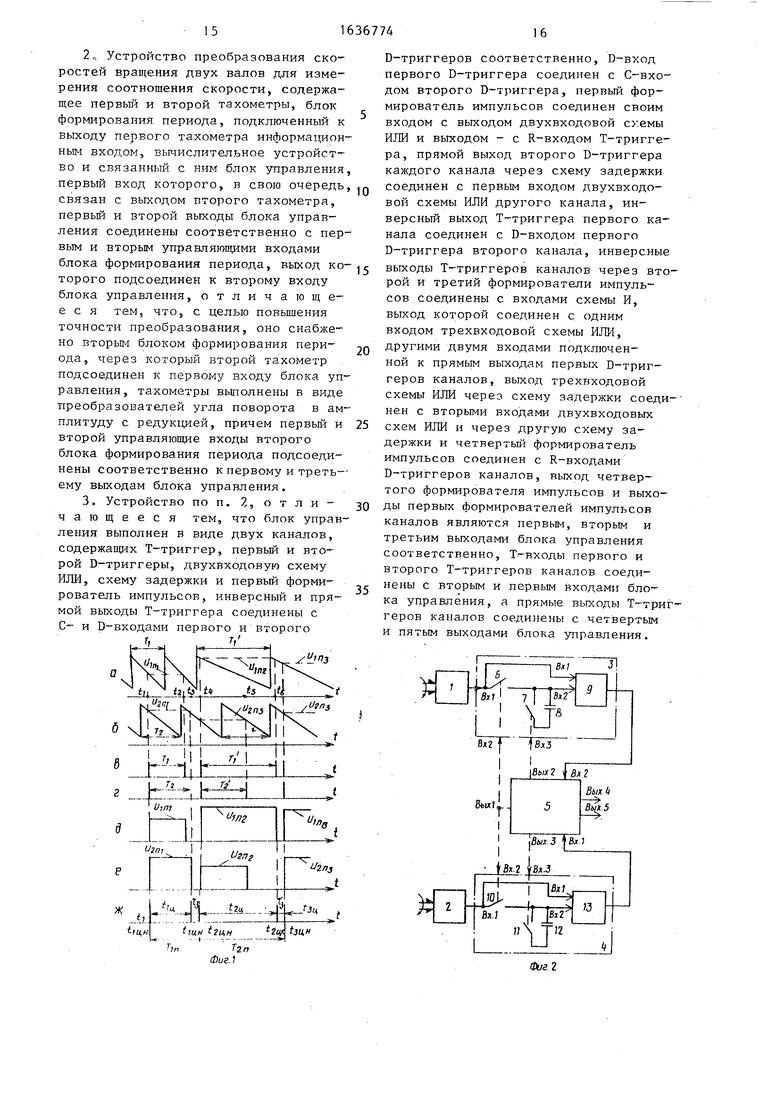

На фиг. 1 даны эпюры, поясняющие предлагаемый способ; на фиг. 2 - структурная схема устройства для реализации способа , на фиг. 3 - структурная схема блока управления уст- ройства для реализации способа1, на фиг. 4 - эпюры, поясняющие работу устройства.по предлагаемому способу.

На фиг. 1 даны следующие обозначения - 0,Ј - импульсные пилообразные сигналы, длительность которых обратно пропорциональна скоростям вращения первого и второго валов; о , 2 - импульсные отметки периодов, соответ ствующих сформированным пилообразным сигналам, ,6 - заполненные уровни напряжения, соответствующие периодам Т и То , Ж - импульсные отметки начала и конца цикла преобразования.

Согласно предлагаемому способу углы поворота обоих валов фиксируют унтарными кодами с равным весом кода. Унитарные коды первого и второго валов преобразуют в последовательности импульсных пилообразных сигналов (фиг.1 а ,&), длительности периодов повторения которых Т 4 и Тг определяюся редукцией М (числом импульсов на оборот вала( и средними на интерва лах измерения скоростями вращения n(t) n(t) соответственно

т. -

n.(t)M

л

Тг n.(t)M

На фиг. 1 показаны случаи нескольких циклов формирования сигналов при T|«i Tz (первый цикл преобразования) и Т,Т2 (второй цикл).

В начальный момент времени t , одновременно фиксируют угловое положение обоих валов путем формирования двух синфазных импульсных отметок (фиг.1 В ,), которые определяют начало цикла преобразования (момент t(U)p фиг.1Д ) и запоминают соответствующие уровни пилообразных сигналов и V чщ (Фиг-1 )- B про- цессе вращения валов фиксируют моменты поворота каждого вала на единицу унитарного кода. Это достигается

д

5 0 5

Q 5

0

5

05

путем сравнения запомненных уровней U ,|п/| и U2n/t c соответствующим участком следующего импульса пилообразного сигнала. В моменты t и t равенства запомненных уровней с пилообразными сигналами (фиг.1 о ,) формируют импульсные отметки периодов Т / и Т и сбрасывают на нуль запомненные напряжения )фиг.1 J,e). Затем сравнивают длительности периодов и формируют импульсную отметку t1L)) окончания цикла (фиг.1,)К) преобразования синфазно с отметкой большего периода Т2 (момент t.j, фиг.1 1).

После сбрасывания на нуль запомненного уровня (), соответствующего большему периоду (Т2), вновь формируют две синфазные отметки начала следующего цикла (момент t., фиг.1 В, 1} с фиксированной задержкой Ъ относительно отметки t и|1: окончания предыдущего цикла . Поскольку фиксированная задержка необходима лишь для сбрасывания на нуль запомненного уровня (U,), соответствующего большему периоду (Т), и является весьма малой по сравнению с Т (доли, единицы микросекунд), длительность периода цикла преобразования Т иопределяется длительностью наибольшего из двух сравниваемых периодов (фиг.1&).

В следующем цикле преобразования, начинающемся в момент t4 tzuu (фиг,), выполняется соотношение TJ Т. При этом длительность второго цикла преобразования определяется максимальной длительностью периода Т : t2 Т1, к Т2П,

Таким образом, предлагаемый способ преобразования скоростей вращения двух валов для измерения соотношения скоростей позволяет сократить длительность цикла преобразования до длительности большего формируемого периода и тем самым повысить точность измерения.

Устройство (фиг.2) содержит импульсные тахометры 1 и 2, сочлененные с двумя соответствующими валами, блоки 3 и 4 формирования периода (БФП и блок 5 управления. Выход тахометра 1 соединен с первым (информационным) входом первого ВФПЗ, подключенного выходом к второму.входу блока 5 управления. Выход тахометра 2 соединен с первым (информационным)j

входом второго БФП 4, подключенного выходом к первому входу блока 5 управления. Первый выход блока 5 управления соединен с вторыми входами (разрешения записи) 3 и 4, а второй и третий выходы соединены с третьими входами (сброса на нуль) БФП 3 и 4 соответственно. Четвертый и пятый выходы блока управления являются выходами устройства и соединены с входами вычислительного устройства (не показано) Импульсные тахометры 1 и 2 выполнены в виде преобразователей угол поворота - амплитуда с редукцией и предназначены для преобразования угла поворота соответствующего вала в напряжение

ивых h(t) + и где U,

выл А, К

oi(t)

ио

напряжение на выходе преобразователя ; нормирующие коэффициенты, угол поворота вала в зависимости от t в пределах единицы унитарного кода, опорное напряжение, необходимое для обеспечения возможности запоминания при минимальном значении пилообразного напряжения .

Величина UQ некритична к выбору плитуды и выбирается больше ширины зоны нечувствительности срабатывания компаратора 9„

Преобразователи импульсных тахометров 1 и 2 идентичны. Каждый из них выполнен в виде фотоэлектрического преобразователя с оптической редукцией М, содержит непрозрачный дис с нанесением на периферии М щелей (прорезей), источник излучения и разрезной фотоприемник, образующие считывающую оптопару. В качестве разрезного фотоприемника может быть использована, например, микросхема типа К849ПП2 (двухэлементное дифференциальное устройство), выполненная в виде усилительной микросхемы с входной фотодиодной площадкой, разрезанной по диагонали.

Расстояние между щелями на диске равно длине фотоприемника. Для согласования уровней сигналов на выходе фотоприемника может быть установлен усилитель. При равномерном вращении диска выходные сигналы фотоприем

10

5

20

5

5

0

0

5

0

5

ника имеют форму пилообразных сигналов, следующих с соответствующим , периодом повторения Т или Т,

Для формирования напряжения Ugb|X сигнал с выхода фотоприемника суммируется в преобразователе угла поворота с постоянным напряжением. При необходимости обеспечить U Вых в форме линейно-нарастающего пилообразного напряжения можно проинвертировать линейно спадающую пилу перед ее суммированием с постоянным напряжением, либо установить диаметрально противоположно другую считывающую оптопару с разрезным фотоприемником и подключить его выход к первому (второму) входу блока 5 управления.

БФП 3 и 4 идентичны и предназначены для формирования импульсных отметок длительности соответствующих периодов и Т.

Первый БФП 3 содержит схему выборки и запоминания (СВЗ), выполненную на ключах 6 и 7 и запоминающем конденсаторе 8. Ключи 6 и 7 реализуются на биполярных и МОП-транзисторах. Первый вход 1 БФП 3 соединен с входом ключа 6, соединенного выходом с входом ключа 7 и конденсатором 8. Выход ключа 7 соединен параллельно конденсатору 8.

СВЗ предназначена для формирования выборочного значения из входного аналогового (пилообразного) напряжения путем кратковременного стробирова- ния в момент появления сигнала на управляющем входе ключа 6 и запоминания напряжения на время периода с.тро- бирования. Ключ 6 СВЗ нормально разомкнут и служит для кратковременного подсоединения входного напряжения к запоминающему конденсатору 8 во время прихода стробирующего импульса на второй (управляющий) вход,т.е.является ключом разрешения записи.

Ключ 7 нормально разомкнут и предназначен для разряда конденсатора 8 в момент прихода кратковременного импульса на третий (управляющий) вход, осуществляя тем самым очистку памяти, тае, является ключом сброса на нуль.

Компаратор 9 служит для формирования .соответствующего перепада напряжений в момент равенства сигналов на его первом и втором входах, соединенных с входом ключа 6 и конденсатором 8 (входом и выходом СВЗ) о При UB)r U на выходе компаратора устанавливается 1, при Uex Uexe компаратор устанавливается в состояние О. Для повышения помехозащищенности компаратор может быть выполнен с гистерезисом.

Вход ключа 6, управляющие входы ключей 6 и 7 и выход компаратора 9 соединены с соответствующими первым вторым и третьим входами и выходом БФП 3.

БФП 4 идентичен по устройству БФП 3. СВЗ БФП 4 выполнен на ключах 10 и 11 и запоминающем конденсаторе 12. Первый вход БФП 4 соединен с входом ключа 10, соединенного выходом с входом ключа 11 и конденсатором 12. Выход ключа 11 соединен параллельно конденсатору 12. Ключи разрешения записи 10 и сброса на нуль 11 нормально разомкнуты.

Компаратор 13 аналогичен по назначению и выполнению компаратору 9. Его первый и второй входы соединены соответственно с входом ключа 1 0 - информационным первым входом БФП 4, и конденсатором 12.

Вход ключа 10, управляющие входы ключей 10 и 11 °и выход компаратора 13 соединены с соответствующими первым-третьим входами и выходом БФП 4.

Блок 5 управления предназначен для синхронизации и формирования импульсов разрешения записи, сброса на нуль в БФП 3 и 4, формирования длительностей временных интервалов Т и Т, определяемых соответствующими скоростями вращения, их сравнения и начального запуска всего устройства. Структурная схема блока 5 управления (фиг.3( содер- жит Т-триггеры 14 и 27, D-тригге- ры 15 и 16, 28 и 29, схемы задержки 17, 24, 25 и 30, формирователи 18, 20, 21, 26 и 31 импульсов, двухвходовые схемы ИЛИ 19 и 32, двух входовую схему И 22, трехвходовую схему ИЛИ 23.

Вход Запуска блока 5 управления соединен с выходом схемы И 22 и предназначен для однократного запуска устройства преобразователя от внешнего генератора импульса (не показан), Который может быть реализован в виде ждущего одновибрато- ра, запускаемого формирователем перепада напряжения от механического переключателя (кнопки). Формирова

5

0

5

0

5

0

5

тель может быть выполнен на основе RS-триггера с коммутируемыми на общую шину R- и S-входами (8).

Устройство работает следующим образом.

В установившемся режиме в характерных точках схемы устройства присутствуют сигналы (фиг.4), которые поясняют работу устройства: а, б - пилоообразные сигналы на выходе тахометров 1 и 2 в, г - импульсы на выходах ФИ 18 и ФИ 31 д. е- импульсы на прямых выходах Т-тригге- ров 14 и 27, ж, з - сигналы на выходе запоминающих конденсаторов 8 и 12 j и, к - сигналы на выходе компараторов 9 и 13.

В исходном состоянии (момент t0, фиг .4 а), соответствующем вращению со скоростями п и ng двух валов,с которы- ми сочленены тахометры 1 и 2, на их выходах формируется пилообразное напряжение U с периодами Т и Тг. Ключи 6 и 7, 10 и 11 разомкнуты. Напряжения на запоминающих конденсаторах 8 и 13 СВЗ БФП 3 и 4 U и Uj noсоответственно. Предположим, что триггеры 14-16, 27-29 находятся в единичном состоянии. На выходе компараторов 9 и 13 - уровень О.

Работу устройства рассмотрим в следующей последовательности: вначале рассмотрим преобразование двух скоростей вращения в соответствующие временные интервалы импульсов длительностью Т и Т , затем - последующую обработку сформированных интервалов времени, осуществляемую внешним вычислительным блоком, не относящимся к преобразователю.

При подаче в момент tj сигнала Запуск от внешнего генератора на

выходе схемы ИЛИ 23 формируется им 24

рез схемы ИЛИ 19 и 32 запускает первые формирователи 18 и 31 импульсов (фиг.4 6,). При этом Т-триггеры 14 и 27 по R-входам устанавливаются в Q исходное нулевое состояние (фиг.4й,9), Ключи 7 и 11 БФП 3 и 4 замыкаются на время с 1fi и Ј5 и тем самым сбрасывают на нуль запомненные на конденсаторах 8 и 12 уровни напряжений (фиг. 4 Ж, р. Так как напряжение на первых входах компараторов 19 и 13 становится больше, чем на втором входе (равно нулю), оба компаратора устанавливаются в состояние 1

(фиг.4 Ц, К). С задержкой времени tZ5 определяемой СЗ 25, в момент t t , запускается ФИ 26 j устанавливая в исходное нулевое состояние по R-вхо- дам D-триггеры 15 и 16, 28 и 29. Одновременно на первом выходе блока 5 управления формируется сигнал разрешения запоминания (записи), который кратковременно и синфазно замы- кает ключи 6 и 10 по вторым входам БФПЗи4. Происходит синфазное запоминание соответствующих уровней напряжения , и Ugn| f1Ha конденсаторах 8 и 12 (фиг. 4 % ,-р . Тем самым осуществляется одновременная фиксация углового положения обоих валов.

Компараторы 9 и 13 срабатывают и синфазно устанавливаются в состоя- ние О (фиг.4и,Х). Сформированные на их выходах перепады 1 - О устанавливают Т-триггеры 14 и 27 в состояние 1 (фиг.4 3 9е) . Тем самым осуществляется синфазное нача- ло формирования периодов Т( и Т. В моменты t-+iH t;+3pesKoro нарастания пилообразных напряжений сигналы на первом и втором входах компараторов 9 и 13 становятся кратко- временно больше запомненных уровней, что приводит к формированию 1 на выходах компараторов. Поскольку на перепады напряжения О - 1 триггеры 14 и 31 не срабатывают, они ос- таются в прежнем состоянии 1. При t 4, и пилообразные напряжения на соответствующих участках вновь становятся равными запомненным уровням. На выходе компараторов 9 и 13 формируются перепады 1 и О по которым Т-триггеры 14 и 27 устанавливаются в состояние О (фиг.4 0-,е) . Тем самым осуществляется фиксирование поворота обоих ва- лов на единицу унитарного кода. При этом на выходах триггеров 14 и 27 сформированы синфазные импульсы длительностью Т i и In, определяемой скоростями вращения п ,, и п „

Рассмотрим три возможных соотношения Т( и Тг, определяющих особенности работы блока 5 управления и формирования сигналов на его первом, втором и третьем выходах.

I. Т,,: Т (фиг.4 а ,5), т.е. импульс большей длительности формируется во втором канале блока 5 управления.

В этом случае получаем следующие соотношения между моментами прихода импульсных сигналов с инверсных и прямых выходов Т триггеров 14 и 27 на С и D-триггеры 15 и 16, 28 и 29:

fcci6 ЈС2в ься.9 и ЬР1 Чявг)

) .01

01

fcM5 T Т2

где t °1 - длительность нулевого уровня до момента возникновения единичного перепада. Неравенство означает, что сигнал записи информации в D-триггер 15 по С-входу приходит, когда на D-входе - О. Согласно принципу работы D-триг гера информация в него не запишется, на прямом выходе D-триггера 15 останется состояние О.

г0 - Т f ° - Т СС28 Lt 1Неравенство означает, что сигнал записи информации в D-триггер 28 по С-входу приходит, когда на D-входе 1. Поэтому информация в него запишется при t t-45- Т2 (фиг.4а ) На прямом выходе D-триггера 28 сформируется 1 при t Т2.

ю

JQ

-° т f. т Cet6 1i,

где t - длительность единичного

уровня до момента возникновения перепада от единицы к нулю.

Неравенство означает, что сигнал записи информации в D-триггер 16 по С-входу приходит, когда на D-вйрде - О. Поэтому информация в него не запишется, на первом выходе D-триггера 16 останется состояние О.

t°1 Т гг t10 - Т С29 М Св29 2

Неравенство означает, что сигнал записи информации в D-триггер 29 по С-входу приходит, когда на D-входе 1 . Поэтому информация в него запишется при t t2+4 T,. На прямом выходе D-триггера 29 сформируется 1.

Из приведенных соотношений видно, что формирование перепада 0й - t на прямых выходах первого и второго D-триггеров канала определяется следующим алгоритмом:

перепад формируется на прямом выходе первого D-триггера 28 при t TЈ , так как период Тг на выходе Т-триггера 27 этого канала больше Tj , 4

перепад О - 1 формируется на прямом выходе второго D-триггера 29 при t It, так как период TЈ на выходе Т-триггера 27 этого канала больше Т., .

Перепад О - 1 на прямом выходе D-триггера 28 является импульс- ной отметкой углового положения вала синфазной с импульсной отметкой максимального периода Т и образует импульсную отметку окончания цикла преобразования длительностью 1ц Тд. (фиг.4 к).

На этом заканчивается формирование длительности t цикла преобразования, равной длительности максимального периода Т на выходе Т-триг гера 27 (фиг.4 е).

Сформированный на прямом выходе D-триггера 29 сигнал 1 (при t t , +4) через схему 30 задержки, ИЛИ 19, ФИ 18 поступает на второй вы ход блока 5 управления и третий вход БФП 3. Происходит кратковременное замыкание ключа 7 на с/«и сброс на нуль при + ,„ запомненного на iконденсаторе 8 уровня напряжения Uinj + ( (фиг.4 ж). При этом напряжение UBX| становится больше UBxa на выходе компаратора 9 и на его выходе формируется 1 (фиг.4и).

Сформированный на прямом выходе D-триггера 28 (при ) сигнал 1 через схему ИЛИ 23, СЗ 24, ИЛИ 19 и 32 поступает на входы ФИ 18 и ФИ 31 с задержкой ,относительно и затем - на вторые и третьи выходы блока 5 управления и связанные с ними третьи входы БФП 3 и 4. Ключи 7 и 11 кратковременно замыкаются на время и Ј соответственно. Напряжение на кон- денсаторе 8 сброшено на нуль при fc 144 Ъо ПоэтомУ в момент t-+5.+ + Ј,4. происходит на нуль только уровня конденсаторе 12 (фиг о 4 «J. ) „ При этом напряжение UB)« становится больше на входе компаратора 13 и на его выходе формируется 1 (фиг.4к).

С выхода схемы ИЛИ 23 сформированный на прямом выходе D-триггера сигнал 1 через СЗ 25 и ФИ 26 поступает на R-входы триггеров 15 и 16, 28 и 29, устанавливая их в начальное состояние О, и с первого

выхода блока 5 управления - на вторые входы БФП 3 и 4. Ключи 6 и 10 кратковременно (на Сгб) синфазно замыкаются при t t«4gs осуществляя с задержкой (-25 (относительно ЁЦ) запоминание уровней Uw;f на конденсаторах 8 и 12 (фиг.4 k ,О

На этом заканчивается формирование периода преобразования, длительность которого Тп определяется длительностью максимального периода Т& и отличается от длительности цикла преобразования t ц на время задержки Ј2 ($иг1 & и 4 к. ) : Тп Т2 +0, Тг +Ј2S t4 + .

С момента начинается новый цикл преобразования, аналогичный Описанному при внешнем запуске (t tti+.), который задержан относительно конца предыдущего цикла на 25 (л- мгкросекунды) .

II., т.е. импульс большей длительности формируется в первом канале блока 5 управления.

Так как оба канала блока 5 управления полностью симметричны, учитывая изложенный алгоритм формирования перепадов О - 1 на прямых выходах D-триггеров каналов, получим:

перепад О - 1 формируется на прямом выходе первого D-триггера 15 при t tv, + Т., так как период Т, на выходе Т-триггера 14 данного канала больше Т

перепад О - 1 формируется на прямом выходе второго D-триггера 16 при t t, +, + Т, так как период Т на выходе Т-триггера 14 данного канала больше Т2. Поскольку дальнейшее прохождение сформированного перепада О - 1, начиная с выхода схемы ИЛИ 23, одинаково и не зависит от того, на какой из входов схемы ИЛИ 23 поступил входной сигнал, длительность цикла преобразования tц равна длительности большего периода Т,. Аналогично осуществляется переход к новому циклу преобразования, задержанному относительно конца предыдущего цикла Havi5( микросекунды): Тр Т{ + Ј3

III.Т Т2 Т0, т.е. в обоих каналах блока 5 управления формируются импульсы одинаковой длительности.

Сформированные на выходах Т-триг- геров 14 и 27 импульсы запускают задним фронтом второй и третий ФИ 20 и 21, имеющие длительности Сго микросекунды ) . Так как Т Т2, на выходе схемы И 22 формируется единичный сигнал длительностью Јzo, который поступает на один из входов схемы ИЛИ 23. С этого момента, по аналогии с рассмотренными двумя случаями Т{.ТЈ И Т| Т, ПРОИСХОДИТ фор-

мирование цикла длительностью t Т0 и начала следующего цикла с задержкой с/25- ( /v- микросекунды) относительно окончания предыдущего: Тп Т0 +с3

На выходе схемы И 22 единичный импульс формируется и в том случае, когда сигналы на выходе ФИ 20 и 21 частично перекрываются во времени вследствие близости измеряемых скоростей вращения и соответствующих им периодов Т, и Т. Этим достигается повышение надежности работы преобразователя в тех случаях, когда сигналы на D- и С-входы П-триггеров блока 5 управления приходят практически одновременно.

Так как длительность импульсов Ј2о весьма мала, сказанное практически не отражается на точности преобразования при Т к Т.

При большем различии длительностей периодов Tf и Т, превышающем 20, работа устройства сводится к рассмотренным случаям Т L Т2или

.

При этом в любом случае длитель- iность цикла преобразования оказывается равной длительности большего периода - соответственно Т или Т .

Поскольку начало следующего цик- ла задержано относительно конца предыдущего на весьма малую величину Ј z.s микР°секУнДы) практически можно считать длительность периода преобразования Т равной длительности цикла t ц (фиг.4 К) .

В дальнейшем циклы преобразования повторяются с периодом

Т„ t,

Я.

-Ч

t,

При дальнейшей обработке информации, осуществляемой вне преобразователя, сформированные интервалы времени Т и Тг, определяемые скоростями вращения п /, и Пд, могут быть преобразованы в вычислительном блоке (не показан) в цифровые эквиваленты (двоичные коды) с помощью известных технических решений и

JQ

75 0 5

0

5

д

0

устройств. Для преобразования в вычислительном блоке интервалов времени в цифровой эквивалент (9, 10) каждый из сформированных импульсов Т, и Т2 с четвертого и пятого выходов блока 5 управления подают на один из двух входов схемы И, к второму входу которой подсоединен генератор импульсов эталонной частоты. Выход каждой схемы И соединен со счетчиком и запоминающим устройством (например, регистр памяти) цифрового вычислителя соотношения скоростей.

На выходе вычислителя формируется результат в виде соответствующего кода соотношения входных цифровых эквивалентов интервалов времени Т и Т .

Формула изобретения

1. Способ преобразования скоростей вращения двух валов для измерения соотношения скоростей, заключающийся в том, что при циклически осуществляемом преобразовании по углам поворота первого и второго валов с одинаковой дискретностью формируют соответствующие унитарные импульсные последовательности, в начале каждого цикла одновременно фиксируют угловое положение обоих валов, фиксируют интервал времени поворота каждого вала на единицу дискрета унитарной импульсной последовательности, отличающи -и- с я тем, что, с целью повышения точности преобразования, осуществляют преобразование углов поворота, первого и второго валов в унитарную последовательность пилообразных импульсных сигналов, запоминают уровни сформированных пилообразных импульсных сигналов, сравнивают заполненный уровень сигнала каждого из валов с уровнем следующего пилообразного импульсного сигнала того же вала на линейном участке пилообразного сигнала, фиксируя при равенстве этих сигналов от начала цикла интервал времени поворота каждого вала на единицу дискрета соответствующей унитарной последовательности, а цикл преобразования при этом завершают по концу большего по длительности интервала времени поворота вала на единицу дискрета.

2„ Устройство преобразования скоростей вращения двух валов для измерения соотношения скорости, содержащее первый и второй тахометры, блок формирования периода, подключенный к выходу первого тахометра информационным входом, вычислительное устройство и связанный с ним блок управления, первый вход которого, в свою очередь, связан с выходом второго тахометра, первьй и второй выходы блока управления соединены соответственно с первым и вторым управляющими входами блока формирования периода, выход которого подсоединен к второму входу блока управления, отличающееся тем, что, с целью повышения точности преобразования, оно снабжено вторым блоком формирования периода, через который второй тахометр подсоединен к первому входу блока управления, тахометры выполнены в виде преобразователей угла поворота в амплитуду с редукцией, причем первый и второй управляющие входы второго блока формирования периода подсоединены соответственно к первому и треть-- ему выходам блока управления.

3, Устройство по п. 2, о т л и

чающееся тем, что блок управления выполнен в виде двух каналов, содержащих Т-триггер, первый и второй D-триггеры, двухвходовую схему ИЛИ, схему задержки и первый формирователь импульсов, инверсный и прямой выходы Т-триггера соединены с С- и D-входами первого и второго г, V

-WME-

S.3

lLML-

KlrJrfH1

& //. .«-,-

с

0

5

0

5

D-триггеров соответственно, D-вход первого D-триггера соединен с С-вхо- дом второго D-триггера, первый формирователь импульсов соединен своим входом с выходом двухвходовой схемы ИЛИ и выходом - с R-входом Т-триггера, прямой выход второго D-триггера каждого канала через схему задержки соединен с первым входом двухвходовой схемы ИЛИ другого канала, инверсный выход Т-триггера первого канала соединен с D-входом первого D-триггера второго канала, инверсные

выходы Т-триггеров каналов через второй и третий формирователи импульсов соединены с входами схемы И, выход которой соединен с одним входом трехвходовой схемы ИЛИ, другими двумя входами подключенной к прямым выходам первых D-триггеров каналов, выход трехвходовой схемы ИЛИ через схему задержки соединен с вторыми входами двухвходовых схем ИЛИ и через другую схему задержки и четвертый формирователь импульсов соединен с R-входами D-триггеров каналов, выход четвертого формирователя импульсов и выходы первых формирователей импульсов каналов являются первым, вторым и третьим выходами блока управления соответственно, Т-входы первого и второго Т-триггеров каналов соединены с вторым и первым входами блока управления, а прямые выходы Т-триггеров каналов соединены с четвертым и пятым выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения относительной разности скоростей вращения | 1986 |

|

SU1455322A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Устройство для измерения скорости вращения вала | 1986 |

|

SU1315904A1 |

| Способ определения скорости вращения вала | 1989 |

|

SU1700482A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| Преобразователь угла поворота вала в длительность импульсов | 1982 |

|

SU1035628A2 |

| Преобразователь кода в скорость вращения вала | 1988 |

|

SU1599991A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1293842A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В НАПРЯЖЕНИЕ | 1987 |

|

RU2056700C1 |

Изобретение относится к технике электрических измерений параметров вращения и может быть использовано для измерения соотношения скоростей (отношения, относительной разности) вращения валов и осей различных машин, например осей ведущих и свободно катящихся колес магистрального электровоза при регулировании силы тяги асинхронных тяговых двигателей. Целью изобретения является повышение точности измерения соотношения скоростей путем уменьшения длительности цикла преобразования. Способ преобразования скоростей вращения двух валов для изме рения соотношения скоростей заключается в том, что при циклически осуществляемом преобразовании по углам поворота первого и второго валов с одинаковой дискретностью формируют соответствующие унитарные последовательности пилообразных импульсных сигналов. В начале каждого цикла одновременно фиксируют угловое положение обоих валов, запоминая в этот момент уровни сформированных пилообразных сигналов, сравнивают заполненный уровень сигнала каждого из валов с уровнем следующего пилообразного сигнала того же вала на линейном участке пилообразного сигнала, фиксируют при равенстве этих сигналов от начала цикла интервал времени поворота каждого вала на единицу дискрета, завершают при этом цикл преобразования по концу большего по длительности интервала времени. Устройство, реализующее этот способ преобразования, содержит первый 1 и вт.о- рой 2 тахометры,выполненные в виде фотоэлектрических преобразователей с оптической редукцией, первый 3 и второй 4 блоки формирования периода,блок управления 5 и вычислительный блок. 2 с. и 1 з.п.ф-лы, 4 ил. с Ј (Л ОЭ СО 05 -4 4

| Устройство для измерения относительной разности скоростей вращения | 1986 |

|

SU1455322A1 |

Авторы

Даты

1991-03-23—Публикация

1989-02-02—Подача