1

(210 4639592/24

(22) 19,01.89

(46) 23.03.91.БКШ. № 11

(71)Сибирский металлургический ин- 1ститут им.Серго Орджоникидзе

(72)Г.В,Мельник, Н.А.Калиногорский, С.В.Коршиков, В.И.Котунов, Ю.А.Шерышев В.П.Туманов

и А.Н.Чурилов

(53)62-50 (088.8)

(56) Авторское свидетельство СССР № 451056, кл. G 05 В 53/00, 1972.

Авторское свидетельство СССР № 1190362, кл. G 05 В 13/00, 1984.

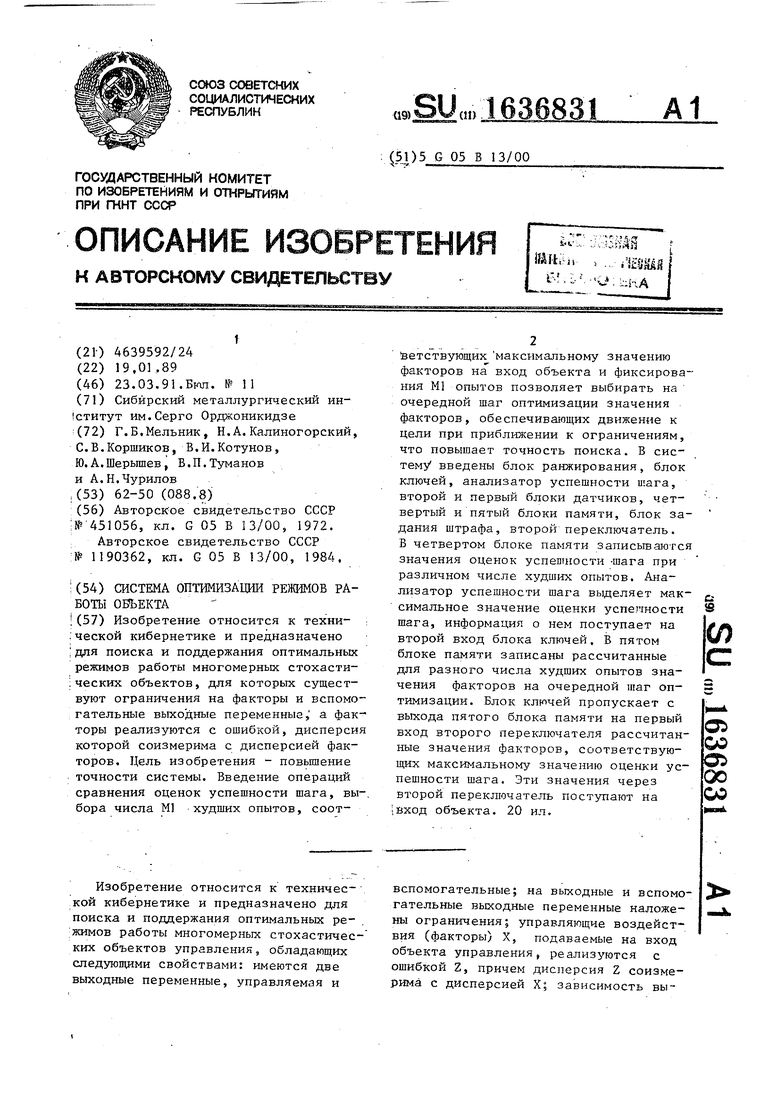

(54)СИСТЕМА ОПТИМИЗАЦИИ РЕЖИМОВ РАБОТЫ ОБЪЕКТА

1 (57) Изобретение относится к технической кибернетике и предназначено

для поиска и поддержания оптимальных режимов работы многомерных стохастических объектов, для которых существуют ограничения на факторы и вспомогательные выходные переменные, а факторы реализуются с ошибкой, дисперсия которой соизмерима с дисперсией факторов. Цель изобретения - повышение точности системы. Введение операций сравнения оценок успешности шага, выбора числа Ml худших опытов, соответствующих максимальному значению факторов на вход объекта и фиксирования Ml опытов позволяет выбирать на очередной шаг оптимизации значения факторов, обеспечивающих движение к цели при приближении к ограничениям, что повышает точность поиска. В систему1 введены блок ранжирования, блок ключей, анализатор успешности шага, второй и первый блоки датчиков, четвертый и пятый блоки памяти, блок задания штрафа, второй переключатель. В четвертом блоке памяти записываются значения оценок успешности -шага при различном числе худших опытов. Анализатор успешности шага выделяет максимальное значение оценки успепности шага, информация о нем поступает на второй вход блока ключей, В пятом блоке памяти записаны рассчитанные для разного числа худших опытов значения факторов на очередной шаг оптимизации. Блок ключей пропускает с выхода пятого блока памяти на первый вход второго переключателя рассчитанные значения факторов, соответствующих максимальному значению оценки успешности шага. Эти значения через второй переключатель поступают на вход объекта. 20 ил.

S

(Л

оъ &о о оо со

| название | год | авторы | номер документа |

|---|---|---|---|

| Система оптимизации режимов работы объекта | 1985 |

|

SU1287103A1 |

| Устройство контроля | 1985 |

|

SU1291931A1 |

| Система оптимизации режимов работы объекта | 1985 |

|

SU1260916A1 |

| АДАПТИВНАЯ СИСТЕМА РЕГУЛИРОВАНИЯ ПРОЦЕССА КОНТРОЛЯ НА МЕТАЛЛОРЕЖУЩЕМ СТАНКЕ | 1990 |

|

RU2042168C1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| Система оптимизации режимов работы объекта | 1984 |

|

SU1190362A1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| СИСТЕМА ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ПРОДАЖИ ТОВАРОВ | 1999 |

|

RU2168762C2 |

| Аналого-дискретный анализатор спектра | 1978 |

|

SU734740A1 |

| Система автоматической оптимизации | 1986 |

|

SU1310773A1 |

Изобретение относится к технической кибернетике и предназначено для поиска и поддержания оптимальных режимов работы многомерных стохастических объектов управления, обладающих следующими свойствами: имеются две выходные переменные, управляемая и

вспомогательные; на выходные и вспомогательные выходные переменные наложены ограничения; управляющие воздействия (факторы) X, подаваемые на вход объекта управления, реализуются с ошибкой Z, причем дисперсия Z соизмерима с дисперсией X; зависимость вы

Годных переменных от входных неизвестна.

Цель изобретения - повышение точности системы.j

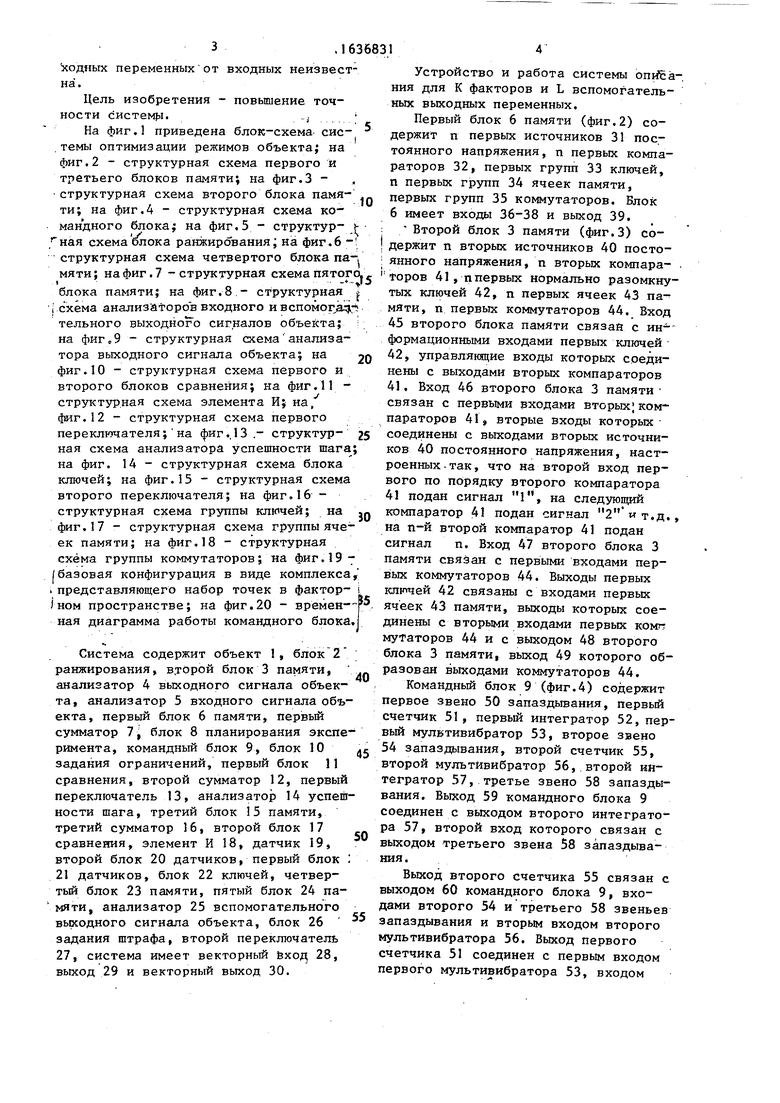

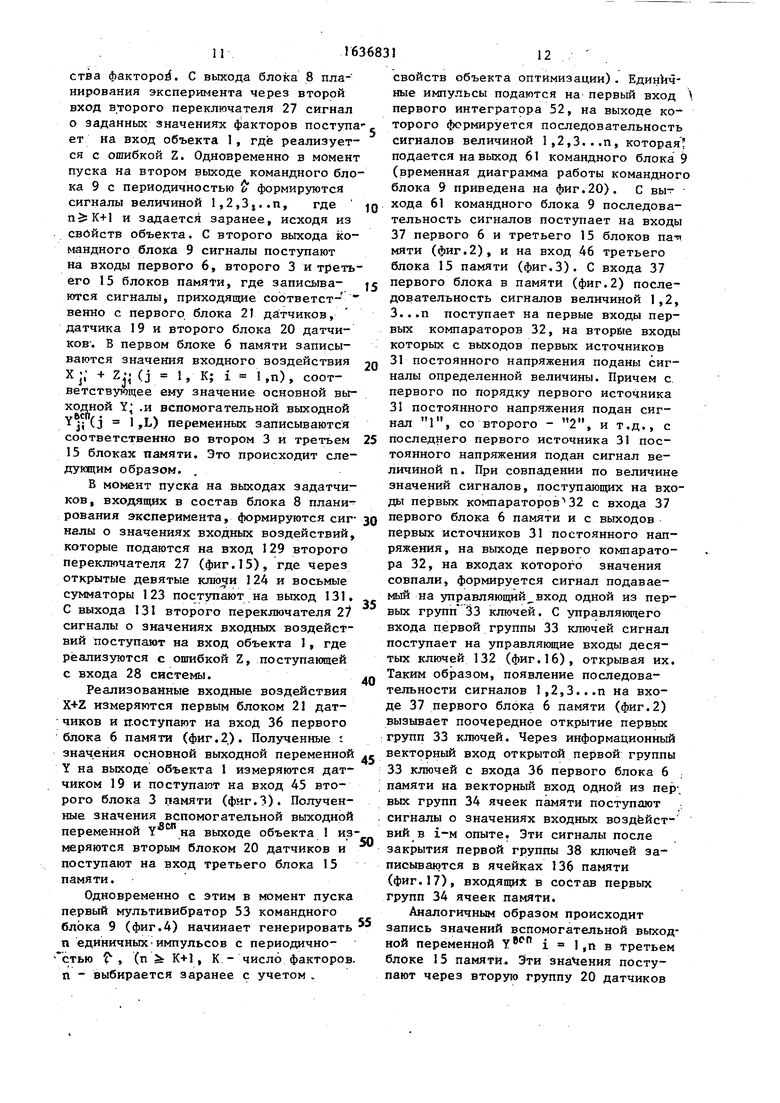

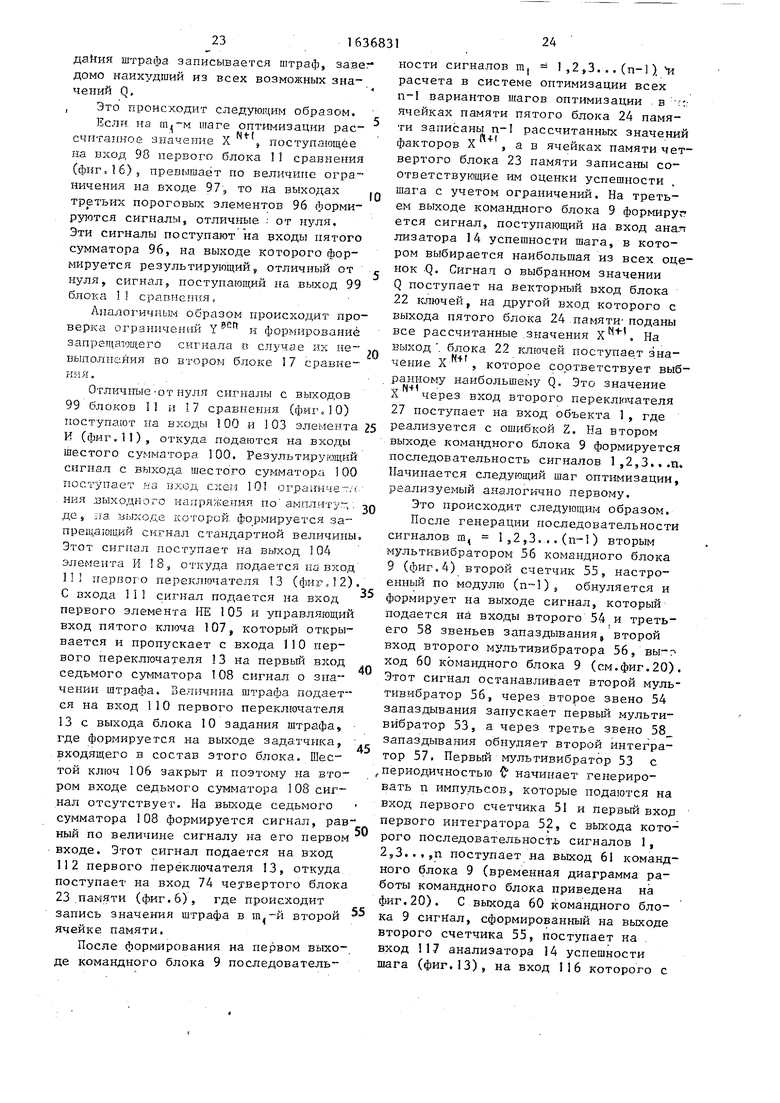

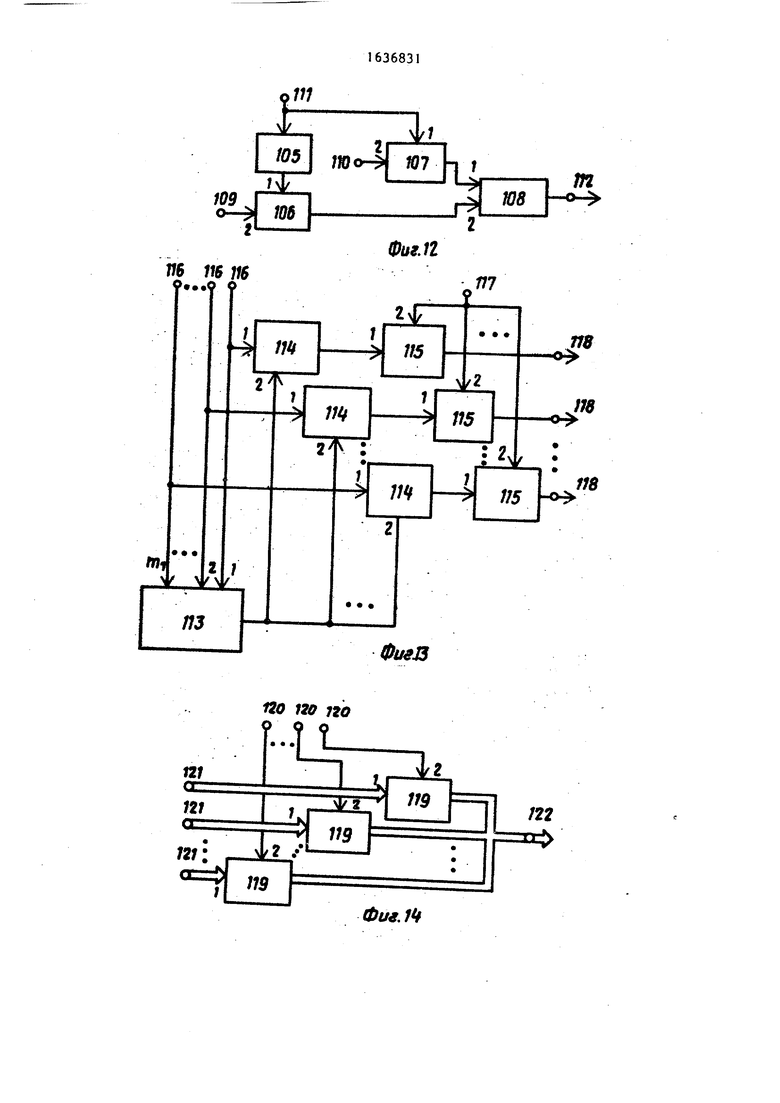

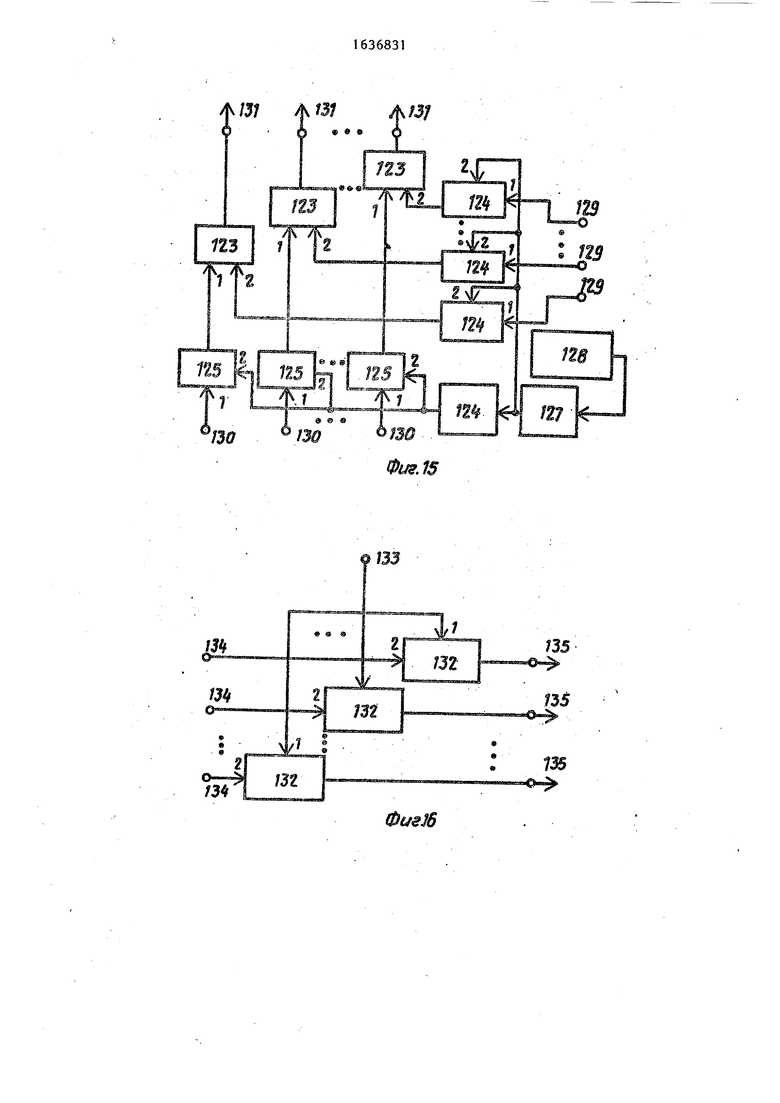

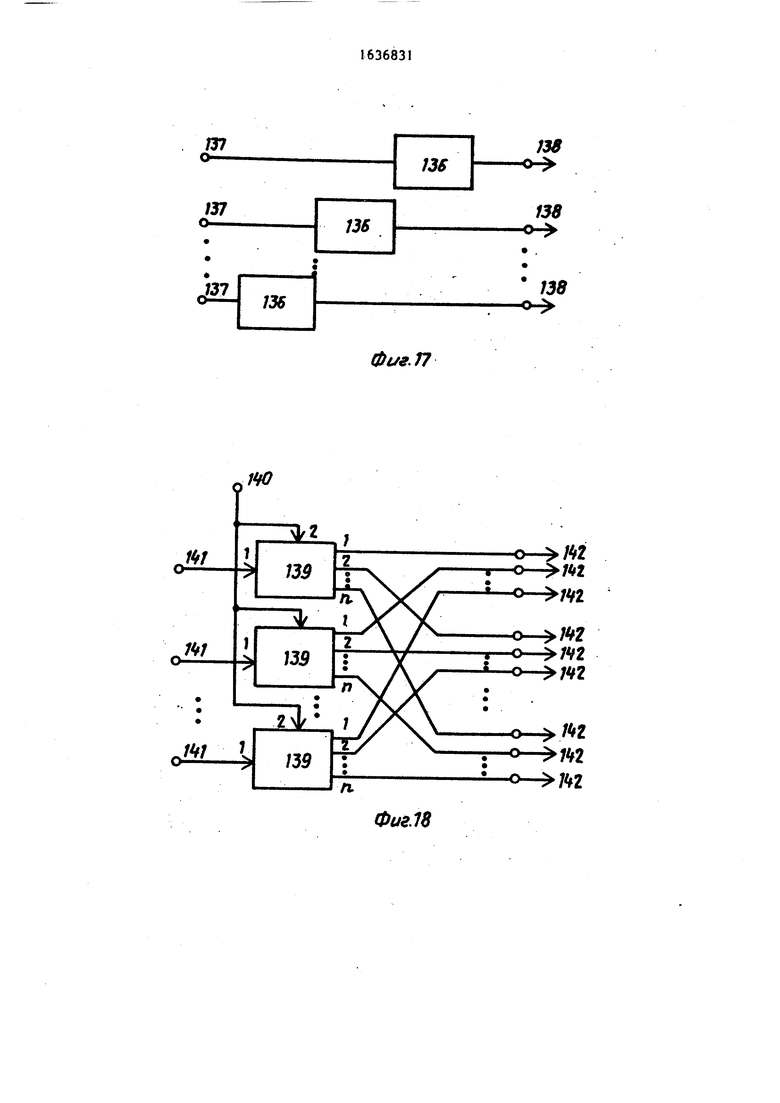

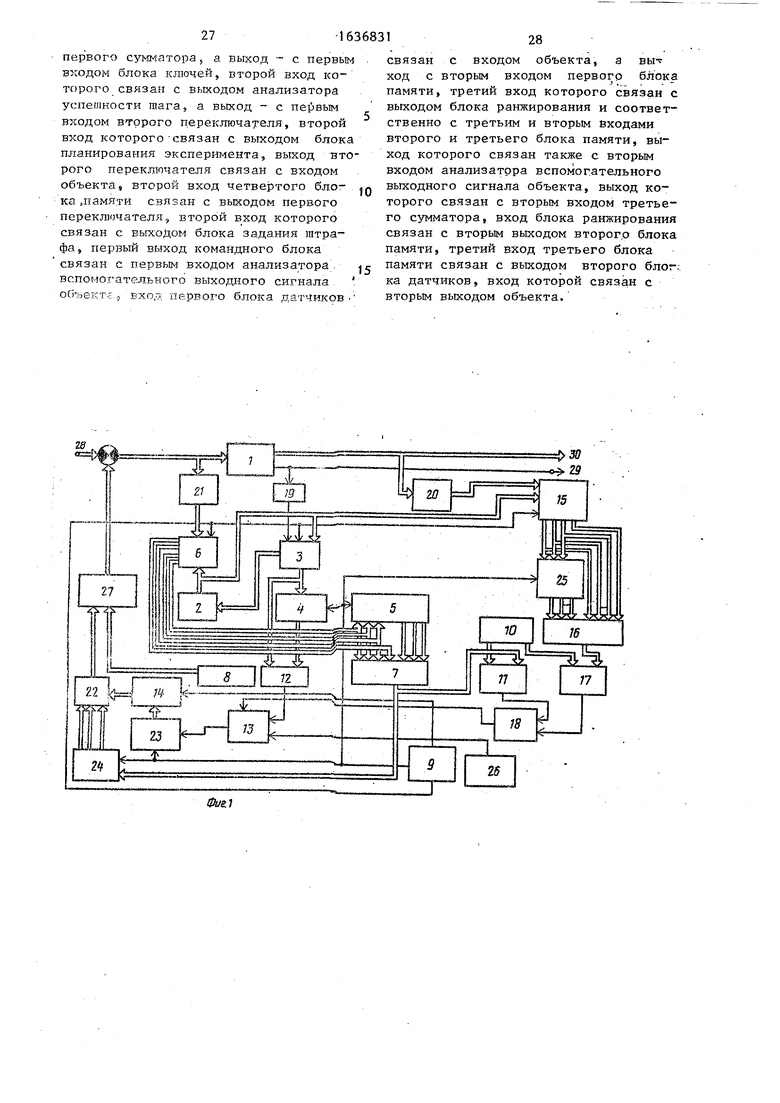

На фиг.1 приведена блок-схема сие- темы оптимизации режимов объекта; на фиг.2 - структурная схема первого и третьего блоков памяти; на фиг.З - „ структурная схема второго блока памяти; на фиг.4 - структурная схема командного блока; на фиг.З - структур- { гная схема блока ранжирования; на фиг. 6 - структурная схема четвертого блока па-.

10

Устройство и работа системы onrfea- ния для К факторов и L вспомогательных выходных переменных.

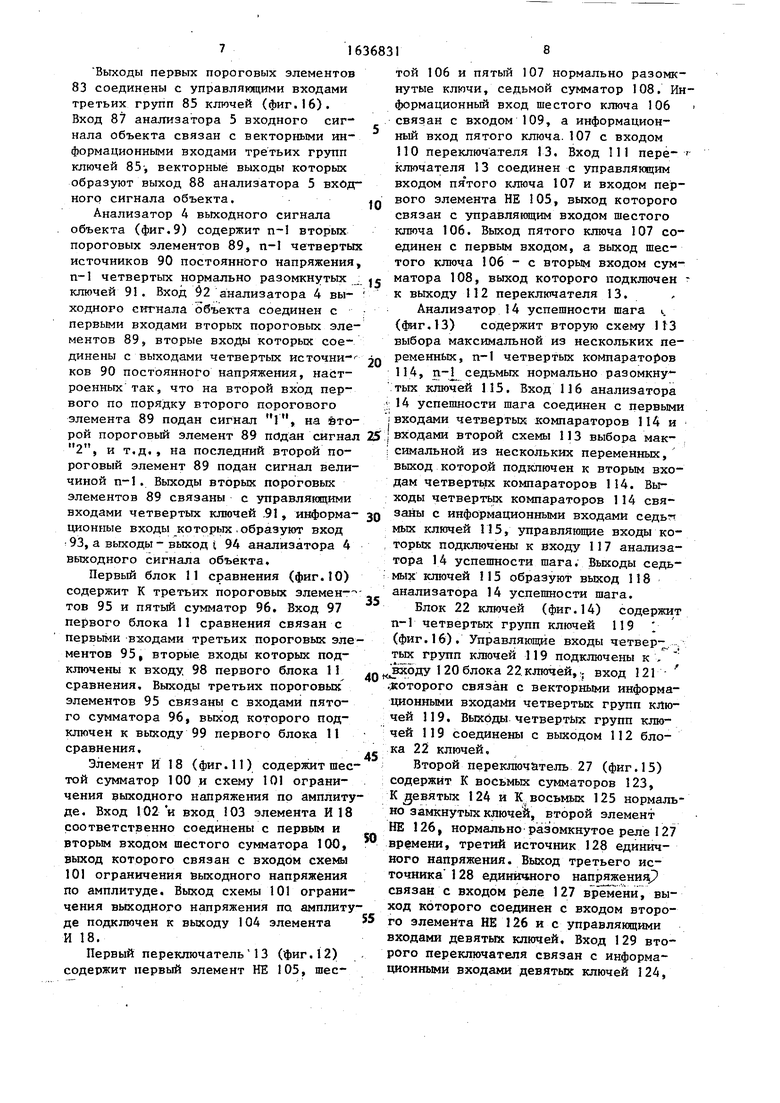

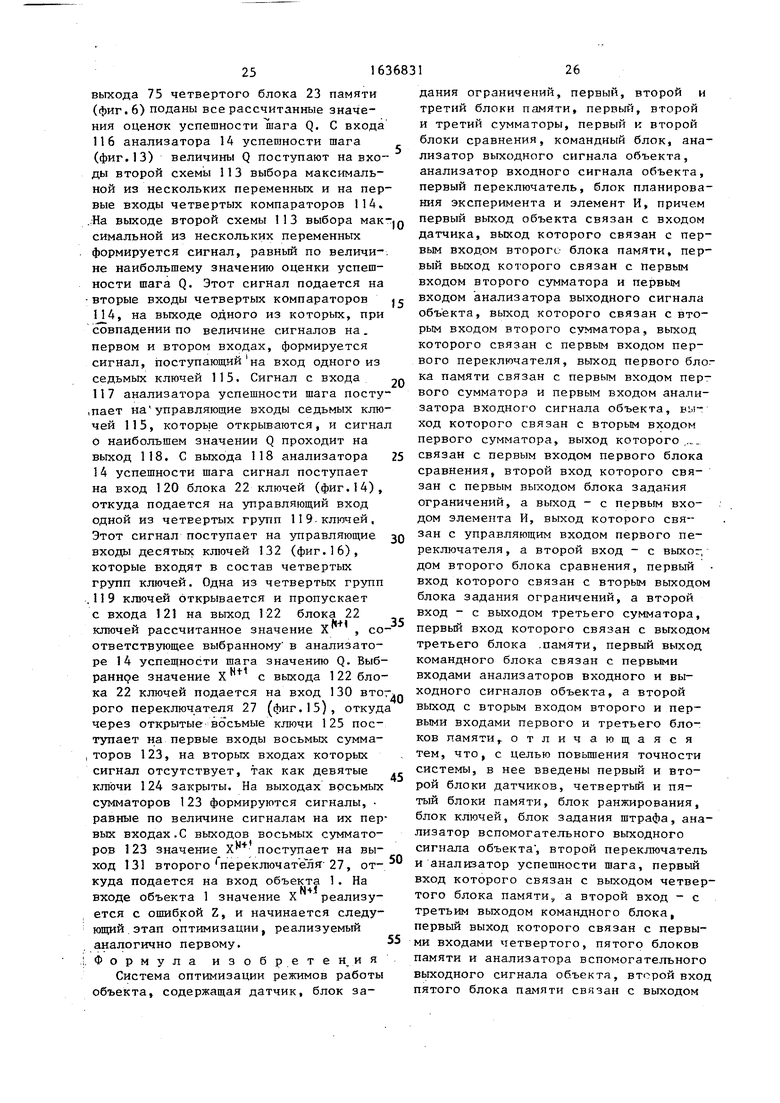

Первый блок 6 памяти (фиг.2) содержит п первых источников 31 постоянного напряжения, п первых компараторов 32, первых групп 33 ключей, п первых групп 34 ячеек памяти, первых групп 35 коммутаторов. Блок 6 имеет входы 36-38 и выход 39.

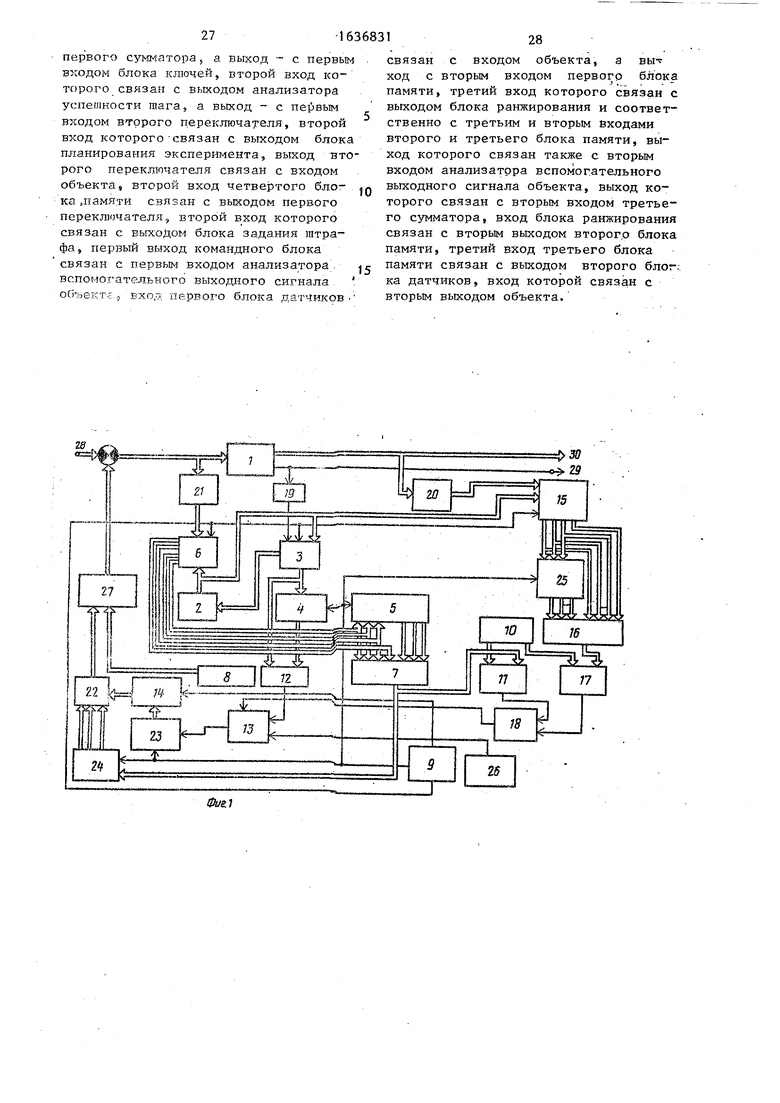

Второй блок 3 памяти (фиг.З) содержит п вторых источников 40 постоянного напряжения, п вторых компара(мяти; на фиг. 7 - структурная схема пятого, 5 i торов 4 , п первых нормально разомкнублока памяти; на фиг.8 - структурная I I схема анализаторов входного ивспомогд тельного выходного сигналов объекта; на фиг„9 - структурная схема анализатора выходного сигнала объекта; на эп фиг.10- структурная схема первого и второго блоков сравнения; на фиг.11 - структурная схема элемента И; на/ фиг.12 - структурная схема первого переключателя; на фиг.. 13 .- структур- 25 ная схема анализатора успешности шага; на фиг. 14 - структурная схема блока ключей; на фиг.15 - структурная схема второго переключателя; на фиг.16 - структурная схема группы ключей; на ,- фиг.17 - структурная схема группы ячеек памяти; на фиг.18 - структурная схема группы коммутаторов; на фиг.19 - |базовая конфигурация в виде комплекса, представляющего набор точек в фактор- i )ном пространстве; на фиг.20 - времен-Р ная диаграмма работы командного блока.

тых ключей 42, п первых ячеек 43 памяти, п первых коммутаторов 44. Вход 45 второго блока памяти связан с ин- формационными входами первых ключей 42, управляющие входы которых соединены с выходами вторых компараторов 41, Вход 46 второго блока 3 памяти связан с первыми входами вторых; компараторов 41, вторые входы которых соединены с выходами вторых источников 40 постоянного напряжения, настроенных - так, что на второй вход первого по порядку второго компаратора 41 подан сигнал 1, на следующий

компаратор 41 подан сигнал 2 и т.д., на n-й второй компаратор 41 подан сигнал п. Вход 47 второго блока 3 памяти связан с первыми входами первых коммутаторов 44. Выходы первых ключей 42 связаны с входами первых ячеек 43 памяти, выходы которых соединены с вторыми входами первых комг мутаторов 44 и с выходом 48 второго блока 3 памяти, выход 49 которого образован выходами коммутаторов 44.

Система содержит объект 1, блок 2 ранжирования, второй блок 3 памяти, .ft анализатор 4 выходного сигнала объекта, анализатор 5 входного сигнала объекта, первый блок 6 памяти, первый сумматор 7, блок 8 планирования эксперимента, командный блок 9, блок 10 задания ограничений, первый блок 11 сравнения, второй сумматор 12, первый переключатель 13, анализатор 14 успешности шага, третий блок 15 памяти, третий сумматор 16, второй блок 17 сравнения, элемент И 18, датчик 19, второй блок 20 датчиков, первый блок 21 датчиков, блок 22 ключей, четвертый блок 23 памяти, пятый блок 24 памяти, анализатор 25 вспомогательного выходного сигнала объекта, блок 26 задания штрафа, второй переключатель 27, система имеет векторный вход 28, выход 29 и векторный выход 30.

50

.с

55

Устройство и работа системы onrfea- ния для К факторов и L вспомогательных выходных переменных.

Первый блок 6 памяти (фиг.2) содержит п первых источников 31 постоянного напряжения, п первых компараторов 32, первых групп 33 ключей, п первых групп 34 ячеек памяти, первых групп 35 коммутаторов. Блок 6 имеет входы 36-38 и выход 39.

Второй блок 3 памяти (фиг.З) содержит п вторых источников 40 постоянного напряжения, п вторых компараi торов 4 , п первых нормально разомкну, 5 i торов 4 , п первых нормально разомкнуIэп 25 ,- i Р

.ft 50

тых ключей 42, п первых ячеек 43 памяти, п первых коммутаторов 44. Вход 45 второго блока памяти связан с ин- формационными входами первых ключей 42, управляющие входы которых соединены с выходами вторых компараторов 41, Вход 46 второго блока 3 памяти связан с первыми входами вторых; компараторов 41, вторые входы которых соединены с выходами вторых источников 40 постоянного напряжения, настроенных - так, что на второй вход первого по порядку второго компаратора 41 подан сигнал 1, на следующий

компаратор 41 подан сигнал 2 и т.д., на n-й второй компаратор 41 подан сигнал п. Вход 47 второго блока 3 памяти связан с первыми входами первых коммутаторов 44. Выходы первых ключей 42 связаны с входами первых ячеек 43 памяти, выходы которых соединены с вторыми входами первых комг мутаторов 44 и с выходом 48 второго блока 3 памяти, выход 49 которого образован выходами коммутаторов 44.

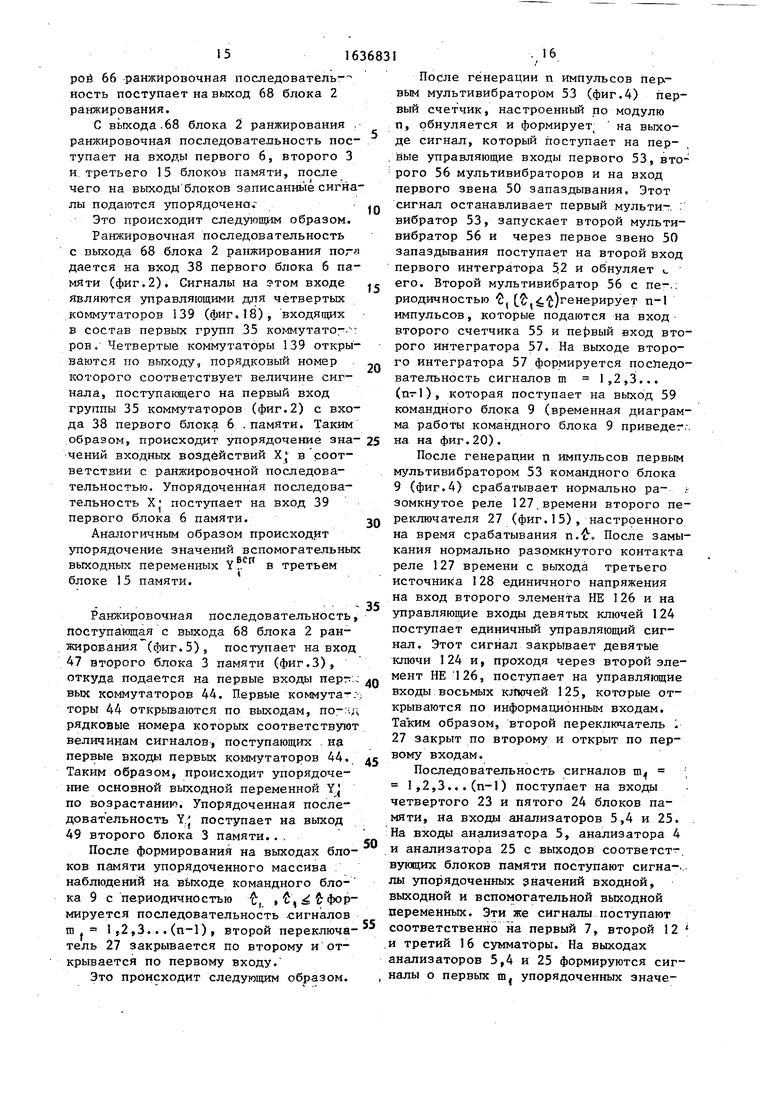

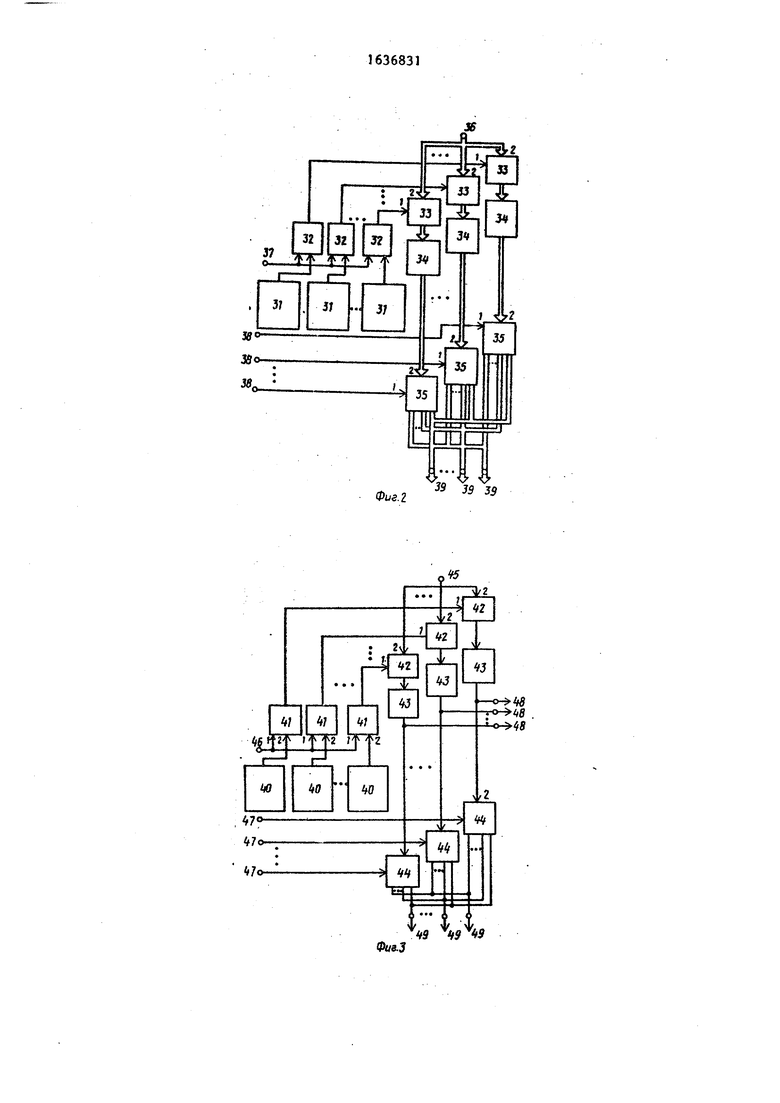

Командный блок 9 (фиг.4) содержит первое звено 50 запаздывания, первый счетчик 51, первый интегратор 52, первый мультивибратор 53, второе звено .с 54 запаздывания, второй счетчик 55, второй мультивибратор 56, второй интегратор 57, третье звено 58 запаздывания. Выход 59 командного блока 9 соединен с выходом второго интегратора 57, второй вход которого связан с выходом третьего звена 58 запаздывания.

Выход второго счетчика 55 связан с выходом 60 командного блока 9, входами второго 54 и третьего 58 звеньев запаздывания и вторым входом второго мультивибратора 56. Выход первого счетчика 51 соединен с первым входом первого мультивибратора 53, входом

5

516368316

первого звена 50 запаздывания и первым Выход 68 блока 2 ранжирования образо- входом второго мультивибратора 56, Зан выходами четвертых сумматоров 66.

выход которого связан с первым входом второго интегратора 57 и входом второ - го счетчика 55. Выход второго звена 54 запаздывания связан с вторым вводом первого мультивибратора 53, выход которого соединен с входом первого счетчика 51 и первым входом первого интегратора 52. Выход первого звена запыздывания связан с вторым входом первого интегратора 52, выход которого подключен к выходу 61 командного блока 9.

Блок 2 ранжирования (фиг.5) содержит п первых схем 62 выбора максимальной из нескольких переменных, n x n третьих компараторов 63, n x n усили- телей 64, (n-l)-x нормально замкнутых вторых ключей 65, n четвертых сумматоров 66. Блок 2 ранжирования состоит из n каналов (на фиг.5 они выделены пунктиром). Первый канал содержит первую схему 62 выбора максимальной из нескольких переменных, n третьих компараторов 63 9 п усилителей 64. Остальные п-1 каналы дополнительно содержат по n вторых ключей 65. Входы каждого из каналов соединены с первыми входами третьих компараторов 63 и входами первой схемы 62 выбора максимальной из нескольких переменных, выход которой связан с вто- рыми входами третьих компараторов 63. Вы ходы третьих компараторов 63, соединены с входами усилителей 64, выходы которых подключены к выходам каналов. - Каналы отличаются друг от друга тем, что усилители 64 первого канала настроены так, что усиливают сигнал, формируемый на выходах третьих компараторов 63, до величины п, усилители 64 второго канала - до величины и т.д. усилители 64 последнего канала - до единичной величины. Выходы канала соединены с управляющими входами вторых ключей 65, входящих в состав следующим за ним каналов, и с соответствующими порядковому номеру канпа входами четвертого сумматора 66. Исключение составляет последний канал, выходы которого соединены только с последними входами четвертых сумматоров 66. Вход 67 блока 2 ранжирования связан с входами первого канала и информационными входами вторых ключей 65, которые входят в состав остальных каналов.

.,

10

15

25

30

20

35

40

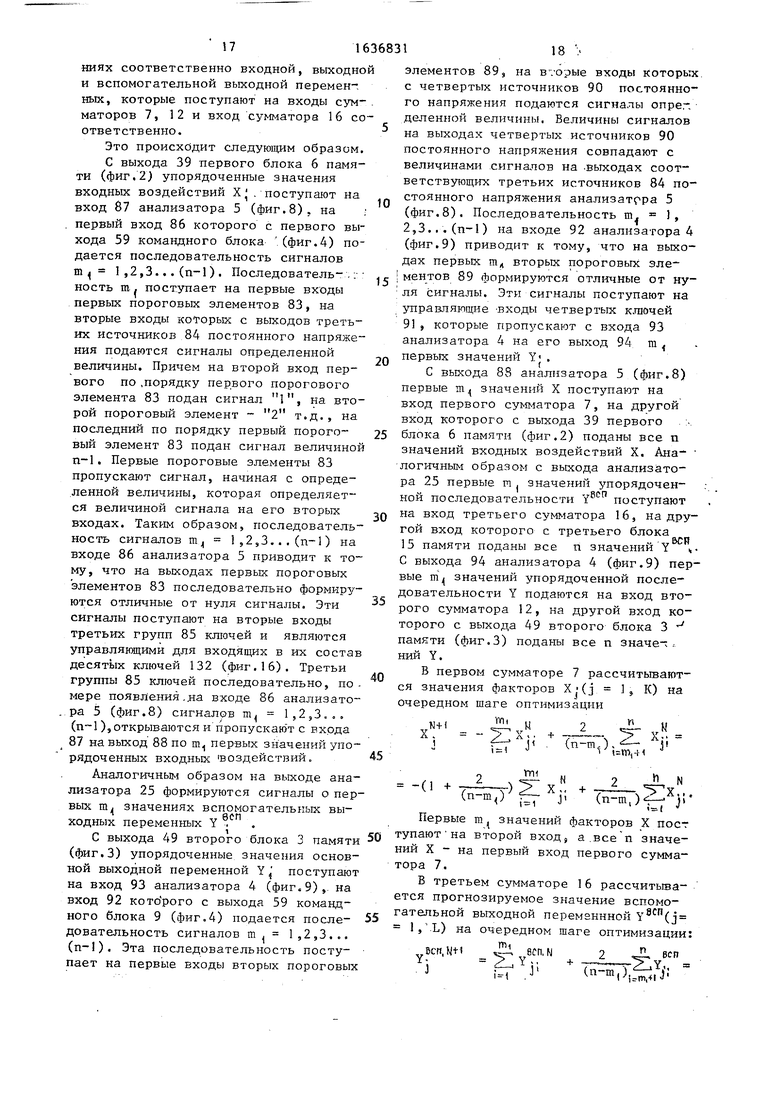

Четвертый блок 23 памяти (фиг.6) содержит первый источник 69 единичного напряжения, второй коммутатор 70, п-1 вторых ячеек 71 памяти, п-1 нор мально разомкнутых третьих ключей 72. Выход первого источника 69 единично го напряжения соединен с первым входом второго коммутатора 70, второй вход которого подключен к первому входу 73 четвертого блока 23 памяти. Выходы второго коммутатора 70 связаны с управляющими входами третьих ключей 72, информационные входы которых подключены к второму входу 74 четвертого блока 23 памяти. Выходы третьих ключей 72 связаны с входами вторых ячеек 71 памяти, выходы которых образуют выход 75 четвертого блока 23 памяти.

Пятый блок 24 памяти (фиг.7) содержит второй источник 76 единичного напряжения, третий коммутатор 77, n-i вторых групп -78 ячеек памяти, п-1 . вторых групп 79 нормально разомкнутых ключей. Выход второго источника 76 единичного напряжения соединен с первым входом третьего коммутатора 77, второй вход которого подключен к первому входу 80 пятого блока памяти. Выход третьего коммутатора 77 связан с управляющими входами вторых групп ключей 79 (фиг.16). Вход 81 пятого блока 24 памяти соединен с векторными информационный входами вторых групп ключей 79, векторные выходы которых связаны с векторными входами

вторых групп ячеек 78 памяти (фиг.17), векторные выходы которых образуют выход 82 пятого блока 24 памяти.

Анализатор 5 входного сигнала объекта (фиг.8) содержит п-1 первых пороговых элементов 83, п-1 третьих источников 84 постоянного напряжения, п-1 третьих групп 85 ключей. Вход 86 анализатора 5 входного сигнала объекта соединен с первыми входами первых пороговых элементов 83, вторые входы которых связаны с выходами третьих ис- источников 84 постоянного напряжения, настроенных так, что на второй вход первого порогового элемента 83 подан сигнал 1, на второй пороговый элемент 83 - 2 и т.д. на последний первьй пороговый элемент 83 подан сигнал величиной п-1.

Выходы первых пороговых элементов 83 соединены с управляющими входами третьих групп 85 ключей (фиг.16). Вход 87 анализатора 5 входного сигнала объекта связан с векторными информационными входами третьих групп ключей 85-, векторные выходы которых образуют выход 88 анализатора 5 входного сигнала объекта.

Анализатор 4 выходного сигнала объекта (фиг.9) содержит п-1 вторых пороговых элементов 89, п-1 четвертых источников 90 постоянного напряжения, п-1 четвертых нормально разомкнутых ключей 9. Вход $2 анализатора 4 вы- ходного сигнала объекта соединен с первыми входами вторых пороговых элементов 89, вторые входы которых соединены с выходами четвертых источни- ков 90 постоянного напряжения, настроенных так, что на второй вход первого по порядку второго порогового элемента 89 подан сигнал 1, на йто10

15

20

той 106 и пятый 107 нормально разомкнутые ключи, седьмой сумматор 108. Ин формационный вход шестого ключа 106 связан с входом 109, а информационный вход пятого ключа. 107 с входом 110 переключателя 13. Вход 111 пере- ключателя 13 соединен с управляющим входом пя того ключа 107 и входом первого элемента НЕ 105, выход которого связан с управляющим входом шестого ключа 106. Выход пятого ключа 107 соединен с первым входом, а выход шестого ключа 106 - с вторым входом сумматора 108, выход которого подключен к выходу 112 переключателя 13.

Анализатор 14 успешности шага i. (фиг.13) содержит вторую схему 113 выбора максимальной из нескольких пе- ременньк, п-1 четвертых компараторов 114, п-1 седьмых нормально разомкнутых ключей 115. Вход 116 анализатора 14 успешности шага соединен с первыми iвходами четвертых компараторов И4 и

рой пороговый элемент 89 пбдан сигнал 25 j:входами второй схемы 113 выбора мак2, и т.д., на последний второй пороговый элемент 89 подан сигнал величиной п-1. Выходы вторых пороговых элементов 89 связаны с управляющими

входами четвертых ключей .91, информа- 30 заны с информационными входами седът

мых ключей 115, управляющие входы которых подключены к входу 117 анализатора 14 успешности шага. Выходы седьмых ключей 15 образуют выход 118 анализатора 14 успешности шага.

ционные входы которых.образуют вход 93, а выходы - выход i 94 анализатора 4 выходного сигнала объекта.

Первый блок 11 сравнения (фиг.10) содержит К третьих пороговых элементов 95 и пятьй сумматор 96. Вход 97 первого блока 11 сравнения связан с первыми входами третьих пороговых элементов 95, вторые входы которых подключены к входу 98 первого блока 11 сравнения. Выходы третьих пороговых элементов 95 связаны с входами пятого сумматора 96, выход которого подключен к выходу 99 первого блока 1 сравнения.

Элемент И 18 (фиг.11) содержит шестой сумматор 100 и схему 101 ограничения выходного напряжения по амплитуде. Вход 102 и вход 103 элемента И 18 соответственно соединены с первым и вторым входом шестого сумматора 100, выход которого связан с входом схемы 101 ограничения выходного напряжения по амплитуде. Выход схемы 101 ограничения выходного напряжения па амплитуде подключен к выходу 104 элемента И 18.

Первый переключатель 13 (фиг.12) содержит первый элемент НЕ 105, шес

0

той 106 и пятый 107 нормально разомкнутые ключи, седьмой сумматор 108. Информационный вход шестого ключа 106 связан с входом 109, а информационный вход пятого ключа. 107 с входом 110 переключателя 13. Вход 111 пере- ключателя 13 соединен с управляющим входом пя того ключа 107 и входом первого элемента НЕ 105, выход которого связан с управляющим входом шестого ключа 106. Выход пятого ключа 107 соединен с первым входом, а выход шестого ключа 106 - с вторым входом сумматора 108, выход которого подключен - к выходу 112 переключателя 13.

Анализатор 14 успешности шага i. (фиг.13) содержит вторую схему 113 выбора максимальной из нескольких пе- ременньк, п-1 четвертых компараторов 114, п-1 седьмых нормально разомкнутых ключей 115. Вход 116 анализатора 14 успешности шага соединен с первыми iвходами четвертых компараторов И4 и

входами второй схемы 113 выбора максимальной из нескольких переменных, выход которой подключен к вторым входам четвертых компараторов 114. Выходы четвертых компараторов 114 связаны с информационными входами седът

мых ключей 115, управляющие входы которых подключены к входу 117 анализатора 14 успешности шага. Выходы седьмых ключей 15 образуют выход 118 анализатора 14 успешности шага.

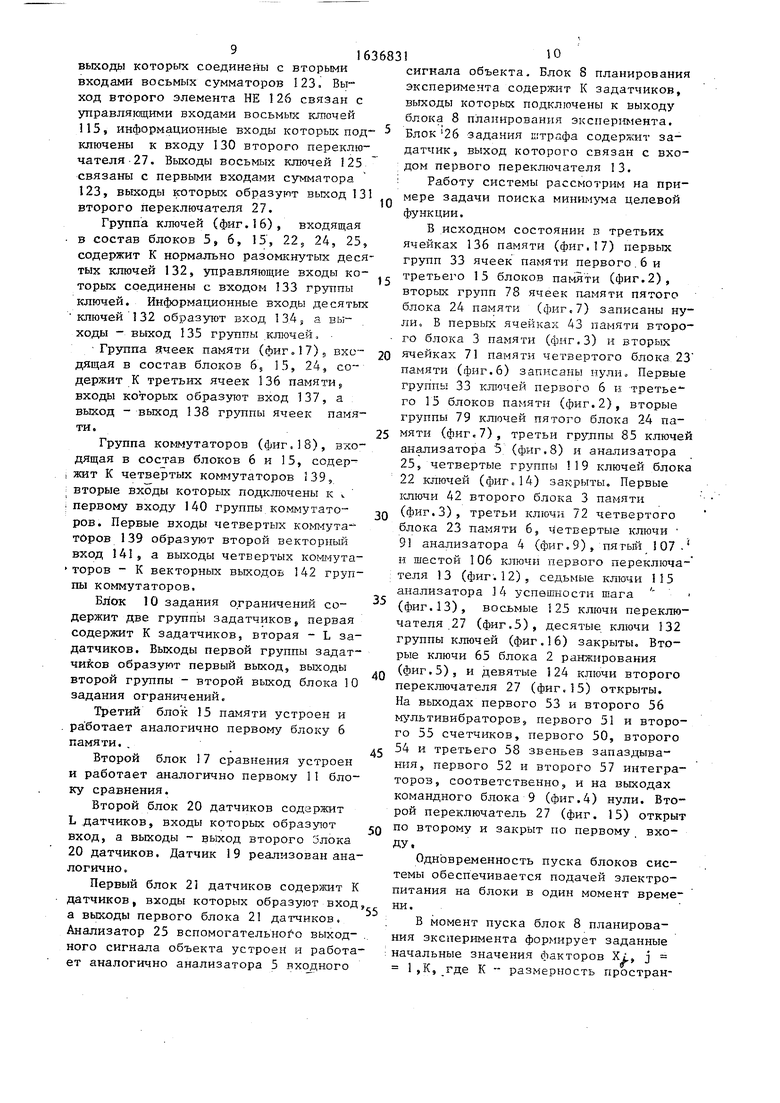

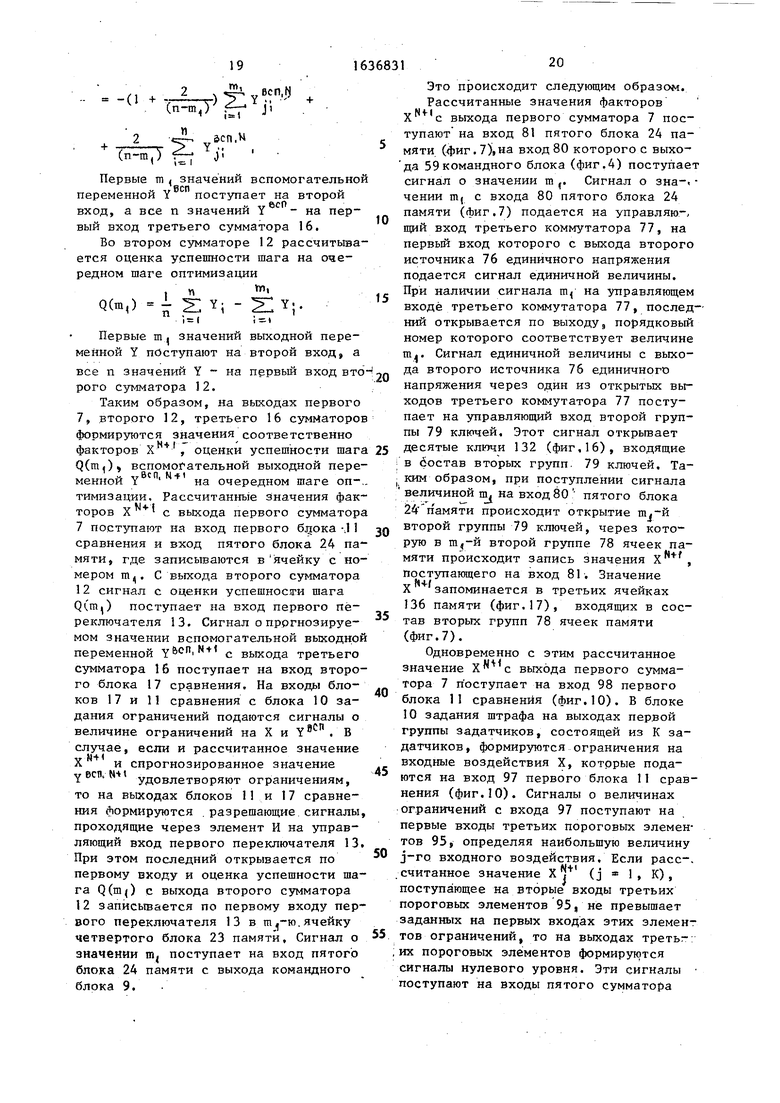

Блок 22 ключей (фиг.14) содержит п-1 четвертых групп ключей 119 1 (фиг.16), Управляющие входы четвер- тых групп ключей 119 подключены к , входу 120 блока 22 ключей,.. вход 121 .которого связан с векторными информационными входами четвертых групп ключей 119. Выходы четвертых групп ключей 119 соединены с выходом 112 блока 22 ключей.

Второй переключатель 27 (фиг.15) содержит К восьмых сумматоров 123, К девятых 124 и К восьмых 125 нормально замкнутых ключей, второй элемент НЕ 126, нормально разомкнутое реле 127 времени, третий источник 128 единичного напряжения. Выход третьего источника 128 единичного напряжения связан с входом реле 1 27 времени, выход которого соединен с входом второго элемента НЕ 126 и с управляющими входами девятых ключей. Вход 129 второго переключателя связан с информационными входами девятых ключей 124,

10

15

9163683

выходы которых соединены с вторыми

входами восьмых сумматоров 123. Выход второго элемента НЕ 126 связан с управляющими входами восьмых ключей 115, информационные входы которых под- 5 ключены к входу 130 второго переключателя 27. Выходы восьмых ключей 125 связаны с первыми входами сумматора 123, выходы которых образуют выход 131 второго переключателя 27.

Группа ключей (фиг.16), входящая в состав блоков 5, 6, 15, 22} 24, 25, содержит К нормально разомкнутых десятых ключей 132, управляющие входы которых соединены с входом 133 группы ключей. Информационные входы десятых ключей 132 образуют вход 134, а выходы - выход 135 группы ключей,

Группа ячеек памяти (фиг.17) вхо 20 дящая в состав блоков 6, 15, 24, содержит К третьих ячеек 136 памяти, входы которых образуют вход 137, а выход - выход 138 группы ячеек памяти.25

Группа коммутаторов (фиг.18), входящая в состав блоков 6 и 15, содер- жит К четвертых коммутаторов 39, вторые входы которых подключены к ,. первому входу 140 группы коммутато- л ров. Первые входы четвертых коммута торов 139 образуют второй векторный вход 141, а выходы четвертых коммута- торов - К векторных выходов 142 группы коммутаторов.

БлЧж 10 задания ограничений со- держит две группы задатчиковs первая содержит К задатчиков, вторая - L за- датчиков. Выходы первой группы задатчиков образуют первый выход, выходы второй группы - второй выход блока 10 задания ограничений.

Третий блок 15 памяти устроен и работает аналогично первому блоку 6 памяти..

Второй блок 17 сравнения устроен и работает аналогично первому 11 блоку сравнения.

Второй блок 20 датчиков содержит L датчиков, входы которых образуют сп вход, а выходы - выход второго Злока 20 датчиков. Датчик 19 реализован аналогично.

Первый блок 23 датчиков содержит К датчиков, входы которых образуют вход, а выходы первого блока 21 датчиков. Анализатор 25 вспомогательного выходного сигнала объекта устроен и работает аналогично анализатора 5 входного

40

45

55

10

15

683

5

20 25

л

сп

40

45

5

11°

сигнала объекта. Блок 8 планирования эксперимента содержит К задатчиков, выходы которых подключены к выходу блока 8 планирования эксперимента. Блок 26 задания штрафа содержит за- датчик, выход которого связан с вхо дом первого переключателя 13.

Работу системы рассмотрим на примере задачи поиска минимума целевой функции.

В исходном состоянии в третьих ячейках 136 памяти (фиг.17) первых групп 33 ячеек памяти первого 6 и третьего 15 блоков памяти (фиг.2), вторых групп 78 ячеек памяти пятого блока 24 памяти (фиг,7) записаны нули В первых ячейках 43 памяти второго блока 3 памяти (фиг.З) и вторых ячейках 71 памяти четвертого блока 23 памяти (фиг.6) записаны нули Первые группы 33 ключей первого 6 и третье - го 15 блоков памяти (фиг.2), вторые группы 79 ключей пятого блока 24 памяти (фиг.7), третьи группы 85 ключей анализатора 5 (фиг.З) и анализатора 25, четвертые группы 119 ключей блока 22 ключей () закрыты. Первые ключи 42 второго блока 3 памяти (фиг.З), третьи ключи 72 четвертого блока 23 памяти 6, четвертые ключи 9 анализатора 4 (фиг,9), пятый 107 . и шестой 106 ключи первого переключателя 13 (фиг.12), седьмые ключи 115 анализатора 14 успешности шага (фиг.13), восьмые 125 ключи переключателя 27 (фиг.5), десятые ключи 132 группы ключей (фиг.16) закрыты. Вторые ключи 65 блока 2 ранжирования (фиг.5), и девятые 124 ключи второго переключателя 27 (фиг,15) открыты. На выходах первого 53 и второго 56 мультивибраторов, первого 51 и второго 55 счетчиков, первого 50, второго 54 и третьего 58 звеньев запаздывания, первого 52 и второго 57 интеграторов, соответственно, и на выходах командного блока 9 (фиг.4) нули. Второй переключатель 27 (фиг. 15) открыт по второму и закрыт по первому вхо- ДУ.

Одновременность пуска блоков системы обеспечивается подачей электропитания на блоки в один момент времени.

В момент пуска блок 8 планирования эксперимента формирует заданные начальные значения факторов XL, j

1 ТГ TJ- .....С

I,К,.где К

размерность пространства факторов. С выхода блока 8 планирования эксперимента через второй вход второго переключателя 27 сигнал о заданных значениях факторов поступа- ет на вход объекта 1, где реализуется с ошибкой Z. Одновременно в момент пуска на втором выходе командного блока 9 с периодичностью Ј формируются сигналы величиной l,2,3t..n, где и задается заранее, исходя из свойств объекта, С второго выхода командного блока 9 сигналы поступают на входы первого 6, второго 3 и третьего 15 блоков памяти, где записываются сигналы, приходящие соответст- веняо с первого блока 21 датчиков, датчика 19 и второго блока 20 датчиков-. В первом блоке 6 памяти записываются значения входного воздействия х + Z (j , К; i 1 ,п), соответствующее ему значение основной выходной Y; .и вспомогательной выходной ( j I ,L) переменных записываются соответственно во втором 3 и третьем 15 блоках памяти. Это происходит следующим образом. .

В момент пуска на выходах задатчи- ков, входящих в состав блока 8 планирования эксперимента, формируются сигналы о значениях входных воздействий, которые подаются на вход 129 второго переключателя 27 (фиг.15), где через открытые девятые ключи 124 и восьмые сумматоры 123 поступают на выход 131. С выхода 131 второго переключателя 27 сигналы о значениях входных воздействий поступают на вход объекта 1, где реализуются с ошибкой Z, поступающей с входа 28 системы.

Реализованные входные воздействия X+Z измеряются первым блоком 21 датчиков и поступают на вход 36 первого блока 6 памяти (фиг.2). Полученные : значения основной выходной переменной Y на выходе объекта 1 измеряются датчиком 19 и поступают на вход 45 второго блока 3 памяти (фиг.Ч). Полученные значения вспомогательной выходной переменной на выходе объекта 1 измеряются вторым блоком 20 датчиков и поступают на вход третьего блока 15 памяти.

Одновременно с этим в момент пуска первый мультивибратор 53 командного блока 9 (фиг.4) начинает генерировать п единичных импульсов с периодично- стью f , (п К+1, К - число факторов, п - выбирается заранее с учетом .

0

5

0

5

0

5

0

5

0

5

свойств объекта оптимизации). Единичные импульсы подаются на первый вход первого интегратора 52, на выходе которого формируется последовательность сигналов величиной 1,2,3...п, которая подается на выход 61 командного блока 9 (временная диаграмма работы командного блока 9 приведена на фиг.20). С выхода 61 командного блока 9 последовательность сигналов поступает на входы 37 первого 6 и третьего 15 блоков пат мяти (фиг.2), и на вход 46 третьего блока 15 памяти (фиг.З). С входа 37 первого блока в памяти (фиг.2) последовательность сигналов величиной 1,2, З...П поступает на первые входы первых компараторов 32, на вторые входы которых с выходов первых источников 31 постоянного напряжения поданы сигналы определенной величины. Причем с первого по порядку первого источника 31 постоянного напряжения подан сигнал 1, со второго - 2, и т.д., с последнего первого источника 31 постоянного напряжения подан сигнал величиной п. При совпадении по величине значений сигналов, поступающих на входы первых компараторов 32 с входа 37 первого блока 6 памяти и с выходов первых источников 31 постоянного напряжения, на выходе первого компаратора 32, на входах которого значения совпали, формируется сигнал подаваемый на управляющий вход одной из первых групп 33 ключей. С управляющего входа первой группы 33 ключей сигнал поступает на управляющие входы десятых ключей 132 (фиг.16), открывая их. Таким образом, появление последовательности сигналов 1,2,3...п на входе 37 первого блока 6 памяти (фиг.2) вызывает поочередное открытие первых групп 33 ключей. Через информационный векторный вход открытой первой группы 33 ключей с входа 36 первого блока 6 памяти на векторный вход одной из пер-, вых групп 34 ячеек памяти поступают сигналы о значениях входных воздействий в i-м опыте. Эти сигналы после закрытия первой группы 38 ключей записываются в ячейках 136 памяти (фиг.17), входящих в состав первых групп 34 ячеек памяти.

Аналогичным образом происходит запись значений вспомогательной выходной переменной у90 i 1,п в третьем блоке 15 памяти Эти значения поступают через вторую группу 20 датчиков

л-

13

с выхода 30 объекта 1 на вход третьего блока 15 памяти.

Поступающая на вход 46 второго блока 3 памяти последовательность сигналов 1,2,3...п подается на первые входы вторых компараторов 41, На вторые входы вторых компараторов 41 с выходов вторых источников 40 постоянного напряжения поданы сигналы величиной от 1 до п, таким же образом как и с выходов первых источников 31 постоянного напряжения первого блока 6 памяти (фиг.2). При совпадении величин сигналов на входах второго компаратора 41 (фиг.З) на его выходе формируется управляющий сигнал, который открывает один из первых ключей 42. Таким образом, появление последователь ности сигналов величиной 1,2,3...п на входе 46 второго блока 3 памяти вызывает, поочередное открытие первых ключей 42. Сигнал о величине основной выходной переменной Y в i-м опыте

/

с входа 45 второго блока 3 памяти про- ходит через открытый i-й первый ключ 42 на вход первой ячейки 43 памяти, -т где записывается. Это происходит при замыкании первого ключа 42 при появлении на входе 46 второго блока 3 па мяти очередного сигнала.

Таким образом, в первых группах 34 ячеек памяти первого б (фиг.2) и, третьего 15 блоков памяти и в первых ячейках 43 памяти второго блока 3 памяти (фиг.З) записаны величины соот-, ветственно входных воздействий Х (j I , К), выходной вспомогательной переменной (j 1 , L) и выходной основной переменной Y-: в п опытах, i 1 , п.

С выхода второго блока 3 памяти сигналы о записанных значениях основной выходной переменной поступают на вход блока 2 ранжирования, где наблюдения упорядочиваются по возрас танию.

Это происходит следующим образом.

С выхода 48 второго блока 3 памяти (фиг.З) сигналы о значениях Y поступают на вход 67 блока 2 ранжирования (фиг.5), откуда подаются на входы первого канала и на информационные входы вторых ключей 65, входящих в состав остальных каналов. В первом канале блока 2 ранжирования сиг- налы поступают на входы первой схемы 62 выбора максимальной из нескольких переменных и на первые входы третьих

163

5

10

15

20

25 п

Ь40

55

683114

компараторов 63. На выходе первой схемы 62 выбора максимальной из несколь ких переменных формируется сигнал, равный по величине наибольшему по значению сигналу на входах этой схемы. Этот сигнал поступает на вторые входы третьих компараторов 63. При совпадении величин сигналов на входах третьего компаратора 63, порядковый номер которого соответствует порядковому номеру наибольшего значения Y в исходной последовательности наблюдений, на выходе последнего формируется единичный сигнал. Этот сигнал поступает на вход усилителя 64, где усиливается до величины п. Таким образом, на одном из выходов первого канала блока 2 ранжирования формируется сигнал величиной п, на остальных выходах этого канала сигналы равны нулю. Сигналы с ВЬЕХОДОВ первого канала поступают на первые входы четвертых сумматоров 66 и на управляющие входы вторых ключей 65 второго канала. При этом второй ключ 65, порядковый номер которого соответствует порядковому номеру наибольшей величины Y в исходной последовательности, закрывается, так как на его управляющем входе присутствует отличный от нуля сигнал. Далее во втором канале блока 2 ранжирования про- . исходит выбор второй по значению величины Y. Выбор осуществляется аналогично работе первого канала. В результате на одном из выходов второго канала блока 2 ранжирования формируется сигнал величиной п-1, на остальных выходах этого канала сигналы равны нулю. Сигналы с выходов второго канала поступают на вторые входы четвертых сумматоров 66 и на управляющие входы вторых ключей 65 третьего канала. Далее в остальных каналах производится выбор третьей, четвертой и т.д. по - значению величины Y. Таким образом, на входы четвертых сумматоров 66 поданы нули и сигналы, величины которых характеризуют положение выходной переменной У в итоговой упорядоченной по возрастанию последовательности. На выходах четвертых сумматоров 66 формируются сигналы, определяющие положе- . ние Y, в ранжированной последовательности, причем совпадает с порядковыми номерами четвертых сумматоров 66 и соответственно с порядковыми номерами Y в исходной последовательности наблюдений, С выходов четвертых суммато45

50

15

1636831

рой 66 ранжировочная последователь- ность поступает на выход 68 блока 2 ранжирования.

С выхода.68 блока 2 ранжирования ранжировочная последовательность поступает на входы первого 6, второго 3 и третьего 15 блоков памяти, после чего на выходы блоков записанные сигналы подаются упорядочена

Это происходит следующим образом.

Ранжировочная последовательность с выхода 68 блока 2 ранжирования по,- дается на вход 38 первого блока 6 памяти (фиг.2). Сигналы на том входе являются управляющими для четвертых коммутаторов 139 (фиг.18), входящих в состав первых групп 35 коммутато-.-- ров. Четвертые коммутаторы 139 открываются по выходу, порядковый номер которого соответствует величине сигнала, поступающего на первый вход группы 35 коммутаторов (фиг.2) с входа 38 первого блока 6 . памяти. Таким

образом, происходит упорядочение зна-

чений входных воздействий XJ в соответствии с ранжировочной последовательностью. Упорядоченная последовательность X поступает на вход 39 первого блока 6 памяти.

Аналогичным образом происходит упорядочение значений вспомогательных

В СП

выходных переменных Y., в третьем блоке 15 памяти.

-

Ранжировочная последовательность,

поступающая с выхода 68 блока 2 ранжирования (фиг.5), поступает на вход 47 второго блока 3 памяти (фиг.З), откуда подается на первые входы пер- . вых коммутаторов 44. Первые коммута-: торы 44 открываются по выходам, по- .;, рядковые номера которых соответствуют величинам сигналов, поступающих на первые входы первых коммутаторов 44. Таким образом, происходит упорядочение основной выходной переменной YJ по возрастанию. Упорядоченная последовательность Y| поступает на выход 49 второго блока 3 памяти.. ,

После формирования на выходах блоков памяти упорядоченного массива наблюдений на выходе командного блока 9 с периодичностью Ј Ј Сформируется последовательность .сигналов m 1 ,2,3... (п-1) , второй переключатель 27 закрывается по второму и открывается по первому входу.

Это происходит следующим образом.

Q

0

.16

После генерации п импульсов пер.- вым мультивибратором 53 (фиг.4) первый счетчик, настроенный по модулю п, обнуляется и формирует1 на выходе сигнал, который поступает на первые управляющие входы первого 53, второго 56 мультивибраторов и на вход первого звена 50 запаздывания. Этот сигнал останавливает первый мультивибратор 53, запускает второй мультивибратор 56 и через первое звено 50 запаздывания поступает на второй вход первого интегратора 52 и обнуляет его. Второй мультивибратор 56 с периодичностью Ј (Ј Сгенерирует п-1 импульсов, которые подаются на вход второго счетчика 55 и первый вход второго интегратора 57. На выходе второго интегратора 57 формируется последовательность сигналов m 1,2,3... (п-1), которая поступает на выход 59 командного блока 9 (временная диаграмма работы командного блока 9 приведет

0

5

Q

0

После генерации п импульсов первым мультивибратором 53 командного блока 9 (фиг.4) срабатывает нормально разомкнутое реле 127 времени второго переключателя 27 (фиг.15), настроенного на время срабатывания п.Ј. После замыкания нормально разомкнутого контакта реле 127 времени с выхода третьего источника 128 единичного напряжения на вход второго элемента НЕ 126 и на управляющие входы девятых ключей 124 поступает единичный управляющий сигнал. Этот сигнал закрывает девятые ключи 124 и, проходя через второй элемент НЕ 126, поступает на управляющие входы восьмых ключей 125, которые открываются по информационным входам. Таким образом, второй переключатель 1 27 закрыт по второму и открыт по первому входам.

Последовательность сигналов т - 1,2,3...(п-1) поступает на входы четвертого 23 и пятого 24 блоков памяти, на входы анализаторов 5,4 и 25. На входы анализатора 5, анализатора 4 и анализатора 25 с выходов соответствующих блоков памяти поступают сигна-. лы упорядоченных значений входной, выходной и вспомогательной выходной переменных. Эти же сигналы поступают соответственно на первый 7, второй 12 4 и третий 16 сумматоры. На выходах анализаторов 5,4 и 25 формируются сигналы о первых Ш| упорядоченных эначениях соответственно входной, выходной и вспомогательной выходной переменных, которые поступают на входы сумматоров 7, 12 и вход сумматора 16 соответственно.

Это происходит следующим образом. С выхода 39 первого блока 6 памяти (фиг.2) упорядоченные значения входных воздействий Х поступают на вход 87 анализатора 5 (фиг.8). на первый вход 86 которого с первого выхода 59 командного блока (фиг.4) подается последовательность сигналов пц 1,2,3...(п-1). Последователь- . ность m , поступает на первые входы первых пороговых элементов 83, на вторые входы которых с выходов третьих источников 84 постоянного напряжения подаются сигналы определенной величины. Причем на второй вход первого по .порядку первого порогового элемента 83 подан сигнал 1, на второй пороговый элемент - 2 т.д., на последний по порядку первый пороговый элемент 83 подан сигнал величиной п-1. Первые пороговые элементы 83 пропускают сигнал, начиная с определенной величины, которая определяется величиной сигнала на его вторых входах. Таким образом, последовательность сигналов т,, 1 ,2,3.. . (п-1) на входе 86 анализатора 5 приводит к тому, что на выходах первых пороговых элементов 83 последовательно формируются отличные от нуля сигналы. Эти сигналы поступают на вторые входы третьих групп 85 ключей и являются управляющими для входящих в их состав десятых ключей 132 (фиг.16). Третьи группы 85 ключей последовательно, по . мере появления.на входе 86 анализато- ра 5 (фиг.8) сигналов т 1,2,3.,. (),открываются и пропускают с входа 87 на выход 88 по т1 первых значений упорядоченных входных воздействий.

Аналогичным образом на выходе анализатора 25 формируются сигналы о первых пь значениях вспомогательных вы5., есп

ходных переменных Y .

С выхода 49 второго блока 3 памяти (фиг.З) упорядоченные значения основной выходной переменной Y ( поступают на вход 93 анализатора 4 (фиг.9), на вход 92 кото рого с выхода 59 командного блока 9 (фиг.4) подается последовательность сигналов m , 1,2,3... (п-1). Эта последовательность поступает на первые входы вторых пороговых

0

5

0

5

0

5

0

элементов 89, на в .-орые входы которых с четвертых источников 90 постоянного напряжения подаются сигналы определенной величины. Величины сигналов на выходах четвертых источников 90 постоянного напряжения совпадают с величинами сигналов на выходах соответствующих третьих источников 84 постоянного напряжения анализатора 5 (фиг.З). Последовательность m. 1, 2,3...(п-1) на входе 92 анализатора 4 (фиг.9) приводит к тому, что на выходах первых т„ вторых пороговых элементов 89 формируются отличные от нуля сигналы. Эти сигналы поступают на управляющие входы четвертых ключей 91} которые пропускают с входа 93 анализатора 4 на его выход 94 m,, первых значений Y« .

С выхода 83 анализатора 5 (фиг.З) первые пц значений X поступают на вход первого сумматора 7, на другой вход которого с выхода 39 первого блока 6 памяти (фиг.2) поданы все п значений входных воздействий X. Аналогичным образом с выхода анализатора 25 первые m . значений упорядоченной последовательности у поступают на вход третьего сумматора 16, на другой вход которого с третьего блока

&CR 15 памяти поданы все п значений Y ,,

С выхода 94 анализатора 4 (фиг.9) первые ггц значений упорядоченной последовательности Y подаются на вход второго сумматора 12, на другой вход которого с выхода 49 второго блока 3 памяти (фиг.З) поданы все п значений Y.

В первом сумматоре 7 рассчитываются значения факторов Xj(j 1, К) на очередном шаге оптимизации

х™

fini

M

- z:x;

1 1

(n-m,) , - ,-H

-(1 +

mi

(n-m,)

N

X-. J1

+ 2 4V

f s Л i .

(n-m,)-. j.

Первые m( значений факторов X пост тупают на второй вход, а все п значений X - на первый вход первого сумматора 7.

В третьем сумматоре 16 рассчитывается прогнозируемое значение вспомогательной выходной переменнной Y8Cn(j I, L) на очередном шаге оптимизации:

,Nti чр een.N + 2t есп

я4 J 1 + n-miJ,S$

гг.

-(1 + r

всп.Ч

1)

+...2 4-

+ frr J;

Первые in значений вспомогательной

переменной Y ° поступает на второй

„ „ вер

вход, а все п значении Y - на первый вход третьего сумматора 16.

Во втором сумматоре 12 рассчитывается оценка успешности шага на очередном шаге оптимизации

,

Q,) -Ј S Y; - 2IY;1 1 ;

Первые m значений выходной переменной Y поступают на второй вход, а все п значений Y - на первый вход вто-4 рого сумматора 12.

Таким образом, на выходах первого 7, второго 12, третьего 16 сумматоров формируются значения соответственно

10

Рассчитанные значения факторов выхода первого сумматора 7 поступают на вход 81 пятого блока 24 па- мяти (фиг. 7),на вход 80 которого с выхо- да 59 командного блока (фиг.4) поступает сигнал о значении m (. Сигнал о зна- чении т( с входа 80 пятого блока 24 памяти (фиг.7) подается на управляю-, щий вход третьего коммутатора 77, на первый вход которого с выхода второго источника 76 единичного напряжения подается сигнал единичной величины. . При наличии сигнала пц на управляющем входе третьего коммутатора 77, последний открывается по выходу, порядковый номер которого соответствует величине т.. Сигнал единичной величины с выхода второго источника 76 единичного напряжения через один из открытых выходов третьего коммутатора 77 поступает на управляющий вход второй группы 79 ключей. Этот сигнал открывает

20

факторов ХН+ Г оценки успешности шага 25 Десятые ключи 132 (фиг,16), входящие Q(m), вспомогательной выходной пере- в с-остав вторых групп 79 ключей. Та- менной на очередном шаге оп- . ким- образом, при поступлении сигнала тимизации. Рассчитанные значения фак величиной т. на вход 80 пятого блока

N+1-----торов с выхода первого сумматора 7 поступают на вход первого блока -11 0 сравнения и вход пятого блока 24 памяти, где записываются в ячейку с номером т,,. С выхода второго сумматора 12 сигнал с оценки успешности шага Q(nij) поступает на вход первого пе24 памяти происходит открытие т,-й второй группы 79 ключей, через которую в т,-й второй группе 78 ячеек памяти происходит запись значения , поступающего на вход 81. Значение X запоминается в третьих ячейках 136 памяти (фиг.17), входящих в сосреключатепя 13. Сигнал опрогнозируе- тав вторых групп 78 ячеек памяти мом значении вспомогательной выходной (фиг.7). переменной с выхода третьего сумматора 16 поступает на вход второго блока 17 сравнения. На входы бло40

Одновременно с этим рассчитанное значение выхода первого сумматора 7 поступает на вход 98 первого блока 11 сравнения (фиг.10). В блоке 10 задания штрафа на выходах первой группы задатчиков, состоящей из К за- датчиков, формируются ограничения на входные воздействия X, которые подаются на вход 97 первого блока 11 сравнения (фиг.10). Сигналы о величинах ограничений с входа 97 поступают на первые входы третьих пороговых элементов 95, определяя наибольшую величину j-ro входного воздействия. Если расе-.

ков 17 и 11 сравнения с блока 10 задания ограничений подаются сигналы о величине ограничений на X и Y9 . В случае, если и рассчитанное значение X и спрогнозированное значение Y вся. N-и удОвлетвОрЯЮТ ограничениям,

то на выходах блоков 11 и 17 сравнения Формируются разрешающие сигналы, проходящие через элемент И на управляющий вход первого переключателя 13. При этом последний открывается по

40

45

50

Одновременно с этим рассчитанное значение выхода первого сумматора 7 поступает на вход 98 первого блока 11 сравнения (фиг.10). В блоке 10 задания штрафа на выходах первой группы задатчиков, состоящей из К за- датчиков, формируются ограничения на входные воздействия X, которые подаются на вход 97 первого блока 11 сравнения (фиг.10). Сигналы о величинах ограничений с входа 97 поступают на первые входы третьих пороговых элементов 95, определяя наибольшую величину j-ro входного воздействия. Если расе-.

первому входу и оценка успешности ша-.считанное значение X j (j 1, К), га Q(m) с выхода второго сумматора поступающее на вторые входы третьих 12 записывается по первому входу пер- пороговых элементов 95, не превышает вого переключателя 13 в т,-ю.ячейку заданных на первых входах этих элемен- четвертого блока 23 памяти. Сигнал о 55 тов ограничений, то на выходах треть- значении т. поступает на вход пятого, их пороговых элементов формируются блока 24 памяти с выхода командного сигналы нулевого уровня. Эти сигналы блока 9. поступают на входы пятого сумматора

Это происходит следующим образом.

Рассчитанные значения факторов выхода первого сумматора 7 поступают на вход 81 пятого блока 24 па- мяти (фиг. 7),на вход 80 которого с выхо- да 59 командного блока (фиг.4) поступает сигнал о значении m (. Сигнал о зна- чении т( с входа 80 пятого блока 24 памяти (фиг.7) подается на управляю-, щий вход третьего коммутатора 77, на первый вход которого с выхода второго источника 76 единичного напряжения подается сигнал единичной величины. При наличии сигнала пц на управляющем входе третьего коммутатора 77, последний открывается по выходу, порядковый номер которого соответствует величине т.. Сигнал единичной величины с выхода второго источника 76 единичного напряжения через один из открытых выходов третьего коммутатора 77 поступает на управляющий вход второй группы 79 ключей. Этот сигнал открывает

0

Десятые ключи 132 (фиг,16), входящие в с-остав вторых групп 79 ключей. Та- ким- образом, при поступлении сигнала величиной т. на вход 80 пятого блока

-----24 памяти происходит открытие т,-й второй группы 79 ключей, через которую в т,-й второй группе 78 ячеек памяти происходит запись значения , поступающего на вход 81. Значение X запоминается в третьих ячейках 136 памяти (фиг.17), входящих в состав вторых групп 78 ячеек памяти (фиг.7).

0

5

0

Одновременно с этим рассчитанное значение выхода первого сумматора 7 поступает на вход 98 первого блока 11 сравнения (фиг.10). В блоке 10 задания штрафа на выходах первой группы задатчиков, состоящей из К за- датчиков, формируются ограничения на входные воздействия X, которые подаются на вход 97 первого блока 11 сравнения (фиг.10). Сигналы о величинах ограничений с входа 97 поступают на первые входы третьих пороговых элементов 95, определяя наибольшую величину j-ro входного воздействия. Если расе-.

.считанное значение X j (j 1, К), поступающее на вторые входы третьих пороговых элементов 95, не превышает заданных на первых входах этих элемен- 5 тов ограничений, то на выходах треть- , их пороговых элементов формируются сигналы нулевого уровня. Эти сигналы поступают на входы пятого сумматора

96, на выходе которого также формируется сигнал нулевого уровня, поступающий на выход 99 первого блока 11 . сравнения.

Аналогичным образом происходит проверка на ограничения рассчитанного значения , N+I во втором блоке 17 сравнения Величины ограничений на (j 1, L) формируются на выходах второй группы задатчиков, состоящей, из К задатчиков, и поступают со второго векторного выхода этого блока на вход второго блока 17 сравнения. На другой вход векторного блока 17 сравнения с выхода третьего сумматора 16 поступает рассчитанное значение Y (j 1 , L). На выходе второго блока 17 сравнения формируется сигнал выполнения или невыполнения ограничений В случае выполнения ограничений сигнал имеет нулевой уровень.

1 Сигналы с выходов 99 блоков 11 и 1 7 сравнения (фиг.10) поступают на первый 102 и второй 103 входы элемента И (фиг.11), откуда подаются на входы шестого сумматора 100. С выхода шестого сумматора 100 сигнал подается на вход схемы 101 ограничения выходного напряжения по амплитуде, с выхода которой поступает на выход 104 элемента И 18. С выхода 104 элемента И 18 разрешающий сигнал нулевого уров- ,ня поступает на управляющий вход 111 первого переключателя 13 (фиг. 12), откуда подается на вход первого элемента НЕ 105. С выхода первого элемента НЕ 105 сигнал подается на управляющий вход шестого ключа 106, на информационный вход которого с вхо-, да 109 первого переключателя 13 подан сигнал оценки успешности шага Р(пц) , поступивший с выхода второго сумматора 12. Если сигнал на третьем входе 111 первого переключателя 13 имеет нулевой уровень, то шестой ключ 106 открывается и пропускает на второй вход седьмого сумматора 108 сигнал о значении оценки успешности шага Q(m). На первом входе пятого сумматора 108 сигнал отсутствует, так как пятый ключ 107 закрыт. На выходе седьмого сумматора 108 формируется .сигнал, равный по величине О.(пц), поданный на второй вход седьмого сумматора 108. С выхода 112 первого пере- 1ключателя 13 величина Q(m) поступает на вход 74 четвертого блока 23 памяти (фиг.6), на вход 73 которого с

5

0

5

0

5

0

5

0

5

выхода 59 командного блока 9 (фиг.4) подается сигнал величиной т. Сигнал величиной т с входа 73 четвертого блока 23 памяти (фиг.6) подается на управляющий вход второго коммутатора 70, на первый вход которого с выхода первого источника 69 единичного напряжения подается сигнал единичной величины. При наличии сигнала величиной т,| на управляющем входе второго коммутатора 70, последний открывается по выходу, порядковый номер котог рого соответствует величине управляющего сигнала. Сигнал единичной вели-, чины с выхода первого источника 69 единичного напряжения через один из открытых выходов второго коммутатора 70 поступает на управляющий вход од- . ного из третьих ключей 72 и открывает его. Таким образом, при поступлении сигнала величиной т( на первый вход 73 четвертого блока 23 памяти происходит открытие пц -го третьего ключа 72, через который на вход т,-и второй ячейки 71 памяти подается величина оценки успешности шага Q(m), поступающая со второго входа 74. Величина Q(m) записывается в второй ячейке 71 памяти при закрытии т{-го третьего ключа 72, которое происходит при поступлении на вход 73 четвертого, блока 23 памяти очередного сигнала последовательности т При этом происходит открытие следующего третьего ключа 72, через который в следующей второй ячейке памяти 71 записывается значение оценки успешности шага на очередном шаге оптимизации Q(m.).

Таким образом, в пятом блоке 24 памяти записаны (п-1) рассчитанных значений . В четвертом блоке 23 памяти, в случае выполнения ограничений задаваемых блокам 10 задания ог раничений, записаны величины оценок успешности шага Q на всех шагах оптимизации.

Если рассчитанные значения X1 на выходе первого сумматора 7 или спрогнозированные значения у СП| на выходе третьего сумматора 16 не удовлетворяют наложенным на них ограничениям, то на выходе элемента И 18 формируется запрещающий сигнал; первый переключатель 13 открывается по второму входу и закрывается по первому. По второму входу первого переключателя 13 в ячейку четвертого блока 23 памяти с выхода блока 26 за. Ы+1

23

1636831

дания штрафа записывается штраф, заведомо наихудший из всех возможных значений Q,

Это происходит следующим образом.

Есл на ш.-м таге оптимизации рас

AI А. I

считанное лшч-етше X , поступающее на вход 98 первого блока 11 сравнения (фиг,16), превышает по величине ограничения на входе 97, то на выходах

третьих пороговых элементов 96 формируются сигналы, отличные от нуля. Эти сигналы поступают на входы пятого сумматора 96, на выходе которого формируется результирующий, отличный от нуля, сигнал, поступающий на выход 99 блока 1 срагшсшш,

Аналогичном образом происходит проверка ограничений Y и формирование запрещающего игпэла в случае их не- выпогшончя во втором блоке 17 сравие- нчя.

Отличные от нуля сигналы с выходов 99 блоков 11 и 17 сравнения () поступают на входы 100 и 103 злепе та И (фиг.11), откуда подаются на входы шестого сумматора 100. Результируодий сигнап с выхода шестого сумматора 100 поступает и ход слей 10 orpj. ни я выходного нллря.ъеаия по амгтлчгу, дс„ лз ъьпЈос,е .со горой формируется запрещающий сигнал стандартной величины Этот сигнап поступает на выход 104 элемента И 18, откуда подается на вход 111 первого переключателя 13 (фиг.12) С входа 1I1 сигнал подается на вход первого элемента НЕ 105 и управляющий вход пятого ключа 107, который открывается и пропускает с входа 110 первого переключателя 13 на первый вход седьмого сумматора 108 сигнал о значении штрафа. Величина штрафа подается на вход 110 первого переключателя 13 с выхода блока 10 задания штрафа, где формируется на выходе задэтчика, входящего в состав этого блока. Шестой ключ 106 закрыт и поэтому на втором входе седьмого сумматора 108 сигнал отсутствует. На выходе седьмого

сумматора 108 формируется сигнал, равный по величине сигналу на его первом входе. Этот сигнал подается на вход 112 первого переключателя 13, откуда поступает на вход 74 четвертого блока 23 памяти (фиг.6), где происходит запись значения штрафа в HI,-и второй ячейке памяти.

После формирования на первом выходе командного блока 9 последователь

0

с

.

5 Q

5

0

5

0

5

24

ности сигналов га, 1,2,3...(п-1) и расчета в системе оптимизации всех п-1 вариантов шагов оптимизации в ячейках памяти пятого блока 24 памяти записаны п-1 рассчитанных значений факторов X , а в ячейках памяти четвертого блока 23 памяти записаны соответствующие им оценки успешности шага с учетом ограничений. На третьем выходе командного блока 9 формирую ется сигнал, поступающий на вход ана-t лизатора 14 успешности шага, в котором выбирается наибольшая из всех оценок Q. Сигнач о выбранном значении Q поступает на векторный вход блока 22 ключей, на другой вход которого с выхода пятого блока 24 памяти поданы

все рассчитанные значения выход

X

N+-I

На

блока 22 ключей поступает значение X , которое соответствует выбранному наибольшему Q. Это значение X через вход второго переключателя 27 поступает на вход объекта 1, где реализуется с ошибкой Z. На втором выходе командного блока 9 формируется последовательность сигналов 1,2,3...п. Начинается следующий шаг оптимизации, реализуемый аналогично первому.

Это происходит следующим образом.

После генерации последовательности сигналов т, 1э2,3.,.(п-1) вторым мультивибратором 56 командного блока 9 (фиг.4) второй счетчик 55, настроенный по модулю ()3 обнуляется и формирует на выходе сигнал, который подается на входы второго 54 и третьего 58 звеньев запаздывания, второй вход второго мультивибратора 56, вы-- ход 60 командного блока 9 (см.фиг.20). Этот сигнал останавливает второй мультивибратор 56, через второе звено 54 запаздывания запускает первый мультивибратор 53, а через третье звено 58 запаздывания обнуляет второй интегратор 57. Первый мультивибратор 53 с гпериодичностью $ начинает генерировать п импульгов, которые подаются на вход первого счетчика 51 и первый вход первого интегратора 52, с выхода которого последовательность сигналов 1, 293..,,п поступает на выход 61 командного блока 9 (временная диаграмма работы командного блока приведена на фиг.20). С выхода 60 командного блока 9 сигнал, сформированный на выходе второго счетчика 55, поступает на вход 117 анализатора 14 успешности шага (фиг.13), на вход 116 которого с

ыхода 75 четвертого блока 23 памяти (фиг. 6) поданы все рассчитанные значеия оценок успешности Ъага Q. С входа

116анализатора 14 успешности шага (фиг.13) величины Q поступают на вхоы второй схемы 113 выбора максимальной из нескольких переменных и на первые входы четвертых компараторов 114. На выходе второй схемы 113 выбора мак-|л симальной из нескольких переменных формируется сигнал, равный по величине наибольшему значению оценки успешности шага Q. Этот сигнал подается на

вторые входы четвертых компараторов j 114, на выходе одного из которых, при совпадении по величине сигналов на. первом и втором входах, формируется сигнал, поступающий на вход одного из седьмых ключей 115. Сигнал с входа

117анализатора успешности шага постуает на управляющие входы седьмых ключей 115, которые открываются, и сигнал о наибольшем значении Q проходит на выход 118. С выхода 118 анализатора

14 успешности шага сигнал поступает на вход 120 блока 22 ключей (фиг,14), откуда подается на управляющий вход одной из четвертых групп 119 ключей. Этот сигнал поступает на управляющие зо входы десятых ключей 132 (фиг.16), которые входят в состав четвертых групп ключей. Одна из четвертых групп 119 ключей открывается и пропускает с входа 121 на выход 122 блока 22 ключей рассчитанное значение Х1 , соответствующее выбранному в анализаторе 14 успешности шага значению Q. Выб- X Nt1 с выхода 1 22 бло20

25

35

ранное значение

ка 22 ключей подается на вход 130 второго переключателя 27 (фиг.15), откуда через открытые восьмые ключи 125 поступает на первые входы восьмых сумматоров 123, на вторых входах которых сигнал отсутствует, так как девятые ключи 124 закрыты. На выходах восьмых сумматоров 123 формируются сигналы, равные по величине сигналам на их пер вых входах.С выходов восьмых суммато40

45

ров 123 значение поступает на выход 131 второго переключателя 27, от куда подается на вход объекта 1. На входе объекта 1 значение X реализуется с ошибкой Z, и начинается следующий этап оптимизации, реализуемый аналогично первому.

Формула изобретен, ия Система оптимизации режимов работы объекта, содержащая датчик, блок за 50

55

|л

j

зо 20

25

35

40

45

50

5

дания ограничений, первый, второй и третий блоки памяти, первый, второй и третий сумматоры, первый к второй блоки сравнения, командный блок, анализатор выходного сигнала объекта, анализатор входного сигнала объекта, первый переключатель, блок планирования эксперимента и элемент И, причем первый выход объекта связан с входом датчика, выход которого связан с первым входом второгс блока памяти, первый выход которого связан с первым входом второго сумматора и первым входом анализатора выходного сигнала объекта, выход которого связан с вторым входом второго сумматора, выход которого связан с первым входом первого переключателя, выход первого блока памяти связан с первым входом первого сумматора и первым входом анализатора входного сигнала объекта, выход которого связан с вторым входом первого сумматора, выход которого . связан с первым входом первого блока сравнения, второй вход которого связан с первым выходом блока задания ограничений, а выход - с первым входом элемента И, выход которого связан с управляющим входом первого переключателя, а второй вход - с выходом второго блока сравнения, первый вход которого связан с вторым выходом блока задания ограничений, а второй вход - с выходом третьего сумматора, первый вход которого связан с выходом третьего блока памяти, первый выход командного блока связан с первыми входами анализаторов входного и выходного сигналов объекта, а второй выход с вторым входом второго и первыми входами первого и третьего блоков памятиг отличающаяся тем, что, с целью повышения точности системы, в нее введены первый и второй блоки датчиков, четвертый и пятый блоки памяти, блок ранжирования, блок ключей, блок задания штрафа, анализатор вспомогательного выходного сигнала объекта , второй переключатель и анализатор успешности шага, первый вход которого связан с выходом четвертого блока памяти, а второй вход - с третьим выходом командного блока, первый выход которого связан с первыми входами четвертого, пятого блоков памяти и анализатора вспомогательного выходного сигнала объекта, второй вход пятого блока памяти связан с выходом

первого сумматора, а выход - с первым входом блока ключей, второй вход которого связан с выходом анализатора успешности тага, а выход - с первым входом второго переключателя, второй вход которого связан с выходом блока планирования эксперимента, выход второго переключателя связан с входом объектаj второй вход четвертого бло- ка .памяти свясан с выходом первого переключателя, второй вход которого связан с выходом блока задания штрафа, первый выход командного блока связан с первым входом анализатора вспоног атоттьно о выходного сигнала ofi jc т -, лсрро о блока пдг - иков

ТВ

3zi

4

связан с входом объекта, а вы- ход с вторым входом первого блока памяти, третий вход которого связан с выходом блока ранжирования и соответственно с третьим и вторым входами второго и третьего блока памяти, выход которого связан также с вторым входом анализатора вспомогательного выходного сигнала объекта, выход которого связан с вторым входом третьего сумматора 9 вход блока ранжирования связан с вторым выходом второго блока памяти, третий вход третьего блока памяти связан с выходом второго блог ка датчиков, вход которой связан с вторым выходом объекта.

30

ЈL

/5

т

кДПР

Я

if

ЯП

if

.«

&

r

X

2 гпф

K -ofif

45 Й

к

if

tt

к

zc

l 1

zc

-o if

СГ

-П

4tL

lЈ89€9I

f

47

5,

о

I

//,

ЗЕ

о«

#оЖ

2

5J©

21

3LL

&

ей

ДР

-o.S4

Фи§.Ю

1J, 2

;о;

wv

2 ШоЈ

I

J±

106

IL

Ц

Г 2

Ю8

т

Фм.12

Фив. 1

Фиг.1§

Фиг.18

Авторы

Даты

1991-03-23—Публикация

1989-01-19—Подача