1

(21)4666907/24

(22)27оОЗо89

(46) 07,04.91 Бншо № 13

(71)Ленинградский электротехнический институт им, ВоИаУльянова (Ленина)

(72)В.И«Варшавский, А Ю„Кондратьев, НоМ,, Кравченко и Б Б Мараховский

(53)681„325.5(088о8)

(56)Авторское свидетельство СССР № 947854, кл„ G 06 F 7/04, 19800

Авторское свидетельство СССР № 1193659, ют G 06 F 7/04, 1985,

(54)УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВУХ га-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ

(57)Изобретение относится к автоматике и вычислительной технике Цель изобретения - повышение быстродействия и уменьшение аппаратурных затрат

Устройство содержит (га+1)/2, ячеек сравнения (ЯС) первого яруса и (т+1)/ /2-1 ЯС четных и нечетных (кроме первого) ярусов, входы прямых и инверсных значений разрядов первого числа, прямых и инверсных значений разрядов второго числа ЯС первого яруса содержит шестнадцать МОП-транзисторов (Т) р-типа и двенадцать Т n-типа. ЯС четных и нечетных (кроме первого)ярусов содержит семь (Т) р-типа (n-типа), шесть Т р-типа (n-v типа) входы и выходы ЯС четных и нечетных (кроме первого) ярусов вырабатывают на выходах код 011, если в анализируемых ими разрядах , код 110, если А В, код 101, если . ЯС четных ярусов вырабатывает инверсные значения этих кодов 4 ил

Ј

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 32-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2023 |

|

RU2800768C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

| Устройство для сравнения двух @ -разрядных двоичных чисел | 1984 |

|

SU1193659A1 |

| Устройство для сравнения двух @ -разрядных двоичных чисел | 1988 |

|

SU1594683A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

Изобретение относится к автоматике и вычислительной технике

Цель изобретения - повышение быстродействия и уменьшение аппаратурных затрат о

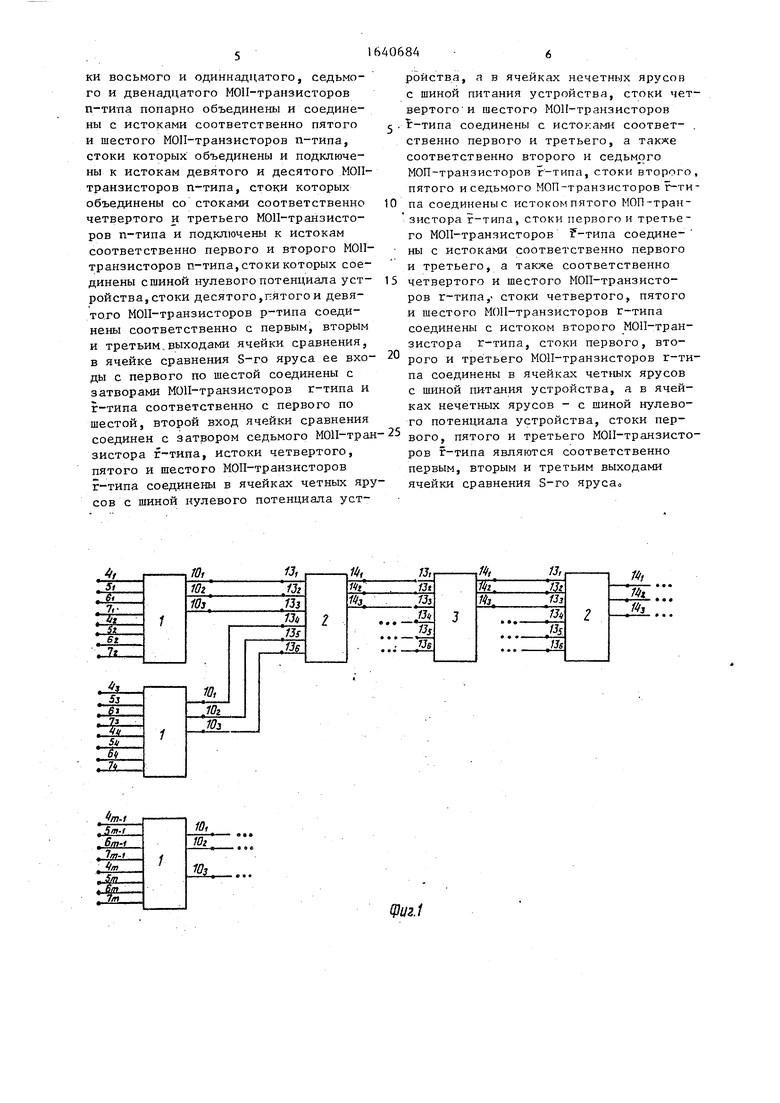

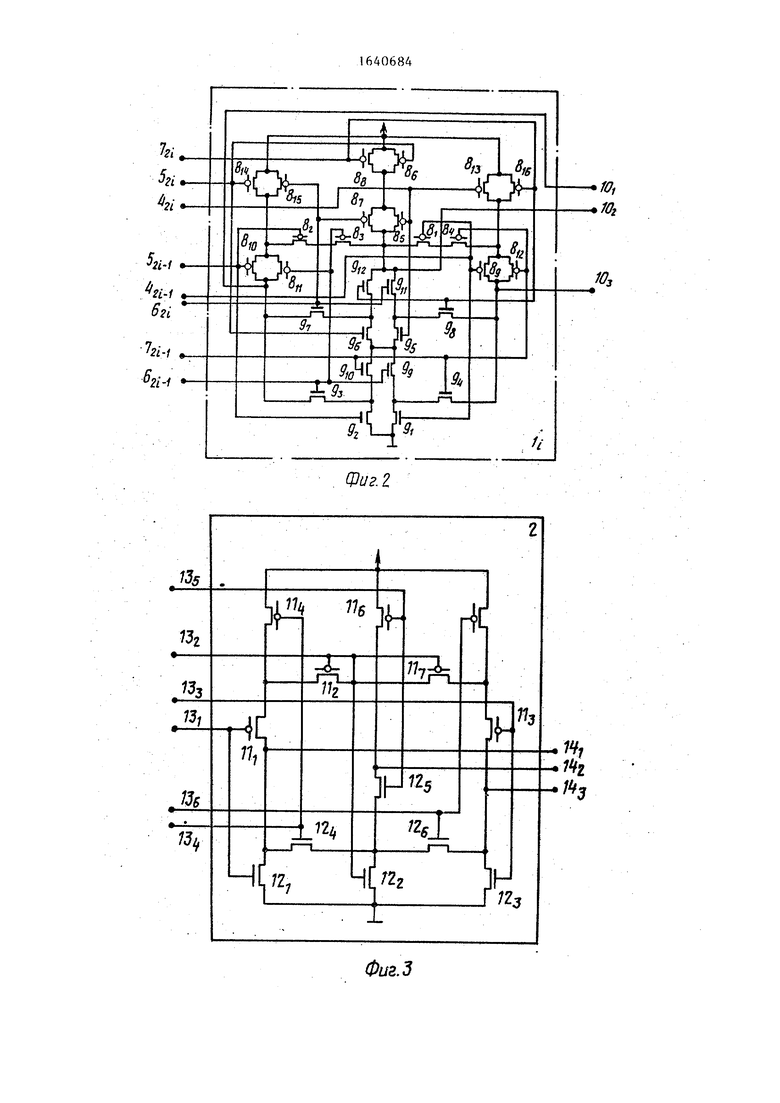

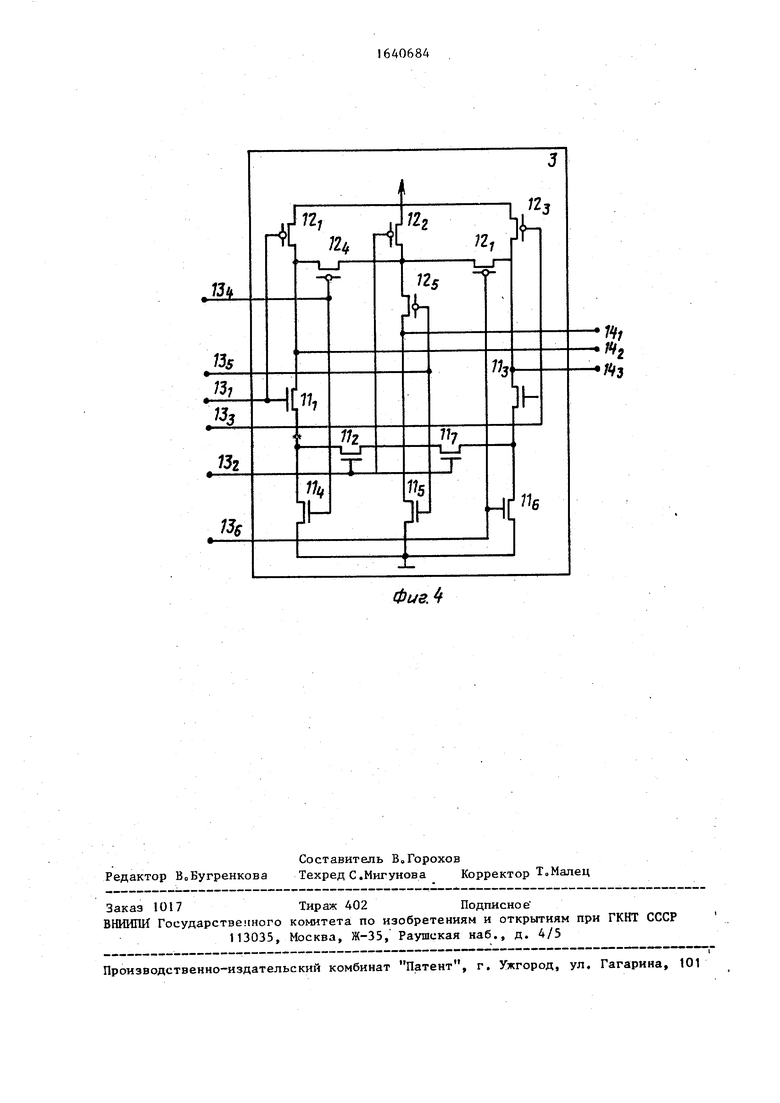

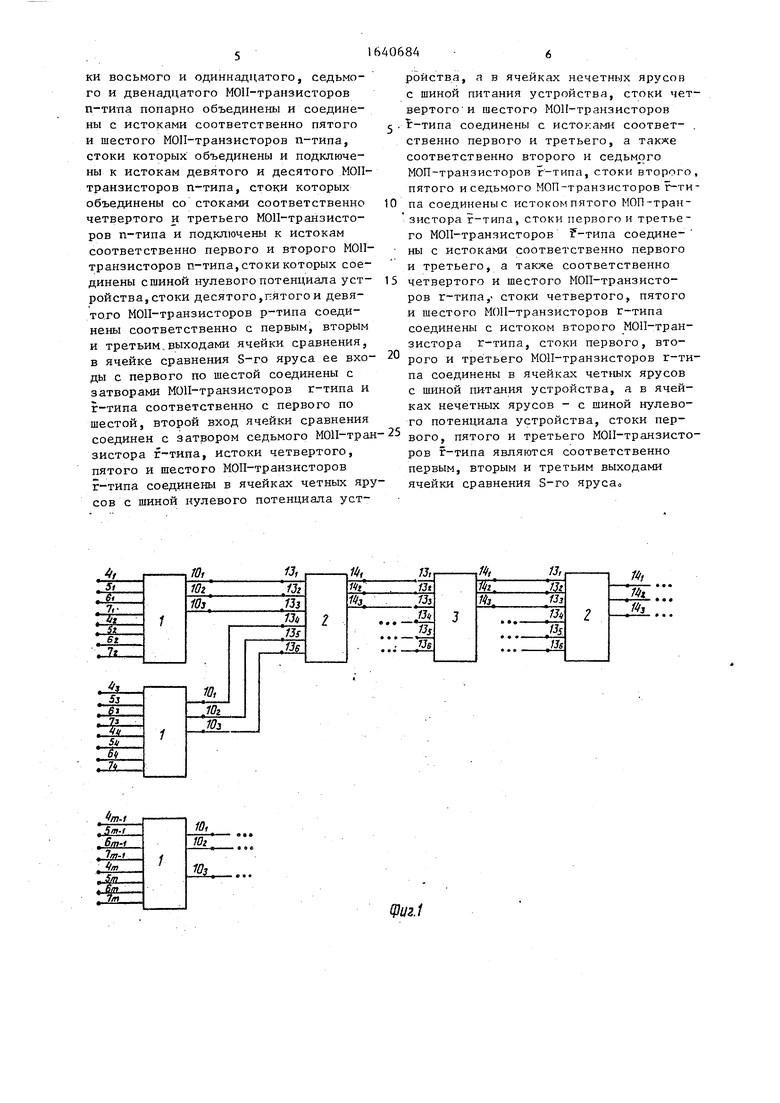

На фиг о1 приведена схема устройства; на фиг02 - 4 - схемы ячеек сравнения первого яруса, нечетных (кроме первого) и четных ярусов

Устройство содержит Ј(т+1)/2 ячеек 1 сравнения первого яруса (где х - ближайшее не большее х целое число) и Ј(та+1)/2-13 ячеек сравнения четных 2 и нечетных (кроме первого) 3 ярусов, входы прямых 4 - 4„и инверсных 5 - 5 „, значений разрядов первого числа, прямых 6 - bm и инверсных 7т значений разрядов второго числа Ячейка первого яруса 1 содержит шестнадцать МОП-транзисторов р-типа 8,6 и двенадцать МОП- транзисторов п-типа 9 f - 9 , выходы 10i - Юзо Ячейка четных (нечетных кроме первого) содержат семь МОП- транзисторов р-типа (n-типа) ll -ll-jr шесть МОП-транзисторов n-типа (р-типа) 12,- 12, входы 13 -136, выходы 14 , - 143

Устройство работает следующим образом.

На входы 4,1, 5,, 6;, 7,1 (i « 1, 2,oeo,m) устройства поступают соответственно прямые и инверсные значе-i ния 1-го разряда первого числа, aj и

OS Ј

О

os оо

a .J - прямое и инверсное значения 1-г разряда второго числа b - и Ь,- (первый разряд является старшим)

Каждая j-я ячейка первого яруса l| (j l,2,ooo Ј(га+1)/2) анализирует соотношение (2j-1)-го и 2j-ro разрядов сравниваемых чисел А и В и вырабатывает на своих выходах 10 -10} код 011, если в этих разрядах А «с. В, код ПО, если А В и код -101, если Каждая ячейка S-ro яруса (, 3,o, (m-l)J +1) объединяет результаты сравнения, выработанные двумя смежными ячейками предыдущего яру са При этом коды на выходах 10 - 10 ячеек 3 нечетных ярусов интегрируются так же, как и коды на выхо- дах ячеек 1 первого яруса, а коды на выходах 10, - 10 ) ячеек 2 четных ярусов инверсны кодам на выходах ячеек 1 и 30 Код на выходах 10 - Юз ячейки последнего, log,(m-l ) + 1-го яруса, является результатом сравнени чисел А и В и интерпретируется в за- висимости от того, является ли этот ярус четным или нечетным

Если числа на входы устройства не поданы (т.е0 на них присутствуют потенциалы логического нуля), то на вы ходах 10 1 - Юз ячеек 1 формируется код 111с Если на какие-либо входы 13 , - 13 з или 1 34. 13 ячеек 2 или 3 поступает этот код, то на выходах Ю | - Юз этих ячеек формируется тот же коде Таким образом, присутствие кода 111 на выходах устройства сигнализирует, что процесс сравнения чисел еще не закончено

ормула изобретения

Устройство для сравнения двух га- разрядных двоичных чисел, содержащее

|2 (9) Ч ячеек сравнения (xj ближайшее не больше хцелое число) ,при- чем входы прямых и инверсных значений (21-1 )-х разрядов первого ивторого чисел устройства ( 2,осо, L(m+1)/2J), входы прямыхи инверсных значений 2i-x разрядов первого и второго чисел устройства соединены с входами соответственно с первого по восьмой 1-й ячейки сравнения первого яруса, входы с первого по шестой j-й ячейки сравнения S-ro яруса (j - 1,2,„„,,т/253, S 2, 3,00,,Clogz(m-l) +1)подклю- чены к выходам соответственно с пер

вого по третий (2j-l)-ft и 2j-u ячеек сравнения (S-l)-ro яруса, первый, второй и третий выходы ячейки сравнения ( )J + I )-го яруса являются выходами устройства, отличающееся тем, что, с целью повышения быстродействия и уменьшения аппаратурных затрат, каждая ячейка сравнения первого яруса содержит двенадцать МОП-транзисторов n-типа и шестнадцать МОП-транзисторов р-типа, каждая ячейка сравнения S-ro яруса содержит шесть МОП-транзисторов г-типа и семь транзисторов f-типа, где

(г, г) .

(р,п) - для S - четного (п,р) - для S -нечетного

$ 0 5

д

0

5

50

5

причем в ячейке первого яруса входы с первого по восьмой соединены с затворами МОП-транзисторов Р-типа соответственно с первого по восьмой и с девятого по шестнадцатый и с затворами МОП-транзисторов n-типа соответственно с первого по восьмой, третий, четвертый, седьмой и восьмой входы соединены с затворами МОП-транзисторов р-типа соответственно с девятого по двенадцатый, истоки шестого, восьмого, четырнадцатого, пятнадцатого, тринадцатого и шестнадцатого МОП-транзисторов Р-типа подключены к шине питания устройства, а их стоки попарно объединены, истоки и стоки девятого и десятого МОП-транзисторов р-типа объединены соответственно с истоками и стоками соответственно двенадцатого и одиннадцатого МОП- транзисторов р-типа, стоки тринадцатого и четырнадцатого МОП-транзисторов р-типа подключены к истокам соответственно девятого и десятого, а также четвертого и второго МОП-транзисторов р-типа, стоки четвертого и второго МОП-транзисторов р-типа соединены с истоками соответственно первого и третьего МОП-транзисторов р-типа, стоки которых подключены к истокам одиннадцатого и двенадцатого МОП-транзисторов n-типа и к стокам пятого и седьмого МОП-транзисторов р-типа, истоки которых подключены к стоку шестого МОП-транзистора р-тнпа, стоки девятого и десятого МОП-транзисторов р-типа соединены с истоками соответственно восьмого и седьмого, а также соответственно четвертого и третьего МОП-транзисторов n-типа, стоки восьмого и одиннадцатого, седьмого и двенадцатого МОП-транзисторов п-титт попарно объединены и соединены с истоками соответственно пятого и шестого МОН-транзисторов п-типа, стоки которых объединены и подключены к истокам девятого и десятого МОП- транзисторов n-типа, стоки которых объединены со стоками соответственно четвертого и третьего МОП-транзисторов n-типа и подключены к истокам соответственно первого и второго МОП- транзисторов n-типа,стоки которых соединены с шиной нулевого потенциала уст- 15 четвертого и шестого МОП-транзисто- ройства,стоки десятого,пятого и девя- ров r-типа,- стоки четвертого, пятого

того МОП-транзисторов р-типа соединены соответственно с первым, вторым и третьим выходами ячейки сравнения, в ячейке сравнения S-ro яруса ее вхо ды с первого по шестой соединены с затворами МОП-транзисторов r-типа и r-типа соответственно с первого по шестой, второй вход ячейки сравнения

- 20

и шестого МОП-транзисторов г-типа соединены с истоком второго МОП-транзистора r-типа, стоки первого, второго и третьего МОП-транзисторов г-типа соединены в ячейках четных ярусов с шиной питания устройства, а в ячейках нечетных ярусов - с шиной нулевого потенциала устройства, стоки персоединен с затвором седьмого МОП-тран 25 вого пятого и третьего МОП-транзисто- зистора r-типа, истоки четвертого, ров f-типа являются соответственно пятого и шестого МОП-транзисторов первым, вторым и третьим выходами r-типа соединены в ячейках четных яру- ячейки сравнения S-ro яруса., сов с шиной нулевого потенциала устроиства, а в ячейках нечетных ярусов с шиной питания устройства, стоки четвертого и шестого МОП-транзисторов

t-типа соединены с соответственно первого и третьего, а также соответственно второго и седьмого МОП-транзисторов r-типа, стоки второго, пятого и седьмого МОП-транзисторов г-типа соединены с истоком пятого МОП-транзистора г-типа, стоки первого и третьего МОП-транзисторов f-типа соединены с истоками соответственно первого и третьего, а также соответственно

20

и шестого МОП-транзисторов г-типа соединены с истоком второго МОП-транзистора r-типа, стоки первого, второго и третьего МОП-транзисторов г-типа соединены в ячейках четных ярусов с шиной питания устройства, а в ячейках нечетных ярусов - с шиной нулевого потенциала устройства, стоки пер25 вого пятого и третьего МОП-транзисто- ров f-типа являются соответственно первым, вторым и третьим выходами ячейки сравнения S-ro яруса.,

Јы411Ы

2 гпф

wow

Vh ,

%

ФигЛ

Авторы

Даты

1991-04-07—Публикация

1989-03-27—Подача