1

Изобретение относится к автома- , тике и вычислительной технике и может быть использовано при построении , асинхронных устройств приема и передачи информации.

Целью изобретения является упрощение регистра, выполненного на КМДП-транзисторах.

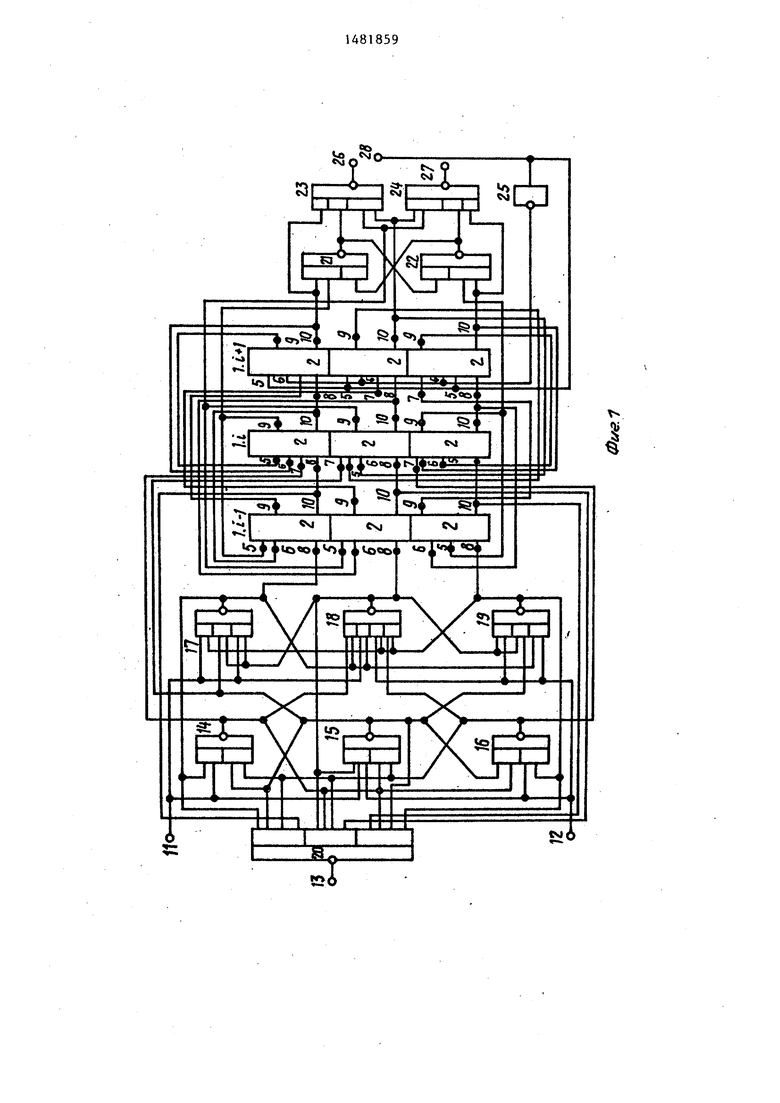

На фиг„ 1 приведена схема асинхронного последовательного регистра и схемы соединения его с источником и приемником информации; на фиг. 2 и 3 - схемы 1-й () и первой ячеек памяти.

Регистр содержит ячейки 1 памяти, каждая из которых состоит из трех симметричных цепочек (частей) 2. Каждая цепочка состоит из логического элемента 3 и инвертора 4. Логи ческие элементы i-й() ячейки памяти содержат пять транзисторов п-типа 3.1-3.5 и шесть транзисторов р-типа 3.6-3,11. Ячейки памяти имеют три управляющих входа-5-7, соответствующие затвору пятого транзистора 3.10 р-типа, стоку четвертого транзистора 3.4 n-типа, затвору пятого транзистора 3.5 n-типа, информационный вход 8, соответствующий затвору третьего транзистора 3.3 п-типа, инверсный 9 и прямой 10 информационные выходы, соответствующие входу и выходу инверторов 4. Б логических элементах первой ячейки памяти пятый транзистор 3.5 n-типа и шестой транзистор 3.И р-типа отсутствуют. Отсутствует также третий управляющий вход 7.

оо

00

ел

со

Регистр имеет также инверсный 11 и прямой 12 информационные входы, управляющий вход 13 записи, одиннадцать элементов И-ИЛИ-НЕ 14-24, инвертор 25, инверсный 26 и прямой 27 информационные выходы и управляющий вход 28 записи.

Асинхронный последовательный регистр работает следующим образом.

| Наборы значений на входах 11 и 12 регистра соответствуют: 10 - источник передает ноль, 01 - источник передает единицу, 11 - источник не переда- ет информации и регистр, набор 00 - запрещен.

Наборы значений на выходах 26 и 27 регистра соответствуют: 01 - регистр передает в приемник ноль, 10 - ре- Тистр передает в приемник единицу,- 00 - регистр не передает в приемник информацию, состояние 11 в процессе работы регистра не возникает.

Состояние ячейки 1 (значения на информационных выходах 9 и 10) соответствует: 001 - в ячейке записан ноль, 100 - в ячейке записана единица, 010 - значение разряда совпадает со значением предыдущего разряда, 000 - информация в ячейке стерта. Приведенное кодирование состояний ячейки означает, что первые и третьи цепочки 2 ячеек 1 регистра образуют каналы, за которыми закреплены соответственно единичное и нулевое значения разрядов сдвигаемого кода, а вторые цепочки 2 этих ячеек 1 - канал для передачи признака совпадения значения очередного разряда сдвигаемого кода со значением предыдущего разряда.

Таким образом, если соседние разряды сдвигаемого кода имеют различное значение, соответствующие этим разрядам единицы продвигаются по различным каналам - первому и третьему, если эти разряды имеют одинаковое значение, соответствующие им единицы продвигаются по первому (третьему) и второму каналам. Этим обеспечивается продвижение единиц.соответствую- щих соседним разрядам сдвигаемого кода, вплотную друг за другом, что повышает быстродействие регистра по сравнению с быстродействием одного канала, так как в последнем единицы продвигаются с интервалом не меньшим, чем в одну ячейку. В результате время между записью в i-ю

5

0

5

0

5

0

5

0

5

ячейку 1 регистра соседних разрядов сдвигаемого кода в предлагаемом асинхронном регистр-е составляет 4 Т. Указанную дисциплину распределения информации по каналам регистра обеспечивает схема соединения его с источником информации. В исходном состоянии на информационных входах регистра зафиксирован набор 11. При этом трехстабильный триггер, образованный элементами 17-19, находится в фазе хранения информации (пусть, например, в него записан набор 010), в соответствии с этим на выходах элементов 14-16 устанавливается набор 101 и первая ячейка регистра хранит информацию, записанную в трехстабильном триггере на элементах 17-19, т.е. набор 010, на выходе элемента 20 (управляющем выходе регистра 13) при этом уста- навливает я значение О, Пусть во всех остальных ячейках регистра информация стерта (т.е. они находятся в состоянии 000), а на управляющем входе 28 зафиксирована 1. Допустим, что на одном из информационных входов 11 или 12 появляется значение О. Тогда трехстабильный триггер на элементах 17-19 переключается в новое состояние 100 или 001 соответственно. Переключение этого триггера вызывает изменение значения на управляющем выходе регистра 13 с О на 1, что является индикацией окончания фазы записи информации из источника. После этого источник вновь устанавливает на информационных входах регистра 11, 12 значение 11, что вызывает перепись информации из триггера на элементах 17-19 в триггер на элементах 14-16. Затем информация из первой ячейки регистра переписывается во вторую ячейку, после чего в первой ячейке сначала информация стирается (состояние 000), что разрешает перепись информации из второй ячейки регистра в третью, а потом ячейка переходит в состояние, соответствующее информации, записанной в триггере на элементах 17-18, т.е. 100 или 001. Запись информации в первую ячейку регистра и в трехстабильный триггер на элементах 14-16 вызывает изменение значения на выходе 13 регистра1 с 1 на О. При этом схема соединения регистра с источником оказывается в состоянии, аналогичном исходному, с отличным от него состоянием трехстабильных триггеров на элементах 14-16 и 17-19.

Если теперь значение О появляется на другом информационном входе регистра (в отличие от предыдущего случая), переключение схемы соединения с источником происходит аналогично описанному, и после гашения источником информации на входах в первую ячейку регистра записывается значение очередного -разряда сдвигаемого кода, отличное от значения предыдущего разряда. Если значение О появляется на том же информационном входе регистра, что и в предыдущем случае, трехстабильный триггер на элементах 17-19 устанавливается в состояние 010, что вызывает запись единицы во вторую цепочку 2 первой ячейки 1 регистра после гашения истоником информации на входах регистра. Запись единицы во- вторую цепочку 2 ячейки 1 означает, что в соответствии с кодированием, совпадение значений очередного и предыдущего разрядов. Введение перекрестных связей между соседними цепочками ячейки препятствует записи информации в любую цепочку ячейке, уже хранящей какую-либо информацию, что обеспечивет правильное функционирование регистра при любых задержках его элементов и при любом их соотношении.

Для преобразования информации, записанной в регистр, в соответствии с описанной дисциплиной, в парафазную служат элементы 23, 24 и 21, 22. Последние два образуют RS-триггер, который устанавливается в нулевое (единичное) состояние при появлении значения 1 на выходе 10 первой (третьей) цепочки 2 предпоследней ячейки и значения 1 на выходе 9 первой (третьей) цепочки 2 предпоследней ячейки регистра. Значение 1 может по- явиться на выходе 10 одной из трех цепочек 2 последней ячейки 1 регистра при наличии значения 1 на его управляющем входе 28. При этом, если значение 1 появляется на выходе 10 первой или третьей цепочки 2 последней ячейки 1, на выходах элементов 23 и 24 устанавливаются значения 1 в соответствии с состоянием RS-триг- гера, образованного элементами 21 и 22. Если значение 1 появляется

на выходе 10 второй цепочки последней и выходе 9 второй цепочки предпослед-. ней ячеек, то на выходах элементов 23 и 24 устанавливаются значения 1 независимо от состояния этого RS-триг- гера. После того, как на выходах 23 и 24 появляются значения 1, т.е. эти значения появляются на информационных выходах 26 и 27, на управляющем входе 28 может быть установлено значение О, которое вызывает стирание информации в последней ячейке 1 регистра и появление на

5 выходах 10 всех ее цепочек 2 значения НО. В результате этого на выходе одного из элементов 23, 24 (т.е. на одном из информационных выходов 26 или 27 регистра) появляется зна0 чение О в соответствии с состоянием RS-триггера, образованного элементами 21 и 22.

Для установки регистра в исходное состояние приемник перед началом ра5 боты при зафиксированном значении

II на информационных входах регистра осуществляет последовательный прием информации из регистра, пока все ячейки за исключением первой, не

0 будут очищены, прием информации из регистра может быть произведен не более чем п раз, где п - число ячеек регистра. Информация, записанная в первую ячейку регистра, в началь5 ном состоянии соответствует состоянию трехстабильного триггера на элементах 14-16 и не соответствует никакой информации, передаваемой источником в регистр, поэтому в про0 цессе работы с регистром, приемник первую порцию информации, принятую после начала передачи информации источником, игнорирует так же, как и те, что приняты им из регистра в

5 процессе его начальной установки. Регистр может быть использован для согласования последовательных устройств, между которыми передается информация, обрамленная стартовым и

o стоповым битами

Быстродействие регистра без учета схемы соединения его с источником составляет 4,где t - задержка КМОП-Транзистора, схема соединения

5 вносит задержку в работу регистра, , с учетом которой его быстродействие (время между записью соседних разрядов сдвигаемого кода) составляет 10J1, такое же, как в известном регистре.

Оценивая затраты оборудования числом транзисторов на реализацию ячейки регистра, получим 39 КМОП-тран- зисторов для предложенного регистра и 54 КМОП-транзистора для известного

Формула изобретения

Асинхронный последовательный регистр, содержащий ячейки памяти, каждая из которых состоит из трех инверторов и трех логических элементов, причем логические элементы каж дой ячейки памяти, кроме первой, содержат пять транзисторов n-типа и шесть транзисторов р-типа, а логические элементы первой ячейки памяти содержат четыре транзистора n-типа и

пять транзисторов р-типа, причем в каждом логическом элементе каждой ячейки памяти сток первого транзистора n-типа соединен с истоком второго транзистора n-типа, сток которого .соединен с истоком третьего тразистора n-типа, исток первого транзистора n-типа каждого логического элемента каждой ячейки памяти соединен с входом соответствующего инвертора данной ячейки памяти, затворы первого и второго транзисторов п-ти- па соединены соответственно с затворами первого и второго транзисторов р-типа, а также с входами других инверторов данной ячейки памяти соответственно, затвор третьего транзистора n-типа соединен с затвором третьего транзистора р-типа, .сток перво- го транзистора р-типа соединен с истоком первого транзистора п-типа и со стоками второго и пятого транзисторов р-типа, а его исток - с шиной питания регистра и с истоками второго, третьего и пятого транзисторов р -типа, затворы четвертых транзистог- ров п- и р-типов соединены с выходом соответствующего инвертора, в каждом логическом элементе каждой ячейки памяти,- кроме первой, сток третьего транзистора n-типа соединен с истоком пятого транзистора n-типа, затвор пятого транзистора р-типа каждого логического элемента каждой ячейки памяти, кроме последней, соединен с входом соответствующего инвертора последующей ячейки памяти, отличающийся тем, что( с целью упрощения регистра, он содержит одиннадцать элементов И-ИЛИ-Н

и инвертор, причем первый и второй входы первой группы И первого, второго и третьего элементов И-ИЛИ-НЕ

соединены соответственно с выходами второго и третьего, первого и третьего и первого и второго элементов И-ИЛИ-НЕ, выходы четвертого, пятого и шестого элементов И-ИЛИ-НЕ соединены соответственно с первыми входами вторых групп И первого, второго и третьего элементов И-ИЛИ-НЕ, а также с первыми входами первой, второй и третьей групп И седьмого элемента

И-ИЛИ-НЕ соответственно, выходы четвертого и шестого элементов И-ИЛИ-НЕ соединены с первыми входами первых групп И шестого и четвертого элементов И-ИЛИ-НЕ, выход пятого элемента

0 И-ИЛИ-НЕ соединен с первыми входами второй и третьей групп И четвертого и шестого элементов И-ИЛИ-НЕ, вторые входы вторых групп И которых соединены с выходом второго элемента

5 И-ИЛИ-НЕ и с вторыми -входами первой и третьей групп И седьмого элемента И-ИЛИ-НЕ, выход четвертого элемента И-ИЛИ-НЕ соединен с первыми входами первой и второй групп И пятого эле0 мента И-ИЛИ-НЕ, второй вход второй группы И которого соединен с выходом первого элемента И-ИЛИ-НЕ, а также с вторым и третьим входами второй и третьей групп И седьмого элемента

5 И-ИЛИ-НЕ, выход шестого элемента И-ИЛИ-НЕ соединен с первыми входами третьей и четвертой групп И пятого элемента И-ИЛИ-НЕ, второй вход третьей группы которого соединен с вы0 ходом третьего элемента И-ИЛИ-НЕ и третьими входами второй и первой групп И седьмого элемента И-ИЛИ-НЕ, вторые входы первой и третьей групп И четвертого, первой группы И пято5 го, второй группы И первого и второго элементов И-ИЛИ-НЕ являются инверсным, а вторые входы четвертой . группы И пятого, первой и третьей групп И шестого, второй группы И третьего и третьи входы второй группы И второго элементов И-ИЛИ-НЕ - прямым информационными входами регистра, выходы инверторов первой ячейки памяти регистра соединены соответственно с четвертыми входами первой, второй и третьей групп И седьмого элемента И-ИЛИ-НЕ, выход которого является управляющим выходом записи регистра, в каждом логическом

0

5

10

91481859

элементе каждой ячейки плмяти, кро- ме первой, затвор пятого транзистора n-типа соединен с затвором шестого транзистора р-типа, исток и сток которого соединены соответственно с истоком и Стоком третьего транзистора р-типа, исток четвертого транзистора n-типа каждого логического элемента каждой ячейки памяти соединен со стоком второго транзистора n-типа, а его сток в каждом логическом элементе каждой ячейки памяти, кроме первой, - со стоком пятого транзистора n-типа, а в каждом логическом элементе первой ячейки памяти - со стоком третьего транзистора n-типа, сток четвертого транзистора n-типа каждого логического элемента каждой ячейки памяти, кроме последней, соединен с выходом соответствующего инвертора последующей ячейки памяти, затвор третьего транзистора -типа каждого логического элемента каждой ячейки памяти, кроме первой, соединен с выходом соответствующего инвертора предыдущей ячейки памяти, затвор пятого транзистора n-типа кажого логического элемента i-й ячейки

15

20

25

памяти, ,п, соединен с входом соответствующего инвертора (i-2)-и ячейки памяти, в каждом логическом элементе каждой ячейки памяти сток четвертого транзистора р-типа соединен со стоком первого транзистора р-типа, а исток - со стоком третьего транзистора р-типа, выход четвертого, пятого и шестого элементов И-ИЛИ-НЕ соединены соответственно с затворами третьих транзисторов n-ти- па первого, второго и третьего логических элементов первой ячейки памят соответственно, выходы первого, второго и третьего элементов И-ИЛИ-НЕ, соединены соответственно с затворами

10

0

5

0

5

5

0 Q

пятых транзисторов n-типа первого, второго и третьего логических элемен- тов второй ячейки памяти, выходы восьмого и девятого элементов И-ИЛИ- НЕ соединены с первыми входами первой группы И девятого и восьмого элементов И-ИЛИ-НЕ, первый и второй входы второй группы И восьмого элемента И-ИЛИ-НЕ соединены с выходом первого инвертора последней ячейки памяти и входом первого инвертора предпоследней ячейки памяти, а первый и второй входы второй группы И девятого элемента И-ИЛИ-НЕ - с выходом третьего инвертора последней ячейки памяти и с входом третьего инвертора предпоследней ячейки памяти, первые входы первой и второй групп И десятого элемента И-ИЛИ-НЕ соединены с первым входом второй группы И и с выходом восьмого элемента И-ИЛИ-НЕ соответственно,а первые входы второй группы И одиннадцатого элемента И-ИЛИ-НЕ соединены с первым входом второй группы И и выходом девятого элемента И-ИЛИ-НЕ соответственно, выходы десятого и одиннадцатого элементов И-ИЛИ-НЕ являются соответственно инверсным и прямым информационными выходами регистра, выход второго инвертора последней и вход второго инвертора предпоследней ячеек памяти соединены соответственно с первым и вторым входами третьих групп И десятого и одиннадцатого элементов И-КЛИ-НЕ, вход инвертора соединен со стоками четвертых транзисторов n-типа логических элементов последней ячейки памяти и является управляющим входом считывания регистра, а выход инвертора - с затворами пятых транзисторов р-типа логических элементов последней ячейки памяти.

о ш оо

го

г

Ф-О

tl

S 678

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1494041A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Параллельный асинхронный регистр на КМДП-транзисторах | 1989 |

|

SU1665405A1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1462422A1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1607016A1 |

| Параллельный асинхронный регистр на МДП-транзисторах | 1988 |

|

SU1615807A1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1624530A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

Изобретение относится к области вычислительной техники и может быть использовано в асинхронных устройствах приема и передачи информации. Целью изобретения является упрощение регистра, выполненного на КМДП-транзисторах. Для достижения этой цели в состав регистра введены одиннадцать элементов И-ИЛИ-НЕ и инвертор, которые осуществляют согласование регистра с источником и приемником информации, а в логических элементах каждой ячейки памяти установлены новые связи между КМДП - транзисторами. Регистр может быть использован только в том случае, если информационные посылки обрамляются стартовым и стоповым битами. 3 ил.

Фие.З

| Авторское свидетельство СССР № 1196954, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1251182A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-05-23—Публикация

1987-03-16—Подача