Изобретение относится к оптоэлектронике и микроэлектронике и может быть использовано для построения двухтактных сдвигающих регистров в фотоприемных субмодулях для мозаичных фотоприемников, в частности в фотоприемниках на микроболометрах.

Известен сдвиговый регистр (патент РФ на изобретение №2344498, МПК G11С 19/00, Н03К 3/037, Н03К 9/001, опубл. 20.01.2009 г.), который выполнен на RS-триггерах и элементах И и ИЛИ, содержащий в каждом разряде первый и второй RS-триггеры, четыре логических элемента И, один элемент ИЛИ, информационный вход, первую и вторую шины управления приемом кода в первый и второй триггеры при выполнении операции сдвига кода, информационный выход, при этом выходы первого и третьего элементов И соединены с R-входами первого и второго RS-триггеров соответственно, выход второго элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с информационным входом, а выход упомянутого элемента ИЛИ подключен к S-входу первого триггера, первые входы первого и второго элементов И связаны с первой шиной управления приемом кода в первый триггер, первые входы третьего и четвертого элементов И соединены с второй шиной управления приемом кода во второй триггер, причем нулевой и единичный выходы первого триггера i-го разряда соединены с вторыми входами третьего и четвертого элементов И (i+1)-гo разряда соответственно, нулевой и единичный выходы второго триггера i-го разряда соединены со вторыми входами первого и второго элементов И (i+1)-гo разряда соответственно, кроме того, первый и второй входы второго элемента ИЛИ соединены с S-входами первого и второго триггеров, выход упомянутого элемента ИЛИ является информационным выходом i-го разряда и т.д.

Недостатком этого сдвигового регистра является то, что он имеет сложную структуру и управление, состоит из большого количества транзисторов и вследствие этого при использовании в качестве блока адресации по вертикали в мозаичных фотоприемниках приводит к падению эффективности преобразования изображений в мозаичном фотоприемнике в целом. (Эффективность преобразования изображений - это отношение количества работающих фоточувствительных элементов (ФЧЭ) в мозаичном фотоприемнике к сумме ФЧЭ, потерянных в «слепых зонах» и работающих в мозаичном фотоприемнике.)

Известен реверсивный сдвиговой регистр (патент РФ на изобретение № 2022372, МПК G11С 19/00, опубл. 30.10.1994 г.), сущность которого состоит в том, что он содержит в каждом разряде JK-триггер, четыре элемента И, в каждом разряде, кроме первого и последнего, четыре элемента ИЛИ, в первом и последнем разрядах - три элемента ИЛИ, шины управления направлением сдвига вправо и влево, вход сброса регистра, вход сдвига, прямой и инверсный информационные входы регистра и выход информации в прямом последовательном коде при сдвиге вправо, прямой и инверсный информационные парафазные входы регистра и выход информации в прямом последовательном коде при сдвиге влево, вход управления режимом сдвига - уплотнение единиц и вход управления режимом сдвига - уплотнение нулей, причем прямой выход JK-триггера каждого разряда, кроме последнего, соединен соответственно с первым входом первого элемента И последующего разряда, а прямой выход JK-триггера каждого разряда, кроме первого, соединен соответственно с первым входом второго элемента И предыдущего разряда, выходы первого и второго элементов И каждого разряда соединены с входами первого элемента ИЛИ, вход которого соединен с J-входом JK-триггера данного разряда, вторые входы первого и второго элементов И всех разрядов являются соответственно входами управления сдвигом вправо и сдвигом влево регистра и т.д. Введение в известный сдвиговой регистр в каждый разряд, кроме первого и последнего, двух элементов ИЛИ (пятого и шестого), в первую ячейку пятого элемента ИЛИ, в последнюю ячейку шестого элемента ИЛИ, а также новых связей позволяет расширить функциональные возможности реверсивного регистра сдвига за счет уплотнения нулей кодовой комбинации как влево, так и вправо регистра.

Недостатком этого реверсивного сдвигового регистра, как и предыдущего, является то, что он имеет сложную структуру и управление, состоит из большого количества транзисторов и вследствие этого при использовании в качестве блока адресации по вертикали в мозаичных фотоприемниках приводит к падению эффективности преобразования изображений в мозаичном фотоприемнике в целом.

Известен регистр сдвига на МДП-транзисторах (авторское свидетельство № 1269210, МПК G11С 19/00, опубл. 07.11.1986 г.), в котором выход каждого из инверторов, составляющих регистр, через коммутирующие транзисторы соединен с входами последующего и предыдущего инверторов. При этом во время первого такта работы сдвигового регистра образуются триггеры, состоящие из четного и последующего нечетного инверторов, а во время второго такта работы - из четного и предыдущего нечетного инверторов.

Недостатком этого регистра сдвига на МДП-транзисторах является то, что он требует большого количества тактовых шин для управляющих сигналов и сложную диаграмму управляющих сигналов, что усложняет технологию его изготовления, снижает быстродействие, повышает стоимость устройства и существенно понижает эффективность мозаичного фотоприемника в целом.

Известен также двухтактный сдвигающий регистр на МОП-транзисторах, принятый за прототип, приведенный в авторском свидетельстве №736172, МПК G11С 19/00, опубл. 25.05.1980 г.

Двухтактный сдвигающий регистр состоит из ячеек, каждая из которых содержит триггер, выполненный на левом и правом переключающих и на левом и правом нагрузочных МОП-транзисторах, левый и правый входные МОП-транзисторы, стабилизирующий МОП-транзистор, ключевой МОП-транзистор, МОП-транзистор в качестве элемента задержки, две тактовые шины, шину питания и шину нулевого потенциала, причем в каждой ячейке сток ключевого МОП-транзистора является входом в ячейку, а в первой ячейке двухтактного сдвигающего регистра является, одновременно, и первым информационным входом двухтактного сдвигающего регистра при считывании информации слева направо, затвор ключевого МОП-транзистора соединен с первой тактовой шиной, а его исток - с затвором левого входного МОП-транзистора, сток которого соединен со стоком левого переключающего, с затвором правого переключающего и с истоком левого нагрузочного МОП-транзисторов; стоки и затворы левого и правого нагрузочных МОП-транзисторов соединены с шиной питания, истоки левого и правого переключающих МОП-транзисторов соединены с шиной нулевого потенциала; исток левого входного МОП-транзистора соединен с истоком правого входного и со стоком стабилизирующего МОП-транзисторов, исток последнего соединен с шиной нулевого потенциала, а его затвор - с истоком МОП-транзистора, образующего элемент задержки, затвор которого соединен с шиной питания, а его сток - с затвором правого входного МОП-транзистора и со второй тактовой шиной; сток правого входного МОП-транзистора соединен со стоком правого переключающего, с затвором левого переключающего и с истоком правого нагрузочного МОП-транзистора, это соединение является выходом ячейки, а в последней ячейке двухтактного сдвигающего регистра является также и первым информационным выходом двухтактного сдвигающего регистра при считывании информации слева направо.

Этот двухтактный сдвигающий регистр, принятый за прототип, создан на основе более экономичной схеме и не требует повышенной амплитуды тактовых сигналов по сравнению с известными аналогами.

Однако он обладает существенными недостатками, а именно сдвигает информацию только в одном направлении и паразитные емкости его тактовых шин существенно влияют на работу двухтактного сдвигающего регистра.

Техническим результатом изобретения является:

- расширение функциональных возможностей за счет обеспечения реверсивности сдвига информации внутри двухтактного сдвигающего регистра,

- минимизация занимаемой площади кристалла ИС,

- расширение области применения за счет возможности двунаправленной передачи информации и стабильной работы двухтактного сдвигающего регистра в условиях существенных паразитных емкостей тактовых шин.

Технический результат изобретения достигается тем, что в двухтактном сдвигающем регистре, состоящем из ячеек, каждая из которых содержит триггер, выполненный на левом и правом переключающих и на левом и правом нагрузочных МОП-транзисторах, левый и правый входные МОП-транзисторы, стабилизирующий МОП-транзистор, ключевой МОП-транзистор, МОП-транзистор в качестве элемента задержки, две тактовые шины, шину питания и шину нулевого потенциала, причем в каждой ячейке сток ключевого МОП-транзистора является входом в ячейку, а в первой ячейке двухтактного сдвигающего регистра является, одновременно, и первым информационным входом двухтактного сдвигающего регистра при считывании информации слева направо, затвор ключевого МОП-транзистора соединен с первой тактовой шиной, а его исток - с затвором левого входного МОП-транзистора, сток которого соединен со стоком левого переключающего, с затвором правого переключающего и с истоком левого нагрузочного МОП-транзисторов, стоки и затворы левого и правого нагрузочных МОП-транзисторов соединены с шиной питания; истоки левого и правого переключающих МОП-транзисторов соединены с шиной нулевого потенциала, исток левого входного МОП-транзистора соединен с истоком правого входного и со стоком стабилизирующего МОП-транзисторов, исток последнего соединен с шиной нулевого потенциала, а его затвор - с истоком МОП-транзистора, образующего элемент задержки, затвор которого соединен с шиной питания, а его сток - с затвором правого входного МОП-транзистора и со второй тактовой шиной, сток правого входного МОП-транзистора соединен со стоком правого переключающего, с затвором левого переключающего и с истоком правого нагрузочного МОП-транзисторов, это соединение является выходом ячейки, а в последней ячейке двухтактного сдвигающего регистра является, одновременно, и первым информационным выходом двухтактного сдвигающего регистра при считывании информации слева направо, в каждую ячейку введены дополнительный МОП-транзистор и третья тактовая шина, причем с ней соединен затвор дополнительного МОП-транзистора, исток которого соединен с затвором левого входного МОП-транзистора, а сток - с выходом следующей ячейки и является вторым входом ячейки, в последней ячейке двухтактного сдвигающего регистра он является, одновременно, и вторым информационным входом двухтактного сдвигающего регистра для считывания информации справа налево, выход первой ячейки двухтактного сдвигающего регистра является, одновременно, и вторым информационным выходом двухтактного сдвигающего регистра при считывании информации справа налево.

Предлагаемый двухтактный сдвигающий регистр за счет введения в каждую его ячейку дополнительного МОП-транзистора, третьей тактовой шины и дополнительных связей обеспечивает возможность сдвига информации внутри двухтактного сдвигающего регистра в прямом и обратном направлении (слева направо и справа налево) и возможность минимизации размера ячейки, а также расширение области применения за счет возможности двунаправленной передачи информации и стабильной работы двухтактного сдвигающего регистра в условиях существенных паразитных емкостей тактовых шин.

Сущность изобретения поясняется нижеследующим описанием и прилагаемыми чертежами.

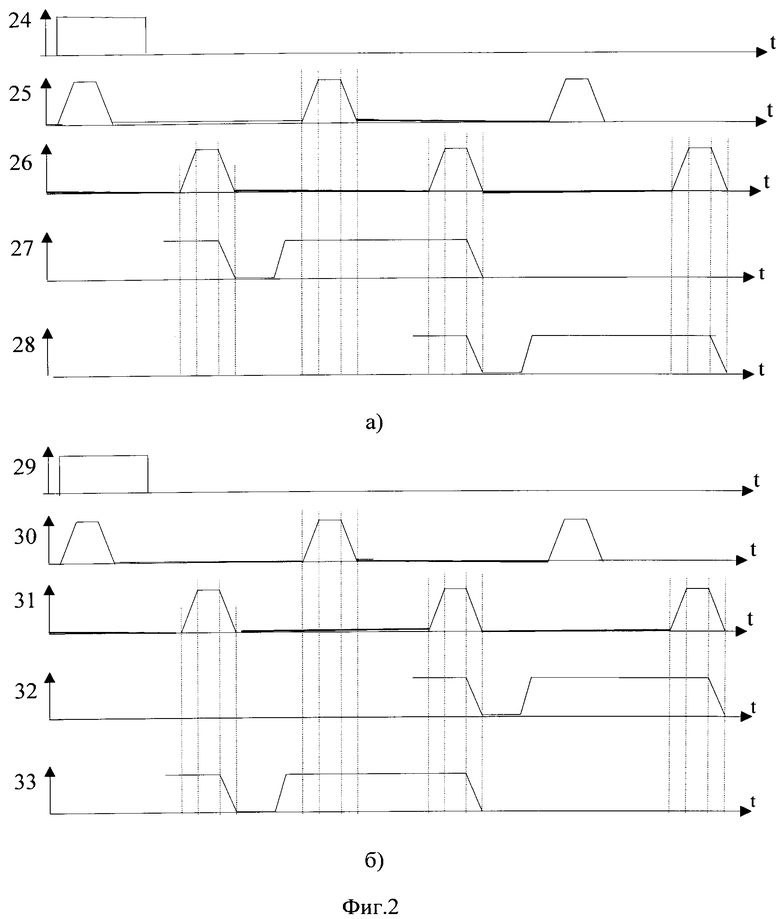

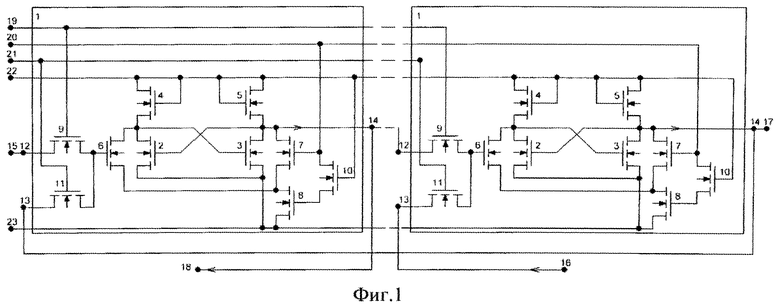

На фиг. 1 приведена функциональная схема двухтактного сдвигающего регистра, на фиг. 2 приведены временные диаграммы работы двухтактного сдвигающего регистра при выполнении операции сдвига информации слева направо и справа налево.

На фиг. 1 приведена функциональная схема двухтактного сдвигающего регистра, где 1 - ячейка, 2, 3 - левый и правый переключающие МОП-транзисторы триггера; 4, 5 - левый и правый нагрузочные МОП-транзисторы триггера; 6, 7 - левый и правый входные МОП-транзисторы; 8 - стабилизирующий МОП-транзистор; 9 - ключевой МОП-транзистор; 10 - МОП-транзистор, образующий элемент задержки; 11 - дополнительный МОП-транзистор; 12 - первый вход ячейки, 13 - второй вход ячейки; 14 - выход ячейки; 15 - первый информационный вход двухтактного сдвигающего регистра, 16 - второй информационный вход двухтактного сдвигающего регистра; 17 - первый информационный выход двухтактного сдвигающего регистра, 18 - второй информационный выход двухтактного сдвигающего регистра; 19 - первая тактовая шина, 20 - вторая тактовая шина, 21 - третья тактовая шина, 22 - шина питания, 23 - шина нулевого потенциала.

Двухтактный сдвигающий регистр организован следующим образом (фиг. 1). В каждой ячейке 1 сток ключевого МОП-транзистора 9 является первым входом 12 ячейки, а в первой ячейке двухтактного сдвигающего регистра он является, одновременно, и первым информационным входом двухтактного сдвигающего регистра 15 при выполнении операции сдвига информации слева направо. Затвор ключевого МОП-транзистора 9 соединен с первой тактовой шиной 19, а его исток - с затвором левого входного 6 и истоком дополнительного 11 МОП-транзисторов. Сток левого входного МОП-транзистора 6 соединен со стоком левого переключающего 2, затвором правого переключающего 3 и с истоком левого нагрузочного 4 МОП-транзисторов, сток и затвор которого соединены с шиной питания 22. Истоки левого 2 и правого 3 переключающих МОП-транзисторов соединены с шиной нулевого потенциала 23. Исток левого входного МОП-транзистора 6 соединен с истоком правого входного 7 и со стоком стабилизирующего 8 МОП-транзисторов. Затвор правого входного МОП-транзистора 7 соединен со стоком МОП-транзистора 10, образующего элемент задержки, и со второй тактовой шиной 20. Сток правого входного МОП-транзистора 7 соединен со стоком правого переключающего 3, с затвором левого переключающего 2 и с истоком правого нагрузочного 5 МОП-транзисторов. Это соединение является выходом 14 ячейки, выход первой ячейки двухтактного сдвигающего регистра является, одновременно, и вторым информационным выходом 18 двухтактного сдвигающего регистра при выполнении операции сдвига информации справа налево, а выход последней ячейки двухтактного сдвигающего регистра является, одновременно, и первым информационным выходом 17 двухтактного сдвигающего регистра при выполнении операции сдвига информации слева направо. Сток и затвор правого нагрузочного МОП-транзистора 5 соединены с шиной питания 22. Исток стабилизирующего МОП-транзистора 8 соединен с шиной нулевого потенциала 23, а его затвор - с истоком МОП-транзистора 10, образующего элемент задержки, затвор которого соединен с шиной питания 22. Затвор дополнительного МОП-транзистора 11 соединен с третьей тактовой шиной 21, его сток соединен с выходом следующей ячейки и является вторым входом 13 ячейки, а в последней ячейке двухтактного сдвигающего регистра, одновременно, является и вторым информационным входом 16 двухтактного сдвигающего регистра.

На фиг. 2,а приведена временная диаграмма работы двухтактного сдвигающего регистра при выполнении операции сдвига информации слева направо, где

24 - сигнал на первом информационном входе 15 двухтактного сдвигающего регистра,

25, 26 - сигналы на первой 19 и второй 20 тактовых шинах соответственно,

27, 28 - сигналы на выходах 14 первой и второй ячеек двухтактного сдвигающего регистра соответственно.

На фиг.2,б приведена временная диаграмма работы двухтактного сдвигающего регистра при выполнении операции сдвига информации справа налево, где

29 - сигнал на втором информационном входе 16 двухтактного сдвигающего регистра,

30, 31- сигналы на третьей 21 и второй 20 тактовых шинах соответственно;

32, 33 - сигналы на выходах 14 предпоследней и последней ячеек двухтактного сдвигающего регистра соответственно.

Рассмотрим работу двухтактного сдвигающего регистра.

Двухтактный сдвигающий регистр (фиг. 1) работает следующим образом при выполнении операции сдвига информации в виде логической единицы «1» или логического нуля «0» вправо (считывание информации слева направо, фиг. 2,а).

Входной сигнал 24 с первого информационного входа 15 двухтактного сдвигающего регистра и, одновременно, с первого входа 12 первой ячейки 1 подается через ключевой МОП-транзистор 9 на затвор левого входного МОП-транзистора 6. Первый тактовый сигнала 25 подается по первой тактовой шине 19 на затвор ключевого МОП-транзистора 9, второй тактовый сигнал 26 - по второй тактовой шине 20 на затвор правого входного МОП-транзистора 7 и через элемент задержки (МОП-транзистор 10) на затвор стабилизирующего 8 МОП-транзистора. Выходной сигнал с выхода ячейки 14 снимается с правого инвертора триггера, собранного на правом переключающем 3 и правом нагрузочном 5 МОП-транзисторах.

Записанная информация хранится в ячейках двухтактного сдвигающего регистра до поступления импульсов тактовых сигналов 25 и 26, имеющих уровень логической «1», на емкости цепи затвора левого входного МОП-транзистора 6. Сдвиг информации осуществляется импульсами двух тактовых сигналов 25 и 26, поступающих по шинам 19 и 20 соответственно. Съем информации производится в интервалах между тактовыми импульсами сигнала 26, поступающего по шине 20.

В отсутствие тактовых импульсов ключевой 9, стабилизирующий 8 и правый входной 7 МОП-транзисторы заперты. Первый тактовый импульс сигнала 25 по первой тактовой шине 19 открывает ключевой МОП-транзистор 9 на время, достаточное для заряда или разряда емкости цепи затвора левого входного МОП-транзистора 6 до уровня, близкого уровню входного сигнала на входе 15. В дальнейшем напряжение на затворе левого входного МОП-транзистора 6 изменяется с постоянной времени, которая для МОП-транзисторов составляет несколько сотен микросекунд или больше. Интервал между тактовыми импульсами сигналов 25 и 26, поступающих по первой 19 и второй 20 тактовым шинам, и длительность тактового импульса сигнала 26 выбираются достаточно малыми, чтобы к моменту снятия импульса сигнала 26 этот уровень не успел существенно измениться. Так как до подачи тактового импульса сигнала 26, поступающего по второй тактовой шине 20, стабилизирующий 8 и правый входной 7 МОП-транзисторы закрыты, то левый входной МОП-транзистор 6 не оказывает влияния на состояние триггера.

Тактовый импульс сигнала 26, поступающий по второй тактовой шине 20, открывает правый входной 7 и стабилизирующий 8 МОП-транзисторы, в результате чего на выходе 14 устанавливается уровень «0», а левый переключающий МОП-транзистор 2 закрывается.

Если уровень входного сигнала 24 близок к напряжению шины нулевого потенциала 23, т.е. имеет уровень логического «0», то закрытый левый входной МОП-транзистор 6 не оказывает влияния на состояние триггера и после открывания правого входного 7 и стабилизирующего 8 МОП-транзисторов. После окончания импульса 26 по шине 20 в триггере будет записан «0».

Если уровень входного сигнала 24 близок к напряжению шины питания 22, т.е. имеет уровень логической «1», то левый входной МОП-транзистор 6 будет открыт. Поэтому, когда тактовый импульс сигнала 26 по второй тактовой шине 20 открывает правый входной 7 и стабилизирующий 8 МОП-транзисторы, уровень «0» устанавливается не только на выходе 14, но и на стоке левого переключающего МОП-транзистора 2, а правый переключающий МОП-транзистор 3 закрывается.

Для записи «1» в триггер необходимо, чтобы ток в цепи МОП-транзисторов 4-6-8 существовал некоторое время посоле исчезновения тока в цепи МОП-транзисторов 5-7-8. Это обеспечивает открывание левого переключающего МОП-транзистора 2 при запертом правом переключающем МОП-транзисторе 3. По окончании тактового импульса сигнала 26, поступившего по второй тактовой шине 20, правый входной МОП-транзистор 7 закрывается раньше, чем стабилизирующий МОП-транзистор 8 (сигнал 27, фиг. 2,а).

Требуемую последовательность закрывания правого входного 7 и стабилизирующего 8 МОП-транзисторов во время действия заднего фронта тактового импульса сигнала 26, поступающего по второй тактовой шине 20, можно достигнуть двумя путями. Повышение порогового напряжения правого входного МОП-транзистора 7 по сравнению со стабилизирующим МОП-транзистором 8 обеспечивает требуемую последовательность закрывания этих транзисторов во время действия заднего фронта импульса тактового сигнала 26. Этого же эффекта можно достигнуть, если тактовый импульс сигнала 26 с затвора правого входного МОП-транзистора 7 подать на затвор стабилизирующего МОП-транзистора 8 через элемент задержки, например через постоянно открытый МОП-транзистор 10, образующий интегральную цепочку совместно с емкостью цепи затвора стабилизирующего МОП-транзистора 8.

Так как в схеме двухтактного сдвигающего регистра выходной сигнал триггера каждой ячейки служит входным сигналом последующего, а шины одноименных тактовых сигналов объединены, то логическая «1» с выхода 14 первой ячейки одновременно окажется на входе 12 второй ячейки двухтактного сдвигающего регистра. Вышеперечисленные операции повторятся, и на выходе 14 второй ячейки появится сигнал 28 (сигнал 28, фиг. 2,а), а по прошествии всех ячеек двухтактного сдвигающего регистра на первом информационном выходе 17 двухтактного сдвигающего регистра появится сигнал, который был введен с первого информационного входа 15 двухтактного сдвигающего регистра.

Двухтактный сдвигающий регистр (фиг. 1) работает следующим образом при выполнении операции сдвига информации в виде логической единицы «1» или логического нуля «0» влево (считывание информации справа налево, фиг. 2,б).

Входной сигнал 29 со второго информационного входа 16 двухтактного сдвигающего регистра и, одновременно, с входа 13 последней ячейки 1 двухтактного сдвигающего регистра подается через дополнительный МОП-транзистор 11 на затвор левого входного МОП-транзистора 6 последней ячейки двухтактного сдвигающего регистра. Первый импульс тактового сигнала 30 подается по третьей тактовой шине 21 на затвор дополнительного МОП-транзистора 11. Затем подается импульс тактового сигнала 31, поступающий по второй тактовой шине 20, на затвор правого входного МОП-транзистора 7 и через элемент задержки (МОП-транзистор 10) на затвор стабилизирующего МОП-транзистора 8. Выходной сигнал 33 (сигнал 33, фиг.2,б) с выхода 14 снимается с правого инвертора триггера, собранного на правом переключающем 3 и правом нагрузочном 5 МОП-транзисторах последней ячейки двухтактного сдвигающего регистра, и подается на второй вход 13 предпоследней ячейки двухтактного сдвигающего регистра. Затем с выхода 14 предпоследней ячейки двухтактного сдвигающего регистра снимается сигнал 32 (сигнал 32, фиг. 2,б).

При сдвиге информации в виде логической единицы «1» или логического нуля «0» влево двухтактный сдвигающий регистр работает аналогично рассмотренному выше сдвигу информации вправо, за исключением того, что в проходящих процессах участвует дополнительный МОП-транзистор 11 и третья тактовая шина 21 вместо ключевого МОП-транзистора 9 и первой тактовой шины 19.

По прошествии всех ячеек двухтактного сдвигающего регистра на втором информационном выходе 18 двухтактного сдвигающего регистра появится сигнал, который был введен со второго информационного входа 16 двухтактного сдвигающего регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1624530A1 |

| Ч.:.СОЮЗНАЯ | 1973 |

|

SU387437A1 |

| Элемент памяти для динамического регистра сдвига | 1977 |

|

SU684617A1 |

| ТРИГГЕР НА МОП—ТРАНЗИСТОРАХ | 1973 |

|

SU391709A1 |

Изобретение относится к оптоэлектронике и микроэлектронике и может быть использовано для построения двухтактных сдвигающих регистров в фотоприемных субмодулях для мозаичных фотоприемников, в частности в фотоприемниках на микроболометрах. Технический результат заключается в обеспечении возможности реверсивного сдвига информации внутри двухтактного сдвигающего резистра и возможности двунаправленной передачи информации и стабильной работы двухтактного сдвигающего регистра в условиях существенных паразитных емкостей тактовых шин. Технический результат достигается за счет двухтактного сдвигающего регистра, который состоит из ячеек, каждая из которых содержит триггер, выполненный на левом и правом переключающих и на левом и правом нагрузочных МОП-транзисторах, левый и правый входные МОП-транзисторы, стабилизирующий МОП-транзистор, ключевой МОП-транзистор, МОП-транзистор в качестве элемента задержки, две тактовые шины, шину питания, шину нулевого потенциала, и их связей, причем в каждую ячейку введены дополнительный МОП-транзистор, третья тактовая шина и их связи. 2 ил.

Двухтактный сдвигающий регистр, состоящий из ячеек, каждая из которых содержит триггер, выполненный на левом и правом переключающих и левом и правом нагрузочных МОП-транзисторах, левый и правый входные МОП-транзисторы, стабилизирующий МОП-транзистор, ключевой МОП-транзистор, МОП-транзистор в качестве элемента задержки, две тактовые шины, шину питания и шину нулевого потенциала, причем в каждой ячейке сток ключевого МОП-транзистора является входом в ячейку, а в первой ячейке двухтактного сдвигающего регистра является, одновременно, первым информационным входом двухтактного сдвигающего регистра при считывании информации слева направо, затвор ключевого МОП-транзистора соединен с первой тактовой шиной, а его исток - с затвором левого входного МОП-транзистора, сток которого соединен со стоком левого переключающего, с затвором правого переключающего и с истоком левого нагрузочного МОП-транзисторов, сток и затвор левого и правого нагрузочных МОП-транзисторов соединены с шиной питания, истоки левого и правого переключающих МОП-транзисторов соединены с шиной нулевого потенциала, исток левого входного МОП-транзистора соединен с истоком правого входного и со стоком стабилизирующего МОП-транзисторов, исток последнего соединен с шиной нулевого потенциала, а его затвор - с истоком МОП-транзистора, образующего элемент задержки, затвор которого соединен с шиной питания, а его сток - с затвором правого входного МОП-транзистора и со второй тактовой шиной, сток правого входного МОП-транзистора соединен со стоком правого переключающего, с затвором левого переключающего, с истоком правого нагрузочного МОП-транзисторов, и это соединение является выходом ячейки, а в последней ячейке двухтактного сдвигающего регистра является, одновременно, и первым информационным выходом двухтактного сдвигающего регистра при считывании информации слева направо, отличающийся тем, что в каждую ячейку введены дополнительный МОП-транзистор и третья тактовая шина, причем с ней соединен затвор дополнительного МОП-транзистора, исток которого соединен с затвором левого входного МОП-транзистора, а сток - с выходом следующей ячейки, и является вторым входом ячейки, а в последней ячейке двухтактного сдвигающего регистра он является, одновременно, и вторым информационным входом двухтактного сдвигающего регистра, выход первой ячейки двухтактного сдвигающего регистра является, одновременно, вторым информационным выходом двухтактного сдвигающего регистра при считывании информации справа налево.

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

| Ч.:.СОЮЗНАЯ | 0 |

|

SU387437A1 |

| СДВИГОВЫЙ РЕГИСТР И ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2010 |

|

RU2493621C2 |

| СДВИГОВЫЙ РЕГИСТР, УСТРОЙСТВО ОТОБРАЖЕНИЯ, СНАБЖЕННОЕ ТАКОВЫМ, И СПОСОБ ВОЗБУЖДЕНИЯ СДВИГОВОГО РЕГИСТРА | 2010 |

|

RU2488180C1 |

| US 6067613 A, 23.05.2000 | |||

Авторы

Даты

2015-04-20—Публикация

2014-05-05—Подача