1

(21)4637415/24

(22)13.01.89

(46) 07,04.91 о Бюл. N 13

(72) В.А.Миндалев и С.Н0Субботин

(53)681.325(088о8)

(56)Авторское свидетельство СССР 1043638, кл. G 06 F 7/50, 1982„

Угрюмов ЕоНо Проектирование элементов и узлов ЭВМо - М0: Высшая школа 1987, с0195, 196, рис 11, 14,

(54)НАКАПЛИВАЮЩИЙ СУММАТОР

(57)Изобретение относится к вычислительной технике и может быть использовано в устройствах передачи информации. Целью изобретения является повышение точности накапливающего сумматора при использовании его в качестве устройства усреднения входного числа для схем фазовой подстройки Накапливающий сумматор содержит регистр 1, комбинационный сумматор 2, два мажоритарных элемента 3,4, элемент НЕ 5, элемент И 6, триггер 7, элемент ИСКЛОЧАЮ- DIEE ИЛИ 8, шину 9 синхронизации и шину 11D входного числа, соединенные между собой функционально 1 ил

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ С ПЕРЕМЕННЫМ МОДУЛЕМ СЧЕТА | 2000 |

|

RU2179784C2 |

| Синтезатор частоты | 1985 |

|

SU1347145A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Арифметическое устройство | 2016 |

|

RU2632411C1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

Ј4

&

зэ

Изобретение относится к вычислительной технике и может быть использовано в устройствах передачи информации о

Цель изобретения - повышение точности накапливающего сумматора при использовании его в качестве устройства усреднения входного числа для схем фазовой подстройки0.Q

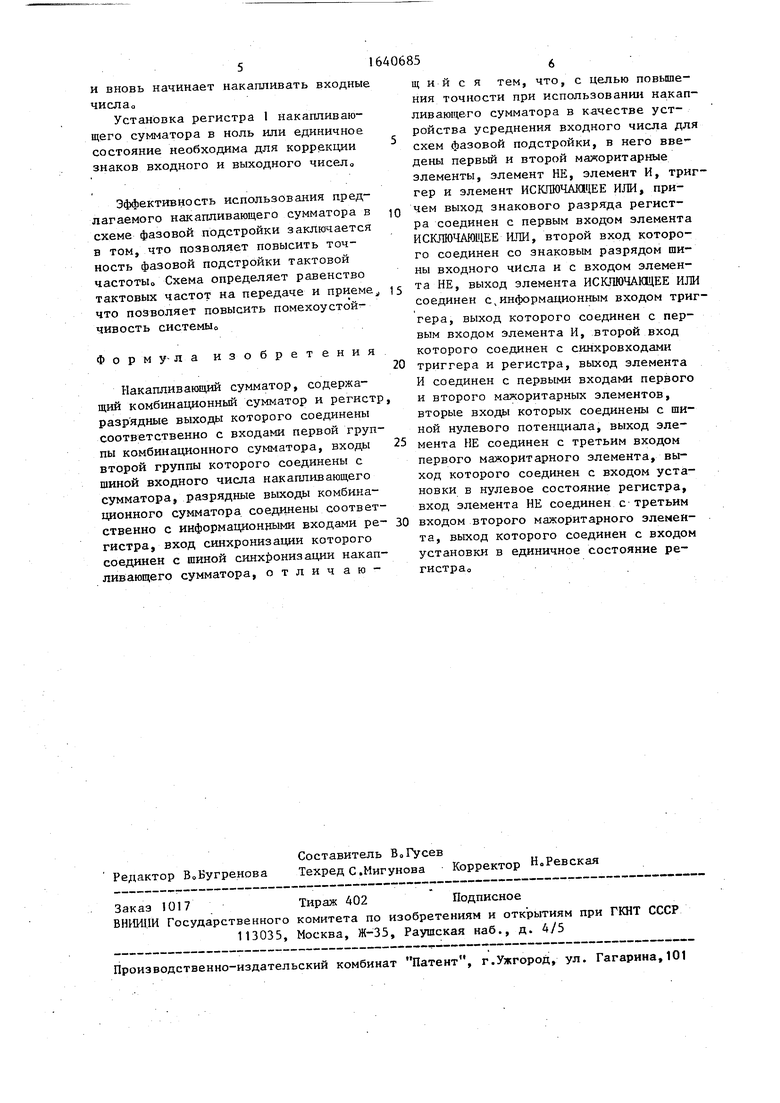

На чертеже представлена функциональная схема накапливающего сумматора.

Накапливающий сумматор содержит регистр 1, комбинационный сумматор 2, первый 3 и второй 4 мажоритарные элементы, элементы НЕ 5 и И 6, триггер 7, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8, шины синхронизации 9 и входного числа 10, соединенные между собой функцио- 2п нальноо

Накапливающий сумматор в качестве устройства усреднения входного числа работает следующим образом0

Код первого слагаемого хранится в 25 регистре 1, а код второго слагаемого поступает по шине 100

В комбинационном сумматоре 2 производится сложение двух чисел, из которых первое поступает по шине 10, зд а второе - с выходов регистра 1 Образованная сумма по импульсу синхронизации, поступающему по шине 9 синхронизации, записывается в регистр 1„ Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8 сравнивает знаки входного и выходного чисел« Если значения знаковых разрядов на выходе накапливающего сумматора и входного числа одинаковые (происходит накопление положительных или отрицатель-до ных чисел), то с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 уровень логического нуля поступает на информационный вход Триггера 7 и записывается в него по импульсу синхронизациио45

Данный уровень логического нуля умножается элементом И 6 на длительность импульса синхронизации и поступает на первые входы мажоритарных элементов 3 и 4, на вторые входы ко- торых поступает уровень логического нуля, и, независимо от уровня на третьих входах, на выходах мажоритарных элементов 3 и 4 присутствует уровень лбгического нуля, который по- .,. ступает на установочные входы регистра 1, не влияя на них Накапливающий сумматор в этом случае суммирует входные числа и результат накапливает в

35

Q

п

5

о 5

,.

5

регистре I , -замещая предыдущее содер- жание0

Если знак входного числа изменился и значения знаковых разрядов на выходе накапливающего сумматора и входного числа разные (О и 1 или 1 и О соответственно), это означает, что накопление необходимо прекратить, так как тактовая частота на приеме схемы фазовой подстройки сравнялась с тактовой частотой на передаче и накапливающий сумматор в этом случае необходимо обнулить или установить в единичное состояние в зависимости от знака входного числа

При разных знаках входных и выходных чисел накапливающего сумматора на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 формируется уровень логической единицы, поступающий на информационный вход триггера 70 Но импульсу синхронизации уровень логической единицы записывается в триггер .7 и с его выхода поступает на первый вход элемента И 6, на выходе которого формируется импульс длительностью, равной импуль- су частоты синхронизациИо Данный импульс поступает на первые входы мажоритарных элементов 3 и 4„ Если на входе накапливающего сумматора положительное число, то на третий вход мажоритарного элемента 3 поступает уровень логической единицы, а на третий вход мажоритарного элемента 4 - уровень логического нуля0 На выходе мажоритарного элемента 3 формируется уровень логической единицы, поступающий на вход установки регистра 1 в ноль, а на выходе мажоритарного элемента 4 - уровень логического нуля0

На разрядных выходах регистра 1 формируются уровни логического нуля, Если на входе накапливающего сумматора отрицательное число, то на третий вход мажоритарного элемента 3 поступает уровень логического нуля, а на третий вход мажоритарного элемента 4 - уровень логической единицы На выходе мажоритарного элемента 3 формируется уровень логического нуля, а на выходе мажоритарного элемента 4 - уровень логической единицы, поступающий на вход установки регистра 1 в единицуо На разрядных выходах регистра 1 формируются уровни логической единицыв Регистр 1 обнуляется или устанавливается в единичное состояние

и вновь начинает накапливать входные числа

Установка регистра 1 накапливающего сумматора в ноль или единичное состояние необходима для коррекции знаков входного и выходного чисела

Эффективность использования предлагаемого накапливающего сумматора в схеме фазовой подстройки заключается в том, что позволяет повысить точность фазовой подстройки тактовой частоты,. Схема определяет равенство тактовых частот на передаче и приеме что позволяет повысить помехоустойчивость системно

Форму-ла изобретения

Накапливающий сумматор, содержащий комбинационный сумматор и регист разрядные выходы которого соединены соответственно с входами первой группы комбинационного сумматора, входы второй группы которого соединены с шиной входного числа накапливающего сумматора, разрядные выходы комбинационного сумматора соединены соответственно с информационными входами ре- 30входом второго мажоритарного элеменгистра, вход синхронизации которогота, выход которого соединен с входом

соединен с шиной синхронизации накап-установки в единичное состояние реливающего сумматора, отлич аю-гистра0

щ и и с я тем, что, с целью повышения точности при использовании накапливающего сумматора в качестве устройства усреднения входного числа для схем фазовой подстройки, в него введены первый и второй мажоритарные элементы, элемент НЕ, элемент И, триггер и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выход знакового разряда регистра соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен со знаковым разрядом шины входного числа и с входом элемента НЕ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с,информационным входом триггера, выход которого соединен с первым входом элемента И, второй вход которого соединен с синхровходами триггера и регистра, выход элемента И соединен с первыми входами первого и второго мажоритарных элементов, вторые входы которых соединены с шиной нулевого потенциала, выход эле5 мента НЕ соединен с третьим входом первого мажоритарного элемента, выход которого соединен с входом установки в нулевое состояние регистра, вход элемента НЕ соединен с третьим

5

0

Авторы

Даты

1991-04-07—Публикация

1989-01-13—Подача