Изобретение относится к вычислительной технике, в частности к устройствам спектрального анализа сигналов, представленных в цифровой форме,

Изобретение может быть использовано при проектировании и построении систем, осуществляющих вычисление спектра сигналов в связи, телеметрии и других областях техники.

Цель изобретения - повышение точности вычисления спектра выходных сигналов.

Сущность изобретения заключается в том. что увеличивается точность вычисления спектра выходных сигналов за счет повышения точности определения усредненных значений АЧХ фильтров. Это достигается тем, что вычисление усредненных значений амплитудно-частотных характеристик (АЧХ) фильтров по шумовому сигналу производится по формуле

1 N

-Я.2Л

(1)

где N - количество отсчетов накопления усреднения при вычислении спектра шумового сигнала, прошедшего АЧХ фильтров;

Vk - результат усреднения на k-ом шаге вычисления;

xk - отсчет спектра (тестового) шумового сигнала, подлежащий усреднению на k-ом шаге вычислений.

При этом дисперсия Д(у) усредненного значения АЧХ фильтров в каждой точке ее частоты, выраженная через дисперсию входного сигнала, равна

Д(У)1д(х)

(2)

Таким образом, чем больше число усреднений N, тем меньше дисперсия Д(у), т.е. гем ниже погрешность оценки усредненного значения АЧХ. Так, если N 1024, то

д(у))

(3)

Сопоставляя этот результат, видим, что точность вычисления усредненных значений АЧХ существенно возрастает при увеличении числа усреднений. Тем самым видно, что операция усреднения по формуле (1) при N 1 существенно увеличивает точность вычисления спектра выходных сигналов устройства.

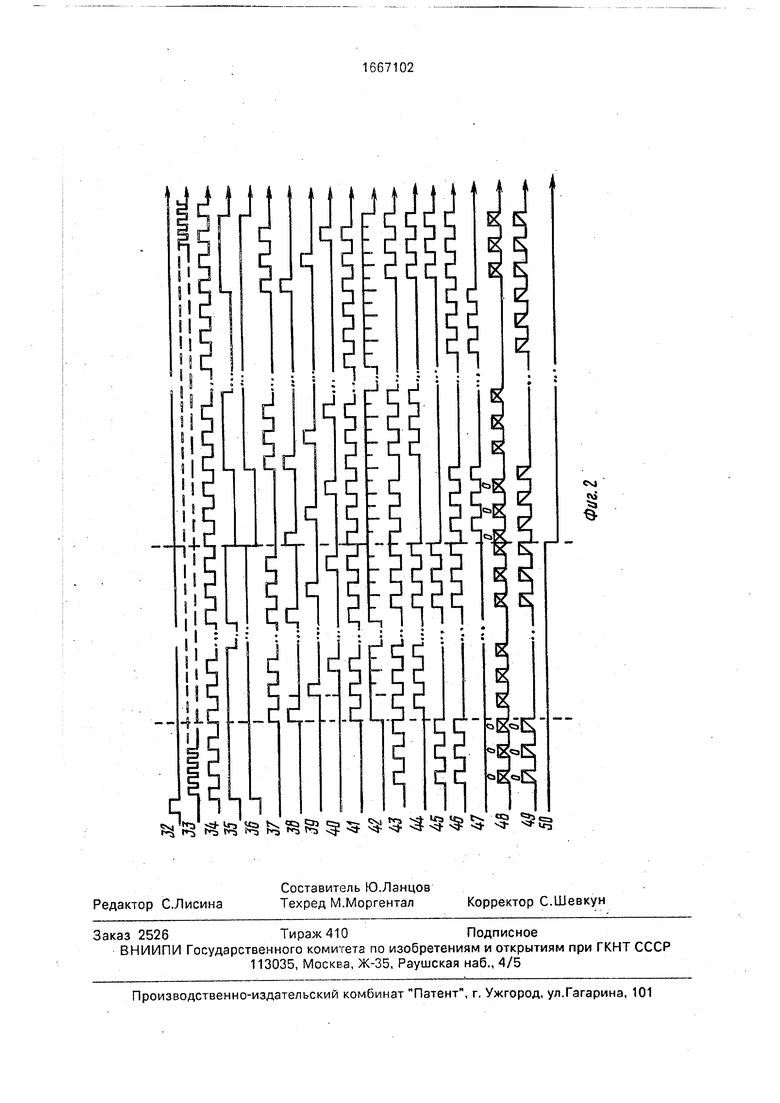

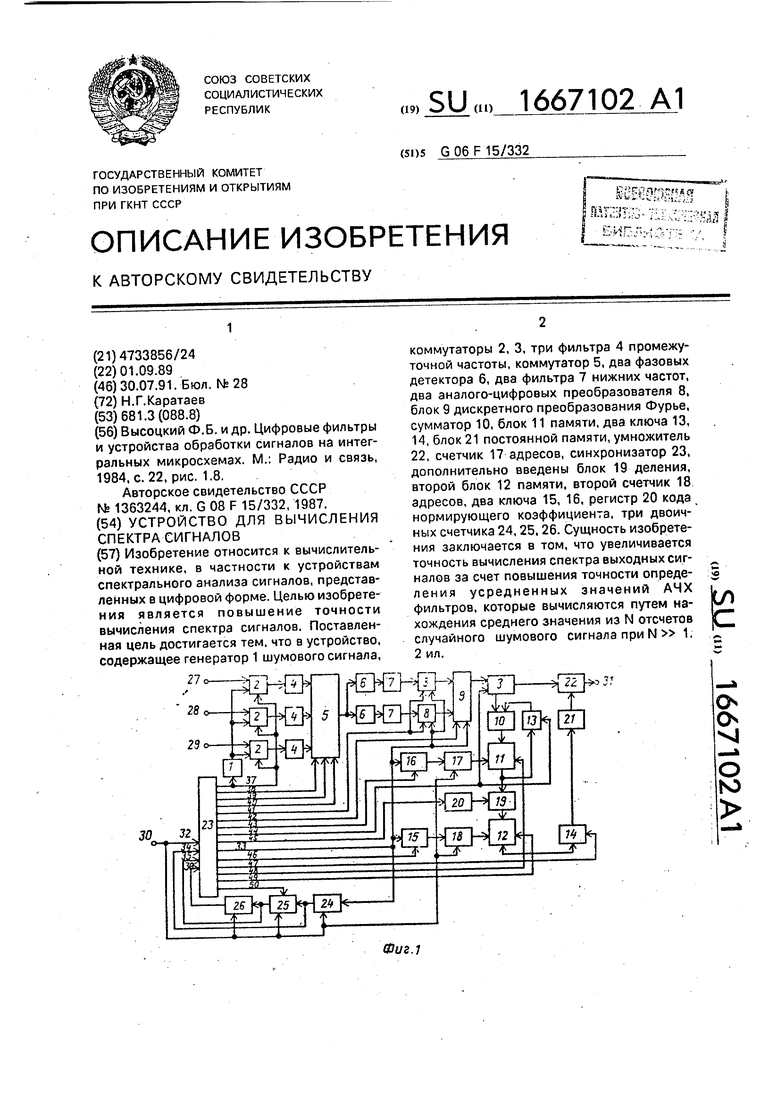

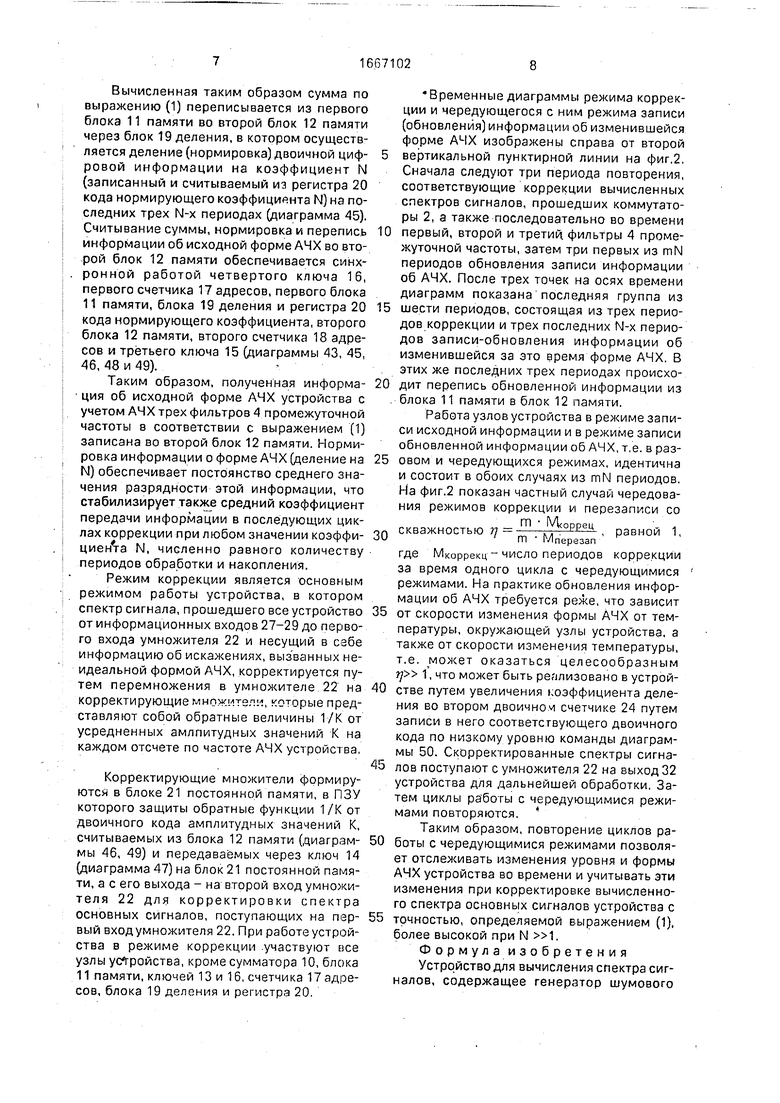

На фиг. 1 представлйна структурная схема yrrponcim для вычисления спектра сигнал)в; на фиг.2 - временные диаграммы, поясняющие работу устройства.

Устройство для вычисления спектра сигналов содержит генератор 1 шумового сигнала, коммутаторы 2-3, фильтры 4 промежуточной частоты, коммутатор 5, два канала, каждый из которых состоит из последовательно соединенных фазового детектора 6, фильтра 7 нижних частот,

0 аналого-цифрового преобразователя (АЦП) 8, блок 9 дискретного преобразования Фурье, сумматор 10, блоки 11-12 памяти, ключи 13-16, счетчики 17-18 адресов, блок 19 деления, регистр 20 кода нормирующего

5 коэффициента, блок 21 постоянной памяти, умножитель 22, синхронизатор 23, двоичные счетчики 24-26, информационные входы 27-29 устройства, вход пуска 30, информационный выход 31, вход 32 пуска

0 синхронизатора, выход 33 синхронизатора, входы 34-36 задания режима синхронизатора и выходы 37-50 синхронизатора.

Обозначение временных диаграмм на фиг.2 соответствует обозначениям входов и

5 выходов синхронизатора.

Устройство работает следующим образом.

С момента поступления сигнала Пуск на вход 30 устройство работает в соответст0 вии с временной диаграммой (см. фиг.2), разделенной на три части вертикальными пунктирными линиями. Левая часть соответствует режиму установки исходного состояния устройства, средняя часть - режиму

5 ускоренной разовой записи исходного состояния формы АЧХ и правая часть соответствует одному из многих одинаковых циклов режима коррекции (осноаной режим), чередующегося с режимом повторной записи те0 кущей, изменившейся формы АЧХ.

Таким образом, и,г,ея временной диаграммы работы устройства заключается в установке исходного состояния устройства, в ускоренной записи исходной формы АЧХ, а

5 затем следуют циклы работы, каждый из которых состоит из режима коррекции и чередующегося с ним режима повторной записи изменившейся формы АЧХ.

Режим установки устройства в исходное

0 состояние начинается при поступлении сигнала ПУСК (диаграмма 32) на вход 30 устройства, который устанавливает в исходное состояние и дает начало работы синхронизатору 23, двоичным счетчикам 24-26, пер5 вому 17 и второму 18 счетчикам4 адресов (диаграммы 33-36, 43-46 фиг.2, слева от первой пунктирной линии), а также устанавливает в исходное нулевое состояние информацию АЦП 8 и блока 9 (диаграммы 41. 42).

Первый двоичный счетчик 24 из тактовой частоты {диаграмма 33) формирует импульсы с периодом обработки Тп (диаграмма 34), второй двоичный счетчик 25 насчитывает m периодов Тп (в нашем случае m 3, по числу фильтров 4 промежуточной частоты) при воздействии единичного уровня диаграммы 50.

Третий двоичный счетчик 26 начинает счет временных интервалов тТп, являю- щихся выходными для счетчика 25. Режим установки устройства в исходное состояние заканчивается записью нулевой информации в первый 11 и второй 12 блоки памяти с помощью тактовой частоты, проходящей че- рез открытые ключи 15 и 16 и осуществляющей полный перебор адресов первого 17 и второго 18 счетчиков адресов, синхронно с поступлением команд управления записью/считыванием (диаграмма 48) для первого блока 11 памяти и команды управления записью (диаграмма 49) для второго блока 12 памяти. При этом нулевая входная информация на первый блок 11 памяти подается с установленного в нулевое состоя- ние (диаграмма 42) блока 9 через коммутатор 3 и сумматор 10, а из первого блока 11 памяти нулевая информация переписывается во второй блок 12 памяти через блок 19 деления, который выполняет функ- цию деления его входной информации на коэффициент N, записанный и считываемый из регистра 20 кода нормирующего коэффициента. В этом режиме операция деления не имеет принципиального значения. Она будет необходима в конце режимов записи в следующих циклах работы устройства.

Режим записи исходного состояния формы АЧХ устройства представляет собой обработку с вычислением спектра широко- полосного сигнала генератора 1 шума за N периодов Тп в полосе АЧХ устройства с вычислением в сумматоре 10 и первом блоке 11 памяти накопленной информации о форме АЧХ, нормировку этой информации (де- лениена блоке 19 деления) и запись этой информации, вычисленной в соответствии с выражением (1) во второй блок 12 памяти.

Точность полученной информации о форме АЧХ тем выше, чем больше число N периодов Тп обработки и усреднения шумовых мгновенных спектров, полученных в каждом периоде Тп вычислений. В этом режиме работают все узлы устройства, кроме второго ключа 14, блока 21 постоянной па- мяти и умножителя 22. Широкополосный сигнал генератора 1 шума (диаграмма 37), прошедший коммутаторы 2 и фильтры 4 промежуточной частоты (диаграмма 37) поочередно с выхода коммутатора 5 (диаграммы 38, 39, 40), управляемого командами (диаграммы 38, 39, 40), поступает на входы фазовых детекторов 6, затем, пройдя их, фильтры 7 нижних частот и АЦП 8, шумовой сигнал, дискретизированный по времени, квантованный по уровню и представленный в двоичном коде на интервалах времени, соответствующих диаграмме 41, подается на входы блока 9, который за эти же интервалы времени (диаграмма 42, первые полупериоды обработки) производит дискретное преобразование Фурье по алгоритму БПФ. Таким образом, на выходе БПФ 9 (диаграмма 42, вторые полупериоды обработки) будут получены три последовательности спектральных отсчетов шумового сигнала, которые являются мгновенными спектрами шумового сигнала, прошедшего АЧХ трех фильтров 4 промежуточной частоты.

Считанный сигнал из блока 9 (диаграммы 42, вторые полупериоды), прошедший коммутатор 3 и поданный на первый вход сумматора 10 (диаграмма 44), затем обрабатывается за N периодов Тп по алгоритму в соответствии с выражением (1). Этот алгоритм реализуется с помощью следующих узлов устройства: сумматор 10, блоки 11 и 12 памяти, ключи 13, 15, 16, счетчики 17 и 18 адресов, блок 19 деления, регистр 20 кода нормирующего коэффициента. Управление работой этих узлов обеспечивается от синхронизатора 23 и двоичных счетчиков 24-26. Прошивка ПЗУ в синхронизаторе 23 соответствует временным диаграммам (фиг.2).

Вычисление суммы (без нормировки) производится на временных интервалах диаграмм 43 и 44 (между первой и второй вертикальными пунктирными линиями), где показаны первые три и последние три N-e периоды вычисления для каждого из трех фильтров 4 промежуточной частоты. Для этих вычислений информация, прошедшая сумматор 10, записывается в блок 11 памяти и подается с его выхода через открытый первый ключ 13 на второй вход сумматора 10, чтобы в результате повторения N подобных одинаковых операций обеспечить алгоритм суммирования (накопления) текущей входной информации сумматора 10 с суммой предыдущей текущей информации, поступающей на второй вход сумматора 10.

Для обеспечения синхронной работы сумматора 10 и первого блока 11 памяти производится одновременное открывание первого 13 и четвертого 16 ключей и синхронный счет адресов в первом счетчике 17 адресов на интервалах действия команд записи, считывания и запоминания (диаграмма 48) для первого блока 11 памяти.

Вычисленная таким образом сумма по выражению (1) переписывается из первого блока 11 памяти во второй блок 12 памяти через блок 19 деления, в котором осуществляется деление (нормировка) двоичной циф- ровой информации на коэффициент N (записанный и считываемый из регистра 20 кода нормирующего коэффициента N) на последних трех N-x периодах (диаграмма 45). Считывание суммы, нормировка и перепись информации об исходной форме АЧХ во второй блок 12 памяти обеспечивается синхронной работой четвертого ключа 16, первого счетчика 17 адресов, первого блока 11 памяти, блока 19 деления и регистра 20 кода нормирующего коэффициента, второго блока 12 памяти, второго счетчика 18 адресов и третьего ключа 15 (диаграммы 43, 45, 46, 48 и 49).

Таким образом, полученная информа- ция об исходной форме АЧХ устройства с учетом АЧХ трех фильтров 4 промежуточной частоты в соответствии с выражением (1) записана во второй блок 12 памяти. Нормировка информации о форме АЧХ (деление на N) обеспечивает постоянство среднего значения разрядности этой информации, что стабилизирует также средний коэффициент передачи информации в последующих циклах коррекции при любом значении коэффи- циен та N, численно равного количеству периодов обработки и накопления.

Режим коррекции является основным режимом работы устройства, в котором спектр сигнала, прошедшего все устройство от информационных входов 27-29 до первого входа умножителя 22 и несущий в себе информацию об искажениях, вызванных неидеальной формой АЧХ, корректируется путем перемножения в умножителе 22 на корректирующие множители, которые представляют собой обратные величины 1/К от усредненных амлпитудных значений К на каждом отсчете по частоте АЧХ устройства.

Корректирующие множители формируются в блоке 21 постоянной памяти, в ПЗУ которого защиты обратные функции 1/К от двоичного кода амплитудных значений К, считываемых из блока 12 памяти (диаграм- мы 46, 49) и передаваемых через ключ 14 (диаграмма 47) на блок 21 постоянной памяти, а с его выхода - на второй вход умножителя 22 для корректировки спектра основных сигналов, поступающих на пер- вый вход умножителя 22. При работе устройства в режиме коррекции участвуют все узлы устройства, кроме сумматора 10, блока 11 памяти, ключей 13 и 16, счетчика 17 адресов, блока 19 деления и регистра 20.

Временные диаграммы режима коррекции и чередующегося с ним режима записи (обновления) информации об изменившейся форме АЧХ изображены справа от второй вертикальной пунктирной линии на фиг.2. Сначала следуют три периода повторения, соответствующие коррекции вычисленных спектров сигналов, прошедших коммутаторы 2, а также последовательно во времени первый, второй и третий, фильтры 4 промежуточной частоты, затем три первых из mN периодов обновления записи информации об АЧХ. После трех точек на осях времени диаграмм показана последняя группа из шести периодов, состоящая из трех периодов коррекции и трех последних N-x периодов записи-обновления информации об изменившейся за это время форме АЧХ. В этих же последних трех периодах происходит перепись обновленной информации из блока 11 памяти в блок 12 памяти.

Работа узлов устройства в режиме записи исходной информации и в режиме записи обновленной информации об АЧХ, т.е. в разовом и чередующихся режимах, идентична и состоит в обоих случаях из mN периодов. На фиг.2 показан частный случай чередования режимов коррекции и перезаписи со

ГП IVloppeu

скважностью

m Mr

равной 1,

ГП Мщфезап

где Мкоррекц - число периодов коррекции за время одного цикла с чередующимися режимами. На практике обновления информации об АЧХ требуется реже, что зависит от скорости изменения формы АЧХ от температуры, окружающей узлы устройства, а также от скорости изменения температуры, т.е. может оказаться целесообразным т 1, что может быть реализовано в устройстве путем увеличения коэффициента деления во втором двоичной счетчике 24 путем записи в него соответствующего двоичного кода по низкому уровню команды диаграммы 50. Скорректированные спектры сигналов поступают с умножителя 22 на выход 32 устройства для дальнейшей обработки. Затем циклы работы с чередующимися режимами повторяются.

Таким образом, повторение циклов работы с чередующимися режимами позволяет отслеживать изменения уровня и формы АЧХ устройства во времени и учитывать эти изменения при корректировке вычисленного спектра основных сигналов устройства с точностью, определяемой выражением (1), более высокой при N 1.

Формула изобретения Устройство для вычисления спектра сигналов, содержащее генератор шумового

сигнала, пять коммутаторов, три фильтра промежуточной частоты, синхронизатор, два фазовых детектора, два фильтра нижних частот, два аналого-цифровых преобразователя, блок дискретного преобразования Фурье, сумматор, первый блок памяти, два ключа, блок постоянной памяти, умножитель, первый счетчик адресов, причем выход генератора шумового сигнала подключен к Первым информационным входам первого, второго и третьего коммутаторов, выходы которых подключены к входам соответственно первого, второго и третьего фильтров промежуточной частоты, выходы которых подключены соответственно к первому, второму и третьему информационным входам четвертого коммутатора, выход которого подключен к входам первого и второго фазовых детекторов, выходы которых подключены к входам соответственно первого и второго фильтров нижних частот, выходы которых подключены к информационным входам соответственно первого и второго аналого-цифровых преобразователей, выходы которых подключены к входам соответст: венно реальной и мнимой составляющих блока дискретного преобразования Фурье, выход которого подключен к информационному входу пятого коммутатора, первый и второй выходы которого подключены соответственно к первому входу умножителя и первому входу сумматора, выход которого подключен к информационному входу первого блока памяти, выход которого подключен к информационному входу первого ключа, выход которого подключен к второму входу сумматора, адресный вход первого блока памяти подключен к информационному выходу первого счетчика адресов, выход второго ключа подключен к адресному входу блока постоянной памяти, выход которого подключен к второму входу умножителя, выход которого является информационным выходом устройства, первым, вторым и третьим информаци- оннымии входами которого являются вторые информационные входы соответственно первого, второго и третьего коммутаторов, управ ляющие входы которых соединены ме/кду собой и подключены к первому выходу синхронизатора, управляющий сход первого ключа соединен с управляющим входом пятого коммутатора и вторым выходом синхронизатора, тактирующие входы блока дискретного преобразования Фурье и аналого-цифровых преобразователей соединены с третьим выходом синхронизатора, отличающее- С я тем, что, с целью повышения точности вычисления спектра сигналов, в него введены блок деления, второй блок памяти, второй

счетчик адресов, третий и четвертый ключи, регистр кода нормирующего коэффициента и три двоичных счетчика, причем выход первого блока памяти подключен к первому входу блока деления, выход которого подключен к информационному входу второго блока памяти, выход и адресный вход которого подключены соответственно к информационному входу второго ключа и к

0 информационному выходу второго счетчика адресов, счетный вход которого подключен к выходу третьего ключа, информационный вход которого подключен к информационному входу четвертого ключа, выход которого

5 подключен к счетному входу первого счетчика адресов, второй вход блока деления подключен к выходу регистра кода нормирующего коэффициента, первый выход синхронизатора подключен к входу запуска генератора шу0 мового сигнала, четвертый, пятый и шестой выходы синхронизатора подключены соответственно к первому, второму и третьему управляющим входам четвертого коммутатора, седьмой выход синхронизатора подклю5 чен к входу сброса блока дискретного преобразования Фурье, восьмой выход синхронизатора подключен к управляющему входу четвертого ключа, девятый выход синхронизатора подключен к входам сброса

0 аналого-цифровых преобразователей, десятый выход синхронизатора подключен к входу считывания регистра кода нормирующего коэффициента, третий выход синхронизатора подключен к информационному входу треть5 его ключа и к счетному входу первого двоичного счетчика, выход которого подключен к первому входу задания режима синхронизатора, второй и третий входы задания режима которого подключены соответственно к выхо0 дам второго и третьего двоичных счетчиков, одиннадцатый выход синхронизатора подключен к управляющему входу третьего ключа, двенадцатый выход синхронизатора подключен к управляющему входу второго

5 ключа, тринадцатый выход синхронизатора подключен к входам управления записью и счишванием первого блока памяти, четырнадцатый выход синхронизатора подключен к входам управления записью и

0 считыванием второго блока памяти, пятнадцатый выход синхронизатора подключен к с/оду записи коэффициента счета второго двоичного счетчика, счетный вход и выход которого подключены соответственно к вы5 ходу псрпого и счетному входу третьего двоичных счетчиков, вход пуска устройства подключен к входу пуска синхронизатора и к в/одьм установки исходного состояния перьогс, второго, третьего двоичных счетчи- коа и первого, второго счетчиков адресов.

Cvj

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления спектра сигналов | 1986 |

|

SU1363244A1 |

| Устройство для вычисления спектра сигналов | 1988 |

|

SU1649566A1 |

| Устройство для вычисления спектра сигналов | 1990 |

|

SU1803920A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Устройство корреляционной обработки широкополосных сигналов | 1989 |

|

SU1741274A2 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для выполнения преобразования Фурье | 1985 |

|

SU1278887A1 |

| Анализатор гармоник | 1988 |

|

SU1663571A1 |

Изобретение относится к вычислительной технике, в частности к устройствам спектрального анализа сигналов, представленных в цифровой форме. Целью изобретения является повышение точности вычисления спектра сигналов. Поставленная цель достигается тем, что в устройство, содержащее генератор 1 шумового сигнала, коммутаторы 2, 3, три фильтра 4 промежуточной частоты, коммутатор 5, два фазовых детектора 6, два фильтра 7 нижних частот, два аналого-цифровых преобразователя 8, блок 9 дискретного преобразования Фурье, сумматор 10, блок памяти 11, два ключа 13, 14, блок 21 постоянной памяти, умножитель 22, счетчик адресов 17, синхронизатор 23, дополнительно введены блок 19 деления, второй блок 12 памяти, второй счетчик 18 адресов, два ключа 15, 16, регистр 20 кода нормирующего коэффициента, три двоичных счетчика 24, 25, 26. Сущность изобретения заключается в том, что увеличивается точность вычисления спектра выходных сигналов за счет повышения точности определения усредненных значений АХЧ фильтров, которые вычисляются путем нахождения среднего значения из N отсчетов случайного шумового сигнала при N*981. 2 ил.

| ВысоцкийФ.Б | |||

| и др | |||

| Цифровые фильтры и устройства обработки сигналов на интегральных микросхемах | |||

| М.: Радио и связь, 1984, с | |||

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления спектра сигналов | 1986 |

|

SU1363244A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1991-07-30—Публикация

1989-09-01—Подача