входы которого соединены соответственно с выходом преобразователя напряжения в частоту и установочным входом накапливающего ререверсивного сумматора, выход реверсивного счетчика является выходом накапливающего реверсивного сумматора, вход преобразователя напряжения в частоту соединен с информационным входом накапливающего реверсивного сумматора и входом компаратора, а первый и второй входы логического элемента равнозначности соединены соответственно с выходом компаратора и входом управления реверсом накапливающего реверсивного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-дискретное интегрирующее устройство | 1985 |

|

SU1327128A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для автоматического переключения однофазных нагрузок в низковольтных распределительных сетях | 1981 |

|

SU1026234A1 |

| Аналого-дискретное интегрирующее устройство | 1986 |

|

SU1377875A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Аналоговый интегратор | 1986 |

|

SU1339592A1 |

| Способ цифрового управления многофазным инвертором | 1989 |

|

SU1683154A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Квадратор | 1986 |

|

SU1322273A1 |

1. УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ, содержащее интегрирующий усилитель, выходом подключенный к первому входу блока сравнения, второй вход которого является входом независимого аргумента устройства, а первый и второй выходы блока сравнения соединены соответственно с входом управления режимом работ интегрирующего усилителя и управляющим входом двухпозиционного переключателя, вькод которого соединен с информационным входом интегрирующего усилителя, первый и второй входы двухпозиционного переключателя, подключены к разнополярным шинам опорного напряжения, отличающееся тем, что, с целью повыщения точности интегрирования, в него введены блок деления на два, трехпозиционный переключатель, накапливающими реверсив-нын сумматор и блок управления, содержащий RS-триггер, D-триггер, три элемента И, элемент ИЛИ и инвертор, выход которого соединен с входом синхронизации р-триггера, а вход соединен с первыми входами элементов И и первым выходом блока сравнения, прямой выход RS:триггера соединен с информационным входом D-трнггера и вторыми входами первого и третьего элементов И, инверсный выход RS-триггера соединен с вторым входом второго элемента И, входы элемента ИЛИ соединены с выходами первого и второго элементов И, третьи входы которых соединены соотйетственно с инверсным, и пряллым выходами D-триггера, третий вход третьего элемента И соединен с прямым выходом D-трнггера, вход блока деления на два и первый вход трехпозиционного переключателя являются входом завнсимой переменной устройства, второй и третий входы трехпозиционного переключателя подключены соответственно к выходу деления на два и входу задания начальных условий устройства, первый и второй управляющие г входы трехпозиционного переключателя соединены соответственно с выходами третьего элемента и элемента ИЛИ блока управления, вход установки в единицу и первый вход установки в ноль RS-триггера которого являются соответственно входами пуска и останова устройства, второй вход установки в ноль RS-триггера и вход установки в но;|Ь D-триггера являются установочным входом О X) устройства и соединены с установочным входом накапливающего реверсивного сумма4 Kj тора, выход трехпозиционного переключателя соединен с информационным входом накапливающего реверсивного сумматора, вход управления реверсом которого подключен к второму выходу блока сравне ния, а выход является выходом устройства. 2. Устройство по п. 1, о т л и ч а ю щ е. е с я тем, что накапливающий реверсивный сумматор содержит преобразователь напряжения в частоту, реверсивный счетчик, компаратор и логический элемент равнозначности, выход которого соединен с входом реверса реверсивного счетчика, счетный и установочный

1

Изобретение относится к аналоговым вычислительным мащинам, в частности к устройства с выполнением вычислительных операдий путем измерения электрических величин, предназначенным для интегрирования, и может быть применено для контроля в различных отраслях промышленности, в частности в строительной механике для определения малодикловой долговечности изделий по характеристикам диаграмм их циклического упруго-пластического деформирования.

Известно устройство для интегрирования, реализующее принщт обобщенного интегрирования зависимой переменной по независимому невременному, аргументу методом трапеций, содержащее переключатели, экстраполяторы нулевого порядка, полусумматор, сумматор, накапливающий сумматор, перемножитель, генератор тактовых импульсов, блок управления и инвертор 1.

Недостатками этого устройства являются большая погрещность, вносимая блоком умножения, сложность блока умножения и сложность устройства в делом.

Наиболее близким к предлагаемому по технической сущности является устройство для интегрирования, содержащее два интегрирующих усилителя, блок сравнения, входы которого подключены соответственно к выходу второго интегрирующего усилителя и к входу независимого аргумента, а выходы соединены соответственно с входами управления режимом работы интегрирующих усилителей и управляющими входами переключателей, переключающие контакты которых подключены соответственно к входам интегрирующих усилителей, а переключаемые контакты переключателей соединены с разнополярными ишнами соответственно зависимой переменной и посТОЯ1ПЮГО напряжения 12J.

В блоке сравнения этого интегратора сравнивается независимый аргумент и выходной сигнал второго интегрирующего усилителя. При положительной; разности зтих сигналов

содержимое первого. интегрирующего усилител увеличивается на +Уг;, при отрицательной разности - уменьшается на - У, где У- значение зависимой переменной в момент времени t срабатывания блока сравнения. Поскольку на каждом такте i блок сравнения формирует сигналы включения интегрирующих усилителей при одинаковых значениях дх приращений .независимого аргумента, выходной сигнал интегратора Zt через п тактов пропорционален выражению

ГА

.-ПР

й.х5 Ч

(1)

L-1

т. е. обобщенному интегралу, вычисленному методом прямоугольников.

Недостатком данного устройства является низкая точность вычисления, поскольку метод прямоугольников обладает наибольшей погрешностью вьиислений по сравнению с другими известными методами численного интегрирования (1). Так, для аналогичных условий интегрирования методом трапеций ролучиМ следующее значение обобщенного интеграла:

Z; дхГУо/2 +.+ Yn/2) (2)

I

являющееся более точным (1). Следовательно, устройство-прототип с интегрированием прямо-, угольниками по сравнению с методом трапеций вносит погрешность

AZ Z - д x(), (3)

которая не постоя1ша и зависит от начального и конечного значений зависимой переменной, т. е. может быть весьма существенной.

Цель изобретения - повышение точности интегрирования.

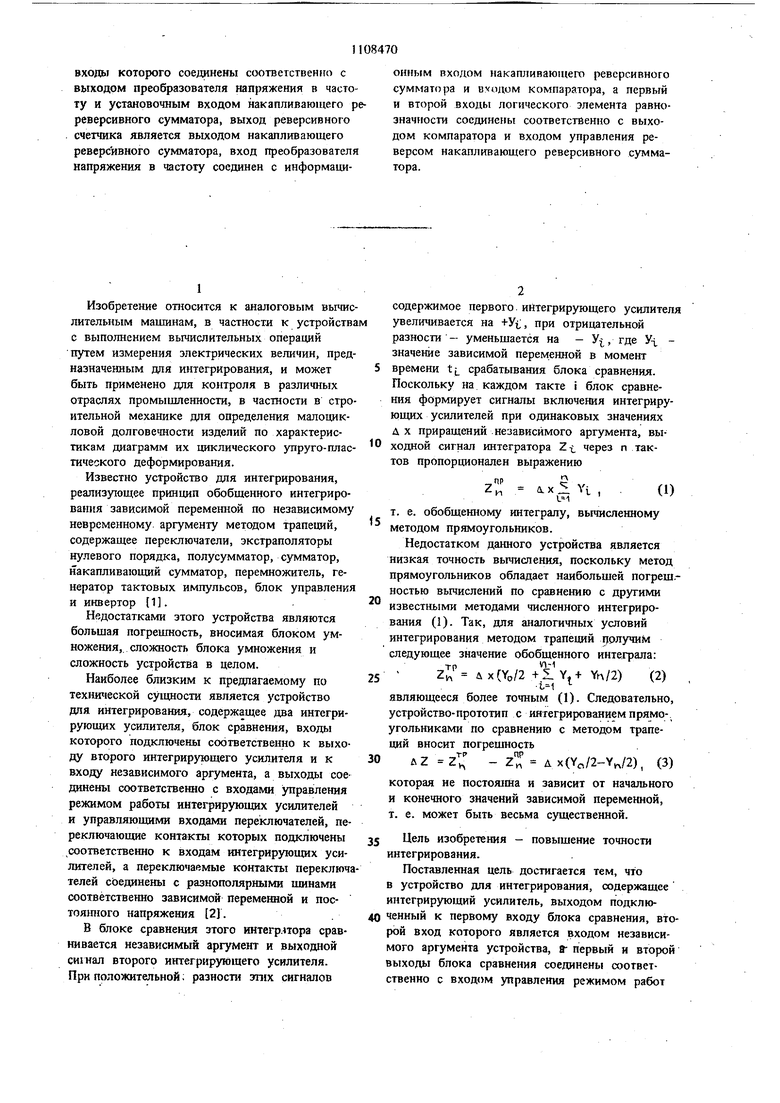

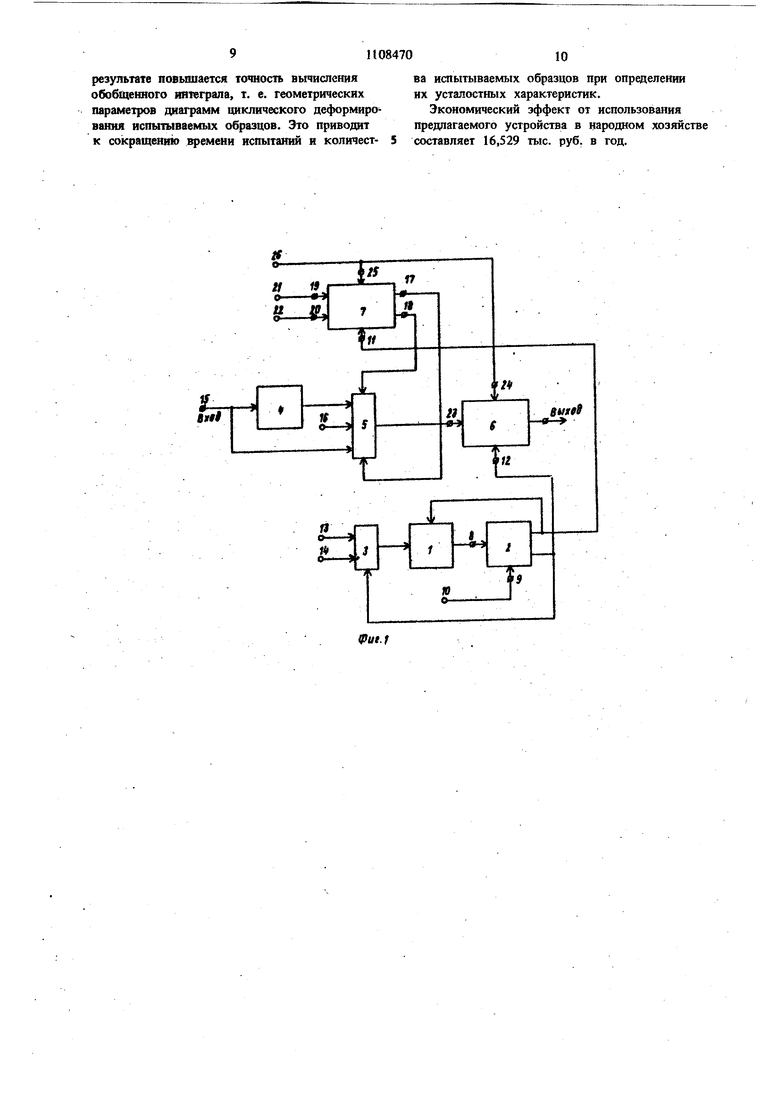

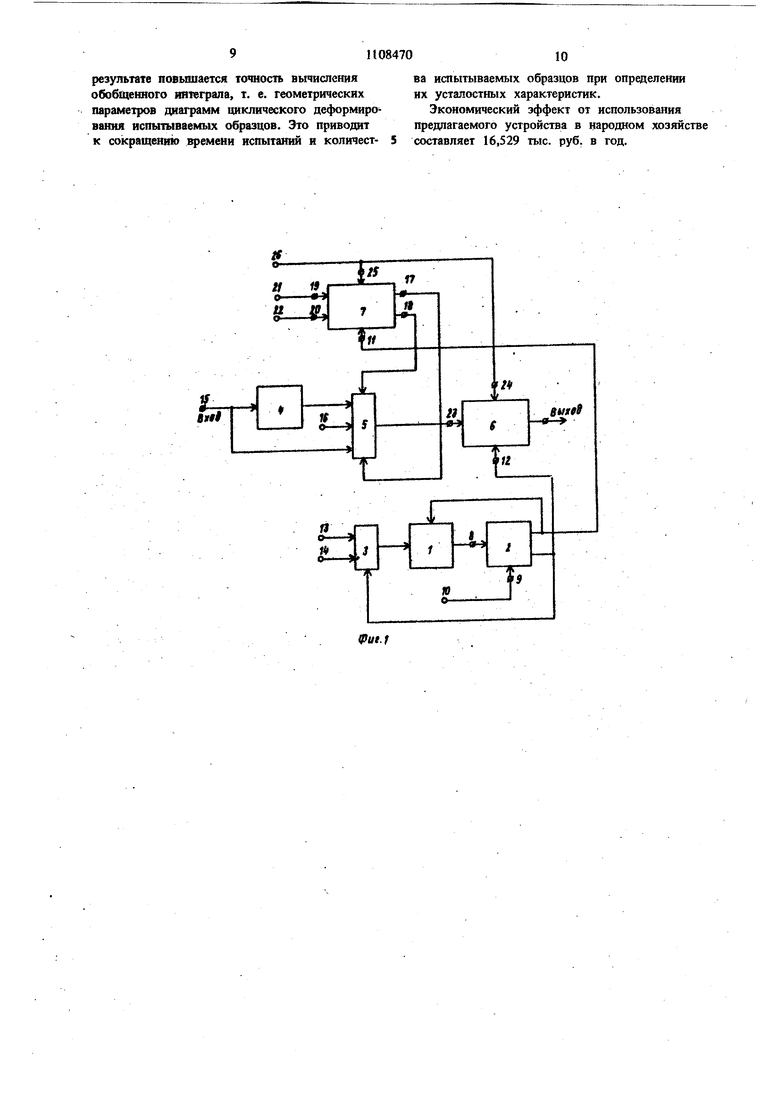

Поставленная цель достигается тем, что в устройство для интегрирования, содержащее интегрирующий усилитель, выходом подключенный к первому входу блока сравнения, второй вход которого является входом независимого аргумента устройства, Г первый и второй выходы блока сравнения соединены соответственно с входом управления режимом работ интегрирующего усилителя и управляющим . входом двухпозищюиного переключателя, выход которого соединен с информационным входом интегрирующего усилителя, первый и второй входы двухпозиционного переключателя подключены к разнополярным шинам опорног напряжения, введены блок деления на два, трехпозиционный переключатель, накапливающий реверсивный сумматор и блок управления, содержащий RS-триггер, D-триггер, три элемента И, элемент ИЛИ и инвертор, выход которого соединен с входом синхронизации D-триггера, а вход соединен с первыми входа ми элементов И и первым выходом блока сравнения, прямой выход RS-триггера соединей с информацио{гным .входом D-триггера и вторыми входами первого и третьего элементов И, инверсный выход RS-триггера соединен с вторым входом второго элемента И, входы элемента ИЛИ соединены с выходами первого и второго элементов И, третьи входы которы соединены соответственно с инверсньш и прямым выходами D-триггера, третий вход третьего элемента И соединен с прямым выходом D-.TpHrrepa, вход блока деления на два и первый вход трехпозиционного переключателя являются входом зависимой переменной устройства, второй и третий входы трехпозиционного переключателя подключены соответственно к выходу блока деления на два и входу задания начальных условий устройств первый и второй торавляющие входы трехпозиционного переключателя соединены соответственно с выходами третьего элемента и эле-1 мента ИЛИ блока управления, вход установки в единицу и первый вход установки в ньль RS-триггера которого являются соответственно входами пуска и останова устройства, второй вход установки в ноль RS-триггера и вход установки в ноль D-триггера является установочным входом устройства и соединены с установочным входом накапливающего реверсивного сумматора, выход трехпозиционного переключателя соединен с информаш онным входом накапливающего реверсивного сумматора, вход управления реверсом которого подключен к второму выходу блока сравнения, а выход является выходом устройства. Накапливающий реверсивный сумматор содержит преобразователь напряжения в частоту, реверсивный счетчик, компаратор и логическ т элемент равнозначности, выход icoторого соединен с входом реверса реверсивного счетчика, счетный и установочный входы которого соединены соответственно с выходом преобразователя напряжения в частоту и ; установочным входом накапливающего реверси ного сумматора, выход реверсивного счетчика является выходом накапливающего реверсивного сумматора, вход преобразователя напряжения в частоту соединен с информационным входом накапливающего реверсивного сумматора и входом компаратора, а первый и второй входы логического элемента равнозначности соединены соответственно с выходом компаратора и входом управления реверсом накапливающего реверсивного сумматора. На фиг. 1 показана блок-схема устройства для интегрирования; на фиг. 2 - функциональная схема накапливающего реверсивного сумматора; на фиг. 3 - функциональная схема блока управления. Устройство для интегрирования (фиг. 1) содержит интегрирующий усилитель 1, блок 2 сравнения, двухпозиционный переключатель 3, блок 4 деления на два, трехпозиционный переключатель 5, накапливающий реверсивный сумматор 6 и блок 7 управления. Вход и выход интегрирующего усилителя 1 подключены соответственно к выходу двухпозиционного переключателя 3 и входу 8 блока 2 сравнения, вход 9 блока 2 сравнения соединен с входом 10 независимого аргумента, первьгй выход блока 2 сравнения подключен к входу управления режимом работы интегрирующего усилителя I и синхронизируемому входу 11блока 7 управления. Второй выход блока 2 сравнения соединен с управляющим входом двухпозиционного переключателя 3 и входом 12управления реверсом накапливающего реверсивного сумматора 6, а входы переключателя 3 соединены с ра;знополярными ишнами положительного 13 и отрицательного 14 опорных напряжений. Вход блока 4 деления на два соединен с первым входом трехпозиционного переключателя 5 и входом 15 зависимой переменной, а выход блока 4 деления на два соединен с третьим входом трехпозиционного переключателя 5, второй переключаемый вход которого подключен к входу 16 задания начальных условий, входы управления первым и третьим входами трехпозиционного переключателя 5 соединены соответственно с первым 17 и вторым 18 выходами блока 7 управления, первый 19 и второй 20 входы управления которого подключены к клемам пуска 21 и останова 22. Выход трехпозиционного переключателя .5 соединен с информационным входом 23 накапливающего реверсивного сумматора 6, установочный вход 24 которого соеданен с уствновочиым входом 25 блока 7 управления и клеммой 26 предварительной установки устройства для интегрирования, а выход накапливающего реверсивйого сумматора 6 является выходом устройства для интегрирования. 511 Накапливающий реверсивный сумматор 6 (фиг. 2) состоит из преобразователя 27 йапря жения в частоту, реверсивного счетчика 28, компаратора 29 и логического -элемента 30 равнозначности, входы которого соеданены с выходом компаратора 29 и входом 12 управления реверсом накапливающего реверсивного сумматора 6, а выход подключен к входу управления реверсом реверсивного счетчика 28 информационный и установочный входы которого в свою очередь соединены соответственно с выходом преобразователя 27 напряжения в частоту и установочным входом 24 накапливающего реверсивного сумматора 6. Входы преобразователя 27 напряжения в частоту и компаратора 29 соединены с информа1ЩОННЫМ входом 23 накапливающего реверсив ного сумматора 6, выходом которого служат выходы реверсивного счетчика 28. Блок 7 управления (фиг. 3) состоит из RS-триггера 31 со сбросом и установкой, D-триггера 32 задержки, трех элементов И 33, 34 и 35, элемента ИЛИ 36 и инвертора 37, выход которого соединен с входом сипхронизации О-триггера, а вход подключен к третьим входам 3-входовых элементов И 33 34 и 35 и синхронизируемому: входу 11 блок 7 управления. Прямой выход триггера со сбро сом и установкой 31 соединен с информационным входом триггера 32 задержки и с первыми входами первого 33 н третьего 35 элементов И, инверсный выход триггера сб сбросом и установкой 31 подключен к первому входу второго элемента И 34, входу установки в единицу и первый вход установки в ноль триггера со сбросом и установкой 31 соединены с первым 19 и вторым- 20 входом управления блока 7 управления, а второй вхо установки в ноль триггера со сбросом и уста новкой 31 соединен с входом установки в ноль триггера 32 задержки и установочным входом 25 блока 7 управления. Прямой выход триггера 32 задержки соединен с вторым входами второго 34 и третьего 35 элементов И, а инверсный выход этого триггера соединен с вторым входом первого элемента И 33, выход которого подключен к первому входу элемента ИЛИ 36, второй вход которого соединен с выходом второго элемента И 34, а выход элемента ИЛИ 36 соединен с вторым выходом 18 блока 7 управления, первый выход 17 которого, в свою очередь, подключен к выходу третьего элемента И 35 Устройство работает следующим образом. При подаче сигнала на клемму 26 предварительной установки устройства он поступает на установочные входы 24 накапливающего реверсивного сумматора 6 и 25 блока 7 управления, устанавливая в нулевое состояние реверсивный счегшк 28, триггер 31 со сбросом и установксй н трииер 32 задержки, тем самым очищая устройство от предыдущей информации. По необходимое™ перед пуском устройства для интегрирования в него могут быть занесены начальные условия, для чего они подаются на вход 16 задания начальных условий и через замкнутый с выходом второй переключаемый вход трехпозиционного переключателя 5 поступает на информационный вход 23 накапливающего реверсивного сумматора 6, фиксируясь в последнем. Госле включения питания на вход интегрирующего усилителя 1 через переключатель 3 выборочно подается опорное напряжение с разнополярных щин 13 и 14 опорного напряжения, в силу чего на выходе интегрирующего усилителя 1 имеет место линейно увеличивающееся или уменьщающееся напряжение U,(t), пропорциональное времени t. На первом выходе блока 2 сравнения формируется сигнал синхронизации, переводящий интегрирующий усилитель 1 в режим интегрирования при отсутствии равенства напряжения и (t) и сигнала независимого аргумента x(t) на вьгходах 8 и 9 соответственно блока 2 сравнения. При равенстве (J(t) (t) сигнал синхронизации исчезает и интегрирующий усилитель 1 переводится в режим хранения информации. На втором выходе блока 2 сравнения формируется сигнал реверса переключателя 3 и накапливающего реверсивного сумматора 6. При положительном знаке разности сигналов x(t)-U (t), т. с. возрастающем характере функции x(t), переключатель 3 коммутирует к входу интегрирующего усилителя 1 положительное опорное напряжение щины 13, а накапливающий реверсивный сумматор 6 переводится в режим суммирования. При отрицательном знаке разности x(t)-U.f (t), г. е. убывающем характере функции x(t), к входу интегрирую щего усилителя 1 коммутируется отрицательное опорное напряжение шины 14, а накапливающий реверсивный сумматор 6 переводится в режим вычитания. В результате напряжение ,«J (t) на выходе интегрирующего усилителя 1 аппроксимирует сигнал независимого аргумента x(t) с шагом квантования по уровню, равным зоне нечувствительности лх блока 2 сравнения, а сигналы синхронизации на первом выходе этого блока формируются в моменты tj, времени, соответствующие условию X(tt4,| )-X(tv) ДХ Сигналы синхронизации с первого выхода лока 2 сравнения поступают на синхронизирумый вход 11 блока 7 управления. После оявления сншала пуска на клемме 21 пуска он поступает на первый вход 19 управления блока 7 управления и устанавливает в единичное состояние триггер 31 со сбросом и установкой, подготавливая к включению первый элемент И 33 и триггер 32 задержки по его информационному входу. При поступлении на синхронизируемый сход 11 первого сигнала синхронизавди с первого выхода блока 2 сравнения он через инвертор 37 переключает триггер 32 задержки в единично состояние по окончании сигнала синхронизации. Одновременно последний проходит чер первый элемент И 33 и элемент ИЛИ 36 на второй выход 18 блока 7 управления, воздействуя на вход управления третьим переключаемым входом трехпозидионного переключателя 5. В результате в накапливающий реверсивный сумматор 6 через его информационный вход 23 с выхода блока 4 деления на два поступает первое значение зависимой переменной, равной У /2, где t д- время формирования первого, после появления сигнала пуска, сигнала синхронизации на первом выходе блока 2 сравнения. Второй и последующие сигналы синхрониза ции пропускаются на первый выход 17 блока 7 управления, поскольку после установки в единицу триггера 32 задержки первым сиг налом синхронизации первый элемент И 33 и второй элемент И 34 блокируются нулевы-: ми сигналами с инверсных выходов триггера 32 задержки и триггера 31 со сбросом и установкой соответственно, а третий элемент И 35 подготавливается к включению единичным сигналом с прямых выходов триггера 3 задержки и триггера 31 со сбросом и установкой, В результате трехпозидионный переключатель 5 управляется по входу управлени своим первым переключаемым входом, и с входа 15 зависимой переменной в накапл1}ва,ющий реверсивный сумматор 6 через его информационный вход 23 поступит) значения зависимой переменной, где i 1, 2, 3,...; t - моменты срабатывания блока 2 сравне ния. Содержимое накапливающего реверсивно сумматора увеличивается на на. каждом i-M моменте времени поступления сигнала синхронизации. При необходимости вычитания очередного значения зависимой переменной на вход 12 реверса накапливающего реверсивного сумматора поступает сигнал реверса с второг выхода блока 2 сравнения. Если знак сигнал зависимой переменной на информационном входе 23 накапливающего реверсивного сумматора 6, определяемый компаратором 29, совпадает со знаком опорного напряжения на шинах 13 и 14, то схема 30 эквивалентности устанавливает реверсивный счетчик 28 режим суммирования, импульсных сигналов с выхода преобразователя 27 напряжения в частоту с частотой, пропорциональной значению зависимой переменной У (t). Если знак сигнала зависимой перемешгой и знак опорного напряжения различ1гые, то элемент 30 эквивалентности переводит реверсивный счетчик 28 в режим вычитания импульсных сигналов с выхода преобразователя 27 напряжения в частоту. В результате содержимое реверсивного счетчика изменяется во времени в соответствии с вычисляемым значением интеграла по независимому невременному аргументу. Для окончания интегрирования на кЛемму 22 останова подается сигнал останова, который через второй вход 20 управления блоком 7 управления поступает на первый вход установки в ноль триггера 31 со сбросом и установкой, переключая последний в нулевое состояние. При этом триггер 32 задержки переключается в нулевое состояние по заднему фронту первого, cлeдJ oщeгo за сигналом останова, сигнала синхронизации, пропуская этот сигнал синхронизации через подготовленный к включению второй элемент И 34 и элемент. ИЛИ 36 на второй выход 18 блока управления, а через него - на вход управления третьим переключаемым входом трехпозиционного переключателя 5. & результате в накапливающий реверсивный сумматор поступит последнее значение зависимой переменной y(ta)/2, прощедщее через блок 4 деления на два, где t - момент, формирования первого, после сигнала останова, сигнала синхронизации на первом выходе блока 2 сравнения. Таким образом за время между моме1ггами, определяемыми поступлением сигналов пуска и останова, содержащее п тактов интегрирования, содержимое накапливающего реверсивного сумматора 6 равно (4) А где Z - начальные условия, что с точностью до постоянного множителя лх, равного зоне нечувствительности блока 2 сравнения, пропорционально обобщенному интегралу . г„/ г вычисленному методом трапеций. Использование новых элементов: блока деления на два, трехпоэиционного переключателя, накапливающего реверсивного сумматора и.блока управления, выгодно отличает пред-ь лагаемое устройство для интегрирования от: прототипа, так как исключается присущая прототипу погрешность интегрирования. В

результате повышается точность вычисления обобщенного интеграла, т. е. геометрических параметров диаграмм циклического деформирования испытываемых образцов. Это приводит к сокращению времени испытаний и количест110847010

ва испытываемых образцов при определении их усталостных характеристик.

Экономический эффект от использования предлагаемого устройства в народном хозяйстве составляет 16,529 тыс. руб. в год.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для интегрирования | 1976 |

|

SU596968A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Интегратор | 1979 |

|

SU807327A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1983-05-11—Подача