Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей информации из параллельной формы в последовательную.

Цель изобретения - расширение области применения за счет возможности управления параметрами преобразования.

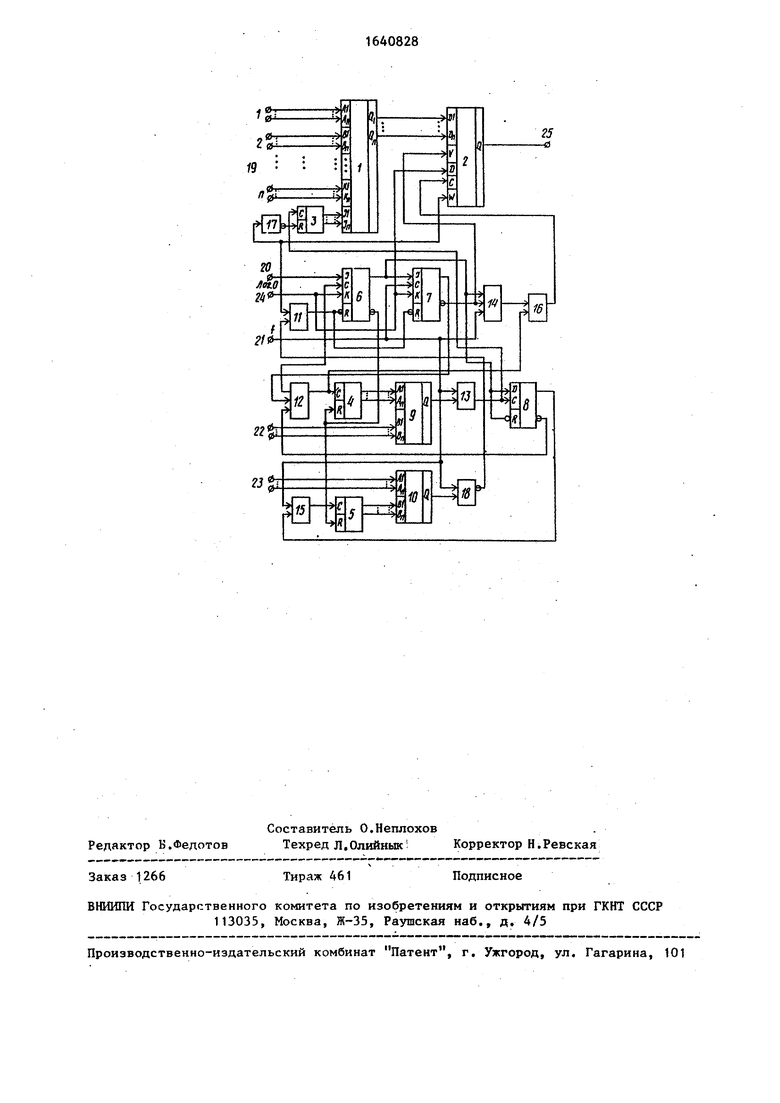

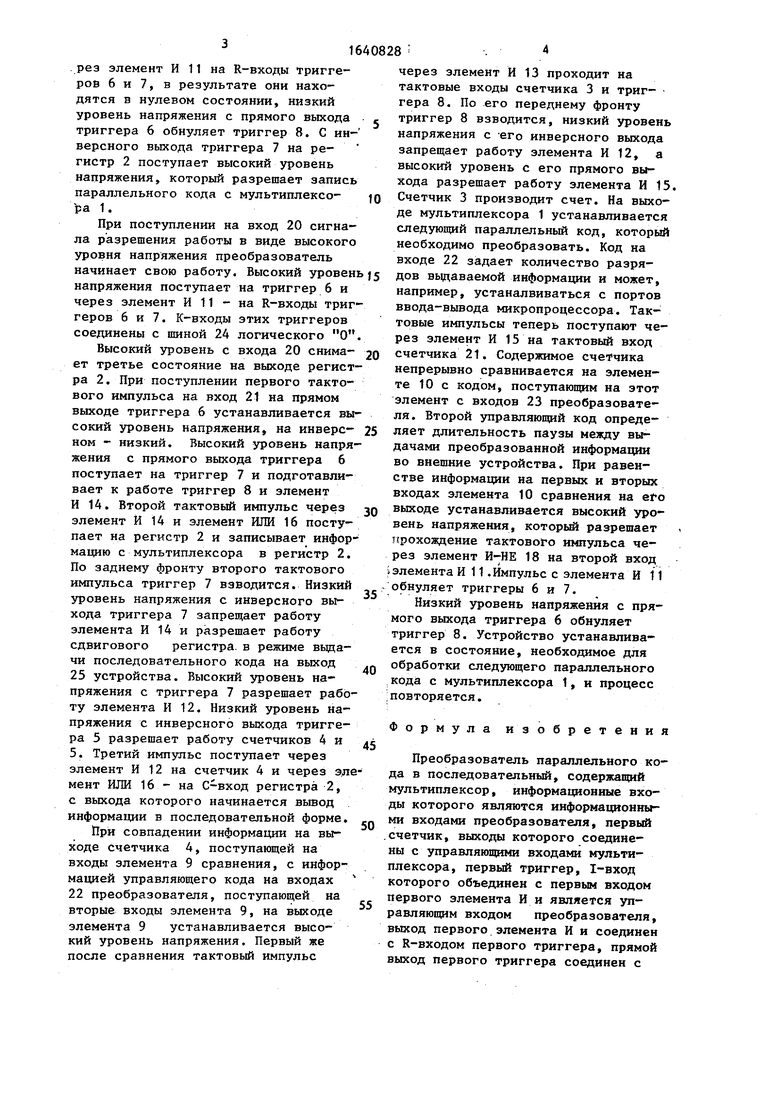

На чертеже представлена схема преобразователя.

Преобразователь содержит мультиплексор 1, регистр -2 сдвига, первый - третий счетчики 3-5, первый-третий триггеры 6-8, первый и второй элементы 9 и 10 сравнения, первый-пятый элементы И 11-15, элемент ИЛИ 16, элемент НЕ 17, элемент И-НЕ 18, информационные 19, управляющий 20, тактовый 21, первый и вторые 22 и 23 управляющие входы

преобразователя, шину лог.О 24 и выходы 25 преобразователя.

Преобразователь работает следующим образом.

Перед началом преобразования элементы устройства находятся в исходном состоянии. На управляющем входе 20 преобразователя находится низкий уровень напряжения. Этот уровень поступает через элемент 17 на счетчик 3, откуда на все шины управления мультиплексора 1 поступают сигналы низкого уровня. В результате на выходе мультиплексора устанавливается необходимый для преобразования первый по счету код, поступающий с одной из п групп входов 19 преобразователя. Низкий уровень с входа 20 лодается на разрешающий вход регистра 2 и управляет третьим состоянием выхода 25 преобразователя. Тот же уровень с входа 20 подается чео

Јъ

О 00

1C

00

рез элемент И 11 на R-входы триггеров 6 и 7, в результате они находятся в нулевом состоянии, низкий уровень напряжения с прямого выхода триггера 6 обнуляет триггер 8. С инверсного выхода триггера 7 на регистр 2 поступает высокий уровень напряжения, который разрешает запись параллельного кода с мультиплексора 1.

При поступлении на вход 20 сигнала разрешения работы в виде высокого уровня напряжения преобразователь начинает свою работу. Высокий уровен напряжения поступает на триггер 6 и через элемент И 11 - на R-входы триггеров 6 и 7. К-входы этих триггеров соединены с шиной 24 логического О

Высокий уровень с входа 20 снима- ет третье состояние на выходе регистра 2. При поступлении первого тактового импульса на вход 21 на прямом выходе триггера 6 устанавливается высокий уровень напряжения, на инверс- ном - низкий. Высокий уровень напряжения с прямого выхода триггера 6 поступает на триггер 7 и подготавливает к работе триггер 8 и элемент И 14. Второй тактовый импульс через элемент И 14 и элемент ИЛИ 16 поступает на регистр 2 и записывает информацию с мультиплексора в регистр 2. По заднему фронту второго тактового импульса триггер 7 взводится. Низкий уровень напряжения с инверсного выхода триггера 7 запрещает работу элемента И 14 и разрешает работу сдвигового регистра, в режиме выдачи последовательного кода на выход 25 устройства. Высокий уровень напряжения с триггера 7 разрешает работу элемента И 12. Низкий уровень напряжения с инверсного выхода триггера 5 разрешает работу счетчиков 4 и 5. Третий импульс поступает через элемент И 12 на счетчик 4 и через элмент ИЛИ 16 - на С-вход регистра 2, с выхода которого начинается вывод информации в последовательной форме.

При совпадении информации на выходе счетчика 4, поступающей на входы элемента 9 сравнения, с информацией управляющего кода на входах 22 преобразователя, поступающей на вторые входы элемента 9, на выходе элемента 9 устанавливается высокий уровень напряжения. Первый же после сравнения тактовый импульс

0

5

0 5 0

5

0

0

через элемент И 13 проходит на тактовые входы счетчика 3 и триггера 8. По его переднему фронту триггер 8 взводится, низкий уровень напряжения с -его инверсного выхода запрещает работу элемента И 12, а высокий уровень с его прямого выхода разрешает работу элемента И 15. Счетчик 3 производит счет. На выходе мультиплексора 1 устанавливается следующий параллельный код, который необходимо преобразовать. Код на входе 22 задает количество разрядов выдаваемой информации и может, например, устаналвиваться с портов ввода-вывода микропроцессора. Тактовые импульсы теперь поступают через элемент И 15 на тактовый вход счетчика 21. Содержимое счетчика непрерывно сравнивается на элементе 10 с кодом, поступающим на этот элемент с входов 23 преобразователя. Второй управляющий код определяет длительность паузы между выдачами преобразованной информации во внешние устройства. При равенстве информации на первых и вторых входах элемента 10 сравнения на его выходе устанавливается высокий уровень напряжения, который разрешает прохождение тактового импульса через элемент И-НЕ 18 на второй вход ;элемента И 11.Импульс с элемента И 11 обнуляет триггеры 6 и 7.

Низкий уровень напряжения с прямого выхода триггера 6 обнуляет триггер 8. Устройство устанавливается в состояние, необходимое для обработки следующего параллельного кода с мультиплексора 1, и процесс повторяется.

Формула изобретения

Преобразователь параллельного кода в последовательный, содержащий мультиплексор, информационные входы которого являются информационными входами преобразователя, первый .счетчик, выходы которого соединены с управляющими входами мультиплексора, первый триггер, 1-вход которого объединен с первым входом первого элемента И и является управляющим входом преобразователя, выход первого элемента И и соединен с R-входом первого триггера, прямой выход первого триггера соединен с

I-входом второго триггера, прямой выход которого соединен с первым входом второго элемента И, тактовый вход второго триггера является тактовым входом устройства, третий-пя- тый элементы И и элемент ИЛИ, о т- личающийся тем, что, с целью расширения области применения, за счет возможности управления параметрами преобразования, в преобразователь введены второй и третий счетчики, элементы сравнения, элемент И-НЕ, элемент НЕ, третий тригге

,

40828

соединен с вторым входом первого элемента И, выход третьего элемента И соединен с С-входами третьего триг- с гера и первого счетчика, R и D-входы третьего триггера и первый вход четвертого элемента И объединены и под- , ключены к прямому выходу первого

триггера, прямой и инверсный выходы to третьего триггера соединены соответственно со вторым входом пятого элемента И и вторым входом второго элемента И, выходы пятого элемента И соединены с С-входом третьего счет

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный распределитель | 1988 |

|

SU1569970A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ДВОИЧНЫХ КОДОВ ХЕММИНГА | 1999 |

|

RU2161369C1 |

| Многоканальное устройство для ввода информации | 1989 |

|

SU1612290A2 |

| Устройство для выделения и вычитания импульсов из последовательности импульсов | 1987 |

|

SU1443153A1 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство для регистрации телевизионного изображения | 1989 |

|

SU1720168A1 |

| Преобразователь серии импульсов в прямоугольный импульс | 1986 |

|

SU1383473A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Компаратор | 1990 |

|

SU1755253A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей информации из параллельной формы в последовательную. Цель изобретения - расширение области применения за счет возможности управления параметрами преобразования. Преобразователь содержит мультиплексор 1, регистр 2 сдвига, первый-третий счетчики 3-5, первый - третий триггеры 6-8, первый и второй элементы 9 и 10 сравнения,- первый - пятый элементы И 11- 15, элемент ИЛИ 16, элемент НЕ 17, элемент И-НЕ 18, информационные 19, управляющий 20, тактовый 21, первые и вторые 22 и 23 управляющие входы преобразователя, шину 24 лог.О и выход 25 преобразователя. 1 ил.

шина логического нуля и регистр сдви- 15 чика, выход второго элемента И соега, выход которого является выходом преобразователя, выходы мультиплексора подключены к соответствующим входам параллельной загрузки регистра сдвига, D-вход регистра сдвига, К- входы первого и второго тригсеров - объединены и подключены к шине логического нуля, инверсный выход первого триггера подключен к R-входам второго и третьего счетчиков, выходы которых подключены к соответствующим первым входам соответствующих элементов сравнения, вторые входы которых являются соответственно первыми и вторыми установочными входами преобразователя, выходы элементов сравнения подключены к первым входам соответственно третьего элемента И и элемента И-НЕ, выход элемента И-НЕ

динен с С-входом второго счетчика и первым входом элемента ИЛИ, выход которого соединен с С-входом регистра сдвига, инверсный выход второго триггера соединен с V-входом регистра сдвига и вторым входом четвертого элемента И, выход которого соединен с вторым входом элемента ИЛИ, W-вход регистра сдвига и вход элемента НЕ 5 объединены и подключены к управляющему входу преобразователя, выход элемента НЕ соединен с R-входом первого счетчика, С-вход первого триггера, третьи входы второго и четвертого элементов И, вторые входы третьего и пятого элементов И и элемента И-НЕ объединены и подключены к тактовому входу преобразователя.

0

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1243097A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-04-07—Публикация

1987-12-17—Подача