Изобретение относится к вычислительной технике и может быть использовано в системах управления и связи для преобразования аналогового сигнала в цифровой.

Известен компаратор, содержащий элемент сравнения аналоговых напряжений, триггер Шмидта, первый и второй одновиб- раторы.

Известен также компаратор, содержащий элемент сравнения аналоговых напряжений, элемент НЕ, первый, второй и третий триггеры и элемент И.

Недостатком данных устройств является низкая стабильность работы, так как элемент сравнения аналоговых напряжений может работать на границе разрешающей способности и на выходе устройств формируются сигналы, не отражающие точно результат сравнения аналоговых напряжений и являющиеся нестабильными по времени.

Наиболее близким по технической сущности к предлагаемому является компаратор, содержащий операционный усилитель (ОУ), неинвертирующий вход которого является информационным входом компаратора, инвертирующий вход - опорным входом компаратора, первый элемент НЕ, вход которого соединен с выходом ОУ, генератор тактовых импульсов, первый триггер, J-вход которого соединен с выходом ОУ, К-вход которого соединен с выходом первого элемента НЕ, С-вход которого соединен с выходом генератора тактовых импульсов, первый элемент задержки, вход которого соединен с выходом генератора тактовых импульсов, первый элемент И, первый вход которого соединён с выходом первого триггера, второй вход которого соединен с выходом первого элемента задержки, регистр сдвига, D-вход которого соединен с выхоч л

СЛ Ю СЛ СО

дом первого триггера, С-вход которого соединен с выходом элемента И, первый счетчик импульсов, С-вход которого соединен с выходом генератора тактовых импульсов, первый дешифратор, вход которого соеди- нен с выходом первого счетчика импульсов, второй счетчик импульсов, С-вход которого соединен с выходом генератора тактовых импульсов, второй дешифратор, вход которого соединен с выходом второго счетчика импульсов, второй элемент задержки, вход которого соединен с выходом первого дешифратора, третий элемент задержки, вход которого соединен с выходом второго дешифратора, первый логический блок срав- нения, вход которого соединен с первым выходом регистра сдвига, С-вход которого соединен с выходом первого дешифратора, второй логический блок сравнения, вход которого соединен с вторым выходом регист- ра сдвига, С-вход которого соединен с выходом второго дешифратора, второй триггер, S-вход которого соединен с выходом Равно первого логического блока сравнения, третий логический блок сравне- ния, первый вход которого соединен с инверсным выходом второго триггера и соединен с входом Разрешение первого счетчика импульсов, второй вход которого соединен с выходом Больше первого ло- гического блока сравнения, третий вход которого соединен с прямым выходом второго триггера и соединен с входом Разрешение второго счетчика ир-чпульсов, четвертый вход которого соединен с выходом второго логического блока сравнения, четвертый логический блок сравнения, первый вход которого соединен с выходом второго элемента задержки, второй вход которого соединен с инверсным выходом второго триггера, третий вход которого соединен с выходом третьего элемента задержки, четвертый вход которого соединен с прямым выходом второго триггера, четвертый элемент задержки, вход которого соединен с выходом четвертого логического блока сравнения и соединен с R-входами первого счетчика импульсов, второго счетчика импульсов, регистра сдвига, второго триггера, выход которого является стробирующим вы- ходом компаратора, второй элемент НЕ, вход которого соединен с выходом четвертого логического блока сравнения, третий триггер, D-вход которого соединен с выходом третьего логического блока сравнения, С-вход которого соединен с выходом второго элемента НЕ, прямой и инверсный выходы которого являются инверсным и прямым выходами компаратора,

Недостатком данного компаратора является его функциональная сложность, обусловленная наличием двух схемных цепей управления и анализа (счетчик импульсов, дешифратор, элемент задержки, логический блок сравнения) и сложность изменения эталонных кодов сравнения в логических блоках сравнения.

Цель изобретения - упрощение компаратора, обеспечивающее при сокращении общего числа элементов на 25-30% сохранение быстродействия,стабильности и точности. Кроме того повышается гибкость в управлении компаратором за счет появления возможности изменять во время работы эталонные коды сравнения, используемые в компараторе для анализа входной информации.

Существенные признаки, отличающие данный компаратор от известного состоят во введении первого мультиплексора, второго мультиплексора и третьего элемента НЕ.

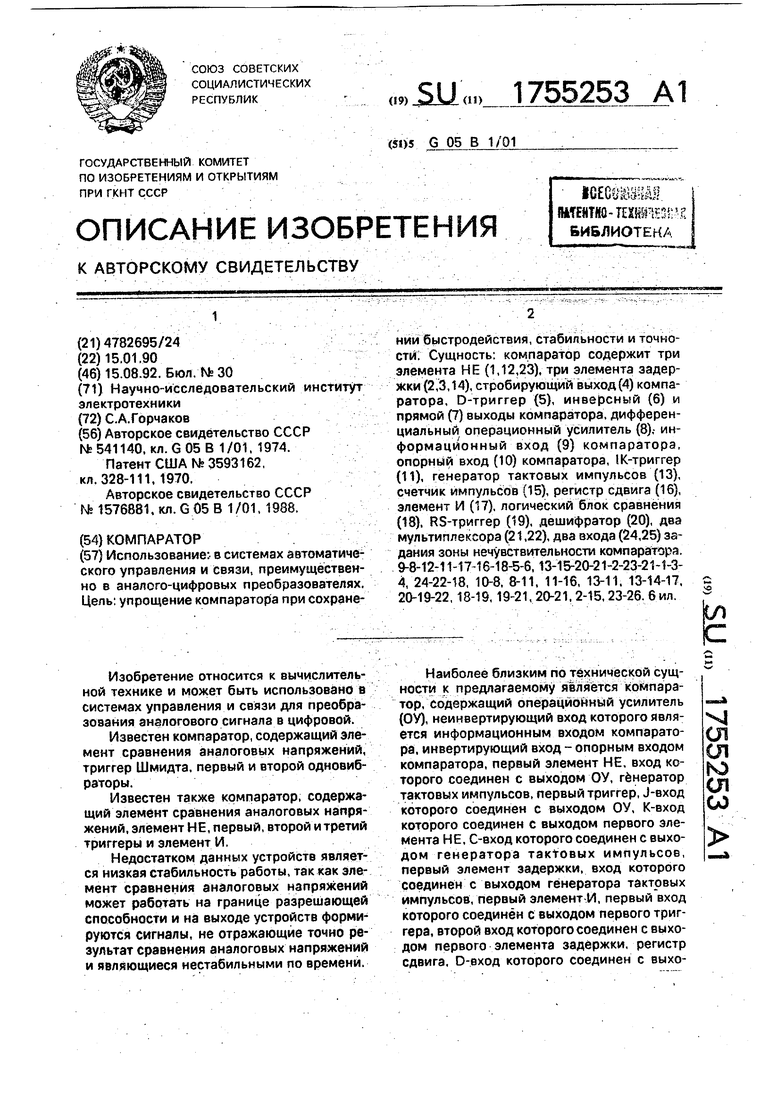

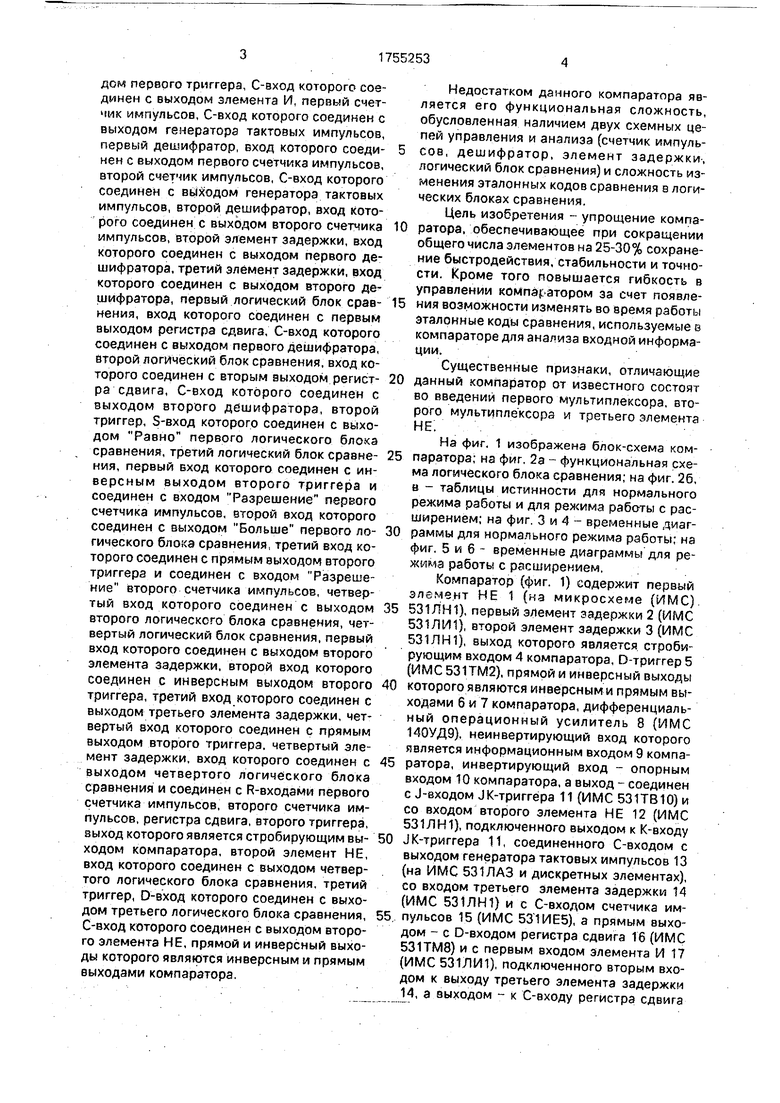

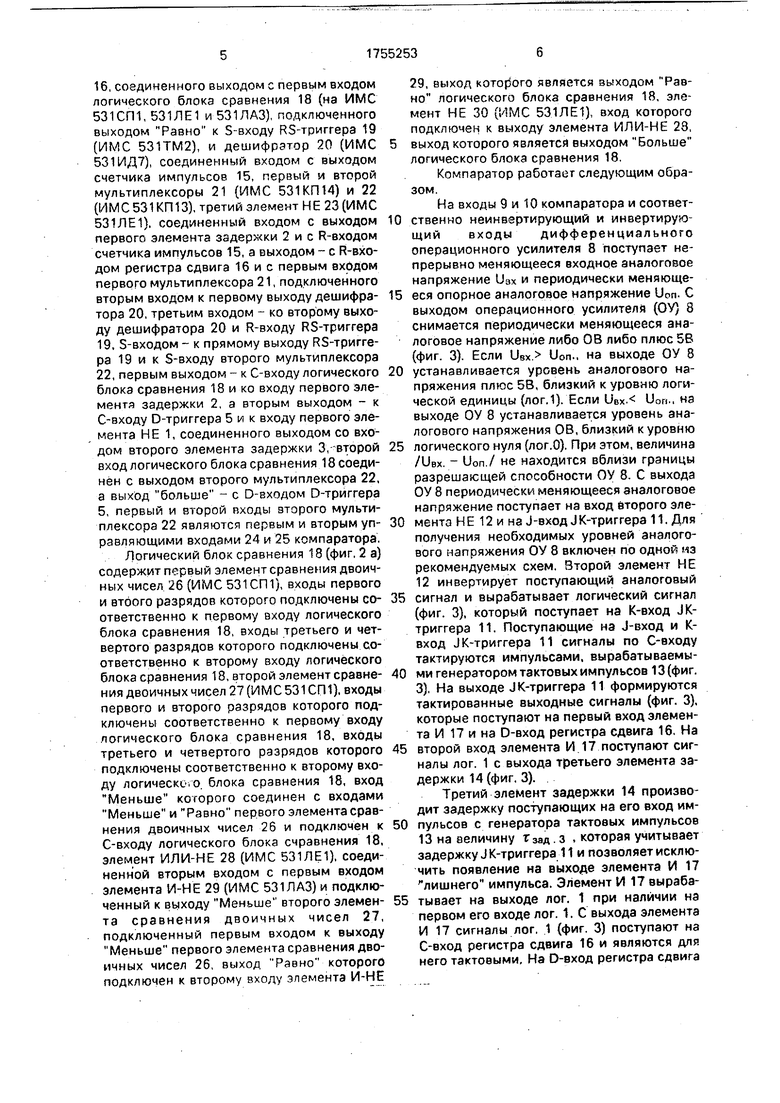

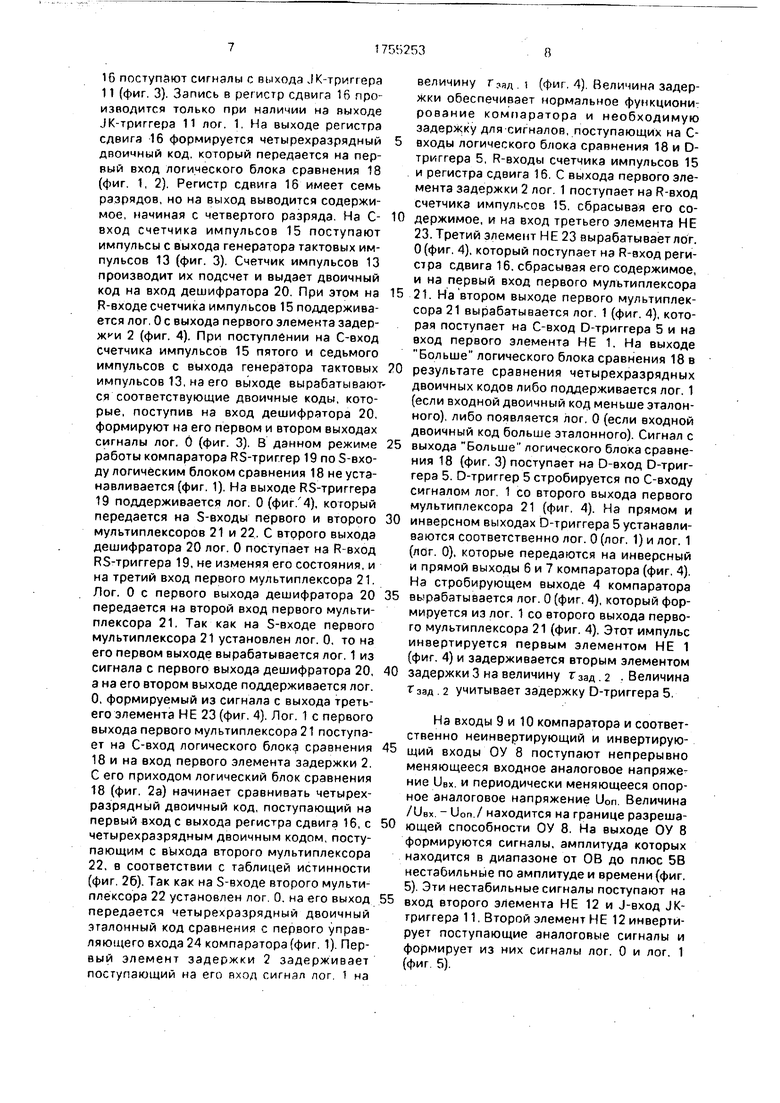

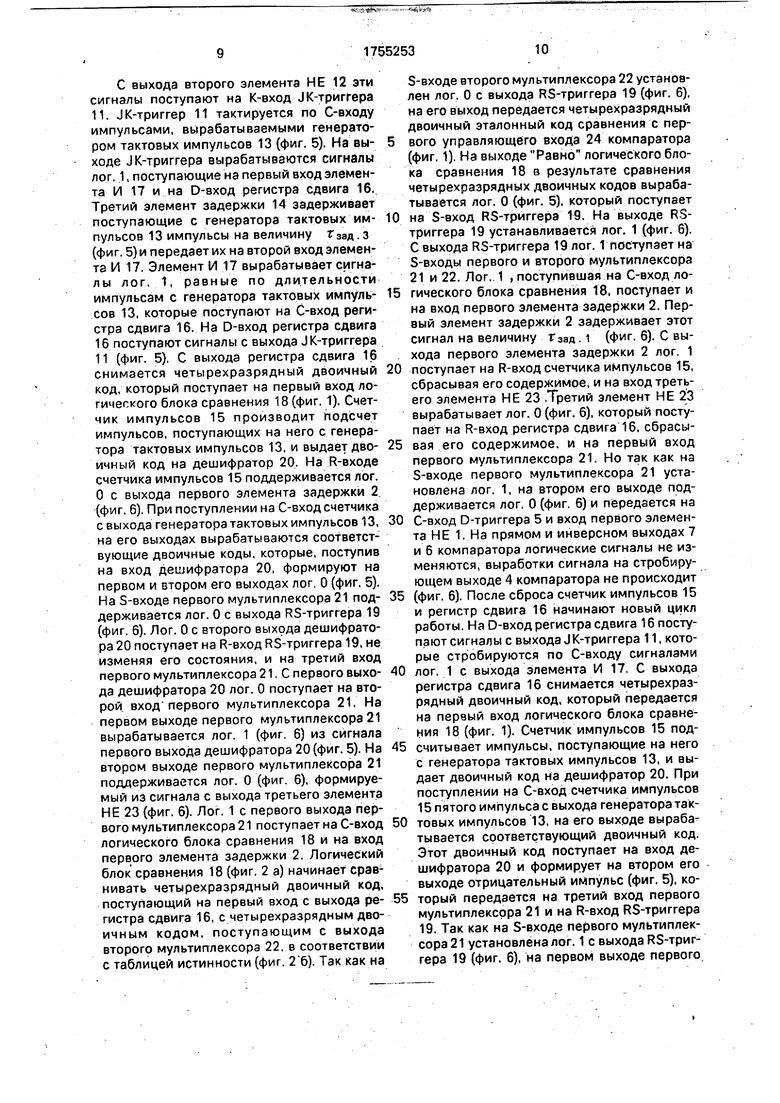

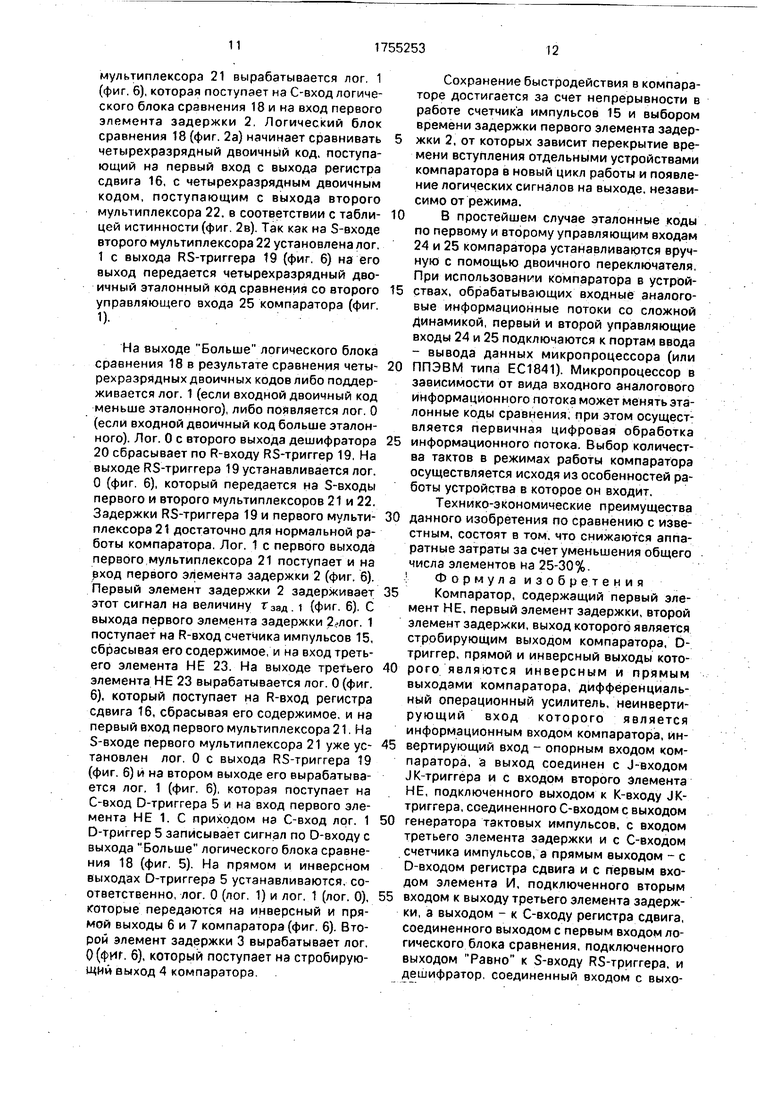

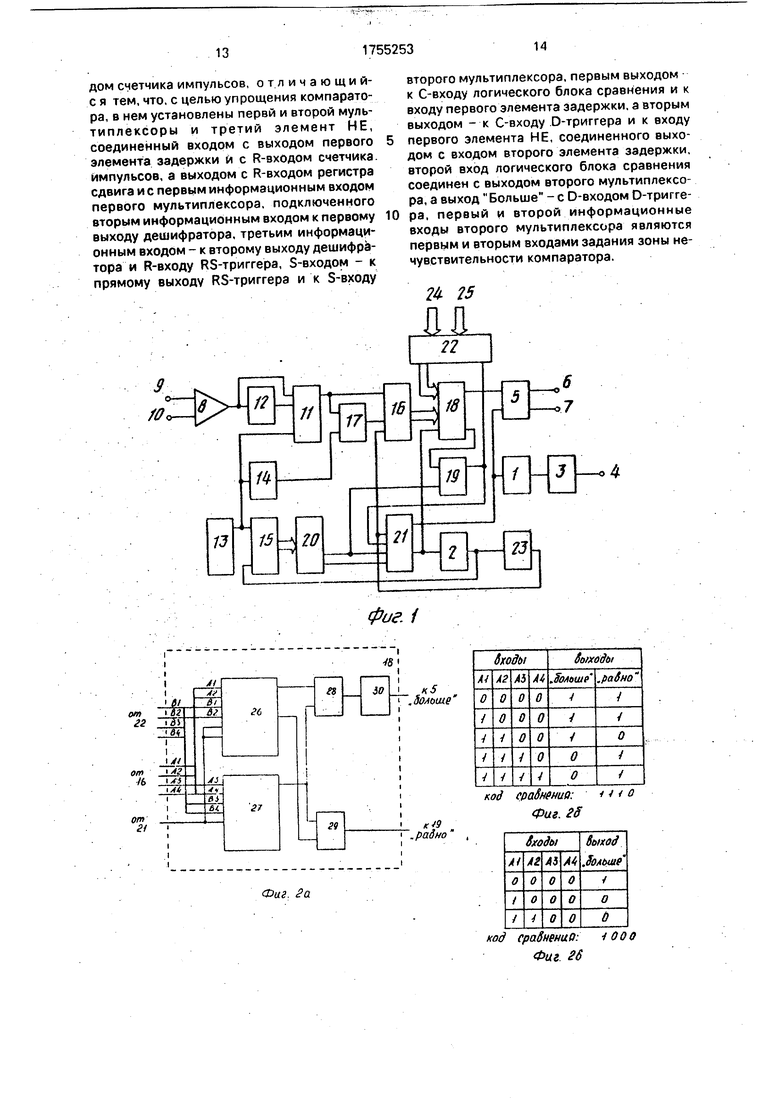

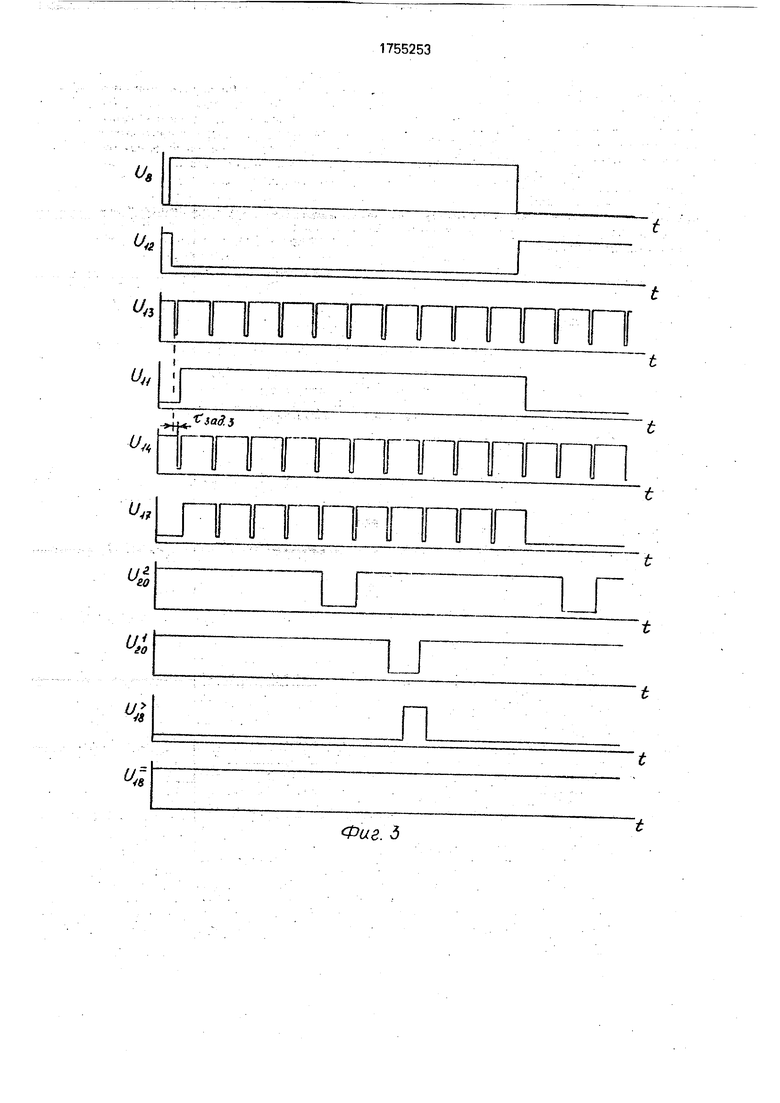

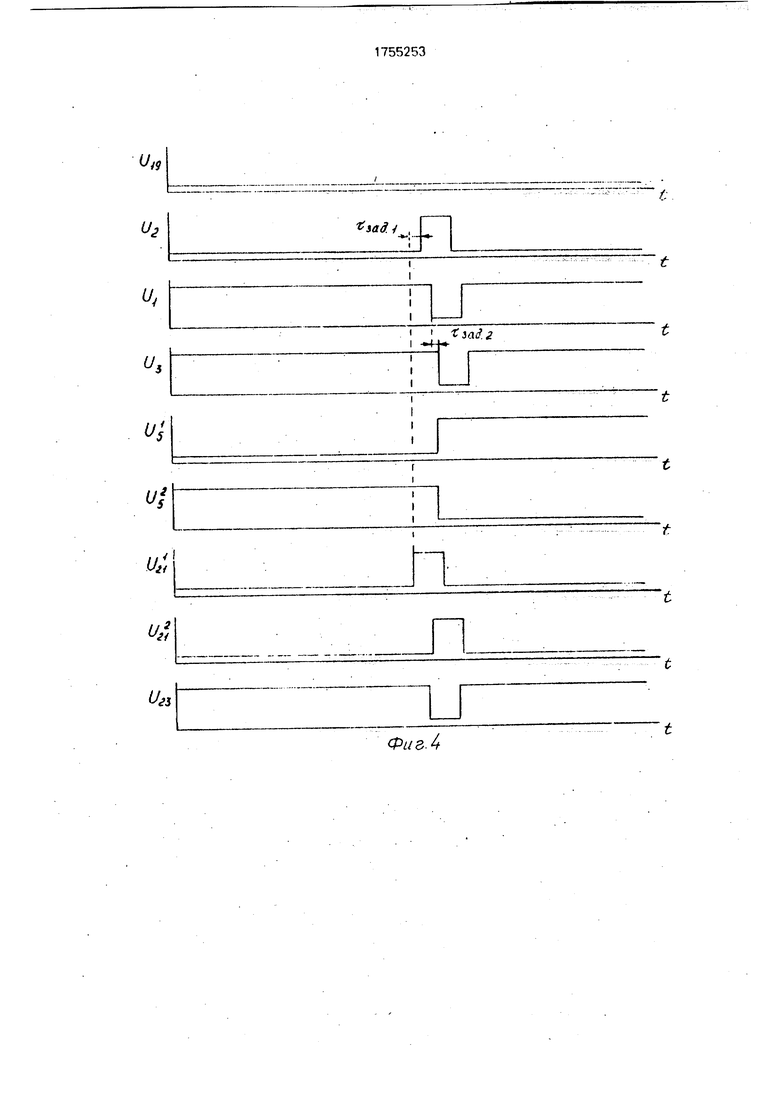

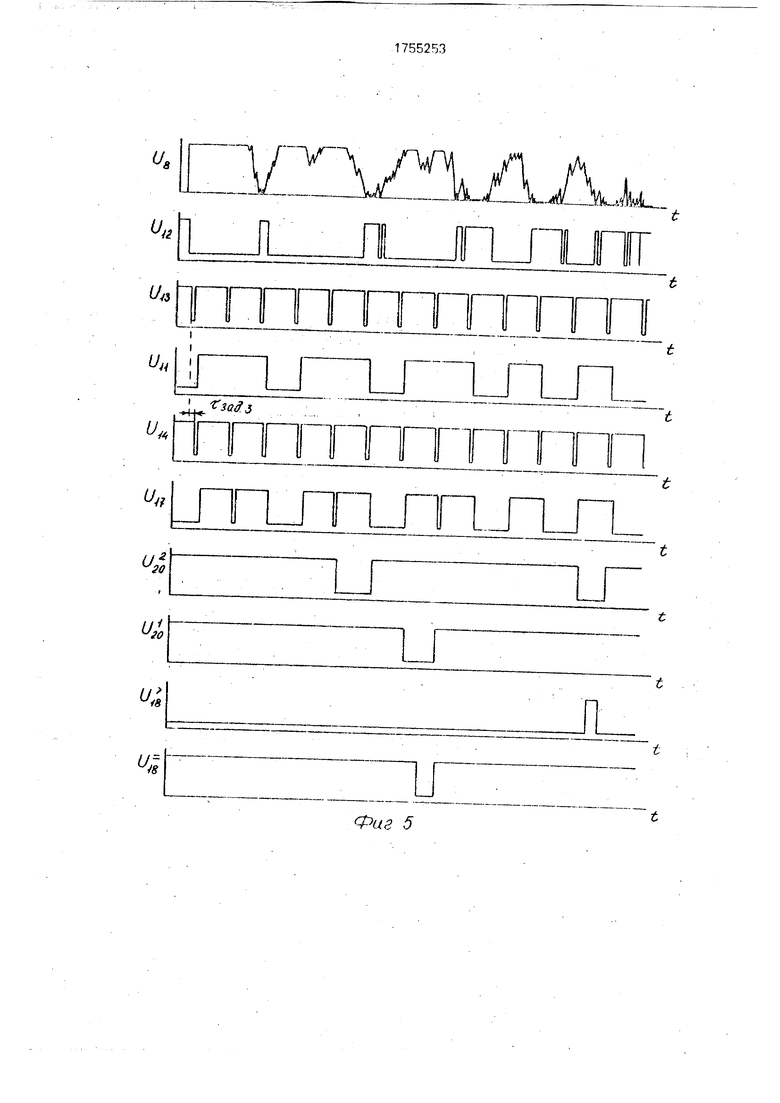

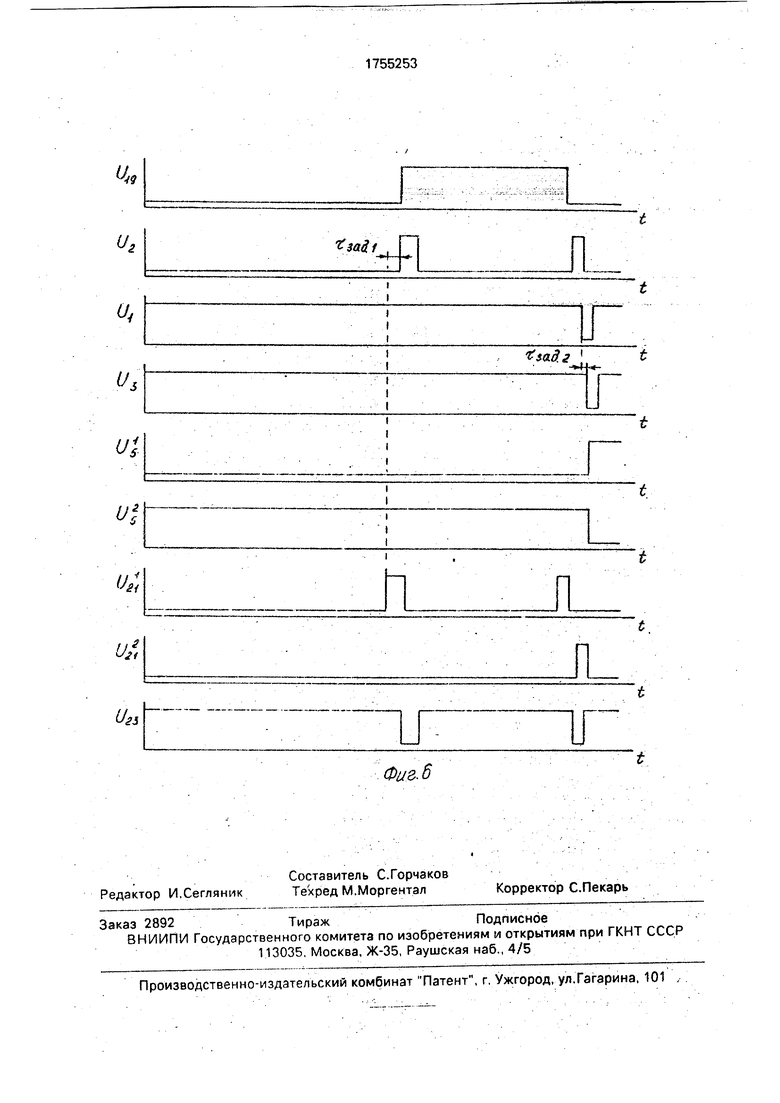

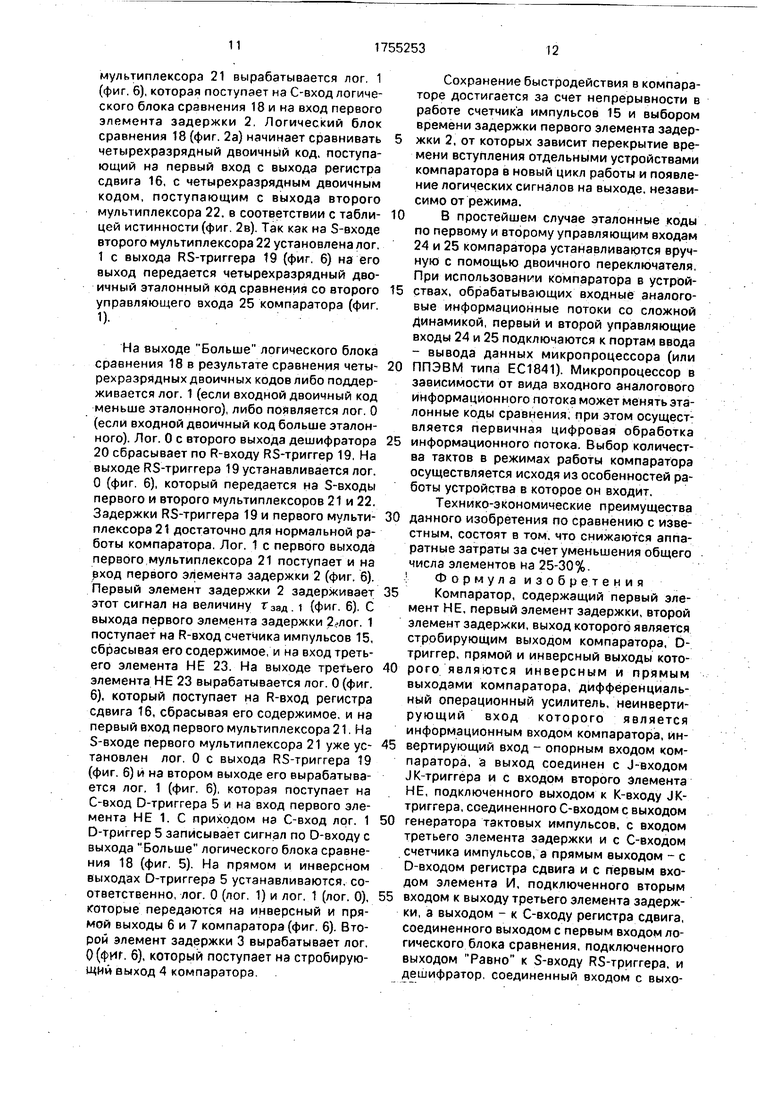

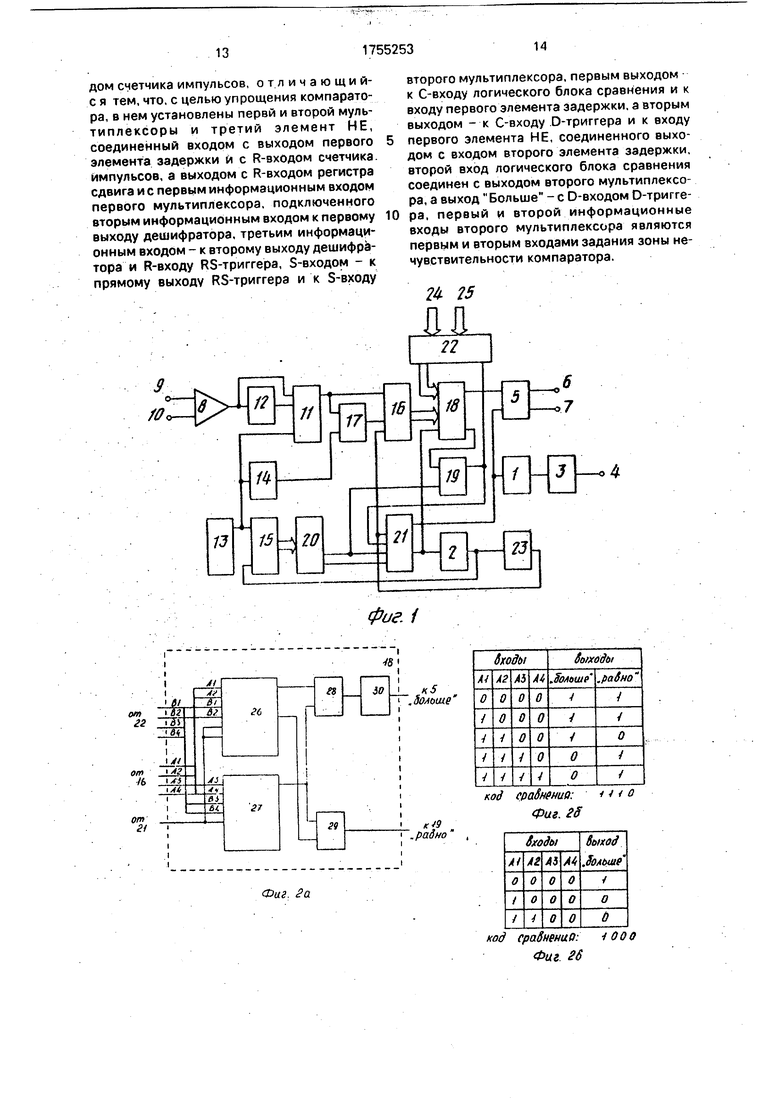

На фиг. 1 изображена блок-схема компаратора; на фиг. 2а - функциональная схема логического блока сравнения; на фиг. 26, в - таблицы истинности для нормального режима работы и для режима работы с расширением; на фиг. 3 и 4 - временные диаграммы для нормального режима работы; на фиг, 5 и б - временные диаграммы для режима работы с расширением.

Компаратор (фиг. 1) содержит первый элемент НЕ 1 (на микросхеме (ИМС) 531ЛН1), первый элемент задержки 2 (ИМС 531ЛИ1), второй элемент задержки 3 (ИМС 531ЛН1), выход которого является стробирующим входом 4 компаратора, D-триггер 5 (ЙМС531ТМ2), прямой и инверсный выходы которого являются инверсным и прямым выходами 6 и 7 компаратора, дифференциальный операционный усилитель 8 (ИМС 140УД9), неинвертирующий вход которого является информационным входом 9 компаратора, инвертирующий вход - опорным входом 10 компаратора, а выход - соединен с J-входом JK-триггера 11 (ИМС 531ТВ10) и со входом второго элемента НЕ 12 (ИМС 531Л Н1), подключенного выходом к К-входу JK-триггера 11, соединенного С-входом с выходом генератора тактовых импульсов 13 (на ИМС 531Л A3 и дискретных элементах), со входом третьего элемента задержки 14 (ИМС 531ЛН1) и с С-входом счетчика импульсов 15 (ИМС 531ИЕ5), а прямым выходом - с D-входом регистра сдвига 16 (ИМС 531ТМ8) и с первым входом элемента И 17 (ИМС 531ЛИ1), подключенного вторым входом к выходу третьего элемента задержки 14, а выходом - к С-входу регистра сдвига

16, соединенного выходом с первым входом логического блока сравнения 18 (на ИМС 531СП1, 531ЛЕ1 и 531ЛАЗ), подключенного выходом Равно к S-входу RS-триггера 19 (ИМС 531ТМ2), и дешифратор 20 (ИМС 531ИД7), соединенный входом с выходом счетчика импульсов 15, первый и второй мультиплексоры 21 (ИМС 531КП14) и 22 (ИМС 531КП13), третий элемент НЕ 23 (ИМС 531ЛЕ1). соединенный входом с выходом первого элемента задержки 2 и с R-входом счетчика импульсов 15, а выходом - с R-входом регистра сдвига 16 и с первым входом первого мультиплексора 21, подключенного вторым входом к первому выходу дешифратора 20, третьим входом - ко второму выходу дешифратора 20 и R-входу RS-триггера 19, S-входом - к прямому выходу RS-триггера 19 и к S-входу второго мультиплексора 22, первым выходом - к С-входу логического блока сравнения 18 и ко входу первого элемента задержки 2, а вторым выходом - к С-входу D-триггера 5 и к входу первого элемента НЕ 1, соединенного выходом со входом второго элемента задержки 3, -второй вход логического блока сравнения 18 соединен с выходом второго мультиплексора 22, а выход больше - с D-входом D-триггера 5, первый и второй входы второго мультиплексора 22 являются первым и вторым управляющими входами 24 и 25 компаратора, Логический блок сравнения 18 (фиг, 2 а) содержит первый элемент сравнения двоичных чисел 26 (ИМС 531 СП 1), входы первого и втоого разрядов которого подключены соответственно к первому входу логического блока сравнения 18, входы третьего и четвертого разрядов которого подключены соответственно к второму входу логического блока сравнения 18, второй элемент сравнения двоичных чисел 27 (ИМС 531СП1), входы первого и второго разрядов которого подключены соответственно к первому входу логического блока сравнения 18, входы третьего и четвертого разрядов которого подключены соответственно к второму входу логически, о блока сравнения 18, вход Меньше которого соединен с входами Меньше и Равно первого элемента сравнения двоичных чисел 26 и подключен к С-входу логического блока счравнения 18, элемент ИЛИ-НЕ 28 (ИМС 531ЛЕ1), соединенной вторым входом с первым входом элемента И-НЕ 29 (ИМС 531 ЛАЗ) и подключенный к выходу Меньше второго элемента сравнения двоичных чисел 27, подключенный первым входом к выходу Меньше первого элемента сравнения двоичных чисел 26, выход Равно которого подключен к второму входу элемента И-НЕ

29, выход которого является выходом Равно логического блока сравнения 18, элемент НЕ 30 (ИМС 531ЛЕ1), вход которого подключен к выходу элемента ИЛИ-НЕ 28,

выход которого является выходом Больше логического блока сравнения 18,

Компаратор работает следующим образом.

На входы 9 и 10 компаратора и соответственно неинвертирующий и инвертирующий входы дифференциального операционного усилителя 8 поступает непрерывно меняющееся входное аналоговое напряжение Uax и периодически меняющееся опорное аналоговое напряжение Uon. С выходом операционного усилителя (ОУ) 8 снимается периодически меняющееся аналоговое напряжение либо ОВ либо плюс 5В (фиг. 3). Если Usx Uon., на выходе ОУ 8

устанавливается уровень аналогового напряжения плюс 5В, близкий к уровню логической единицы (лог.1). Если Uex. Don., на выходе ОУ 8 устанавливается уровень аналогового напряжения ОВ, близкий к уровню

логического нуля (лог.О). При этом, величина /ивх. - Don./ не находится вблизи границы разрешающей способности ОУ 8. С выхода ОУ 8 периодически меняющееся аналоговое напряжение поступает на вход второго элемента НЕ 12 и на J-вход JК-триггера 11. Для получения необходимых уровней аналогового напряжения ОУ 8 включен по одной мз рекомендуемых схем. Второй элемент НЕ

12инвертирует поступающий аналоговый сигнал и вырабатывает логический сигнал

(фиг. 3), который поступает на К-вход JK- триггера 11. Поступающие на J-вход и К- вход J К-триггера 11 сигналы по С-входу тактируются импульсами, вырабатываемыми генератором тактовых импульсов 13(фиг. 3), На выходе JK-триггера 11 формируются тактированные выходные сигналы (фиг. 3), которые поступают на первый вход элемента И 17 и на D-вход регистра сдвига 16, На

второй вход элемента И 17 поступают сигналы лог. 1 с выхода третьего элемента задержки 14 (фиг. 3).

Третий элемент задержки 14 производит задержку поступающих на его вход импульсов с генератора тактовых импульсов

13на величину Тзад.з , которая учитывает задержку JK-триггера 11 и позволяет исключить появление на выходе элемента И 17 лишнего импульса. Элемент И 17 вырабатывает на выходе лог. 1 при наличии на первом его входе лог. 1. С выхода элемента И 17 сигналы лог. 1 (фиг. 3) поступают на С-вход регистра сдвига 16 и являются для него тактовыми. На D-вход регистра сдвига

16 поступают сигналы с выхода JK-триггера 11 (фиг. 3). Запись в регистр сдвига 16 производится только при наличии на выходе JK-триггера 11 лог. 1. На выходе регистра сдвига 16 формируется четырехразрядный двоичный код. который передается на первый вход логического блока сравнения 18 (фиг. 1, 2). Регистр сдвига 16 имеет семь разрядов, но на выход выводится содержимое, начиная с четвертого разряда. На С- вход счетчика импульсов 15 поступают импульсы с выхода генератора тактовых импульсов 13 (фиг. 3). Счетчик импульсов 13 производит их подсчет и выдает двоичный код на вход дешифратора 20. При этом на R-входе счетчика импульсов 15 поддерживается лог. О с выхода первого элемента задер- 2 (фиг. 4). При поступлении на С-вход счетчика импульсов 15 пятого и седьмого импульсов с выхода генератора тактовых импульсов 13, на его выходе вырабатывают ся соответствующие двоичные коды, которые, поступив на вход дешифратора 20, формируют на его первом и втором выходах сигналы лог. О (фиг. 3). В данном режиме работы компаратора RS-триггер 19 по S-вхо- ду логическим блоком сравнения 18 не устанавливается (фиг. 1). На выходе RS-триггера 19 поддерживается лог. О (фиг/4), который передается на S-входы первого и второго мультиплексоров 21 и 22. С второго выхода дешифратора 20 лог. О поступает на R-вход RS-триггера 19, не изменяя его состояния, и на третий вход первого мультиплексора 21. Лог. О с первого выхода дешифратора 20 передается на второй вход первого мультиплексора 21. Так как на S-входе первого мультиплексора 21 установлен лог. О, то на его первом выходе вырабатывается лог. 1 из сигнала с первого выхода дешифратора 20, а на его втором выходе поддерживается лог. О, формируемый из сигнала с выхода третьего элемента НЕ 23 (фиг. 4). Лог. 1 с первого выхода первого мультиплексора 21 поступает на С-вход логического блока сравнения 18 и на вход первого элемента задержки 2. С его приходом логический блок сравнения 18 (фиг. 2а) начинает сравнивать четырехразрядный двоичный код, поступающий на первый входе выхода регистра сдвига 16, с четырехразрядным двоичным кодом, поступающим с выхода второго мультиплексора 22. в соответствии с таблицей истинности (фиг. 26). Так как на S-входе второго мультиплексора 22 установлен лог 0. на его выход передается четырехразрядный двоичный эталонный код сравнения с первого управляющего входа 24 компаратора (фиг. 1). Первый элемент задержки 2 задерживает поступающий на его вход сигнал лог 1 на

величину г зад 1 (фиг. 4) Величина задержки обеспечивает нормальное функционирование компаратора и необходимую задержку для сигналов, поступающих на С- входы логического блока сравнения 18 и D- триггера 5, R-входы счетчика импульсов 15 и регистра сдвига 16. С выхода первого элемента задержки 2 лог. 1 поступает на R-вход счетчика импульсов 15. сбрасывая его содержимое, и на вход третьего элемента НЕ 23. Третий элемент НЕ 23 вырабатывает лог. О (фиг. 4), который поступает на R-вход регистра сдвига 16. сбрасывая его содержимое, и на первый вход первого мультиплексора 21. На втором выходе первого мультиплексора 21 вырабатывается лог. 1 (фиг. 4), которая поступает на С-вход D-триггера 5 и на вход первого элемента НЕ 1. На выходе Больше логического блока сравнения 18 в результате сравнения четырехразрядных двоичных кодов либо поддерживается лог. 1 (если входной двоичный код меньше эталонного), либо появляется лог, 0 (если входной двоичный код больше эталонного). Сигнал с выхода Больше логического блока сравнения 18 (фиг. 3) поступает на D-вход D-триггера 5. D-триггер 5 стробируется по С-входу сигналом лог. 1 со второго выхода первого мультиплексора 21 (фиг. 4). На прямом и инверсном выходах D-триггера 5 устанавливаются соответственно лог. О (лог. 1) и лог. 1 (лог. 0), которые передаются на инверсный и прямой выходы 6 и 7 компаратора (фиг. 4). На стробирующем выходе 4 компаратора вырабатывается лог. О (фиг. 4), который формируется из лог. 1 со второго выхода первого мультиплексора 21 (фиг. 4). Этот импульс инвертируется первым элементом НЕ 1 (фиг. 4) и задерживается вторым элементом задержки 3 на величину г3ад.2 .Величина г зад 2 учитывает задержку D-триггера 5.

На входы 9 и 10 компаратора и соответственно неинвертирующий и инвертирующий входы ОУ 8 поступают непрерывно меняющееся входное аналоговое напряжение DBX и периодически меняющееся опорное аналоговое напряжение Uon Величина /Uex -Uon / находится на границе разрешающей способности ОУ 8. На выходе ОУ 8 формируются сигналы, амплитуда которых находится в диапазоне от 0В до плюс 5В нестабильные по амплитуде и времени (фиг. 5). Эти нестабильные сигналы поступают на вход второго элемента НЕ 12 и J-вход JK- григгера 11. Второй элемент НЕ 12 инвертирует поступающие аналоговые сигналы и формирует из них сигналы лог. О и лог. 1 (фиг 5).

С выхода второго элемента НЕ 12 эти сигналы поступают на К-вход JK-триггера 11. JK-триггер 11 тактируется по С-входу импульсами, вырабатываемыми генератором тактовых импульсов 13 (фиг. 5). На выходе JK-триггера вырабатываются сигналы лог. 1, поступающие на первый вход элемента И 17 и на D-вход регистра сдвига 16. Третий элемент задержки 14 задерживает поступающие с генератора тактовых импульсов 13 импульсы на величину Г3ад.з (фиг. 5) и передает их на второй вход элемента И 17. Элемент И 17 вырабатывает сигналы лог, 1, равные по длительности импульсам с генератора тактовых импульсов 13, которые поступают на С-вход регистра сдвига 16. На D-вход регистра сдвига 16 поступают сигналы с выхода JK-триггера 11 (фиг. 5). С выхода регистра сдвига 16 снимается четырехразрядный двоичный код, который поступает на первый вход логического блока сравнения 18 (фиг. 1). Счетчик импульсов 15 производит подсчет импульсов, поступающих на него с генератора тактовых импульсов 13, и выдает двоичный код на дешифратор 20. На R-входе счетчика импульсов 15 поддерживается лог. О с выхода первого элемента задержки 2 (фиг. 6). При поступлении на С-вход счетчика с выхода генератора тактовых импульсов 13, на его выходах вырабатываются соответствующие двоичные коды, которые, поступив на вход дешифратора 20, формируют на первом и втором его выходах лог. О (фиг. 5). На S-входе первого мультиплексора 21 поддерживается лог. О с выхода RS-триггера 19 (фиг. 6). Лог. О с второго выхода дешифратора 20 поступает на R-вход RS-триггера 19, не изменяя его состояния, и на третий вход первого мультиплексора 21. С первого выхода дешифратора 20 лог. О поступает на второй вход первого мультиплексора 21. На первом выходе первого мультиплексора 21 вырабатывается лог. 1 (фиг. 6) из сигнала первого выхода дешифратора 20 (фиг. 5). На втором выходе первого мультиплексора 21 поддерживается лог. О (фиг. б), формируемый из сигнала с выхода третьего элемента НЕ 23 (фиг. 6). Лог. 1 с первого выхода первого мультиплексора 21 поступает на С-вход логического блока сравнения 18 и на вход первого элемента задержки 2. Логический блок сравнения 18 (фиг. 2 а) начинает сравнивать четырехразрядный двоичный код, поступающий на первый вход с выхода регистра сдвига 16, с четырехразрядным двоичным кодом, поступающим с выхода второго мультиплексора 22, в соответствии с таблицей истинности (фиг. 2 б). Так как на

S-входе второго мультиплексора 22 установлен лог. О с выхода RS-триггера 19 (фиг. 6), на его выход передается четырехразрядный двоичный эталонный код сравнения с первого управляющего входа 24 компаратора (фиг. 1). На выходе Равно логического блока сравнения 18 в результате сравнения четырехразрядных двоичных кодов вырабатывается лог. О (фиг. 5), который поступает

на S-вход RS-триггера 19. На выходе RS- триггера 19 устанавливается лог. 1 (фиг. 6). С выхода RS-триггера 19 лог. 1 поступает на S-входы первого и второго мультиплексора 21 и 22. Лог, 1 , поступившая на С-вход логического блока сравнения 18, поступает и на вход первого элемента задержки 2. Первый элемент задержки 2 задерживает этот сигнал на величину гэад.1 (фиг. 6). С выхода первого элемента задержки 2 лог. 1

поступает на R-вход счетчика импульсов 15, сбрасывая его содержимое, и на вход третьего элемента НЕ 23 Третий элемент НЕ 23 вырабатывает лог. О (фиг. 6), который поступает на R-вход регистра сдвига 16, сбрасывая его содержимое, и на первый вход первого мультиплексора 21, Но так как на S-входе первого мультиплексора 21 установлена лог. 1, на втором его выходе поддерживается лог. О (фиг. 6) и передается на

С-вход D-триггера 5 и вход первого элемента НЕ 1. На прямом и инверсном выходах 7 и 6 компаратора логические сигналы не изменяются, выработки сигнала на стробиру- ющем выходе 4 компаратора не происходит

(фиг. 6). После сброса счетчик импульсов 15 и регистр сдвига 16 начинают новый цикл работы. На D-вход регистра сдвига 16 поступают сигналы с выхода JK-триггера 11, которые стробируются по С-входу сигналами

лог. 1 с выхода элемента И 17, С выхода регистра сдвига 16 снимается четырехразрядный двоичный код, который передается на первый вход логического блока сравнения 18 (фиг. 1). Счетчик импульсов 15 подсчитывает импульсы, поступающие на него с генератора тактовых импульсов 13, и выдает двоичный код на дешифратор 20. При поступлении на С-вход счетчика импульсов 15 пятого импульса с выхода генератора тактовых импульсов 13, на его выходе вырабатывается соответствующий двоичный код. Этот двоичный код поступает на вход дешифратора 20 и формирует на втором его выходе отрицательный импульс (фиг. 5). который передается на третий вход первого мультиплексора 21 и на R-вход RS-триггера 19. Так как на S-входе первого мультиплексора 21 установлена лог. 1 с выхода RS-триггера 19 (фиг. 6), на первом выходе первого

мультиплексора 21 вырабатывается лог. 1 (фиг. 6), которая поступает на С-вход логического блока сравнения 18 и на вход первого элемента задержки 2. Логический блок сравнения 18 (фиг. 2а) начинает сравнивать четырехразрядный двоичный код, поступающий на первый вход с выхода регистра сдвига 16, с четырехразрядным двоичным кодом, поступающим с выхода второго мультиплексора 22. в соответствии с таблицей истинности (фиг. 2в). Так как на S-входе второго мультиплексора 22 установлена лог. 1 с выхода RS-триггера 19 (фиг. 6) на его выход передается четырехразрядный двоичный эталонный код сравнения со второго управляющего входа 25 компаратора (фиг. 1).

На выходе Больше логического блока сравнения 18 в результате сравнения четырехразрядных двоичных кодов либо поддерживается лог. 1 (если входной двоичный код меньше эталонного), либо появляется лог. О (если входной двоичный код больше эталонного). Лог. О с второго выхода дешифратора 20 сбрасывает по R-входу RS-триггер 19, На выходе RS-триггера 19 устанавливается лог. О (фиг. 6), который передается на S-входы первого и второго мультиплексоров 21 и 22. Задержки RS-триггера 19 и первого мультиплексора 21 достаточно для нормальной работы компаратора. Лог. 1 с первого выхода первого мультиплексора 21 поступает и на ,вход первого элемента задержки 2 (фиг. 6). Первый элемент задержки 2 задерживает этот сигнал на величину тэад. 1 (фиг. 6). С выхода первого элемента задержки . 1 поступает на R-вход счетчика импульсов 15, сбрасывая его содержимое, и на вход третьего элемента НЕ 23. На выходе третьего элемента НЕ 23 вырабатывается лог. О (фиг. 6), который поступает на R-вход регистра сдвига 16, сбрасывая его содержимое, и на первый вход первого мультиплексора 21. На S-входе первого мультиплексора 21 уже установлен лог. О с выхода RS-триггера 19 (фиг. 6) и на втором выходе его вырабатывается лог, 1 (фиг. 6), которая поступает на С-вход D-триггера 5 и на вход первого элемента НЕ 1. С приходом на С-вход лог. 1 D-триггер 5 записывает сигнал по 0-входу с выхода Больше логического блока сравнения 18 (фиг. 5). На прямом и инверсном выходах D-триггера 5 устанавливаются, соответственно, лог. О (лог. 1) и лог. 1 (лог. 0), которые передаются на инверсный и прямой выходы 6 и 7 компаратора (фиг. 6). Второй элемент задержки 3 вырабатывает лог, О (фиг. 6), который поступает на стробирую- ЩМй выход 4 компаратора

Сохранение быстродействия в компараторе достигается за счет непрерывности в работе счетчика импульсов 15 и выбором времени задержки первого элемента задержки 2, от которых зависит перекрытие времени вступления отдельными устройствами компаратора в новый цикл работы и появление логических сигналов на выходе, независимо от режима.

0 В простейшем случае эталонные коды по первому и второму управляющим входам 24 и 25 компаратора устанавливаются вручную с помощью двоичного переключателя, При использовании компаратора в устрой5 ствах, обрабатывающих входные аналоговые информационные потоки со сложной динамикой, первый и второй управляющие входы 24 и 25 подключаются к портам ввода - вывода данных микропроцессора (или

0 ППЭВМ типа ЕС1841). Микропроцессор в зависимости от вида входного аналогового информационного потока может менять эталонные коды сравнения, при этом осуществляется первичная цифровая обработка

5 информационного потока. Выбор количества тактов в режимах работы компаратора осуществляется исходя из особенностей работы устройства в которое он входит.

Технико-экономические преимущества

0 данного изобретения по сравнению с известным, состоят в том. что снижаются аппаратные затраты за счет уменьшения общего числа элементов на 25-30%.

Формул а изобретени я

5 Компаратор, содержащий первый элемент НЕ, первый элемент задержки, второй элемент задержки, выход которого является стробирующим выходом компаратора, D- триггер, прямой и инверсный выходы кото0 рого являются инверсным и прямым выходами компаратора, дифференциальный операционный усилитель, неинвертирующий вход которого является информационным входом компаратора, ин5 вертирующий вход - опорным входом компаратора, а выход соединен с J-входом JK-триггера и с входом второго элемента НЕ, подключенного выходом к К-входу JK- триггера, соединенного С-входом с выходом

0 генератора тактовых импульсов, с входом третьего элемента задержки и с С-входом счетчика импульсов, а прямым выходом - с D-входом регистра сдвига и с первым входом элемента И, подключенного вторым

5 входом к выходу третьего элемента задержки, а выходом - к С-входу регистра сдвига, соединенного выходом с первым входом логического блока сравнения, подключенного выходом Равно к S-входу RS-триггера. и дешифратор, соединенный входом с выходом счетчика импульсов, отличающий- с я тем, что, с целью упрощения компаратора, в нем установлены первй и второй муль- типлексоры и третий элемент НЕ, соединенный входом с выходом первого элемента задержки и с R-ВХОДОМ счетчика импульсов, а выходом с R-входом регистра сдвига и с первым информационным входом первого мультиплексора, подключенного вторым информационным входом к первому выходу дешифратора, третьим информационным входом - к второму выходу дешифратора и R-входу RS-триггера, S-входом - к прямому выходу RS-триггера и к S-входу

0

второго мультиплексора, первым выходом к С-входу логического блока сравнения и к входу первого элемента задержки, а вторым выходом - к С-входу D-триггера и к входу первого элемента НЕ, соединенного выходом с входом второго элемента задержки, второй вход логического блока сравнения соединен с выходом второго мультиплексора, а выход Больше - с D-входом D-триггера, первый и второй информационные входы второго мультиплексора являются первым и вторым входами задания зоны нечувствительности компаратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Компаратор | 1988 |

|

SU1631512A1 |

| Устройство для входного контроля изделий | 1990 |

|

SU1746388A2 |

| МНОГОКАНАЛЬНЫЙ ИСТОЧНИК ЭЛЕКТРОПИТАНИЯ С ЗАЩИТОЙ | 1990 |

|

RU2011258C1 |

| Устройство с динамическим выбором маршрутов передачи данных | 1987 |

|

SU1587529A1 |

| Устройство для входного контроля изделий | 1989 |

|

SU1619313A1 |

| Устройство для диагностики неисправностей технических объектов | 1988 |

|

SU1536357A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

Использование:- в системах автоматического управления и связи, преимущественно в аналого-цифровых преобразователях. Цель: упрощение компаратора при сохранении быстродействия, стабильности и точности. Сущность: компаратор содержит три элемента НЕ (1,12,23), три элемента задержки (2,3,14), стробирующий выход (4) компаратора, D-триггер (5), инверсный (6) и прямой (7) выходы компаратора, дифференциальный операционный усилитель (8),- информационный вход (9) компаратора, опорный вход (10) компаратора, 1К-триггер

9

i

/О

от 21

Фиг 2а

Фиг. 1

код срайненив: Фиг. 25

1410

код сравнений: Фиг 26

1 000

и.

г

1

6t

/з

ттттттттттттп

и.

ц

ТТТТТПГ1ТТТТТ

и

V/

ГПГП1ПГТТТ

д

/

п

Ф«2. 3

Ъ

и/

.

t зпЗ з

I

Фиг 4

/,

и.

и

affs

и.

S4

гттпппгпт

и.

у/

ч

Ј|

AL

лгипигтг

Фиг 5

| Устройство для сравнения напряжений | 1974 |

|

SU541140A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Патент США №3593162, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| Нелинейное корректирующее устройство | 1988 |

|

SU1576881A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-08-15—Публикация

1990-01-15—Подача