Фиг.1

Изобретение относится к электроизмерительной технике, а именно к электронным шахматным часам.

Целью изобретения является повышение надежности часов, а также сокращение объ- ема индицируемой информации по мере убывания времени и числа ходов.

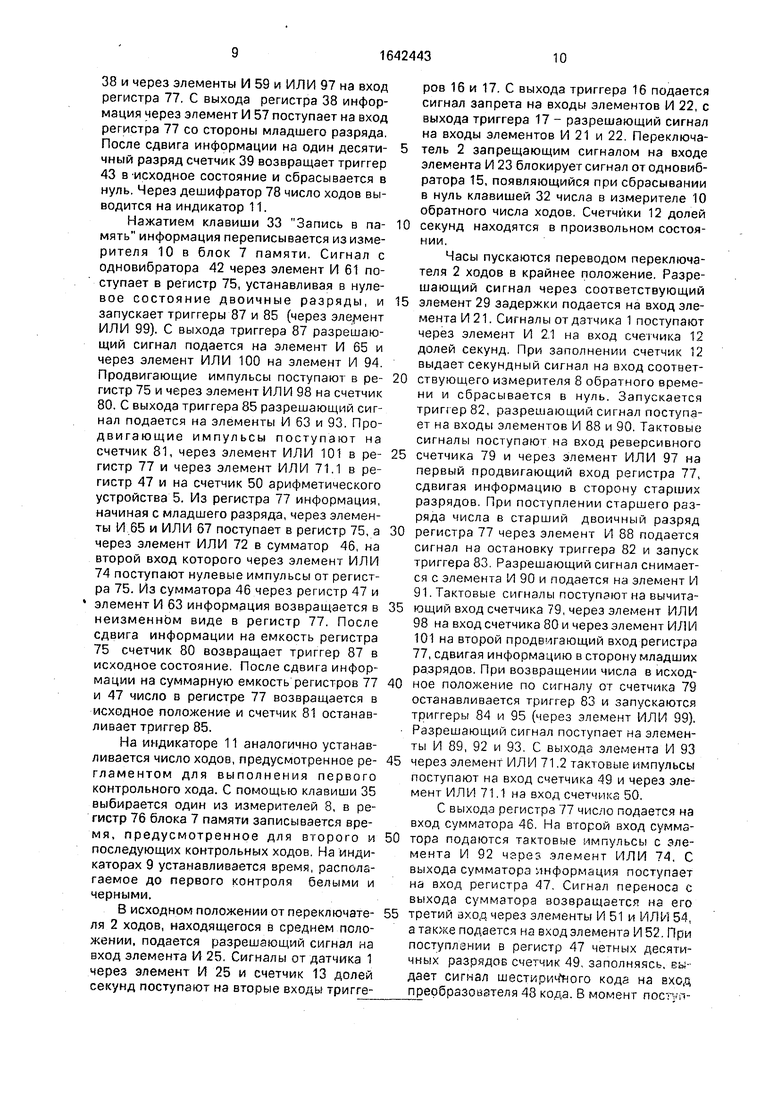

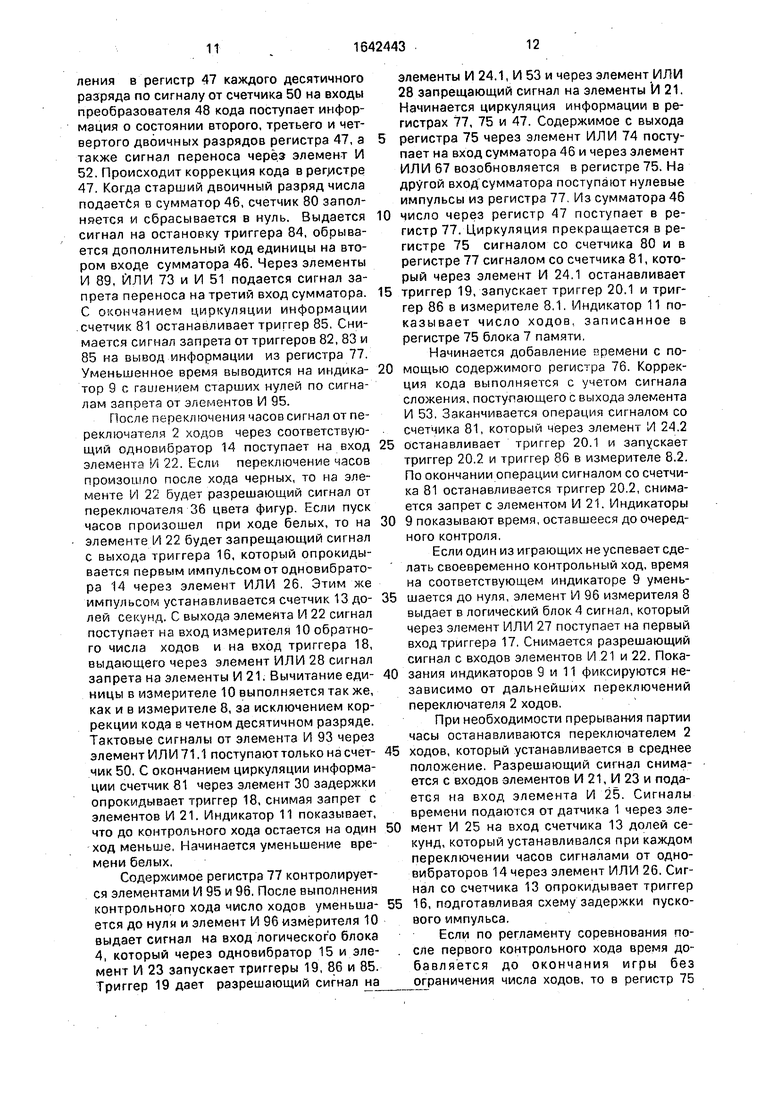

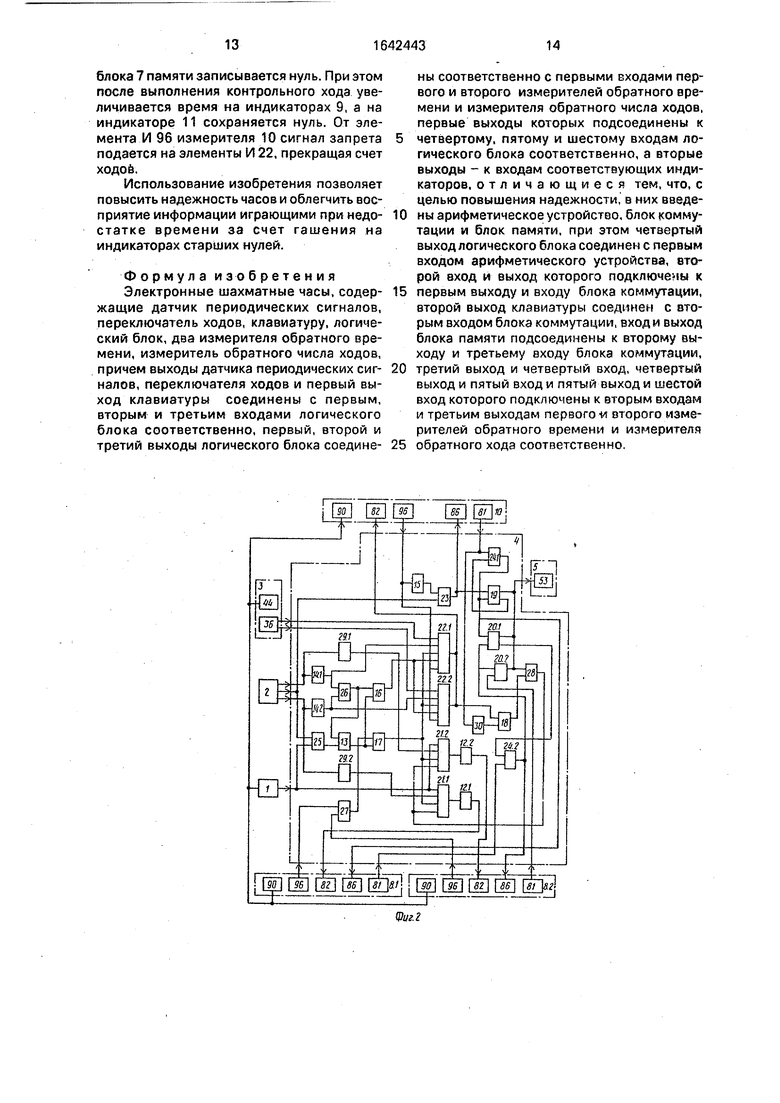

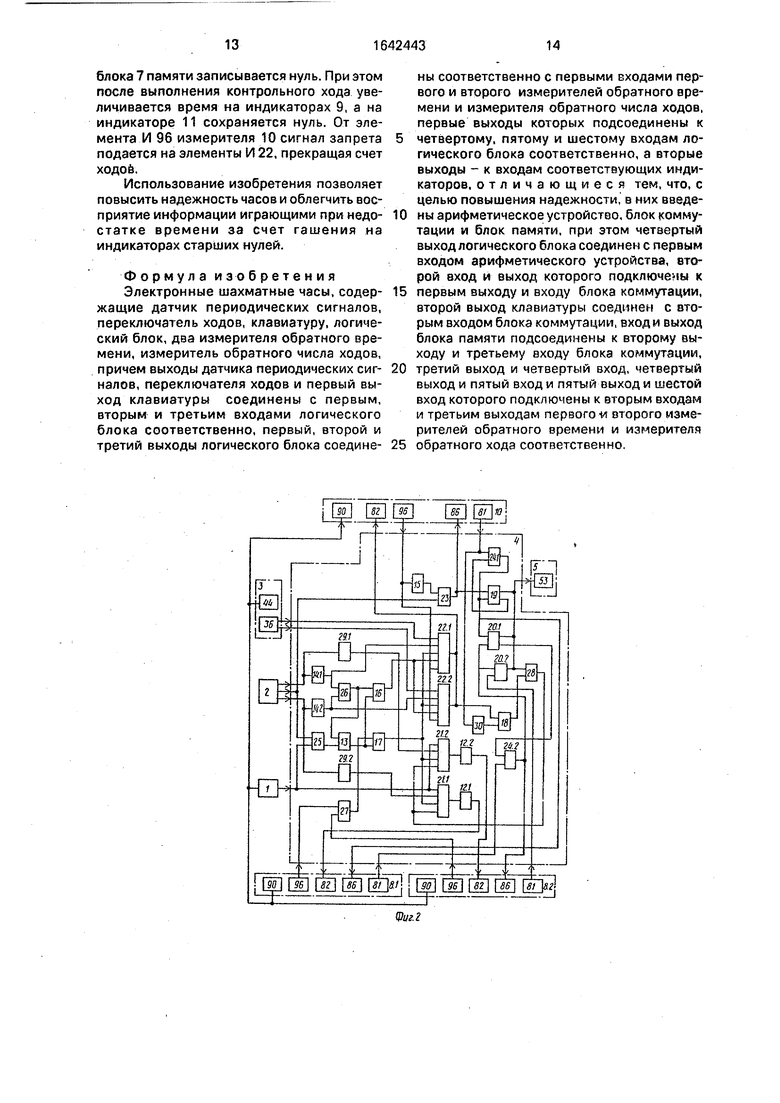

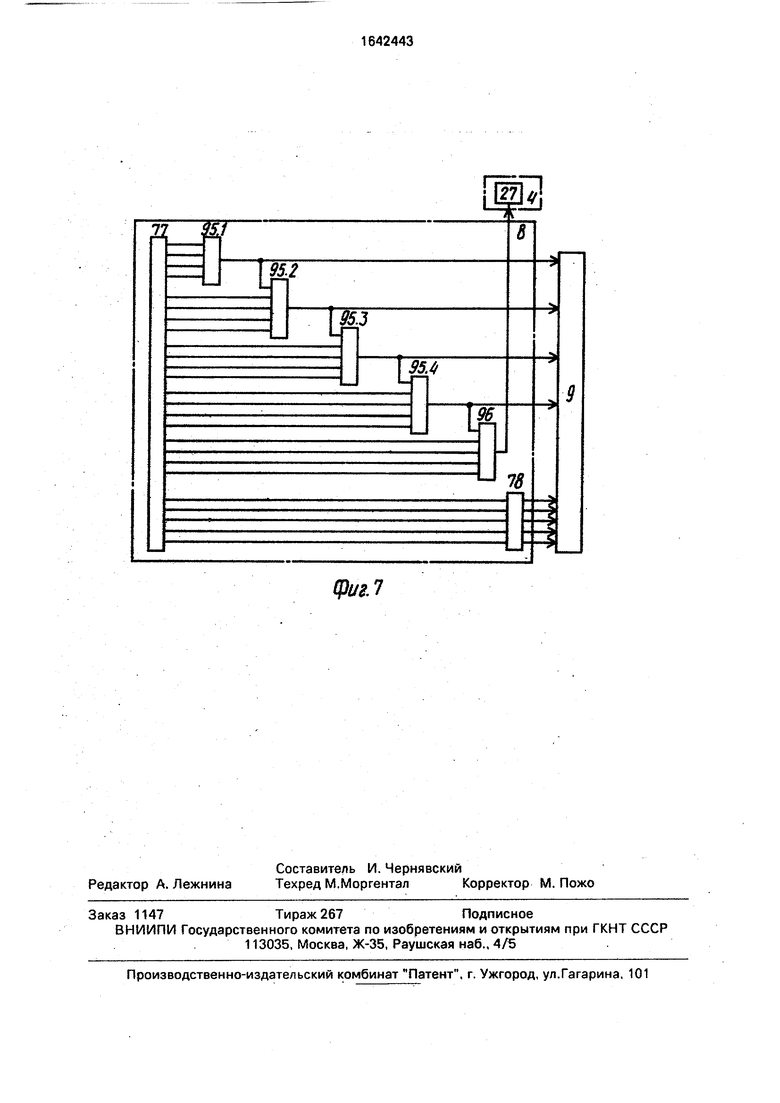

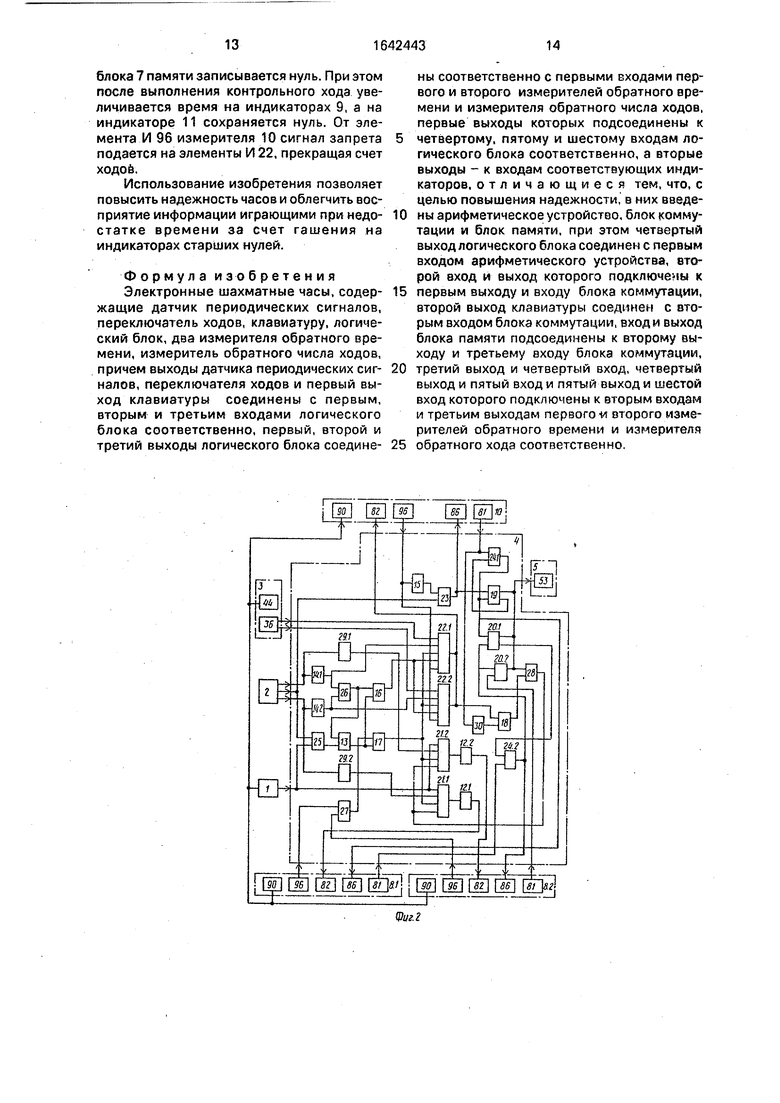

На фиг. 1 изображена структурная схема часов; на фиг.2 - функциональная схема логического блока; на фиг.З - функциональная схема клавиатуры; на фиг.4 - функциональная схема арифметического устройства; на фиг.5 - функциональные схемы блока коммутации и блока памяти; на фиг.б - функциональная схема измерителя обратного числа ходов; на фиг.7 - функциональная схема измерителя обратного времени.

Электронные шахматные часы (фиг.1) содержат датчик 1 периодических сигналов, переключатель ходов 2, клавиатуру 3, логи- ческий блок 4, арифметическое устройство 5, блок 6 коммутации, блок памяти, первый измеритель 8.1 обратного времени, второй измеритель 8.2 обратного времени, первый индикатор 9.1, второй индикатор 9.2, изме- ритель 10 обратного числа ходов и третий индикатор 11,

Датчик 1 периодических сигналов, переключатель 2 ходов и клавиатура 3 подключен выходами к первому, втооому и третьему входам логического блока 4, соединенного первым, вторым и третьим выходами с первыми входами измерителей 8 обратного времени и измерителя 10 обратного числа ходов, подсоединенных первы- ми выходами к четвертому, пятому и шестому входам логичесокго блока 4, вторыми выходами - к входам первого и второго индикаторов 9 и третьего индикатора 11, третьими выходами - к четвертому, пятому и шестому входам, а вторыми входами - к третьему, четвертому и пятому выходам блока 6 коммутации. Блок 7 памяти соединен выходом с третьим входом, а входом - с вторым выходом блока б коммутации Арифметическое устройство 5 подсоединено первым входом к четвертому выходу логического блока 4, вторым входом - к пятому выходу, а выходом - к первому входу блока 6 коммутации, к второму входу которого под- ключей второй выход клавиатуры 3.

Логический блок 4 (фиг.2) включает счетчики 12.1,12.2 и 13 долей секунд (долей секунд),одновибраторы 14.1,14.2 и .триггеры 16-19,20.1 и 20.2, логические элемен- ты И 21.1, 21.2, 22.1, 22.2, 23, 24.1, 24.2 и 25, логические элементы ИЛИ 26-28 и элементы 29.1, 29.2 и 30 задержки.

Клавиатура 3 (фиг.З) содержит цифровые клавиши 31.1 -31.10, клавишу Сброс

32, клавишу Запись в память 33, адресные клавиши с фиксацией 34, 35.1 и 35.2 переключатель 36 цвета фигур, шифратор 37, регистр 38, счетчик 39, одновибраторы 40.1-40.10, 41 и 42, триггер 43, логический элемент И 44 и логический элемент ИЛИ 45.

Арифметическое устройство 5 (фиг.4) состоит из сумматора 46, регистра 47, преобразователя. 48 кода, счетчиков 49 и 50, логических элементов И 51-53 и логического элемента ИЛИ 54.

Блок 6 коммутации содержит логические элементы И 55,56.1,56.2, 57,58.1,58.2, 59, 60.1, 60.2, 61, 62.1 62.2, 63, 64.1, 64.2, 65 66.1, 66.2 и логические элементы ИЛИ 67 - 70,71.1,71.2,72-74.

Блок 7 памяти состоит из регистра 75 емкостью в два десятичных разряда и регистра 76 емкостью в пять десятичных разрядов.

Измеритель 8 обратного времени и измеритель 10 обратного числа ходов образуют регистр 77, дешифратор 78, счетчики 79-81. триггеры 82 - 87, логические элементы И 88 - 96, и логические элементы ИЛИ 97-101.

Датчик 1 периодических сигналов, содержащий кварцевый генератор и делитель частоты, связан в части сигналов времени с входами элементов И 21 и 25 в логическом блоке 4, а в части тактовых сигналов - с входами элементов И 44 в клавиатуре 3 и И 90 - 94 в измерителях 8 и 10.

Переключатель 2 ходов крайними положениями связан с входами одновибраторов 14 и через элементы 29 задержки с входами элементов И 21, а средним положением - с входами элементов И 23 и 25 в логическом блоке 4.

Выходы элементов И 21 через счетчики 12 долей секунд связаны с входами триггеров 82 измерителей 8 обратного, времени. Выходы одновибратов 14 связаны с входами элементов И 22 и через элемент ИЛИ 26 с устанавливающим входом счетчика 13 долей секунд и входом триггера 16 задержки пускового импульса при счете ходов, выход которого связан с входами элементов И 22. Выходы элементов И 96 измерителей 8 через элемент ИЛИ 27 связаны с входом триггера 17 автоматической остановки часов, выход которого связан с входами элементов И 21 и 22. Выход элемента И 25 через счетчик 13 долей секунд связан с вторыми входами триггеров 16 и 17.

Переключатель 36 цвета фигур клавиатуры 3 связан с входами элементов И 22, объединенные выходы которых связаны с входом триггера 18 уменьшения числа ходов

и входом триггера 82 в измерителе 10. Выход триггера 18 через элемент ИЛИ 28 связан с входами элементов И 21. Выход элемента И 96 в измерителе 10 связан с входами элементов И 22 и через одновибра- тор 15 с входом элемента И 23, выход которого- связан с входом триггера 86 в измерителе 10 и входом триггера 19 добавления числа ходов, выход которого связан с входом элемента И 24.1. Выход счетчика 81 в измерителе 10 также связан с входом элемента И 24.1 и через элемент 30 задержки с вторым входом триггера 18. Выход элемента И 24.1 связан с вторым входом триггера 19, входом триггера 20.1 добавле- ния времени, выход которого связан с входом элемента И 24.2, и входом триггера 86 в измерителе 8.1. Выход счетчика 81 в измерителе 8.1 связан через элемент И 24.2 с вторым входом триггера 20.1, входом триггера 20.2 добавления времени и входом триггера 86 в измерителе 8.2, Выход счетчика 81 измерителя 8.2 связан с вторым входом триггера 20,2. Объединенные выходы триггеров 19 и 20 связаны с вхо- дом элемента И 53 арифметического устройства 5 и входом элемента ИЛИ 28.

Десять цифровых клавиш 31.1-31.10 клавиатуры связаны через одновибрато- ры 40.1 - 40.10 с входами шифратора 37 и через элемент ИЛИ 45 с входом триггера 43 сдвига информации в регистре 38 емкостью в один десятичный разряд. Выход триггера 43 связан с входом элемента И 44, выход которого связан с продвигаю- щим входом регистра 38. Выходы шифратора 37 связаны с входами двоичных разрядов регистра 38, информационный выход которого связан с входами элементов И 57 и 58 блока 6 коммутации. Выход элемента И 44 связан с входами элементов И 59 и 60 и через счетчик 39 с вторым входом триггера 43. Клавиши Сброс 32 через одновибратор 41 и Запись в память 33 через одновибратор 42 связаны с входами элементов И 55, 56 и 61, 62 соответственно. С входами блока 6 коммутации связаны также клавиша 34 выбора измерителя 10 и клавиши 35 выбора измерителей 8.

В арифметическом устройстве 5 имеют- ся одноразрядный сумматор 46, два входа которого связаны с выходами элементов ИЛИ 72 и 74 блока 6 коммутации, а первый выход - с информационным входом регистра 47 емкостью в один десятичный раз- ряд. Информационный выход регистра 47 связан с входами элементов И 63 и 64 блока 6 коммутации, а выходы второго, третьего и четвертого двоичных разрядов - с входами преобразователя 48 кода. Три

выхода преобразователя 48 кода связаны с входами второго, третьего и четвертого двоичных разрядов регистра 47, а четвертый выход через элемент ИЛИ 54 - с третьим входом сумматора 46, второй выход которого связан с входами элементов И 51 и 52. С другим входом элемента И 51 связан выход элемента ИЛИ 73 блока 6 коммутации, с выходом - вход элемента ИЛИ 54. Выход элемента ИЛИ 71.2 блока 6 коммутации связан через счетчик 49 с четвертым входом преобразователя 48 кода, выход элемента ИЛИ 71.1 - с продвигающим входом регистра 47, а также с входом счетчика 50, выход которого связан с шиной выдачи кода регистра 47 и входами элементов И 52 и 53. Выходы элементов И 52 и 53 связаны с пятым и шестым входами преобразователя 48 кода.

Блок 6 коммутации единообразно связан с измерителями 8 и 10 (на фиг.4 показаны связи с измерителем 10, связи с измерителями 8 оборваны). Выход адресной клавиши 34 связан с входами элементов И 55, 57, 59 и 61. Выходы адресных клавиш 35 связаны с входами элементов И 56, 58,

60и 62. Выходы элементов И 55, 57, 59 и

61связаны с входами измерителя 10, выходы элементов И 56, 58, 60 и 62 - с входами измерителей 8. Выход элемента И 55(56) связан с шиной Сброс регистра 77, выход элемента И 57 (58) - с первым информационным входом регистра 77, выход элемента И 59(60) - с элементом ИЛИ 97, выход элемента И 61(62) - с входами.триг- гера 87 и элемента ИЛИ 99. Выход элемента И 61 связан также с шиной Сброс регистра 75 блока 7 памяти, а выходы элементов И 62 через элемента ИЛИ 69 - с шиной Сброс регистра 76.

Выход элементов И 93 измерителей 8 через элемент ИЛИ 71.2 вместе с выходом элемента И 93 измерителя 10 связаны с входом элемента ИЛИ 71.1. Выход триггера 85 связан с входом элемента И 63(64), выход которого соединен с вторым информационным входом регистра 77. Информационный выход регистра 77 связан с входом элемента ИЛИ 72 и совместно с выходом триггера 87 с входами элемента И 65(66). Выход элемента И 65 через элемент ИЛИ 67 связан с информационным входом регистра 75, а выходы элементов И 66 через элемент ИЛИ 70 - с информационным входом регистра 76. Выходы элементов И 89 связаны с входами элемента ИЛИ 73, а выходы элементов И 92 совместно с информационными выходами регистров 75 и 76 - с входами элемента ИЛИ 74. Выход регистра 75 связан также с входом элемента ИЛИ 67, а выход регистра

76- с входом элемента ИЛИ 70. Выход элемента И 94 в измерителе 10 связан с продвигающим входом регистра 75, а выходы элементов И 94 в измерителях 8 через элемент ИЛИ 68 - с продвигающим входом регистра 76.

Измерители 8 и 10 обратного времени и обратндго числа ходов отличаются емкостью реверсивных регистров 77 и дешифра- торов 78, а также количеством элементом И 95. В измерителе 8 регистр и дешифратор рассчитаны на пять десятичных разрядов (часы, десятки и единицы минут, десятки и единицы секунд), содержится четыре эле- мента И 95. В измерителе 10 регистр и дешифратор рассчитаны на два десятичных разряда (десятки и единицы ходов) и имеется один элемент И 95.

Выходы двоичных разрядов регистра

77через дешифратор 78 связаны с индикатором 9 в измерителях 8 и индикатором 11 в измерителе 10. В измерителе 10 инверсные выходы двоичных разрядов старшего десятичного разряда регистра 77 связаны с входами элемента И 95, выход которого связан с входом индикатора 11 и входом элемента И 96. Инверсные выходы младшего десятичного разряда связаны с входами элемента И 96, выход которого связан с входами одновибратора 15 и элементов И 22 логического блока 4. В измерителе 8 инверсные выходы двоичных разрядов регистра 77 связаны с входами элементов И 95.1 - 95.4

и И 96 в порядке убывания десятичных раз- рядов. Выходы элементов И 95 связаны с входами индикатора 9 и последующих элементов И 95 и 96. Выход элемента И 96 связан с входом элемента ИЛИ 27 в логическом блоке 4.

Триггер 82 формирует сигнал сдвига информации в регистре 77 до старшего двоичного разряда. Выход триггера 82 связан с входами элементов И 88 и 90. Выход последнего связан с входом реверсивного счетчика 79 и через элемент ИЛИ 97 с первым продвигающим входом регистра 77. Выход старшего двоичного разряда регистра 77 через элемент И 88 связан с вто- - рым входом триггера 82 и первым входом триггера 83, формирующего сигнал сдвига информации в регистре 77 в исходное состояние. Выход триггера 83 связан с входом элемента И 91, выход которого связан с вторым входом счетчика 79, через элемент ИЛИ 98 - с входом счетчика 80 и через элемент ИЛИ 101 - с вторым продвигающим входом регистра 77. Выход счетчика 79 связан с вторым входом триггера

83, первым входом триггера 84 и через элемент ИЛИ 99 с первым входом триггера 85.

Триггер 84 формирует дополнительный код единицы. Выход триггера 84 связан с входами элементов И 89 и 92. Выход последнего через элемент ИЛИ 98 и счетчик 80 связан с входом элемента И 89 и вторыми входами триггеров 84, 86 и 87. Триггер 85 формирует сигнал циркуляции информации в регистре 77 через сумматор 46 и регистр 47. Выход триггера 85 связан с входом элемента И 93, выход которого через счетчик 81 связан с вторым входом триггера 85.

Триггер 86 в измерителе 10 формирует сигнал циркуляции информации в регистре 75 блока 7 памяти и в измерителе 8 сигнал циркуляции информации в регистре 76. Выход триггера 86 через элементы ИЛИ 100 и И 94 связан с входом ИЛИ 98. Триггер 87 формирует такой же сигнал при записи в память. Выход триггера 87 связан с входом элемента ИЛИ 100.

Электронные шахматные часы работают следующим образом.

До начала игры часы остановлены переключателем 2 ходов, установленным в среднее положение. Отдатчика 1 периодических сигналов импульсные сигналы, следующие с частотой долей секунд, поступают на вход блока 4, тактовые сигналы - в клавиатуру 3 и измерители 8 и 10 обратного времени и обратного числа ходов.

С помощью клавиатуры 3 в часы вводится исходная информация. Переключателем 36 часы ориентируются по цвету фигур на шахматной доске. При этом разрешающий сигнал поступает на элемент И 22, соответствующий положению переключателя 2 после хода черных. Клавишей 34 выбирается измеритель 10 обратного числа ходов.

С помощью клавиши Сброс 32 сигнал от одновибратора 41 через элемент И 55 поступает в регистр 77, устанавливая все двоичные разряды в нулевое состояние. С выхода регистра через дешифратор 78 нуль выводится на индикатор 11. При этом сигналом запрета с элемента И 95 гасится нуль в старшем разряде индикатора 11. С помощью цифровых клавиш 31 на индикаторе 11 устанавливается число ходов, предусмотренное регламентом для выполнения второго и последующих контрольных ходов. При этом с одновибратора 40 через шифратор 37 сигнал поступает на устанавливающие входы регистра 38 и через элемент ИЛИ 45 запускается триггер 43, с выхода которого подается разрешающий сигнал на элемент И 44. Тактовые сигналы поступают на продвигающий вход регистра

38 и через элементы И 59 и ИЛИ 97 на вход регистра 77. С выхода регистра 38 информация через элемент И 57 поступает на вход регистра 77 со стороны младшего разряда. После сдвига информации на один десяти- 5 чный разряд счетчик 39 возвращает триггер 43 в-исходное состояние и сбрасывается в нуль. Через дешифратор 78 число ходов выводится на индикатор 11.

Нажатием клавиши 33 Запись в па- 10 мять информация переписывается из измерителя 10 в блок 7 памяти. Сигнал с одновибратора 42 через элемент И 61 поступает в регистр 75, устанавливая в нулевое состояние двоичные разряды, и 15 запускает триггеры 87 и 85 (через элемент ИЛИ 99). С выхода триггера 87 разрешающий сигнал подается на элемент И 65 и через элемент ИЛИ 100 на элемент И 94. Продвигающие импульсы поступают в ре- 20 гистр 75 и через элемент ИЛИ 98 на счетчик 80. С выхода триггера 85 разрешающий сигнал подается на элементы И 63 и 93. Продвигающие импульсы поступают на счетчик 81, через элемент ИЛИ 101 в ре- 25 гистр 77 и через элемент ИЛИ 71.1 в регистр 47 и на счетчик 50 арифметического устройства 5. Из регистра 77 информация, начиная с младшего разряда, через элементы И 65 и ИЛИ 67 поступает в регистр 75, а 30 через элемент ИЛИ 72 в сумматор 46, на второй вход которого через элемент ИЛИ

74поступают нулевые импульсы от регистра 75. Из сумматора 46 через регистр 47 и

элемент И 63 информация возвращается в 35 неизменном виде в регистр 77. После сдвига информации на емкость регистра

75счетчик 80 возвращает триггер 87 в исходное состояние. После сдвига информации на суммарную емкость регистров 77 40 и 47 число в регистре 77 возвращается в исходное положение и счетчик 81 останавливает триггер 85.

На индикаторе 11 аналогично устанавливается число ходов, предусмотренное ре- 45 гламентом для выполнения первого контрольного хода. С помощью клавиши 35 выбирается один из измерителей 8, в регистр 76 блока 7 памяти записывается время, предусмотренное для второго и 50 последующих контрольных ходов. На индикаторах 9 устанавливается время, располагаемое до первого контроля белыми и черными.

В исходном положении от переключате- 55 ля 2 ходов, находящегося в среднем положении, подается разрешающий сигнал на вход элемента И 25. Сигналы от датчика 1 через элемент И 25 и счетчик 13 долей секунд поступают на вторые входы триггеров 16 и 17. С выхода триггера 16 подается сигнал запрета на входы элементов И 22, с выхода триггера 17 - разрешающий сигнал на входы элементов И 21 и 22. Переключатель 2 запрещающим сигналом на входе элемента И 23 блокирует сигнал от одновибратора 15, появляющийся при сбрасывании в нуль клавишей 32 числа в измерителе 10 обратного числа ходов. Счегчики 12 долей секунд находятся в произвольном состоянии.

Часы пускаются переводом переключателя 2 ходов в крайнее положение. Разрешающий сигнал через соответствующий элемент 29 задержки подается на вход элемента И 21. Сигналы отдатчика 1 поступают через элемент И 21 на вход 12 долей секунд. При заполнении счетчик 12 выдает секундный сигнал на вход соответствующего измерителя 8 обратного времени и сбрасывается в нуль. Запускается трипер 82, разрешающий сигнал поступает на входы элементов И 88 и 90. Тактовые сигналы поступают на вход реверсивного счетчика 79 и через элемент ИЛИ 97 на первый продвигающий вход регистра 77, сдвигая информацию в сторону старших разрядов. При поступлении старшего разряда числа в старший двоичный разряд регистра 77 через элемент И 88 подается сигнал на остановку триггера 82 и запуск триггера 83 Разрешающий сигнал снимается с элемента И 90 и подается на элемент И 91. Тактовые сигналы поступают на вычитающий вход счетчика 79, через элемент ИЛИ 98 на вход счетчика 80 и через элемент ИЛИ 10 на второй продвигающий вход регистра 77, сдвигая информацию в сторону младших разрядов, При возвращении числа в исходное положение по сигналу or счетчика 79 останавливается триггер 83 и запускаются триггеры 84 и 95 (через элемент ИЛИ 99). Разрешающий сигнал поступает на элементы И 89, 92 и 93. С выхода элемента И 93 через элемент ИЛИ 71.2 тактовые импульсы поступают на вход счетчика 49 и через элемент ИЛИ 71.1 на вход счетчика 50.

С выхода регистра 77 число подается на вход сумматора 46. На второй вход сумматора подаются тактовые импульсы с элемента И 92 чарез элемент ИЛИ 74, С выхода сумматора информация поступает на вход регистра 47. Сигнал переноса с выхода сумматора возвращается на его третий ауод через элементы И 51 и ИЛИ 54, а также подается на вход элемента И 52. При поступлении в регистр 47 четных десятичных разрядов счетчик 49, заполняясь, выдает сигнал шестиричного кода на вход преобразователя 48 кода. В момент ПОСТУЧления в регистр 47 каждого десятичного разряда по сигналу от счетчика 50 на входы преобразователя 48 кода поступает информация о состоянии второго, третьего и четвертого двоичных разрядов регистра 47, а также сигнал переноса через элемент И 52. Происходит коррекция кода в регистре 47. Когда старший двоичный разряд числа подается в сумматор 46, счетчик 80 заполняется и сбрасывается в нуль. Выдается сигнал на остановку триггера 84, обрывается дополнительный код единицы на втором входе сумматора 46. Через элементы И 89, ИЛИ 73 и И 51 подается сигнал запрета переноса на третий вход сумматора. С окончанием циркуляции информации счетчик 81 останавливает триггер 85. Снимается сигнал запрета от триггеров 82, 83 и 85 на вывод информации из регистра 77. Уменьшенное время выводится на индикатор 9 с гашением старших нулей по сигналам запрета от элементов И 95.

После переключения часов сигнал от переключателя 2 ходов через соответствующий одновибратор 14 поступает на вход элемента А 22. Если переключение часов произошло после хода черных, то на элементе И 22 будет разрешающий сигнал от переключателя 36 цвета фигур. Если пуск часов произошел при ходе белых, то на элементе И 22 будет запрещающий сигнал с выхода триггера 16, который опрокидывается первым импульсом от одновибрато- ра 14 через элемент ИЛИ 26. Этим же импульсом устанавливается счетчик 13 долей секунд. С выхода элемента И 22 сигнал поступает на вход измерителя 10 обратного числа ходов и на вход триггера 18, выдающего через элемент ИЛИ 28 сигнал запрета на элементы И 21. Вычитание единицы в измерителе 10 выполняется так же, как и в измерителе 8, за исключением коррекции кода в четном десятичном разряде. Тактовые сигналы от элемента И 93 через элемент ИЛ И 71.1 поступают только на счетчик 50. С окончанием циркуляции информации счетчик 81 через элемент 30 задержки опрокидывает триггер 18, снимая запрет с элементов И 21. Индикатор 11 показывает, что до контрольного хода остается на один ход меньше, Начинается уменьшение времени белых.

Содержимое регистра 77 контролируется элементами И 95 и 96, После выполнения контрольного хода число ходов уменьшается до нуля и элемент И 96 измерителя 10 выдает сигнал на вход логического блока 4, который через одновибратор 15 и элемент И 23 запускает триггеры 19, 86 и 85. Триггер 19 дает разрешающий сигнал на

элементы И 24.1, И 53 и через элемент ИЛИ 28 запрещающий сигнал на элементы И 21. Начинается циркуляция информации в регистрах 77, 75 и 47. Содержимое с выхода

регистра 75 через элемент ИЛИ 74 поступает на вход сумматора 46 и через элемент ИЛИ 67 возобновляется в регистре 75. На другой вход сумматора поступают нулевые импульсы из регистра 77 Из сумматора 46

0 число через регистр 47 поступает в регистр 77. Циркуляция прекращается в регистре 75 сигналом со счетчика 80 и в регистре 77 сигналом со счетчика 81, который через элемент И 24.1 останавливает

5 триггер 19, запускает триггер 20.1 и триггер 86 в измерителе 8,1. Индикатор 11 показывает число ходов, записанное в регистре 75 блока 7 памяти.

Начинается добавление рремени с по0 мощью содержимого регистра 76. Коррекция кода выполняется с учетом сигнала сложения, поступающего с выхода элемента И 53, Заканчивается операция сигналом со счетчика 81, который через элемент Л 24.2

5 останавливает триггер 20.1 и запускает триггер 20.2 и триггер 86 в измерителе 8.2. По окончании операции сигналом со счетчика 81 останавливается триггер 20.2, снимается запрет с элементом И 21. Индикаторы

0 9 показывают время, оставшееся до очередного контроля.

Если один из играющих не успевает сделать своевременно контрольный ход, время на соответствующем индикаторе 9 умень5 шается до нуля, элемент И 96 измерителя 8 выдает в логический блок 4 сигнал, который через элемент ИЛИ 27 поступает на первый вход триггера 17. Снимается разрешающий сигнал с входов элементов И 21 и 22. Пока0 зания индикаторов 9 и 11 фиксируются независимо от дальнейших переключений переключателя 2 ходов.

При необходимости прерывания партии часы останавливаются переключателем 2

5 ходов, который устанавливается в среднее положение. Разрешающий сигнал снимается с входов элементов И 21, И 23 и подается на вход элемента И 25. Сигналы времени подаются от датчика 1 через эле0 мент И 25 на вход счетчика 13 долей секунд, который устанавливался при каждом переключении часов сигналами от одно- вибраторов 14 через элемент ИЛИ 26. Сигнал со счетчика 13 опрокидывает триггер

5 16, подготавливая схему задержки пускового импульса.

Если по регламенту соревнования после первого контрольного хода время добавляется до окончания игры без ограничения числа ходов, то в регистр 75

блока 7 памяти записывается нуль. При этом после выполнения контрольного хода увеличивается время на индикаторах 9, а на индикаторе 11 сохраняется нуль. От элемента И 96 измерителя 10 сигнал запрета подается на элементы И 22, прекращая счет ходов.

Использование изобретения позволяет повысить надежность часов и облегчить восприятие информации играющими при недо- статке времени за счет гашения на индикаторах старших нулей.

Формула изобретения Электронные шахматные часы, содержащие датчик периодических сигналов, переключатель ходов, клавиатуру, логический блок, два измерителя обратного времени, измеритель обратного числа ходов, причем выходы датчика периодических сигналов, переключателя ходов и первый выход клавиатуры соединены с первым, вторым и третьим входами логического блока соответственно, первый, второй и третий выходы логического блока соединены соответственно с первыми входами первого и второго измерителей обратного времени и измерителя обратного числа ходов, первые выходы которых подсоединены к

четвертому, пятому и шестому входам логического блока соответственно, а вторые выходы - к входам соответствующих индикаторов, отличающиеся тем, что, с целью повышения надежности, в них введены арифметическое устройство, блок коммутации и блок памяти, при этом четвертый выход логического блока соединен с первым входом арифметического устройства, второй вход и выход которого подключены к

первым выходу и входу блока коммутации, второй выход клавиатуры соединен с вторым входом блока коммутации, вход и выход блока памяти подсоединены к второму выходу и третьему входу блока коммутации,

третий выход и четвертый вход, четвертый выход и пятый вход и пятый выход и шестой вход которого подключены к вторым входам и третьим выходам первого м второго измерителей обратного времени и измерителя

обратного хода соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электронные шахматные часы | 1985 |

|

SU1273874A1 |

| Устройство для ввода информации | 1982 |

|

SU1064275A1 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1136141A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Токарно-винторезный станок | 1987 |

|

SU1526954A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля знаний обучаемых | 1990 |

|

SU1758658A1 |

| Устройство для ввода информации | 1986 |

|

SU1334140A1 |

| Устройство для поиска кадров микрофильма | 1983 |

|

SU1111185A1 |

| Устройство для ввода-вывода информации | 1987 |

|

SU1451674A1 |

Изобретение относится к электроизмерительной технике, а именно к электронным шахматным часам, и позволяет повысить надежность устройства. Часы содержат датчик 1 периодических сигналов, переключатель 2 ходов, клавиатуру 3, логический блок 4, блок 7 памяти, измерители обратного времени 8.1 и 8.2 и обратного числа ходов to с индикаторами 9.1, 9.2 и 11. Новым в часах является арифметическое устройство 5 и блок 6 коммутации. Арифметические операции уменьшения и периодического добавления времени и- числа ходов выполняются централизованно. 7 ил.

Ш б UB ИВ Ю& Ш Ш1 Ш ИВ LfLF

O

-fc.

(43

-C

-fc.

CO

Е1Фгш

CH72fr9t

фигЛ

| Электронные шахматные часы | 1985 |

|

SU1273874A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-04-15—Публикация

1987-04-03—Подача