Изобретение относится к технике связи и может быть использовано для повышения эффективности передачи сигналов по каналам связи с ограниченным частотным и энергетическим потенциалом.

Цель изобретения - повышение информативности системы за счет уменьшения полосы частот при передаче сигналов по радиоканалу связи.

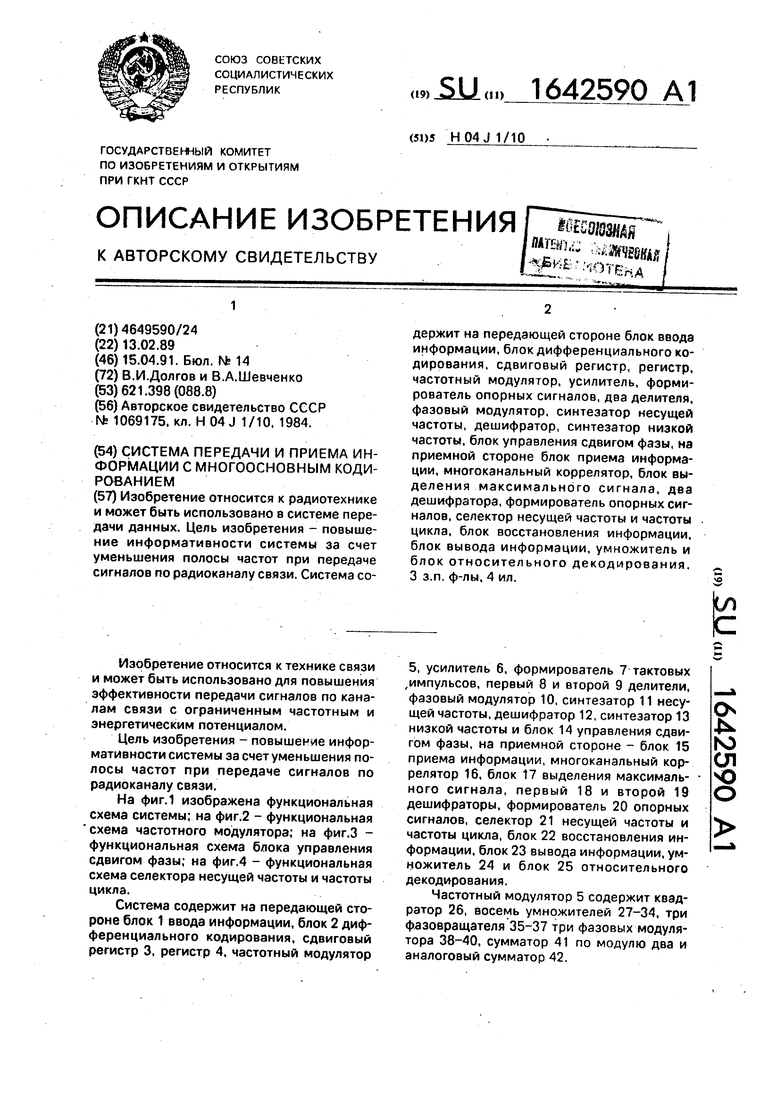

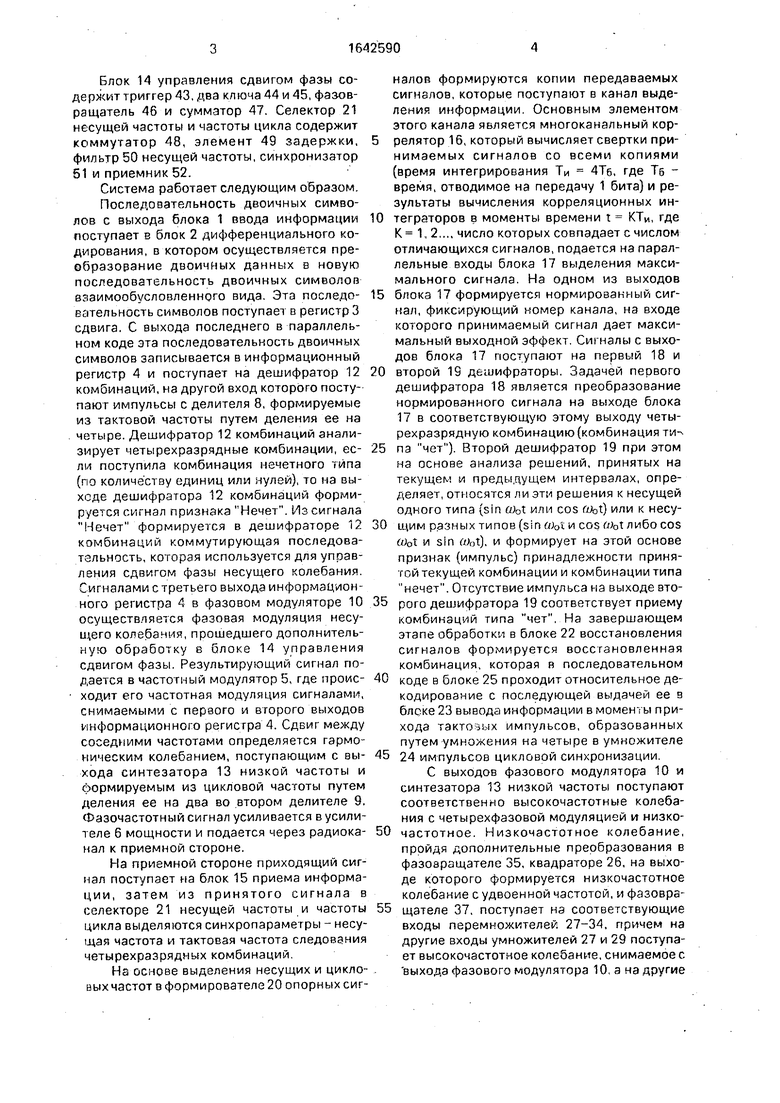

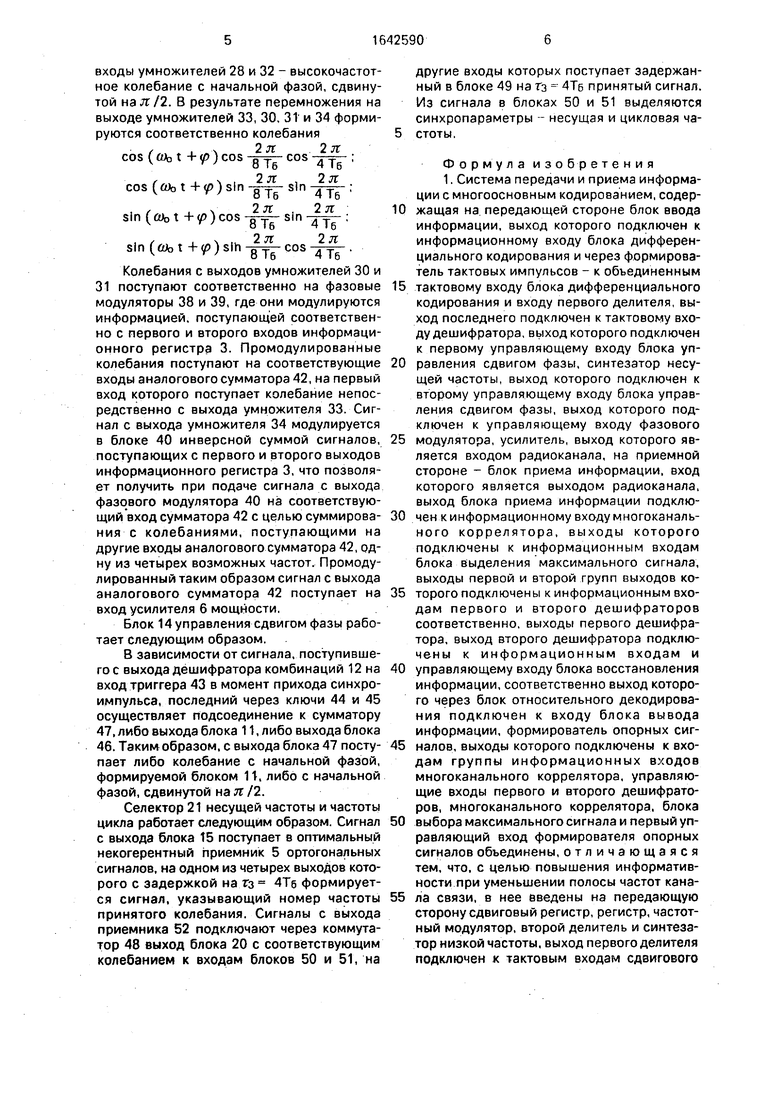

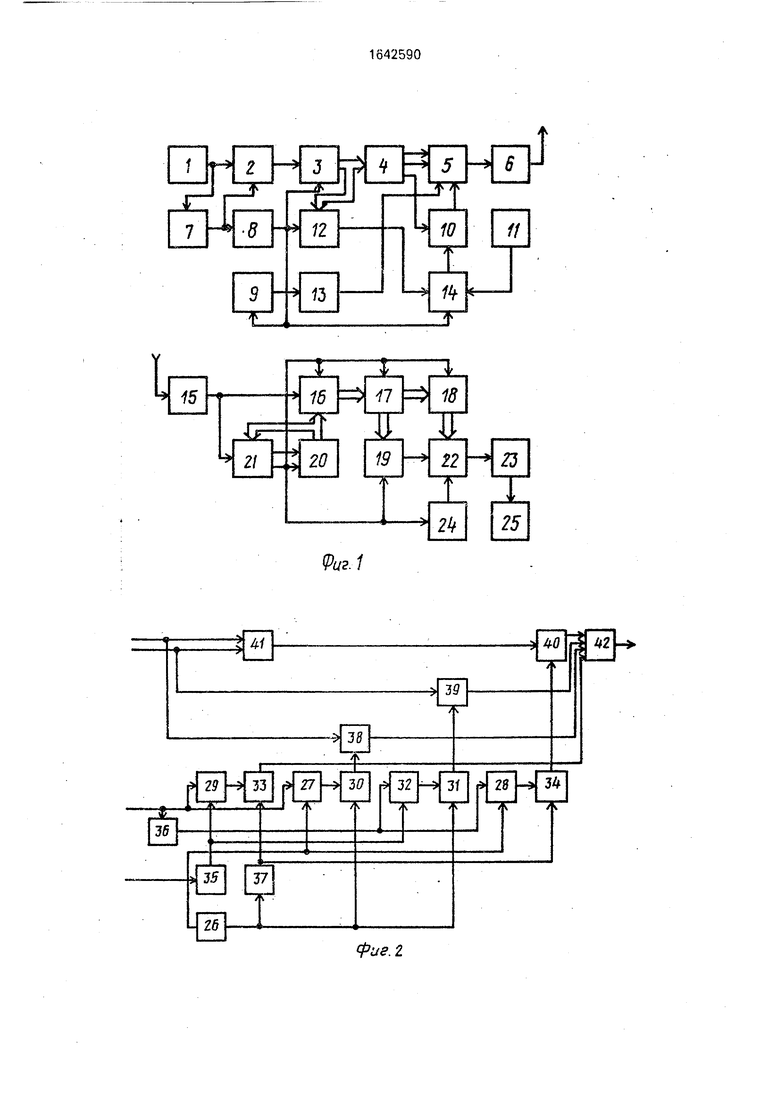

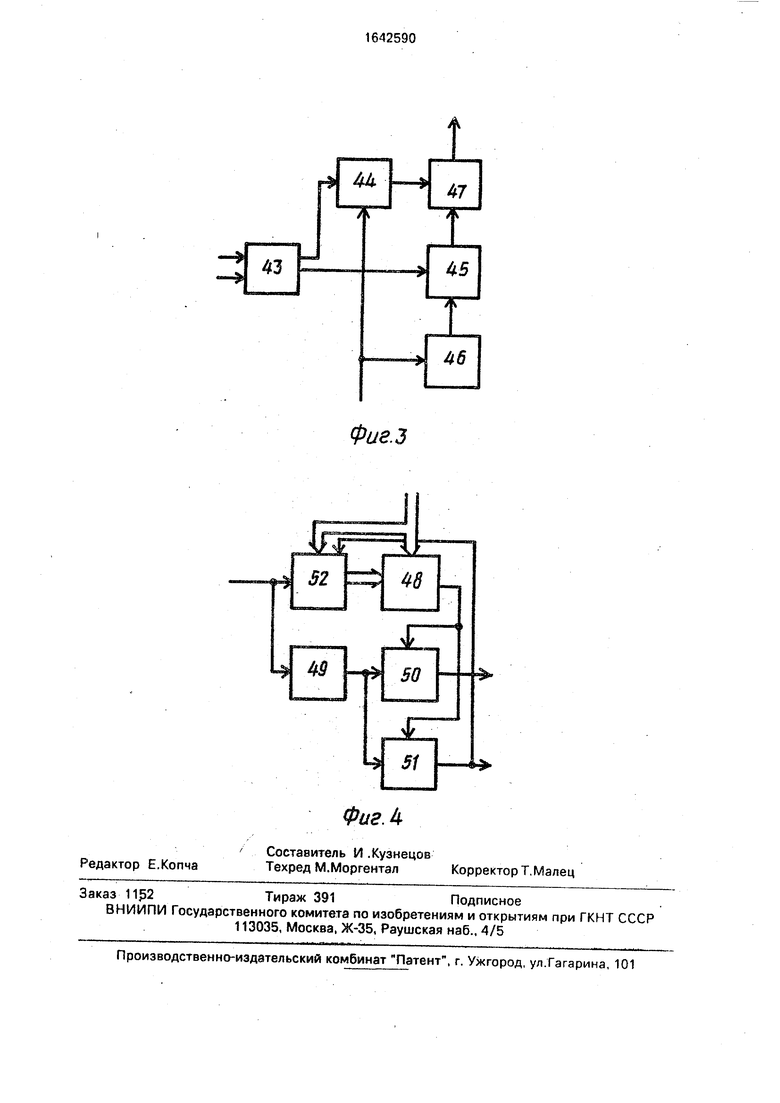

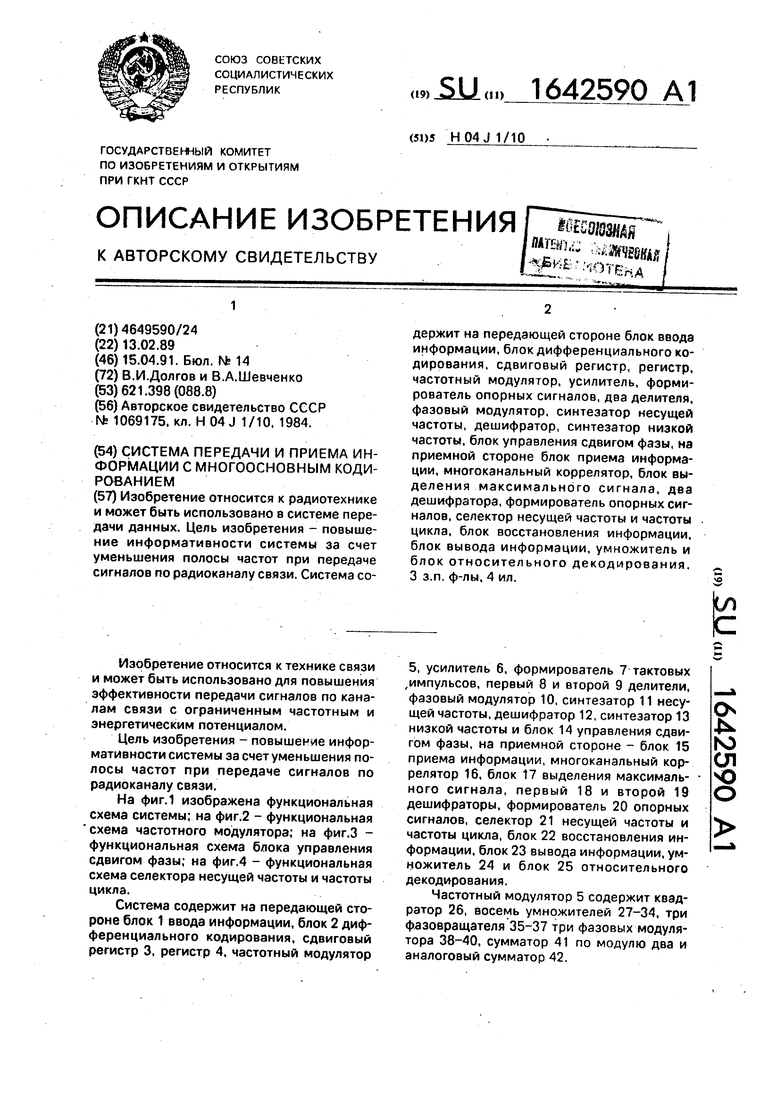

На фиг.1 изображена функциональная схема системы; на фиг.2 - функциональная схема частотного модулятора; на фиг.З - функциональная схема блока управления сдвигом фазы; на фиг.4 - функциональная схема селектора несущей частоты и частоты цикла.

Система содержит на передающей стороне блок 1 ввода информации, блок 2 дифференциального кодирования, сдвиговый регистр 3, регистр 4, частотный модулятор

5, усилитель 6, формирователь 7 тактовых ,импульсов, первый 8 и второй 9 делители, фазовый модулятор 10, синтезатор 11 несущей частоты, дешифратор 12, синтезатор 13 низкой частоты и блок 14 управления сдвигом фазы, на приемной стороне - блок 15 приема информации, многоканальный коррелятор 16, блок 17 выделения максимального сигнала, первый 18 и второй 19 дешифраторы, формирователь 20 опорных сигналов, селектор 21 несущей частоты и частоты цикла, блок 22 восстановления информации, блок 23 вывода информации, умножитель 24 и блок 25 относительного декодирования,

Частотный модулятор 5 содержит квадратор 26, восемь умножителей 27-34, три фазовращателя 35-37 три фазовых модулятора 38-40, сумматор 41 по модулю два и аналоговый сумматор 42.

Os

N

ГО СП

ю о

Блок 14 управления сдвигом фазы содержит триггер 43, два ключа 44 и 45, фазовращатель 46 и сумматор 47. Селектор 21 несущей частоты и частоты цикла содержит коммутатор 48, элемент 49 задержки, фильтр 50 несущей частоты, синхронизатор 51 и приемник 52.

Система работает следующим образом. Последовательность двоичных символов с выхода блока 1 ввода информации поступает в блок 2 дифференциального кодирования, в котором осуществляется преобразование двоичных данных в новую последовательность двоичных символов взаимообусловленного вида. Эта последовательность символов поступает в регистр 3 сдвига. С выхода последнего в параллельном коде эта последовательность двоичных символов записывается в информационный регистр 4 и поступает на дешифратор 12 комбинаций, на другой вход которого поступают импульсы с делителя 8, формируемые из тактовой частоты путем деления ее на четыре. Дешифратор 12 комбинаций анализирует четырехразрядные комбинации, если поступила комбинация нечетного типа (по количеству единиц или нулей), то на выходе дешифратора 12 комбинаций формируется сигнал признака Нечет. Из сигнала Нечет формируется в дешифраторе 12 комбинаций коммутирующая последовательность, которая используется для управления сдвигом фазы несущего колебания. Сигналами с третьего выхода информационного регистра 4 в фазовом модуляторе 10 осуществляется фазовая модуляция несущего колебания, прошедшего дополнительную обработку в блоке 14 управления сдвигом фазы. Результирующий сигнал подается в частотный модулятор 5, где происходит его частотная модуляция сигналами, снимаемыми с первого и второго выходов информационного регистра 4. Сдвиг между соседними частотами определяется гармоническим колебанием, поступающим с выхода синтезатора 13 низкой частоты и бормируемым из цикловой частоты путем деления ее на два во втором делителе 9. Фазочастотный сигнал усиливается в усили- теле 6 мощности и подается через радиоканал к приемной стороне.

На приемной стороне приходящий сигнал поступает на блок 15 приема информации, затем из принятого сигнала в селекторе 21 несущей частоты и частоты цикла выделяются синхропарамегры - несущая частота и тактовая частота следования четырехразрядных комбинаций

На основе выделения несущих и цикло- выхчастот в формирователе 20 опорных сигналов формируются копии передаваемых сигналов, которые поступают в канал выделения информации. Основным элементом этого канала является многоканальный коррелятор 16, который вычисляет свертки принимаемых сигналов со всеми копиями (время интегрирования Ти 4Тб, где Тб - время, отводимое на передачу 1 бита) и результаты вычисления корреляционных интеграторов в моменты времени t КТИ, где К 1, 2..., число которых совпадает с числом отличающихся сигналов, подается на параллельные входы блока 17 выделения максимального сигнала. На одном из выходов

блока 17 формируется нормированный сигнал, фиксирующий номер канала, на входе которого принимаемый сигнал дает максимальный выходной эффект. Сигналы с выходов блока 17 поступают на первый 18 и

второй 19 дешифраторы. Задачей пеового дешифратора 18 является преобразование нормированного сигнала на выходе блока 17 в соответствующую этому выходу четырехразрядную комбинацию (комбинация ти

па чет). Второй дешифратор 19 при этом на основе анализа решений, принятых на текущем и предыдущем интервалах, определяет, относятся ли эти решения к несущей одного типа (sin o;0t или cos Wot) или к несущим разных типов (sin и созоы либо cos W0t и sin Obt), и формирует на этой основе признак (импульс) принадлежности приня- гойтекущей комбинации и комбинации типа нечет. Отсутствие импульса на выходе второго дешифратора 19 соответствует приему комбинаций типа чет. На завершающем этапе обработки в блоке 22 восстановления сигналов формируется восстановленная комбинация, которая в последовательном

коде в блоке 25 проходит относительное декодирование с последующей выдачей ее в блоке 23 вывода информации в моменты прихода тактовых импульсов, образованных путем умножения на четыре в умножителе

24 импульсов цикловой синхронизации.

С выходов фазового модулятора 10 и синтезатора 13 низкой частоты поступают соответственно высокочастотные колебания с четырехфазовой модуляцией и низкочастотное. Низкочастотное колебание, пройдя дополнительные преобразования в фазовращателе 35, квадраторе 26, на выходе которого формируется низкочастотное колебание с удвоенной частотой, и фазовра5 щателе 37, поступает на соответствующие входы перемножителек 27-34, причем на другие входы умножителей 27 и 29 поступает высокочастотное колебание, снимаемое с выхода фазового модулятора 10, а на другие

входы умножителей 28 и 32 - высокочастотное колебание с начальной фазой, сдвинутой на л:/2. В результате перемножения на выходе умножителей 33, 30, 31 и 34 формируются соответственно колебания

cos ( (DO t + р ) cos о ... cos , -,. ;

В I б4 I б

COS (ftb t ) Sin

sin (ctfet +#)cos

In 8Тб 2я

sin

sin

2л: 4T6 2л

8T6 J1 4T6 sin (ttfe t + 9 ) sin -gy- cos .- .

Колебания с выходов умножителей 30 и 31 поступают соответственно на фазовые модуляторы 38 и 39, где они модулируются информацией, поступающей соответственно с первого и второго входов информационного регистра 3. Промодулированные колебания поступают на соответствующие входы аналогового сумматора 42, на первый вход которого поступает колебание непосредственно с выхода умножителя 33. Сигнал с выхода умножителя 34 модулируется в блоке 40 инверсной суммой сигналов, поступающих с первого и второго выходов информационного регистра 3, что позволяет получить при подаче сигнала с выхода фазового модулятора 40 на соответствующий вход сумматора 42 с целью суммирования с колебаниями, поступающими на другие входы аналогового сумматора 42, одну из четырех возможных частот. Промоду- лированный таким образом сигнал с выхода аналогового сумматора 42 поступает на вход усилителя 6 мощности.

Блок 14 управления сдвигом фазы работает следующим образом.

В зависимости от сигнала, поступившего с выхода дешифратора комбинаций 12 на вход триггера 43 в момент прихода синхроимпульса, последний через ключи 44 и 45 осуществляет подсоединение к сумматору 47, либо выхода блока 11, либо выхода блока 46. Таким образом, с выхода блока 47 поступает либо колебание с начальной фазой, формируемой блоком И, либо с начальной фазой, сдвинутой на п II.

Селектор 21 несущей частоты и частоты цикла работает следующим образом. Сигнал с выхода блока 15 поступает в оптимальный некогерентный приемник 5 ортогональных сигналов, на одном из четырех выходов которого с задержкой на гз 4Тб формируется сигнал, указывающий номер частоты принятого колебания. Сигналы с выхода приемника 52 подключают через коммутатор 48 выход блока 20 с соответствующим колебанием к входам блоков 50 и 51, на

другие входы которых поступает задержанный в блоке 49 на Гз 4Тб принятый сигнал. Из сигнала в блоках 50 и 51 выделяются синхропараметры - несущая и цикловая ча- 5 стоты.

Формула изобретения 1. Система передачи и приема информации с многоосновным кодированием, содер0 жащая на передающей стороне блок ввода информации, выход которого подключен к информационному входу блока дифференциального кодирования и через формирователь тактовых импульсов - к объединенным

5 тактовому входу блока дифференциального кодирования и входу первого делителя, выход последнего подключен к тактовому входу дешифратора, выход которого подключен к первому управляющему входу блока ул0 равления сдвигом фазы, синтезатор несущей частоты, выход которого подключен к второму управляющему входу блока управления сдвигом фазы, выход которого подключен к управляющему входу фазового

5 модулятора, усилитель, выход которого является входом радиоканала, на приемной стороне - блок приема информации, вход которого является выходом радиоканала, выход блока приема информации подклю0 чен к информационному входу многоканального коррелятора, выходы которого подключены к информационным входам блока выделения максимального сигнала, выходы первой и второй групп выходов ко5 торого подключены к информационным входам первого и второго дешифраторов соответственно, выходы первого дешифратора, выход второго дешифратора подключены к информационным входам и

0 управляющему входу блока восстановления информации, соответственно выход которого через блок относительного декодирования подключен к входу блока вывода информации, формирователь опорных сиг5 налов, выходы которого подключены к входам группы информационных входов многоканального коррелятора, управляющие входы первого и второго дешифраторов, многоканального коррелятора, блока

0 выбора максимального сигнала и первый управляющий вход формирователя опорных сигналов объединены, отличающаяся тем, что, с целью повышения информативности при уменьшении полосы частот кана5 ла связи, в нее введены на передающую сторону сдвиговый регистр, регистр, частотный модулятор, второй делитель и синтезатор низкой частоты, выход первого делителя подключен к тактовым входам сдвигового

регистра, второго делителя и блока управления сдвигом фазы, выход блока дифферен- циапьного кодирования подключен к информационному входу сдвигового регистра, выходы которого подключены к информационным входам дешифратора и регистра, первый, второй и третий выходы которого подключены к первому и второму информационным входам частотного модулятора и информационному входу фазового модулятора соответственно, выход частотного модулятора подключен к входу усилителя, выход второго делителя через синтезатор низкой частоты и выход фазового модулятора подключены к первому и второму управляющим входам частотного модулятора соответственно, на приемной стороне - селектор несущей частоты и частоты цикла, умножитель, выход блока приема информации подключен к информационному входу селектора несущей частоты и частоты цикла, первый выход которою подключен к первому управляющему входу формирователя опорных сигна- лов и к входу , умножителя, выход последнего подключен к тактовому входу блока восстановления информации, второй выход селектора несущей частоты л частоты цикла подключен к второму управляющему входу формирователя опорных сигналов, выходы которого подключены к входам группы информационных входов селектора несущей частоты и частоты цикла.

2. Система по п.1,отличающаяся тем, что частотный модулятор содержит кзадратор, восемь умножителей, три фазовращателя, три фазовых модулятора, сумматор по модулю два и аналоговый сумматор, первый вход сумматора по модулю два и информационный вход первого фазового модулятора объединены и являются первым информационным входом частотного модулятора, второй вход сумматора по модулю два и информационный вход второго фазового модулятора объединены и являются вторым информационным входом частотного модулятора, выход сумматора по модулю два подключен к информационному входу третьего модулятора, входы первого фазовращателя, квадратора и первые входы пер- ЕЮГО ц второго умножителей объединены и являются первым управляющим входом частотного модулятора, вход второго фазовращателя, второй вход первого умножителя и первый вход третьего умножителя объединены и являются вторым управляющим входом частотного модулятора, выход квадратора подключен к входу третьего фазовращателя и к первым входам четвертого

и пятого умножителей, выход первого фазовращателя подключен к первому входу шестого умножителя и к второму входу третьего умножителя, выход второго фазов

ращателя подключен к второму входу второ го умножителя и к второму входу шестой умножителя, выход третьего фазовращате ля подключен к первым входам седьмого восьмого умножителей, выходы первой

второго, третьего и шестого умножителе подключены к вторым входам четвертой восьмого, седьмого и пятого умножителе соответственно, выходы четвертого, пятой и восьмого умножителей подключены к уп

равляющим входам первого, второго к третьего фазовых модуляторов соответственно, выходы последних и выход седьмого умножителя подключены к первому, второму, третьему и четвертому входам аналогового сумматора соответственно, выход последнего является выходом частотного модулятора,

3.Система поп 1,отличающаяся тем, что блок управления сдвигом фазы со

держит триггер, два ключа, фазовращатель и сумматор, информационный вход и синх- ровход триггера являются первым управляющим и тактовым входами блока соответственно, первый и второй входы

триггера подключены к первым входам первого и второго ключей соответственно, выходы последних подключены к входам сумматора, выход которого является выходом блока, второй вход первого ключа и

вход фазовращателя объединены и являются вторым управляющим входом блока, выход фазовращателя подключен к второму входу второго ключа.

4.Система по п. 1,отличающаяся тем, что селектор несущей частоты и частоты

цикла содержит коммутатор, элемент задержки, фильтр несущей частоты, синхронизатор и приемник, первый вход которого и вход элемента задержки объединены и яаляются информационным входом селектора, соответствующие входы групп входов приемника и входы первой группы входов коммутатора объединены и являются входами группы информационных входов селек0 тора, выход элемента задержки подключен к первым входам фильтра несущей частоты и синхронизатора, выход последнего подключен к второму входу приемника и является первым выходом селектора, выходы

5 приемника подключены к входам второй группы входов коммутатора, выход которого подключен к вторым входам синхронизатора и фильтра несущей частоты, выход которого является вторым выходом селектора,

J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования сигналов с четырехпозиционной манипуляцией | 2016 |

|

RU2631149C1 |

| Система связи с многоосновным кодированием | 1987 |

|

SU1443190A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

| ФАЗОВЫЙ МОДУЛЯТОР ШУМОПОДОБНОГО КОЛЕБАНИЯ | 2017 |

|

RU2656722C1 |

| ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ С ПОВЫШЕННОЙ ИНФОРМАЦИОННОЙ СКРЫТНОСТЬЮ | 1992 |

|

RU2033692C1 |

| ПРИЕМНО-ПЕРЕДАЮЩЕЕ УСТРОЙСТВО ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2123761C1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ С МНОЖЕСТВЕННЫМ ДОСТУПОМ И ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2003 |

|

RU2240653C1 |

| ЛИНИЯ РАДИОСВЯЗИ | 2002 |

|

RU2219660C2 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

Изобретение относится к радиотехнике и может быть использовано в системе передачи данных. Цель изобретения - повышение информативности системы за счет уменьшения полосы частот при передаче сигналов по радиоканалу связи. Система содержит на передающей стороне блок ввода информации, блок дифференциального кодирования, сдвиговый регистр, регистр, частотный модулятор, усилитель, формирователь опорных сигналов, два делителя, фазовый модулятор, синтезатор несущей частоты, дешифратор, синтезатор низкой частоты, блок управления сдвигом фазы, на приемной стороне блок приема информации, многоканальный коррелятор, блок выделения максимального сигнала, два дешифратора, формирователь опорных сигналов, селектор несущей частоты и частоты цикла, блок восстановления информации, блок вывода информации, умножитель и блок относительного декодирования. 3 з.п. ф-лы, 4 ил.

I

ft/2 /

/I

/ ъ

37

42

h

Г 28 Т

3

pue.2

Фие.З

| Система связи с многоосновным кодированием | 1982 |

|

SU1069175A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1991-04-15—Публикация

1989-02-13—Подача