I

(21)4699046/24

(22)11.04.89

(46) 23.04.91. Бкш. Р 15 (72) А.С.Родин, А.П.Пабанов и В.Ю.Бабичев

(53)681.325(088.8)

(56)Авторское свидетельство СССР И 951306, кл. С 06 F 9/22, 1981.

Авторское свидетельство СССР № 1282125, кл. G 06 F 9/46, 1985.

(54)УСТРОЙСТВО ПРИОРИТЕТНОГО ПРЕРЫВАНИЯ

(57)Изобретение относится к вычисли- . тельной технике и может быть использовано в ЭВМ, применяемых в качестве управляющих устройств в различных си-

W

стемах и комплексах. Целью изобретения является расширение области применения за счет обработки запроса с учетом времени его прерывания. Устройство приоритетного прерывания содержит блок приоритетного прерывания, дешифратор, группу элементов И и таймер, содержащий группу счетчиков, триггеров и элементов ИЛИ-НЕ. В устройстве отслеживаются ситуации, когда время дообслуживания принятого запроса меньше времени, требуемого ЭВМ для перехода к обслуживанию запроса с оольшим приоритетом, при этом учитывается приоритет прерывающего запроса.1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритетного прерывания | 1985 |

|

SU1282125A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для приоритетного прерывания | 1985 |

|

SU1287159A1 |

| Устройство приоритетного прерывания для микро-ЭВМ | 1982 |

|

SU1113803A1 |

| Многоканальное устройство приоритета | 1985 |

|

SU1283765A1 |

| Устройство приоритета | 1986 |

|

SU1410031A1 |

| Устройство для обслуживания запросов | 1989 |

|

SU1741132A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1571588A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1984 |

|

SU1332326A1 |

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ, применяемых в качестве управляющих устройств в различных системах и комплексах.

Целью изобретения является расширение области применения за счет обработки запроса с учетом времени его прерывания.

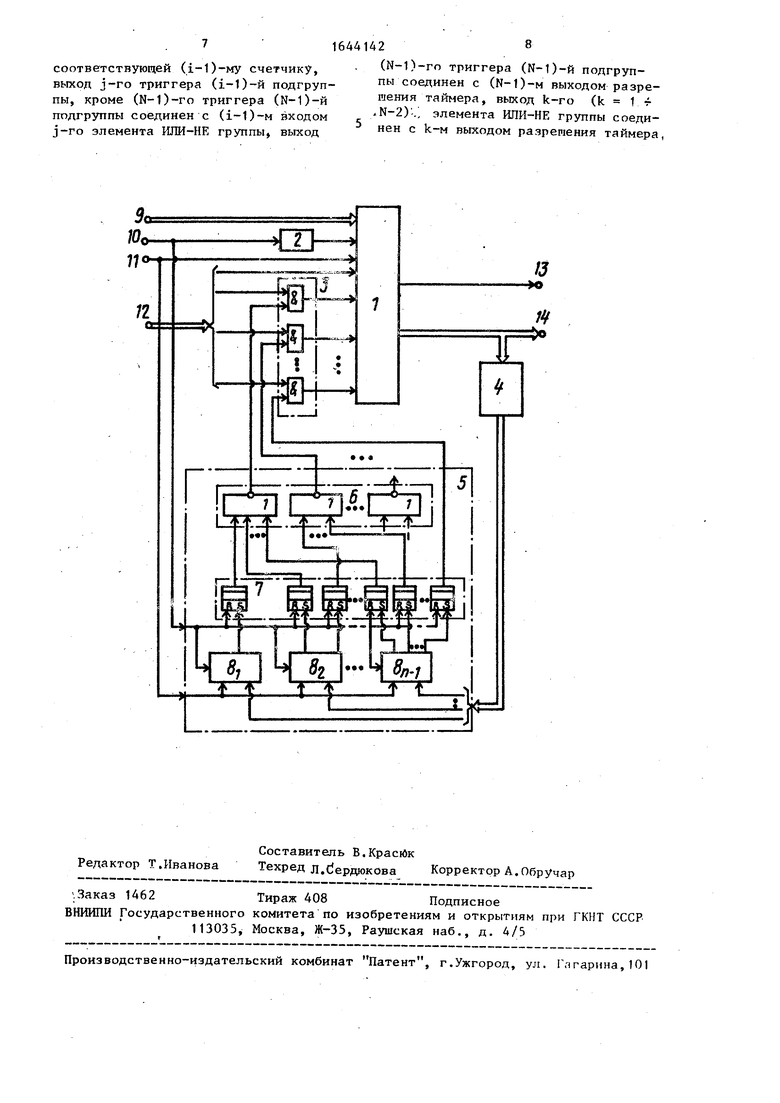

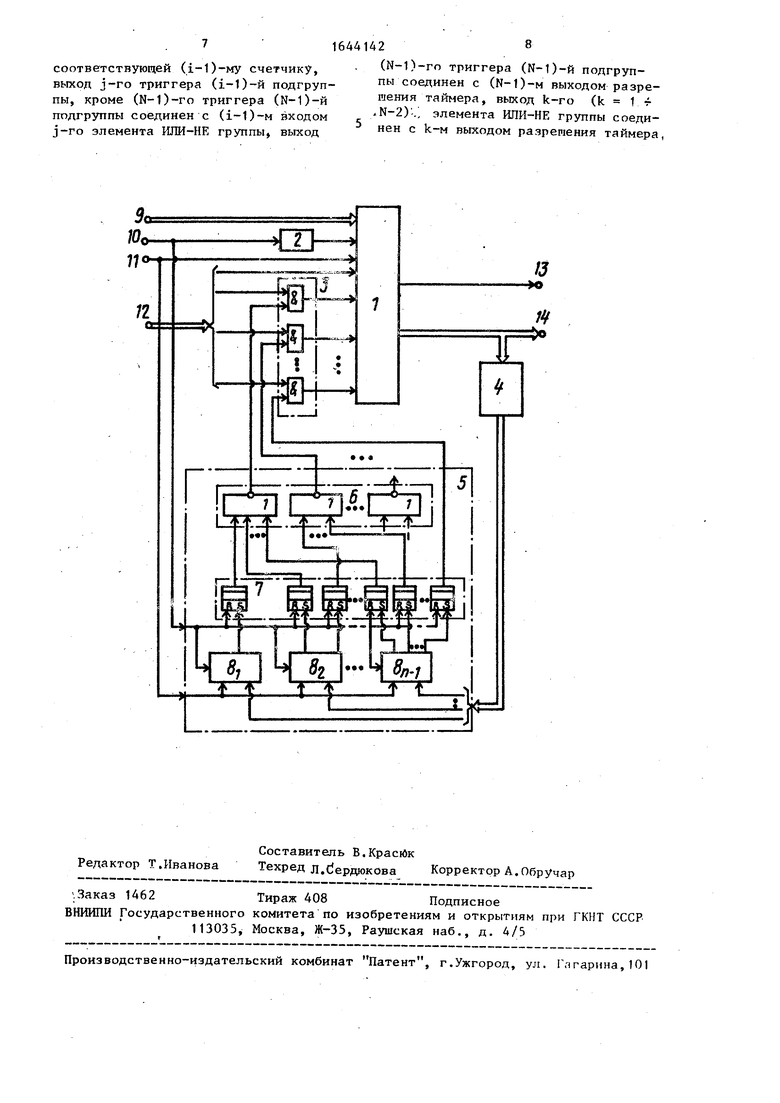

На чертеже представлена структурная электрическая схема устройства приоритетного прерывания.

Устройство содержит блок 1 приоритетного прерывания (БПП), элемент задержки 2, группу 3 элементов И, дешифратор 4, таймер 5, состоящий из группы 6 элементов ШМ-HR, группы 7 триггеров, счетчиков 8,8П,, группу входов 9 кода текущего приоритета, вход 10 разрешения приема кода текущего состояния, тактовый

вход 11, группу входов 12 запросов на прерывания, выход 13 сигналов прерывания и группу выходов 14 кодов запросов.

Устройство работает следующим образом.

В исходном состоянии ЭВМ свободна и это ее состояние зафиксировано в БГШ 1. На выходе сигналов прерывания 13 имеется единичный сигнал (логическая единица).

При поступлении на вход БПП 1 запроса на прерывание через вход 12 устройства и элемент И 3 группы на выходе БГОТ 1 и соответственно на выходе 13 устройства появляется нулевой сигнал (логический нуль), который фиксируется ЭВМ. ЭВМ, обнаружив сигнал прерывания, записывает его в свою память, после чего вырабатывает и выдает на вход 10 устройства и

а

4

4 №

3164

далее на вход установки таймера 5 и на вход элемента задержки 2 сигнал разрешения приема кода ее нового состояния. Этот сигнал устанавливает в исходное (нулевое) состояние все триггеры и счетчики в таймере 5 и, задержавшись на один такт в элементе задержки 2, поступает на КПП 1.При полученииг данного сигнала КПП 1 вы- дает на вход дешифратора 4 и выход 14 устройства код запроса, соответствующий приоритету этого запроса. После считывания кода запроса и записи нового состояния ЭВМ в БПП 1 сигнал разрешения приема кода текущего состояния ЭВМ снимается. НПП 1 переходит в состояние готовности к приему новых запросов на прерывания, а дешифратор 4, получив код запроса, вы- дает сигнал на группу входов запуска таймера 5. С группы входов запуска таймера 5 данный сигнал поступает на вход запуска одного из счетчиков 8 8„пи. При этом с дешифратора 4 сиг- нал поступает на вход запуска счетчика 8 гч тогда, когда на его вход поступает код, соответствующий запросу самого низкого приоритетного уровня, и соответственно на счет-

чик 8. сигнал запуска поступает при появлении на входе дешифратора 4 кода, соответствующего запросу второго приоритетного уровня. Если на выход 14 устройства и вход дешифратора 4 с БПП 1 выдается код запроса первого (высшего) приоритетного уровня, то с дешифратора 4 на группу входов запуска таймера 5 сигнал не поступает. В выработке такого сигнала нет необходимости, так как процесс обслуживания запроса высшего приоритета в ЭВМ не прерывается, а ВПП 1 до - окончания рбслуживания этого запроса сигналы прерывания не формирует и на выходе 13 устройства нулевой сигнал не появляется.

При появлении сигнала на входе запуска счетчика 8 последний начинает отсчет заданного количества mt тактов. Если в течение отсчета т,, тактов счетчиком 84 на выходе сигналов прерывания НПП 1 появляется нулевой сигнал, что означает в данном случае появление запроса на прерывание высшего приоритета, то этот сигнал через выход 13 устройства передается на вход 3RM. Последняя прекращает обработку ранее принятого прерывания,

Q 5 0

5

0

5

0

5

0

5

записывает вновь поступившее и посыпает на вход 10 устройства сигнал разрешения приема кода нового состояния ЭВМ в НПП 1 через элемент задержки 2, а также на установочный вход таймера 5. Счетчик 8 в таймере 5 переходит в исходное состояние (обнуляется), а через такт (время задержки в элементе задержки 2) в НПП 1 записывается это новое состояние ЭВМ. После снятия сигнала с входа 10 устройства КПП 1 переходит в состояние готовности к приему новых запросов на прерывания, но ни один из счетчиков таймера 5 не ведет отсчет тактов. Если во время отсчета счетчиком 8 в таймере 5п тактов нулевой сигнал прерывания на выходе КПП 1 (выходе 13 устройства) не появляется, то по окончании счета т тактов счетчик 8,, выдает на S-вход первого триггера в группе 7 триггеров сигнал, по которому последний переходит в единичное состояние. С выхода данного триггера сигнал (логическая единица) через первый элемент ИЛИ-НЕ в группе 6 элементов ШШ-НЕ таймера 5 передается в инвертированном виде (уже как логический нуль) на разрешающий вход одного из элементов И группы 3 и закрывает его, запрещая тем самым поступление сигнала запроса высшего приоритета с группы входов 12 устройства на выделенный данному приоритету вход запроса на прерывание БПП 1. Только после обработки в ЭВМ записанного прерывания, когда она выдаст на вход 10 устройства сигнал разрешения приема ее состояния, счетчик 8 и триггер в группе 7 триггеров таймера 5 перейдут в исходное состояние (обнуляются) и сигнал запрета (логический нуль) с разрешающего входа элементов И группы 3 снимается. Спустя такт сигнал разрешения приема нового сигнала ЭВМ с входа 10 устройства пройдет элемент задержки 2 и поступит на вход КПП 1, обеспечив считывание выработанного в БПП 1 кода запроса на группу выходов 14 устройства из сигнала запроса на прерывание, поступившего тактом ранее через открывшийся элемент И группы 3 на выделенный для высшего приоритета вход запроса на прерывание БПП 1.

Если с группы выходов кодов запросов на прерывания КПП 1 выдается

код, соответствующий запросу низшего приоритета, но в таймере 5 счетчик 8 п- начинает отсчет in так- (i 1, п-1). При завершении

тон

отсчета m м ; , . . . ,тп

тактов

П-1

соответственно на свои, вмходы 1, 2,...,п-1 счетчик 8.--. вьщает сигналы, поступающие далее на входы тригеров в группе 7 триггеров, переводящие эти триггеры в единичные состояния. Единичные сигналы поступают на элементы ИЛИ-НЕ группы 6, а далее с выходов элементов ИЛИ-НЕ группы 6 элементов ИЛИ-НЕ инвертированные сигналы (логические нули) передаются на разрешающие входы элементов И в группе 3 элементов И и закрывают их.

Алгоритм работы устройства приоритетного прерывания при отсчете счетчиком 8 (i 1, п-1) в таймере 5 какого-либо количества тактов аналогичен алгоритму его работы, описанному выше для счетчика 8 .

Сигналы запросов на прерывание, соответствующие поступлению запросов низшего (n-го) приоритета с вход 12 устройства, поступают непосредственно на вход КПП 1, минуя группу 3 элементов И, так как эти сигналы не вызывают формирования и выдачи на выход 13 устройства логических нулей и прерывания процессов обслуживания заявок в ЭВМ.

На разрешающий вход элемента И в группе 3 элементов И, через которую в БПП 1 поступают запросы на прерывания от заявок предпоследнего (n-l)-ro приоритетного уровня, сигналы запрета поступают непосредственно с триггера группы 7 триггеров, S-вход которого соединен с выходом счетчика таймера 5. Т.е. управление указанным элементом И обеспечивается только от счетчика , через триггер, так как при поступлении запросов на прерывания от заявок предпоследнего приоритетного уровня могут блоком Г приоритетного прерывания выдаваться логические нули на выход 13 устройства, если в ЭВМ обслуживаются заявки последнего (низшего) приоритета.

Формула изобретения

Устройство приоритетного прерывания, содержащее блок приоритетного прерывания и таймер, причем группа

входов кода текущего приоритета устройства соединена с группой входов кода текущего состояния блока приоритетного прерывания, тактовый вход которого соединен с тактовым входом таймера и является тактовым входом устройства, вход разрешения приема кода текущего состояния устройства

соединен с установочным входом таймера,первый вход запроса на прерывание блока приоритетного прерывания соединен с первым запросным входом устройства, группа выходов кода запроса блока приоритетного прерывания является группой выходов устройства, отличающееся тем, что, с целью расширения области применения за счет обработки запроса с учетом времени его прерывания, в него введены элемент задержки, группа из N-1 элементов И (N - число входов запросов на прерывание устройства) и дешифратор, а таймер содержит группу из N-2 элементов ИЛИ-НЕ,

группу из N

(N-1) 2

триггеров и N-1

счетчиков, причем вход элемента за- держки соединен со входом разрешения приема кода текущего состояния устройства, а выход - с входом разрешения приема кода текущего состояния блока приоритетного прерывания, 1-й (i 2; N) вход запроса на прерывание которого соединен с выходом (i -1)-го элемента И группы, первый вход которого соединен с i-м запросным входлм устройства, группа выходов

кода запроса блока приоритетного прерывания соединена с группой входов дешифратора, группа выходов которого соединена с группой входов запуска таймера, выход прерывания блока приоритетного прерывания соединен с выходом прерывания устройства, второй вход (i-l)-ro элемента И группы соединен с (1-1)-м выходом разрешения таймера, в таймере установочный

вход таймера соединен с нулевым входом каждого триггера группы и с входом сброса каждого счетчика, тактовый вход соединен с тактовым входом каждого счетчика (i-1)-и вход запуска

таймера соединен с входом запуска (i-1)-ro счетчика j-й (j I f i-1) выход (i-lj-ro счетчика соединен с единичным входом j-ro триггера в (i -1)-й подгруппе из (i-1) триггеров,

соответствующей (1-1)-му счетчику, выход j-ro триггера (1-1)-й подгруппы, кроме (N-l)-ro триггера (М-1)-й подгруппы соединен с (1-1)-м входом j-ro элемента ИЛИ-НЕ группы, выход

I I I

ф-.. f /С-J

(N-1)-ro триггера (N-l)-ft подгруппы соединен с (N-I)-M выходом разрешения таймера, выход k-го (k 1 4 .N-2) -., элемента ИЛИ-НЕ группы соединен с k-м выходом разрешения таймера,

Авторы

Даты

1991-04-23—Публикация

1989-04-11—Подача