сан первый байт адреса подпрограммы обслуживания прерывания, поступает из активизированного БПП и записывается в регистр адреса, здесь же происходит инкрементировайие адреса

1

Изобретение относится к вычислительной технике и может быть использовано для организации прерываний в микро-ЭВМ.

Целью изобретения является расширение функциональных возможностей за счет формирования абсолютного адреса подпрограммы обслуживания прерывания.

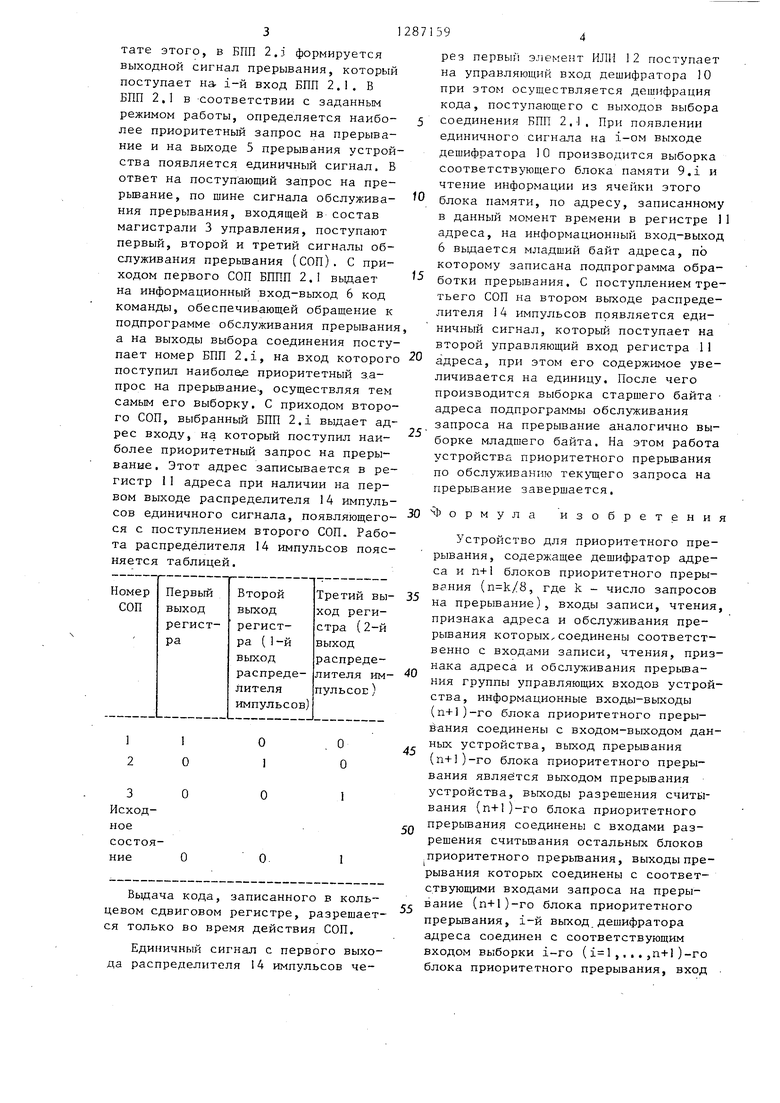

На чертеже изображена структурная схема предлагаемого устройства-для приоритетного прерывания.

Устройство содержит дешифратор 1 адреса, п блоков приоритетного прерывания (БПП) 2,.п, магистраль 3 управления, содержащую шины Запись , Чтение, Признак адреса, Обслуживание прерывания, входы 4 запросов, выход 5 прерывания устройства, информационный вход-выход 6 устройства, вход 7 адреса, магистральный усилитель 8, п-1 блоков памяти 9.1- 9.П-1, дешифратор 10, регистр 11 .адреса, первый и второй элементы ИЛИ 12 и 13 и распределитель 14 импульсов .

Блок приоритетного прерьтания может быть вьтолнен на базе микросхемы программируемого блока приоритетного прерьшания, производящей переход на подпрограмму обслуживания прерьшания с помощью команды типа CALL , , где CALL - команда, передаваемая по прерьшанию; А - младший байт адре- :Са; А- - старший байт адреса подпрограммы обработки на прерывание (например, микросхема К580ИК59).

Устройство работает следующим образом.

В исходном состоянии в блоки 9.1- 9.п-1 памяти по четным адресам, начиная с нулевого, записаны младшие байты адресов подпрограммы обслуживания запросов на прерывание, а по нечетным - соответствующие старшие байты

для выбора второго байта адреса подпрограммы. Работа отдельных узлов устройства тактируется импульсами, поступающими от распределителя импульсов. 1 ил., 1 табл.

адресов. Здесь считается, что адреса памяти представляют собой двухбайтные числа. В распределителе 14 импульсов, в случае его выполнения на кольцевом регистре записан код 001. Единица находится в старшем разряде.

Перед началом работы устройства для прерывания производится програмJQ мирование всех БПП 2.1-2.П путем записи в них управляющих слоев. Во время программирования БПП 2,1 (,n) осуществляется его выборка с помощью дешифратора 1 адреса, на который по

15 входу адреса устройства поступает адрес БПП 2.1. При этом под воздействием управляющих.сигналов, поступающих по магистрали 3 управления в БПП 2.1, записываются управляющие

20 слова. Причем запись информации в БПП 2.1 производится непосредственно с информационного вх9Да-выхода 6 устройства, а в остальные - через магистральный усилитель 8, который откры25 Бается только во время обращения к БПП 2, 2-2 .п под воздействием единичног сигнала, поступающего с выхода элемента ИЛИ 13 на второй управляющий вход. Направлением передачи информаЗОции через магистральный усилитель 8 управляет сигнал записи, поступающий с магистрали 3 управления на первый управляющий вход. Как правило программирование БПП производится послеЗздовательной записью трех управляющих слов. После программирования всех БПП устройство прерывания готово к работе.

40

45

Запросы на прерывание поступают на входы 4 запросов, С поступлением одновременно нескольких запросов на прерывание на входы 1-го БПП 2.1 в нем согласно установленному режиму обслуживания запросов, заданного управляющими словами, выделяется наиболее приоритетный запрос, В резуль

тате этого, в БПП 2.J формируется выходной сигнал прерывания, который поступает на- i-й вход БПП 2.1, Б БПП 2.1 в соответствии с заданным режимом работы, определяется наиболее приоритетный запрос на прерывание и на выходе 5 прерывания устройства появляется единичный сигнал. В ответ на поступающий запрос на пре- рьюание, по шине сигнала обслуживания прерывания, входящей в состав магистрали 3 управления, поступают первый, второй и третий сигналы обслуживания прерьшания (СОП). С приходом первого СОП БППП 2.1 выдает на информационный вход-выход 6 код команды, обеспечивающей обращение к подпрограмме обслуживания прерывания а на выходы выбора соединения поступает номер БПП 2.1, на вход которого поступил наиболее приоритетный з.а- прос на прерьшание., осуществляя тем самым его выборку. С приходом второго СОП, выбранный БПП 2.1 выдает адрес входу, на который поступил наиболее приоритетный запрос на прерывание. Этот адрес записывается в регистр 11 адреса при наличии на первом выходе распределителя 14 импульсов единичного сигнала, появляющегося с поступлением второго СОП. Работа распределителя 14 импульсов поясняется таблицей.

Выдача кода, записанного в кольцевом сдвиговом регистре, разрешается только во время действия СОП,

Единичный сигнал с первого выхода распределителя 14 импульсов чеfO

15

0

25

рез первый элемент ИЛИ 12 поступает на управляющий вход дешифратора 10 при этом осуществляется дешифрация кода, поступающего с выходов выбора соединения БПП 2.. При появлении единичного сигнала на 1-ом выходе дешифратора 10 производится выборка соответствующего блока памяти 9,1 и чтение информации из ячейки этого блока памяти, по адресу, записанному в данный момент времени в регистре 11 адреса, на информационный вход-выход 6 вьщается младший байт адреса, по которому записана подпрограмма обработки прерывания, С поступлением третьего СОП на втором выходе распределителя 14 импульсов появляется единичный сигнал, которьш поступает на второй управляющий вход регистра 11 адреса, при этом его содержимое увеличивается на единицу. После чего производится выборка старшего байта адреса подпрограммы обслуживания запроса на прерывание аналогично выборке младшего байта. На этом работа устройства приоритетного прерьшания по обслуживанию текущего запроса на прерывание завершается,

ЗО Формула изобретения

Устройство для приоритетного прерывания, содержащее дешифратор адреса и п+1 блоков приоритетного прерывания (, где k - число запросов на прерывание), входы записи, чтения, признака адреса и обслуживания прерывания которых соединены соответственно с входами записи, чтения, признака адреса и обслуживания прерьшания группы управляющих входов устройства, информационные входы-выходы (п+1)-го блока приоритетного преры- йания соединены с входом-выходом данных устройства, выход прерьшания (п+1)-го блока приоритетного прерывания является выходом прерьшания устройства, выходы разрешения считывания (n+l)-ro блока приоритетного прерывания соединены с входами разрешения считьшания остальных блоков приоритетного прерьшания, выходы прерывания которых соединены с соответствующими входами запроса на прерывание (п+1)-го блока приоритетного прерьшания, выход дешифратора адреса соединен с соответствующим входом выборки 1-го (,.,,,п+1)-го блока приоритетного прерьшания, вход

5

0

5

512

дешифратора адреса подключен к адресному входу устройства, входы запроса на прерывание п блоков приоритетного прерьшания являются входами запросов на прерьюание устройства, отличающеееся тем, что, с целью расширения функциональных .возможностей за счет формирования абсолютного адреса программы обслуживания прерьшания, в него введены магистральный усилитель, п блоков памяти, дешифратор, регистр адреса, первый и второй элементы ИЛИ и распределитель импульсов, причем информационный вход распределителя им- пульсов подключен к входу обслуживания прерывания группы управляющих входов устройства, первый выход распределителя импульсов соединен с первым входом записи регистра.адреса и первым входом первого элементаШ1И, выход которого соединен с входом разрешения дешифратора, выходы разрешения считывания (п+1)-го блока приориРедактор Ю. Середа

Составитель В. Гудовскнй Техред Л.Олейник

Заказ 7718/52 Тираж 694БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул.Проектная, 4

596

тетного прерьшания соединены с информационными входами дешифратора, выходы которого соединены с соответствующими входами выборки соответствующих блоков памяти, выход регистра адреса соединен с адресными входами блоков памяти, выходы которых подключены .к входу-выходу данных устройства, вход записи магистрального усилителя соединен с входом записи группы управляющих входов устройства, вход выборки магистрального усилителя соединен с выходом второго -элемента ИЛИ, входы которого соединены соответственно с первого по п-й выходами дешифратора адреса, входы-выходы данных п блоков приоритетного прерывания соединены с первым входом- выходом магистрального усилителя и информационным входом регистра адреса , второй вход - выход магистрального усилителя соединен с входом - выходом данных устроцст- ва.

Корректор Е. Сирохман Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритетного прерывания для микроЭВМ | 1986 |

|

SU1446620A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для обслуживания запросов | 1985 |

|

SU1283768A1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Система для обмена информацией | 1985 |

|

SU1298760A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1176340A1 |

| Устройство для программного управления объектом | 1988 |

|

SU1605211A1 |

Изобретение относится к области вычислительной техники и может быть использовано для организации прерывания в микро-ЭВМ. Устройство для приоритетного прерьтания обеспечивает непосредственный переход на подпрограмму обслуживания запроса прерывания, записанную в постоянной памяти микро-ЭВМ, путем выбора младшего и старшего байтов адреса этой подпрограмм из блока памяти. При этом отпадает необходимость в формировании дополнительного перехода по адресу, где размещена подпрограмма обслуживания прерьшания. Устройство для приоритетного прерывания содержит дешифратор адреса 1 (п+1) блоков приоритетного прерьшания 2 (РПП), магистральный усилитель 8, п блоков .памяти 9, дешифратор 10, регистр адреса П, два элемента ИЛИ 12 и 13 и распределитель импульсов 14. При обслуживании запроса прерывания по коду, вьщаваемому ведущим БПП, выбираются ведомый БПП и блок памяти, соответствующий этому БПП. Адрес ячейки блока памяти, в которой запи« (Л tc 00 ел со

| Устройство приоритетного прерывания для микро-ЭВМ | 1982 |

|

SU1113803A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Горбунов В | |||

| П., Панфилов Д | |||

| И., Преснухин Д | |||

| П, Микропр оцессоры | |||

| Основы построения микро-ЭВМ | |||

| М.: Высшая школа, 1984, с | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-01-30—Публикация

1985-05-28—Подача