кументированием всех да1пых Поставлен- нал цель достигается использованием дешифратора 6, позволяющего определять признак передаваемого сообщения на основании информации, содержащейся в регистре 1, дешифратора 7, осуществляющего коммутацию устройства с нужным объектом управления для последующего обмена информацией. Одновременное до- 10 кументирование данных обеспечивается при помощи введения дополнительного блока памяти, что позволяет осуществлять считывание протокола обмена из одного блока памяти в то время, как 15 другой блок памяти используется для документирования информации. Каждому объему управления выделяется фиксированная область памяти, что достигается применением блока 20 формиро- 20

вания текущего адреса. Определение текущего адреса осуществляется сумматором 11 посредством сложения базового адреса в блоке памяти для данного объекта управления и смещения. Базовые адреса хранятся в блоке 3 памяти. По заполнении информацией, предназначенной объекту управления, выделенной для нее области происходит переключение блоков памяти таким образом, ч то блок памяти, который служит для документирования информации, становится доступным для считывания протокола обмена, а вместо него подключается другой блок памяти. Такая возможность обеспечивается использованием мультиплексоров 21. и 22 и блока 23 управления считыванием, 6 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ПОГРАНИЧНОГО КОНТРОЛЯ | 2006 |

|

RU2316811C1 |

| Устройство для идентификации паролей пользователей | 1988 |

|

SU1667116A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| Устройство для контроля ответов обучаемого | 1987 |

|

SU1529272A1 |

| Устройство для выборки информации из блока памяти | 1986 |

|

SU1387033A1 |

| Устройство для формирования учебной информации | 1988 |

|

SU1562951A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Устройство для контроля знаний обучаемых | 1989 |

|

SU1679523A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| СИСТЕМА ЭЛЕКТРОННОГО ДИСТАНЦИОННОГО SMS-ГОЛОСОВАНИЯ | 2010 |

|

RU2421813C1 |

Изобретение относится к-вычислительной технике, в частности к системам накопления информации. Цель изобретения - расширение функциональных возможностей системы за счет реализации функции анализа признаков передаваемой информации и адресации ее объектам управления с одновременным до(Л оэ 4 4Ь Ј СО

Изобретение относится к области 2 автоматизированных систем управления, в частности к системам обмена информацией.

Цель изобретения - расширение функциональных возможностей системы за 3 счет реализации функции анализа признаков передаваемой информации и адресации ее объектам управления с одновременным документированием всех данных.

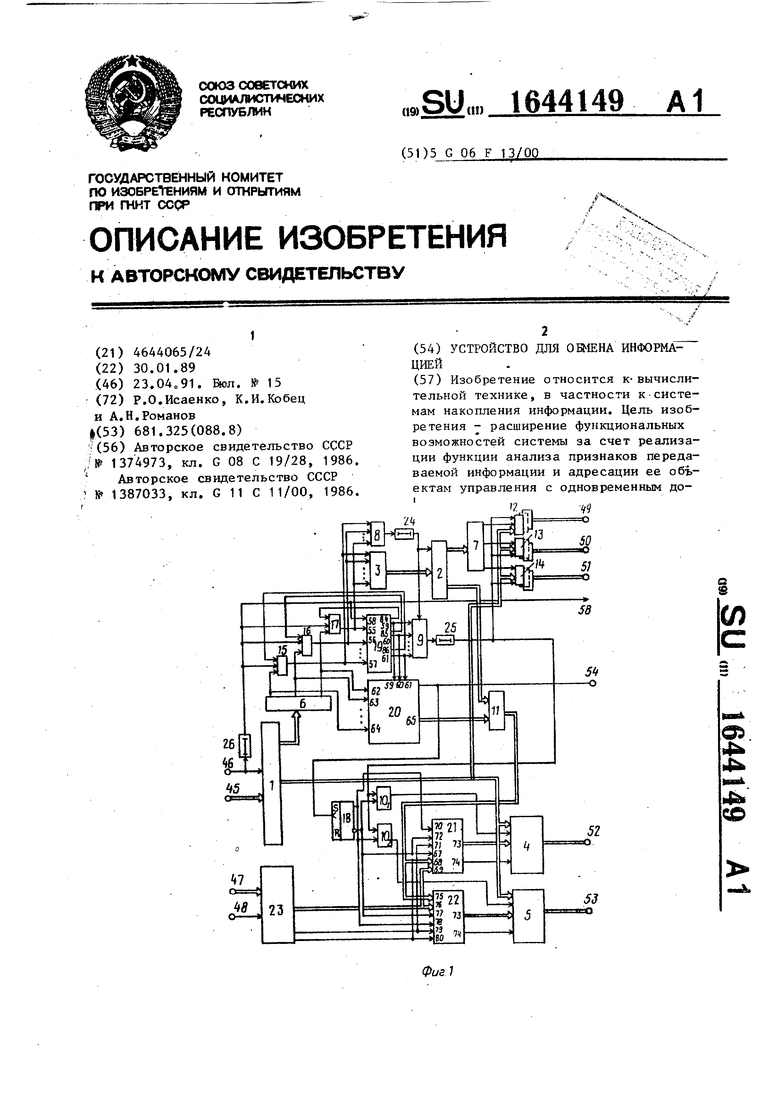

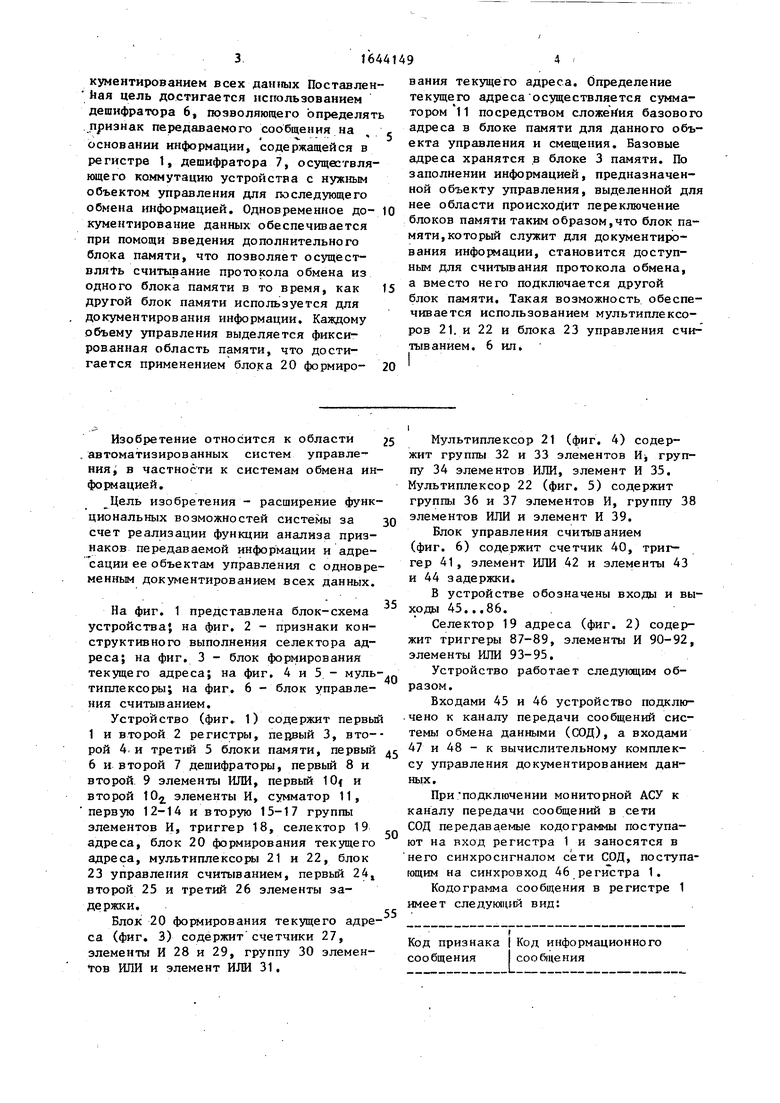

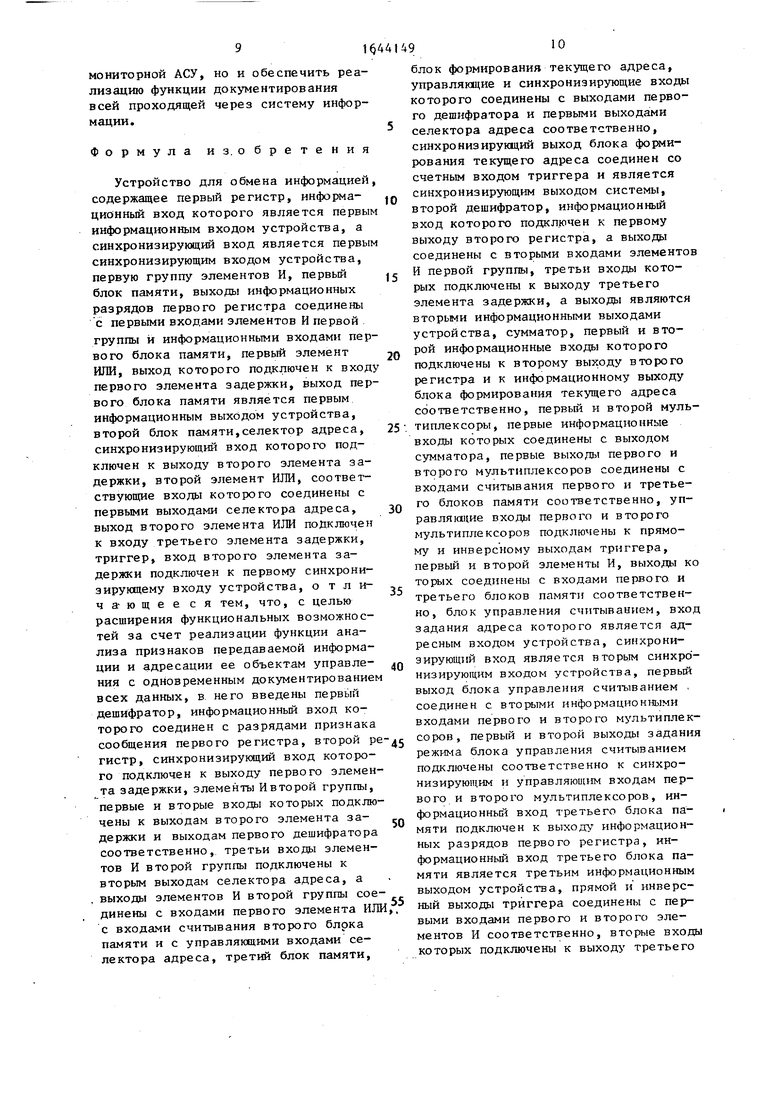

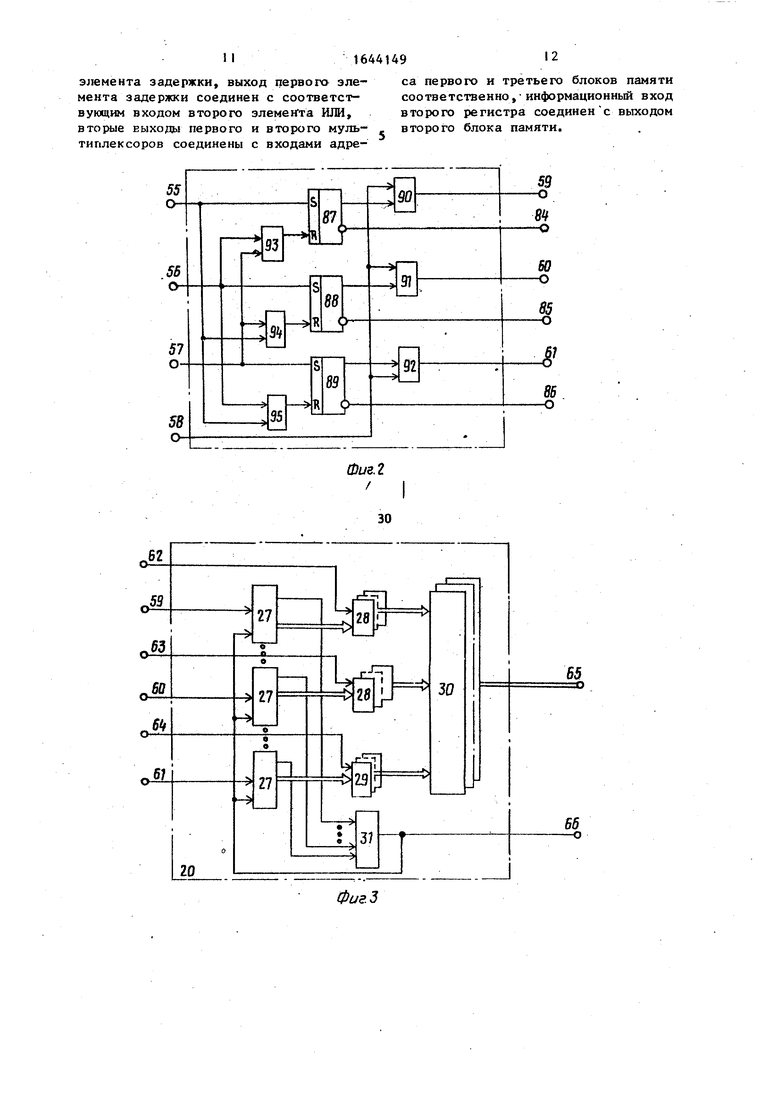

На фиг, 1 представлена блок-схема устройства} на фиг. 2 - признаки конструктивного выполнения селектора адреса; на фиг. 3 - блок формирования текущего адреса; на фиг, 4 и 5 - мультиштексоры; на фиг. 6 - блок управления считыванием.

Устройство (фиг. 1) содержит первый 1 и второй 2 регистры, певвый 3, вто-- рой 4 и третий 5 блоки памяти, первый 6 и второй 7 дешифраторы, первый 8 и второй 9 элементы ИЛИ, первый 10 и второй 10 элементы И, сумматор 11, первую 12-14 и вторую 15-17 группы элементов И, триггер 18, селектор 19 адреса, блок 20 формирования текущего адреса, мультиплексоры 21 и 22, блок 23 управления считыванием, первый 244 второй 25 и третий 26 элементы задержки.

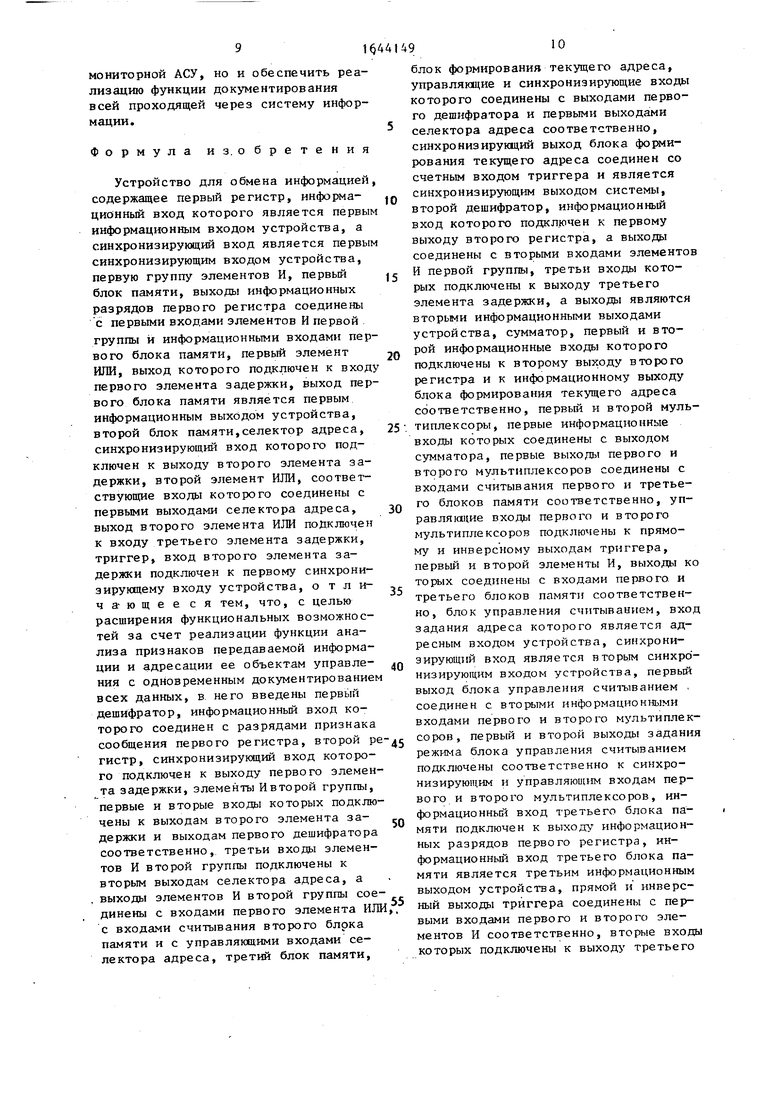

Блок 20 формирования текущего адреса (фиг. 3) содержит счетчики 27, элементы И 28 и 29, группу 30 элементов ИЛИ и элемент ИЛИ 31.

-

0

5

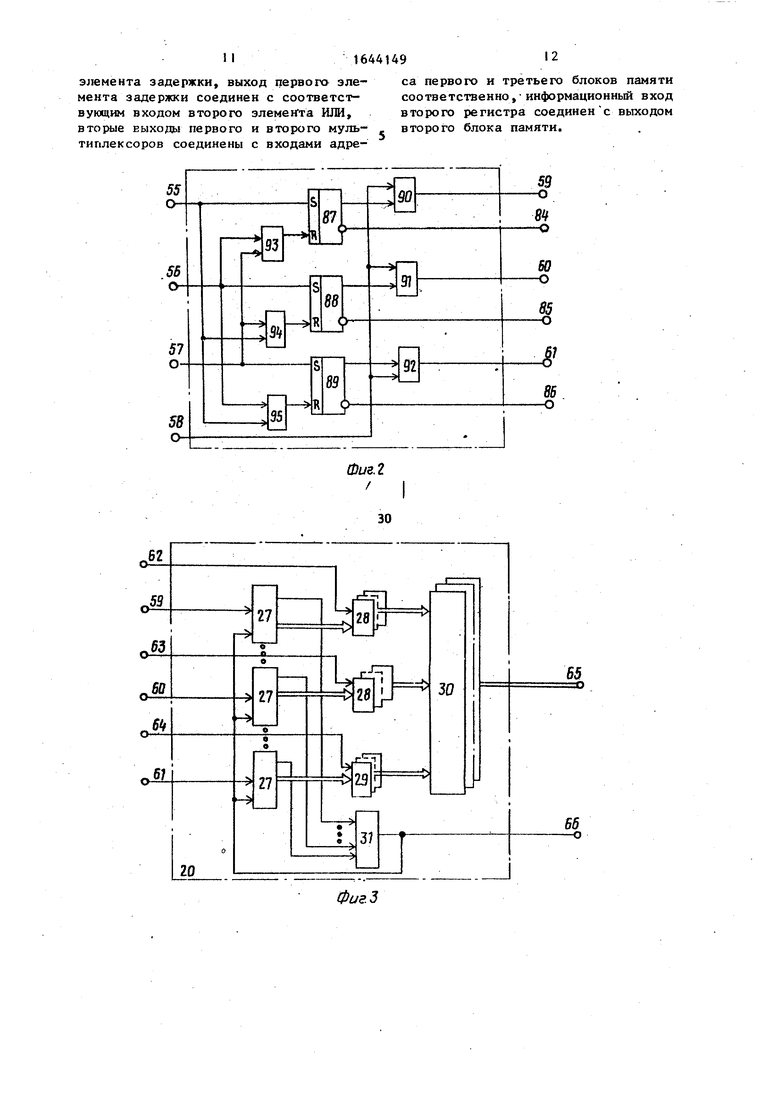

Мультиплексор 21 (фиг. 4) содержит группы 32 и 33 элементов И, группу 34 элементов ИЛИ, элемент И 35. Мультиплексор 22 (фиг. 5) содержит группы 36 и 37 элементов И, группу 38 элементов ИЛИ и элемент И 39.

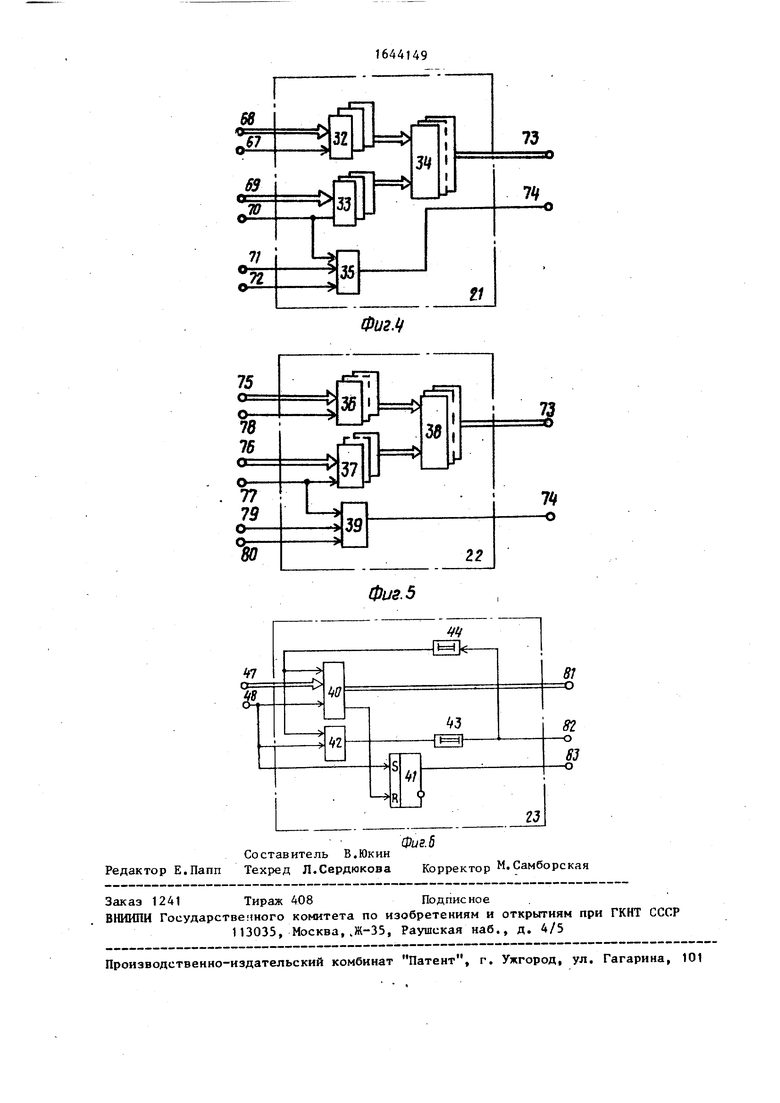

Блок управления считыванием (фиг. 6) содержит счетчик 40, триггер 41, элемент ИЛИ 42 и элементы 43 и 44 задержки.

В устройстве обозначены входы и выходы 45...86.

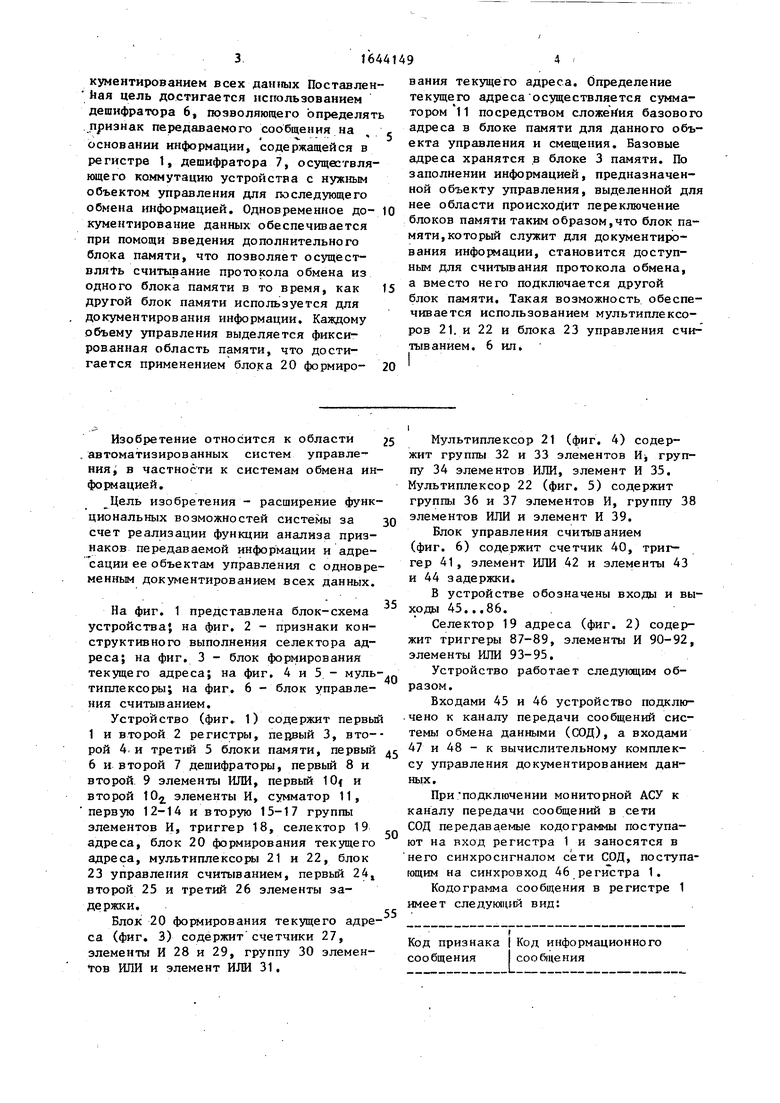

Селектор 19 адреса (фиг. 2) содержит триггеры 87-89, элементы И 90-92, элементы ИЛИ 93-95.

Устройство работает следующим образом.

Входами 45 и 46 устройство подключено к каналу передачи сообщений системы обмена данными (СОД), а входами 47 и 48 - к вычислительному комплексу управления документированием данных.

При подключении мониторной АСУ к каналу передачи сообщений в сети СОД передаваемые кодограммы поступают на вход регистра 1 и заносятся в него синхросигналом сети СОД, поступающим на синхровход 46 регистра 1.

Кодограмма сообщения в регистре 1 имеет следующий вид:

Г Код признака | Код информационного

сообщения I сообщения

516

Дешифратор 6 расшифровывает код признаковой части и в зависимости от кода признака открывает один из элементов И 15-17.

Например, если код признака соот- ветствует информации, относящейся к донесениям, будет открыт элемент И 15 если код признака соответствует информации, относящейся к заявкам, буде открыт элемент И 16, если к задачам - открыт элемент И 17 и т.п.

Допустим, что код признака поступившего сообщения относится к заявкам. Тогда будет открыт элемент И 16, на другой вход которого поступает синхроимпульс, задержанный элементами 26 на время срабатывания регистра 1 и дешифратора 6, Этот синхроимпульс проходит через элемент И 16 и одно- временно поступает на вход 56 селектора 19 адреса, на вход элемента ИЛИ 8 и на вход считывания фиксированной ячейки блока 3, выполненного в виде постоянного запоминающего

устройства.

Поступая на вход считывания фиксированной ячейки блока 3 памяти, этот импульс считывает содержимое ячейки блока 3 памяти в регистр 2, куда содержимое заносится синхроимпульсом с выхода элемента 24 задержки, задерживающего синхроимпульс на время считывания кода из блока 3 в регистр 2.

В каждой из фиксированных ячеек блотса памяти 3 хранится информация в следующем в иде:

Код базового 40 адреса в памяти, куда записывается входная информация 45

Дешифратор 7 расшифровывает код номера канала, по которому должна быть передана информация и открывает одни из элементов И 12-14, к входам кото- рых подключены информационные выходы первого регистра.

Синхроимпульс с выхода элемента 24 задержки проходит через элемент ИЛИ 9 и после задержки на время сбрасывания регистра 2 и дешифратора 7 элементом 25 он поступает на входы элементов И 12-14, переписывая (выдавая) через них содержимое регистра 1 TOMV

.Q

., 20 25

зо

35

40 45

Q

5

49 6

объекту мониторной АСУ, которому эта информация необходима, через соответствующие выходы 49-51.

Параллельно с описанным выше процессом выдачи информации объекту мониторной АСУ последняя должна быть документирована. С этой целью выходы дешифратора 6 и селектора 19 адреса соединены с соответствующими входами блока 20, а высокий потенциал с выхода дешифратора 6 (согласно данного примера) поступает на вход 63 блока 20.

Поскольку принято для примера, что открыт элемент И 16, то импульс с его выхода поступает на вход 56 селектора 19, откуда он поступает на единичный вход триггера 88 (фиг. 2) и устанавливает его в единичное состояние. Одновременно через элементы ИЛИ 93-95 этот импульс поступает на нулевые входы триггеров 87 и 89, сбрасывая их (или подтверждая) в исходное состояние.

Одновременно низким потенциалом с инверсного выхода триггера 88, подаваемым через выход 85 селектора 19 на один из входов элемента И 16, этот элемент запирается по третьему входу.

Высоким потенциалом с входа 63 (фиг. 3) в блоке 20 будет открыта по одному входу группа элементов И 28, к другим входам которых подключены выходы счетчика 27, находящегося в исходном состоянии.

Показания соответствующего счетчика 27 находящегося в нулевом состоянии, через элементы ИЛИ 30 поступают на выход 65 и далее на один вход комбинационного сумматора 11, на другой вход которого поступает код базового адреса с выхода регистра 2.

Сумматор 11 прибавляет к базовому адресу текущий адрес - число сообщений (в данном случае оно равно нулю) и на адресных входах блоков 4- ,и 5, выполненных в виде ОЗУ, устанавливается адрес ячейки памяти, куда должно быть записано сообщение. В качестве импульса записи используется тот же импульс синхронизации с выхода элемента задержки, который поступает на входы записи блоков 4 и 5 памяти через один из элементов И 10 t или 10,.

Учитывая, что триггер 18 находится в нулевом состоянии, следователь но, с инверсного выхода триггера открыт элемент И 10Х и импульс записи поступает только на вход записи блока 4.

Необходимость двух блоков памяти 4 и 5 обусловлена тем, что после заполнения соответствующих областей памяти один из блоков памяти отключается от режима записи (документирования) входных сообщений и переходит в режим считывания, а другой блок памяти, наоборот, из режима считывания переходит в режим записи. Задача управления работой этих блоко реализуется мультиплексорами 21 и 22, выполненными аналогичным образом (фиг. 4 и 5).

Адрес ячейки записи с выхода сумматора 11 поступает на одни адресные входы 68 и 75 мультиплексоров 21 и 22, а адрес ячейки считывания поступает на другие адресные входы 69 и 7 мультиплексоров.

Коммутация адреса с выходов элементов 32, 33 и 36, 37 через элемент ИЛИ 34 и 38 осуществляется потенциалми с прямого и инверсного выходов триггера 18.

Таким образом, в рассматриваемом случае на адресный вход блока 4 памяти с выхода 73 мультиплексора 21 поступает код адреса с входа 68, т.к с входа 67 на другие входы элементов И 32 подается разрешающий потенциал. Элементы И 33 по второму входу будут закрыты низким потенциалом с прямого выхода триггера 18 (вход 70 блока 21)

Заперт будет также элемент И 34 тем же отрицательным потенциалом. В то же время у второго мультиплексора 22 элементы И 36 будут блокированы низким потенциалом с прямого выхода триггера 18, а элементы И 37, на которые с входа 76 поступает код адреса считывания с блока 23, будут открыты высоким потенциалом с инверсного выхода триггера 18. Этим же потенциалом будет открыт элемент И 39, через который на вход управления считыванием блока 5 поступают импульсы с выхода блока 23. Момент переключения работы блоков 4 и 5 с режима на . режим фиксируется тогда, когда один и счетчиков (любой) 27 будет заполнен полностью.

Тогда очередной импульс с выхода переполнения одного из счетчиков 27 ((фиг. 3) проходит через элемент

0

5

0

5

0

5

0

5

0

5

ИЛИ 31 и поступает с выхода 66 на счетный вход триггера 18, переключая тем самым блоки 4 и 5 с режима на режим. Тот же импульс с выхода элемента ИЛИ 31 сбрасывает все счетчики в исходное состояние.

Для считывания той информации, которая записана одним из блоков памяти, на вход 47 блока 23 (фиг. 6) поступает код адреса считывания, на синхровход 48 блока 23 поступает сигнал считывания. По этому сигналу код адреса записывается в счетчик 40 и по кодовым шинам выдается на выход 81. Одновременно с этим тот же импульс с входа 48 проходит элемент ИЛИ 42 на вход элемента 43 задержки и единичный вход триггера 41, устанавливая последний в единичное состояние и выдавая тем самым высокий потенциал на выход 83.

После задержки на время занесения кода в счетчик 40 и срабатывания триггера 41 на выходе 82 появляется импульс считывания, который через входы 71 и 79 поступает на мультиплексоры 21 и 22.

Как только все адреса ячеек блока памяти будут просмотрены,на выходе переполнения счетчика 40 появится импульс, который возвращает триггер 41 в исходное состояние и с выхода 83 снимается высокий разрешающий потенциал.

Если же, например, по каналам сети СОД передается пакет кодограмм, относящихся к одному и тому же признаку, то очередной импульс (для данного случая) с выхода элемента 26 задержки не пройдет через элемент И 16, так как последний заперт с выхода 85 селектора 19.

В этом случае импульс с входа 58 (фиг. 2) селектора 19 пройдет через открытый по второму входу элемент И 91 на вход 60 и далее через элемент ИЛИ 9 описанным выше образом, а также с входа 60 блока 20 поступает на счетный вход соответствующего счетчика 27, фиксируя добавление единицы к текущему адресу записи информации с соответствующим признаком.

Таким образом, введение новых узлов и блоков позволило существенно расширить функциональные возможности системы, позволив не только реализовать функцию отбора требуемой инфор- мации из каналов передачи данных СОД и передаче ее объектам управления

мониторной АСУ, но и обеспечить реализацию функции документирования всей проходящей через систему информации.

Формула из. обретения

Устройство для обмена информацией, содержащее первый регистр, информа- ционный вход которого является первым информационным входом устройства, а синхронизирующий вход является первым синхронизирующим входом устройства, первую группу элементов И, первый

блок памяти, выходы информационных разрядов первого регистра соединены с первыми входами элементов И первой группы и информационными входами первого блока памяти, первый элемент ИЛИ, выход которого подключен к входу первого элемента задержки, выход первого блока памяти является первым информационным выходом устройства, второй блок памяти,селектор адреса, синхронизирующий вход которого подключен к выходу второго элемента задержки, второй элемент ИЛИ, соответствующие входы которого соединены с первыми выходами селектора адреса, выход второго элемента ИЛИ подключен к входу третьего элемента задержки, триггер, вход второго элемента задержки подключен к первому синхронизирующему входу устройства, о т л и- ча-ющее ся тем, что, с целью расширения функциональных возможностей за счет реализации функции анализа признаков передаваемой информации и адресации ее объектам управле- ния с одновременным документированием всех данных, в него введены первый дешифратор, информационный вход которого соединен с разрядами признака сообщения первого регистра, второй pe гистр, синхронизирующий вход которого подключен к выходу первого элемента задержки, элементы Ивторой группы, первые и вторые входы которых подключены к выходам второго элемента задержки и выходам первого дешифратора соответственно, третьи входы элементов И второй группы подключены к вторым выходам селектора адреса, а выходы элементов И второй группы соединены с входами первого элемента ИЛИ,. с входами считывания второго блока памяти и с управляющими входами селектора адреса, третий блок памяти,

5

55

Q j

0 5 0 5 Q j

0

5

блок формирования текущего адреса, управляющие и синхронизирующие входы которого соединены с выходами первого дешифратора и первыми выходами селектора адреса соответственно, синхронизирующий выход блока формирования текущего адреса соединен со счетным входом триггера и является синхронизирующим выходом системы, второй дешифратор, информационный вход которого подключен к первому выходу второго регистра, а выходы соединены с вторыми входами элементов И первой группы, третьи входы которых подключены к выходу третьего элемента задержки, а выходы являются вторыми информационными выходами устройства, сумматор, первый и второй информационные входы которого подключены к второму выходу второго регистра и к информационному выходу блока формирования текущего адреса соответственно, первый и второй мультиплексоры, первые информационные входы которых соединены с выходом сумматора, первые выходы первого и второго мультиплексоров соединены с входами считывания первого и третьего блоков памяти соответственно, управляющие входы первого и второго мультиплексоров подключены к прямому и инверсному выходам триггера, первый и второй элементы И, выходы ко торых соединены с входами первого и третьего блоков памяти соответственно, блок управления считыванием, вход задания адреса которого является адресным входом устройства, синхронизирующий вход является вторым синхронизирующим входом устройства, первый выход блока управления считыванием , соединен с вторыми информационными входами первого и второго мультиплексоров, первый и второй выходы задания режима блока управления считыванием подключены соответственно к синхронизирующим и управляющим входам первого и второго мультиплексоров, информационный вход третьего блока памяти подключен к выходу информационных разрядов первого регистра, информационный вход третьего блока памяти является третьим информационным выходом устройства, прямой и инверсный выходы триггера соединены с первыми входами первого и второго элементов И соответственно, вторые входы которых подключены к выходу третьего

II

элемента задержки, выход первого элемента задержки соединен с соответствующим входом второго элемента ИЛИ,

1644149|2

са первого и третьего блоков памяти соответственно,-информационный вход второго регистра соединен с выходом

вторые выходы первого и второго муль- , второго блока памяти, типлексоров соединены с входами адреФиг.2

f 30

Фиг.3

fj O

$

w

42

Фиг4

Фиг. 5

57

4з

82 -о

S3 -о

| Авторское свидетельство СССР , № 1374973, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-04-23—Публикация

1989-01-30—Подача