Изобретение относится к автоматике, телемеханике и вычислительной технике и может быть использовано для приема и обработки информации, передаваемой по каналам связи в безрегистровых и многорегистровых кодах.

Цель изобретения - расширение области применения устройства.

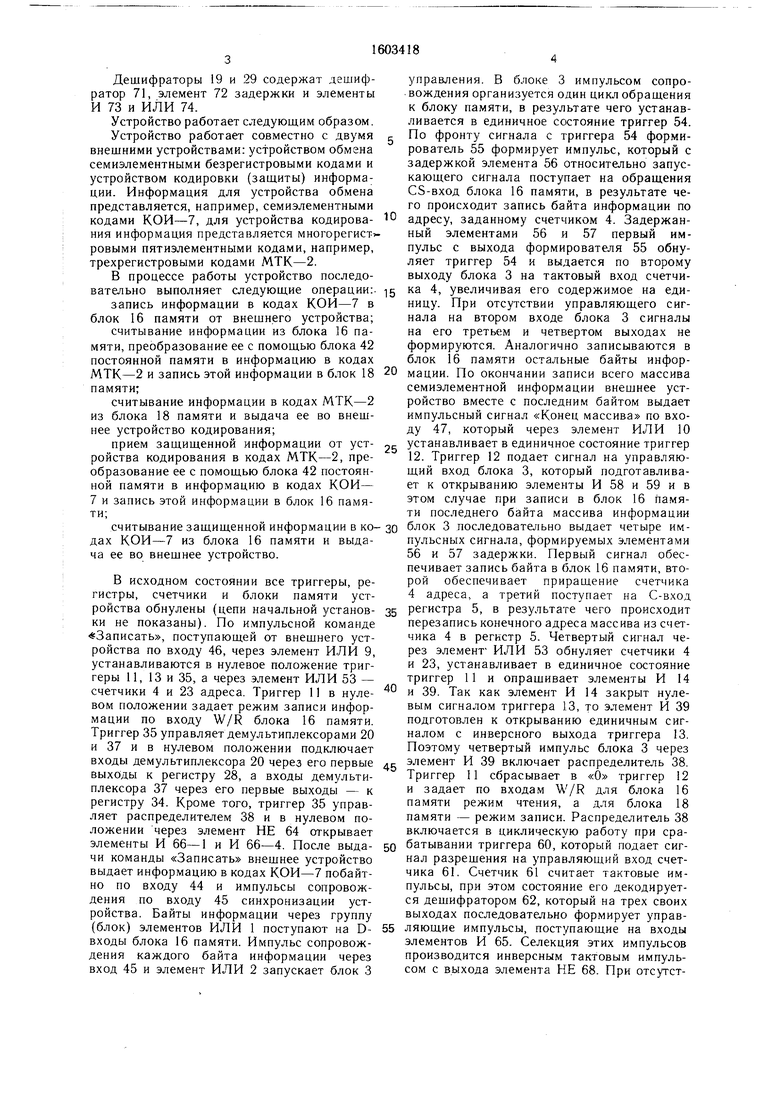

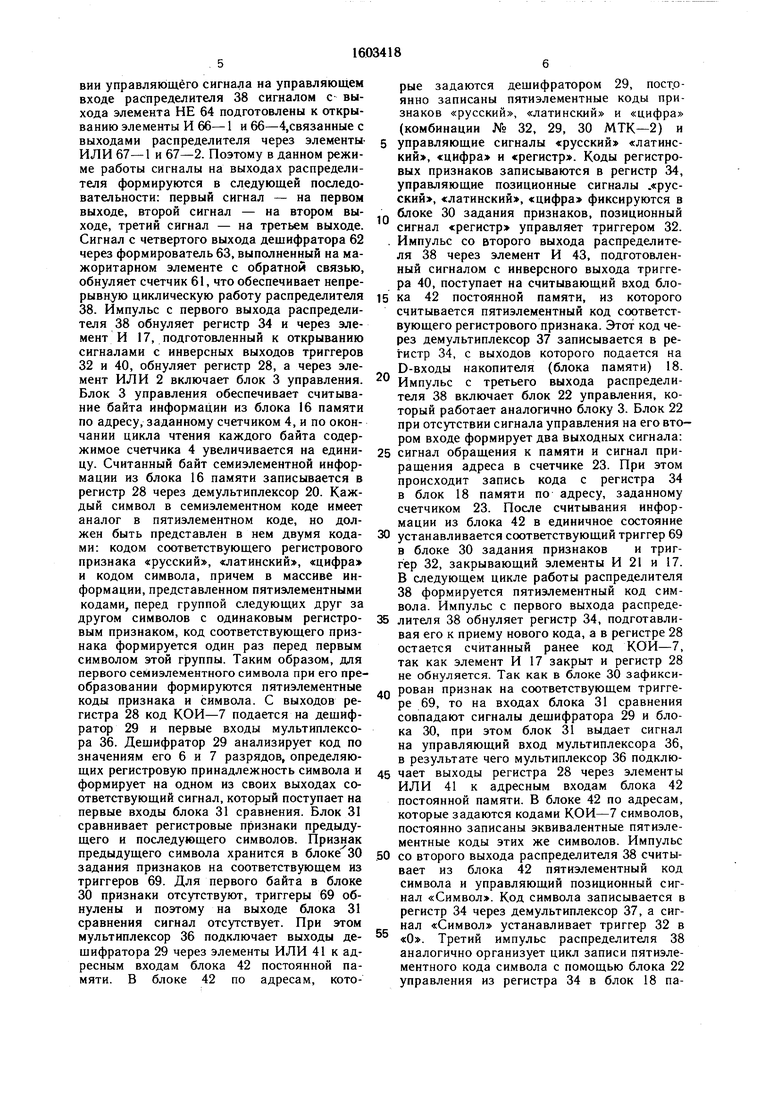

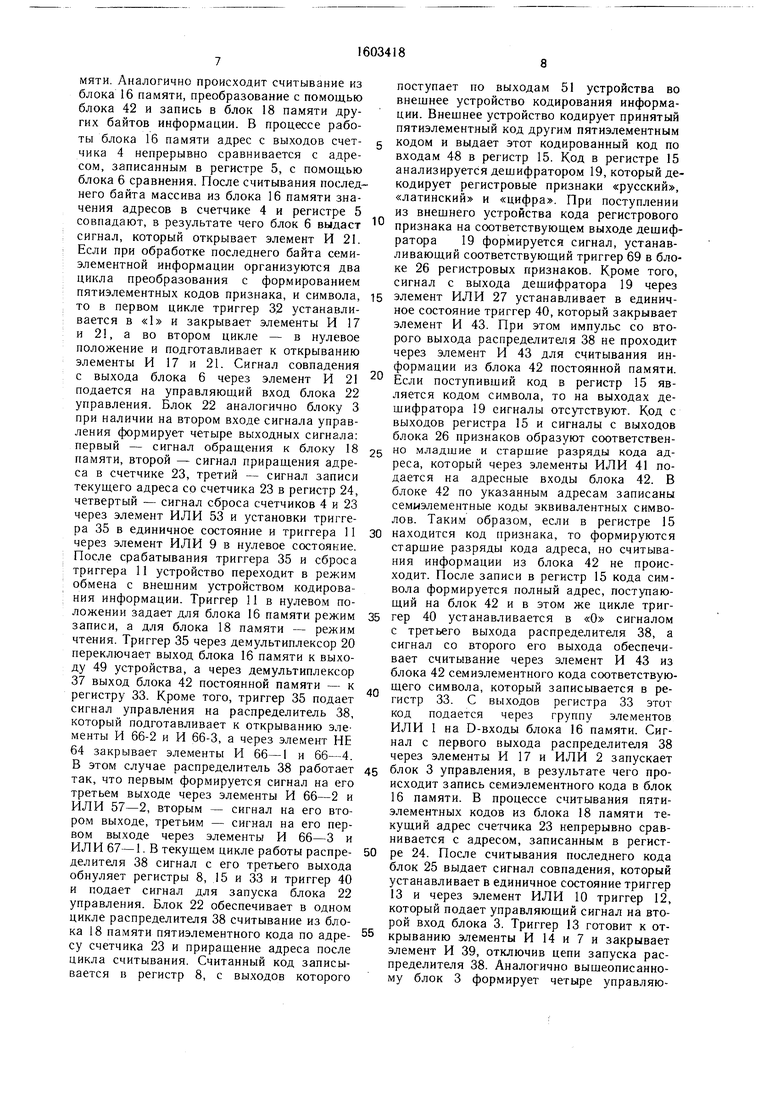

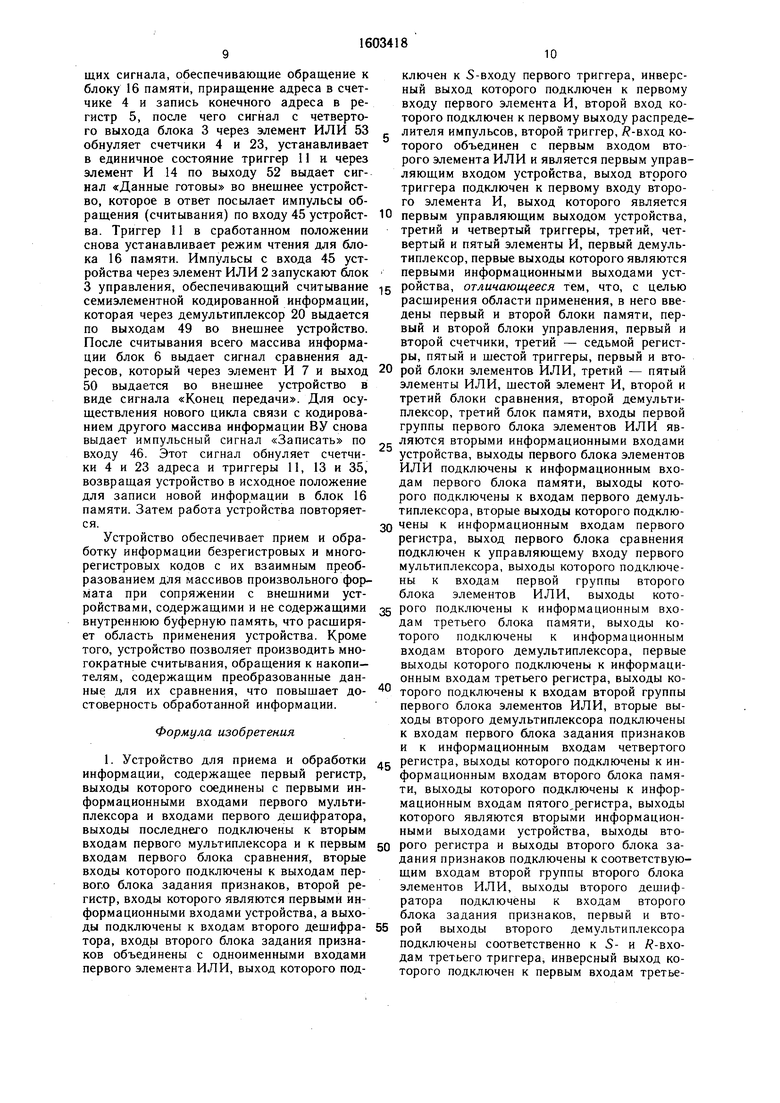

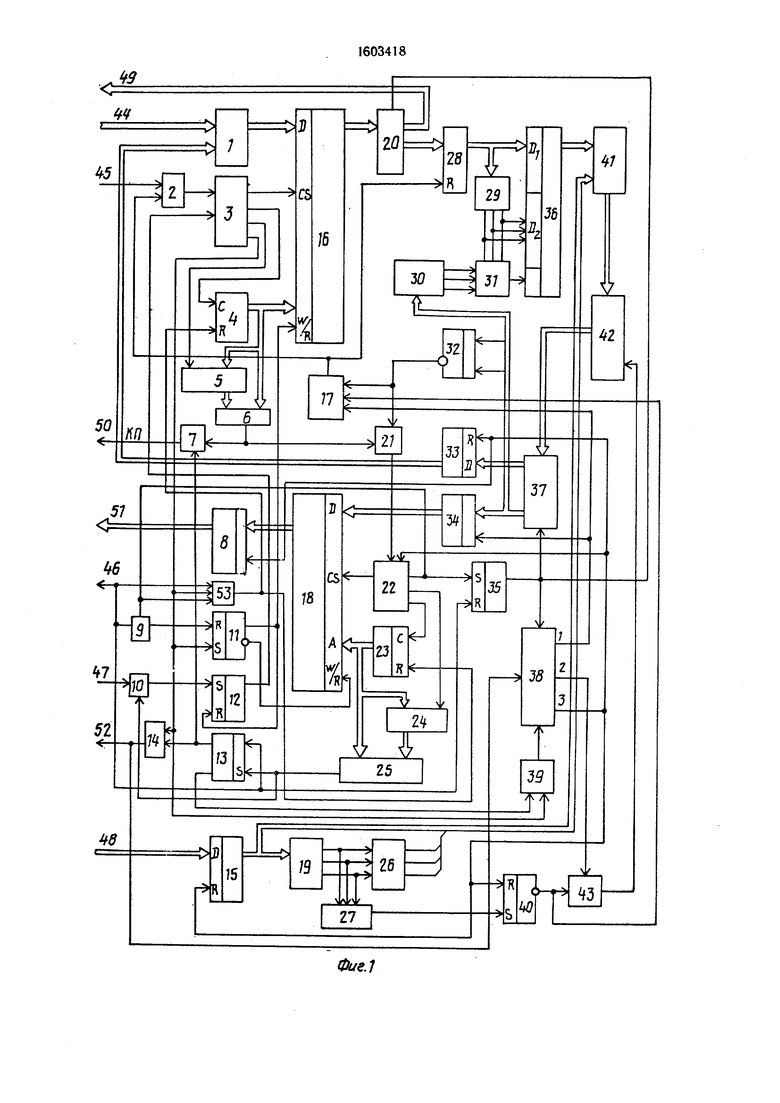

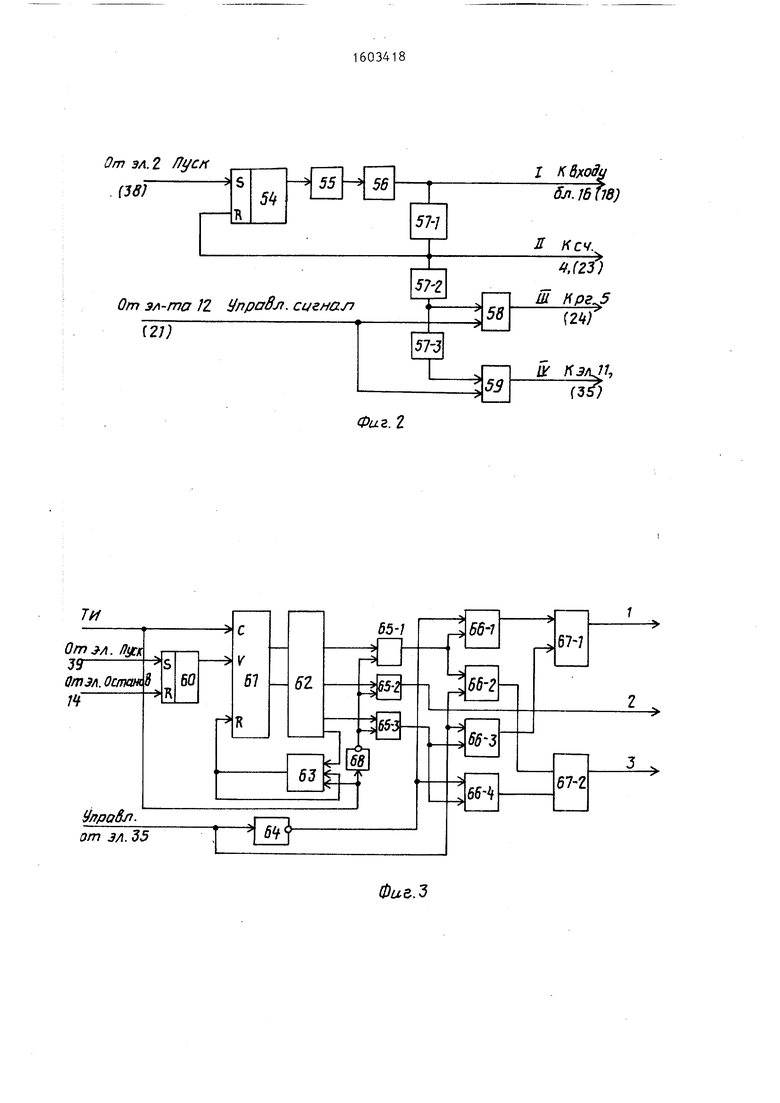

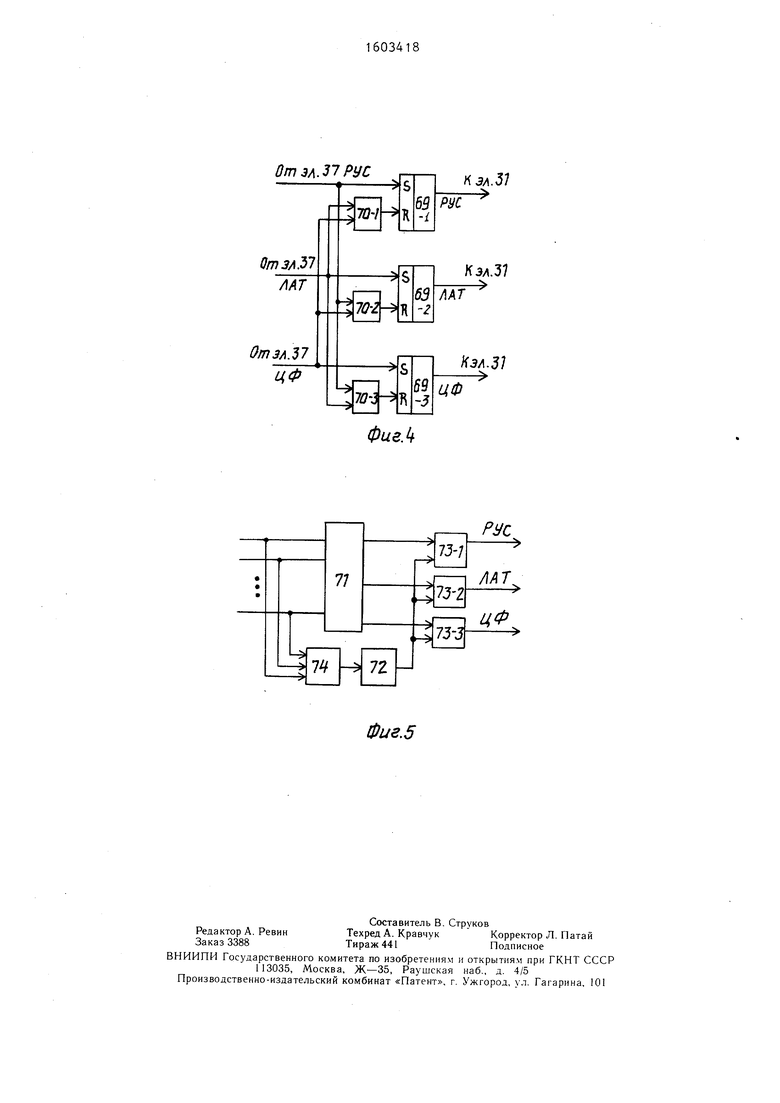

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - схема блока управления; на фиг. 3 - схема распределителя; на фиг. 4 - схема блока задания признаков; на фиг. 5 - схема де- . шифратора.

Устройство содержит блок элементов ИЛИ 1, элемент ИЛИ 2, блок 3 управления, счетчик 4, регистр 5, блок 6 сравнения, элемент И 7, регистр 8, элементы ИЛИ 9 и 10, триггеры 11 - 13, элeмeнt И 14, регистр 15, блок 16 памяти, элемент И 17, блок памяти 18, дешифратор 19, демультиплексор 20, элемент И 21, блок 22 управления, счетчик 23, регистр 24, блок 25 сравнения, блок 26 задания признаков, элемент ИЛИ 27, регистр 28, дешифратор 29, блок 30 задания

признаков, блок 31 сравнения, триггер 32, регистры 33 и 34, триггер 35, мультиплексор 36, демультиплексор 37, распределитель 38 импульсов, элемент И 39, триггер 40, блок 41 элементов ИЛИ, блок 42 постоянной памяти, элемент И 43, вход 44 семиэле- ментной безрегистровой информации, вход 45 синхронизации, вход 46 записи, вход 47 конца массива, вход 48 пятиэлементной многорегистровой информации, выход 49 семи- элементной безрегистровой информации, выход 50 конца передачи, выход 51 пятиэлементной многорегистровой информации, выход 52 готовности данных и элемент ИЛИ 53.

Блоки 3 и 22 управления содержат триггер 54, формирователь 55 импульсов, элементы 56 и 57 задержки и элементы И 58 и 59.

Распределитель 38 содержит триггер 60, счетчик 61, дешифратор 62, мажоритарный элемент 63, элементы НЕ 64, И 65, И 66, ИЛИ 67 и НЕ 68.

Блоки 26 и 30 задания признаков содержат триггеры 69 и элементы ИЛИ 70.

(Л

О5

о со

41

00

Дешифраторы 19 и 29 содержат дешиф-управления. В блоке 3 импульсом сопроратор 71, элемент 72 задержки и элементы Вождения организуется один цикл обращения

И 73 и ИЛИ 74.к блоку памяти, в результате чего устанавУстройство работает следующим образом.ливается в единичное состояние триггер 54.

Устройство работает совместно с двумя По фронту сигнала с триггера 54 формивнещними устройствами: устройством обменарователь 55 формирует импульс, который с семиэлементными безрегистровыми кодами и устройством кодировки (защиты) информа

ции. Информация для устройства обмена представляется, например, семиэлементными

вательно выполняет следующие операции: запись информации в кодах КОИ-7 в блок 16 памяти от внешнего устройства; считывание информации из блока 16 памяти, преобразование ее с помощью блока 42 постоянной памяти в информацию в кодах

задержкой элемента 56 относительно запускающего сигнала поступает на обращения CS-вход блока 16 памяти, в результате че „ ,,го происходит запись байта информации по

кодами КОИ-7, для устройства кодирова- Ю адресу, заданному счетчиком 4. Задержан- ния информация представляется многорегист ный элементами 56 и 57 первый им- ровыми пятиэлементными кодами, например, пульс с выхода формирователя 55 обну- трехрегистровыми кодами МТК-2.ляет триггер 54 и выдается по второму

В процессе работы устройство последо- выходу блока 3 на тактовый вход счетчи15 ка 4, увеличивая его содержиглое на единицу. При отсутствии управляющего сигнала на втором входе блока 3 сигналы на его третьем и четвертом выходах не формируются. Аналогично записываются в блок 16 памяти остальные байты инфорМТК-2 и запись этой информации в блок 18 20 мации. По окончании записи всего массива памяти;семиэлементной информации внешнее устсчитывание информации в кодах МТК-2 ройство вместе с последним байтом выдает из блока 18 памяти и выдача ее во внещ- импульсный сигнал «Конец массива по вхо- нее устройство кодирования;ду 47, который через элемент ИЛИ 10

прием защищенной информации от уст- jc устанавливает в единичное состояние триггер ройства кодирования в кодах МТК-2, пре-

образование ее с помощью блока 42 постоянной памяти в информацию в кодах КОИ-

7 и запись этой информации в блок 16 памяти;

считывание защищенной информации в ко-30блок 3 последовательно выдает четыре имдах КОИ-7 из блока 16 памяти и выда-пульсных сигнала, формируемых элементами

ча ее во внещнее устройство.56 и 57 задержки. Первый сигнал обеспечивает запись байта в блок 16 памяти, втоВ исходном состоянии все триггеры, ре-рой обеспечивает приращение счетчика

гистры, счетчики и блоки памяти уст-4 адреса, а третий поступает на С-вход

ройства обнулены (цепи начальной установ- 35Регистра 5, в результате чего происходит

ки не показаны). По импульсной командеперезапись конечного адреса массива из счет12. Триггер 12 подает сигнал на управляющий вход блока 3, который подготавливает к открыванию элементы И 58 и 59 и в этом случае при записи в блок 16 памяти последнего байта массива информации

«Записать, поступающей от внешнего устройства по входу 46, через элемент ИЛИ 9, устанавливаются в нулевое положение триггеры 11, 13 и 35, а через элемент ИЛИ 53 счетчики 4 и 23 адреса. Триггер 11 в нулевом положении задает режим записи информации по входу W/R блока 16 памяти. Триггер 35 управляет демультиплексорами 20 и 37 и в нулевом положении подключает

40

чика 4 в регистр 5. Четвертый сигнал через элемент ИЛИ 53 обнуляет счетчики 4 и 23, устанавливает в единичное состояние триггер 11 и опрашивает элементы И 14 и 39. Так как элемент И 14 закрыт нулевым сигналом триггера 13, то элемент И 39 подготовлен к открыванию единичным сигналом с инверсного выхода триггера 13. Поэтому четвертый импульс блока 3 через

входы демультиплексора 20 через его первые 45 элемент И 39 включает распределитель 38. выходы к регистру 28, а входы демульти- Триггер 11 сбрасывает в «О триггер 12 плексора 37 через его первые выходы - к и задает по входам W/R для блока 16 регистру 34. Кроме того, триггер 35 управ- памяти режим чтения, а для блока 18 ляет распределителем 38 и в нулевом по- памяти - режим записи. Распределитель 38 ложении через элемент НЕ 64 открывает включается в циклическую работу при сра- элементы И 66-1 и И 66-4. После выда- 50 батывании триггера 60, который подает сигнал разрешения на управляющий вход счетчика 61. Счетчик 61 считает тактовые импульсы, при этом состояние его декодируется дешифратором 62, который на трех своих выходах последовательно формирует управ(блок) элементов ИЛИ 1 поступают на D - 55 ляющие импульсы, поступающие на входы входы блока 16 памяти. Импульс сопровож- элементов И 65. Селекция этих импульсов дения каждого байта информации через производится инверсным тактовым импуль- вход 45 и элемент ИЛИ 2 запускает блок 3 сом с выхода элемента НЕ 68. При отсутстчи команды «Записать внешнее устройство выдает информацию в кодах КОИ-7 побайтно по входу 44 и импульсы сопровождения по входу 45 синхронизации устройства. Байты информации через группу

устанавливает в единичное состояние триггер

блок 3 последовательно выдает четыре им12. Триггер 12 подает сигнал на управляющий вход блока 3, который подготавливает к открыванию элементы И 58 и 59 и в этом случае при записи в блок 16 памяти последнего байта массива информации

перезапись конечного адреса массива из счет0

чика 4 в регистр 5. Четвертый сигнал через элемент ИЛИ 53 обнуляет счетчики 4 и 23, устанавливает в единичное состояние триггер 11 и опрашивает элементы И 14 и 39. Так как элемент И 14 закрыт нулевым сигналом триггера 13, то элемент И 39 подготовлен к открыванию единичным сигналом с инверсного выхода триггера 13. Поэтому четвертый импульс блока 3 через

5 элемент И 39 включает распределитель 38. Триггер 11 сбрасывает в «О триггер 12 и задает по входам W/R для блока 16 памяти режим чтения, а для блока 18 памяти - режим записи. Распределитель 38 включается в циклическую работу при сра- 0 батывании триггера 60, который подает сигнал разрешения на управляющий вход счетчика 61. Счетчик 61 считает тактовые импульсы, при этом состояние его декодируется дешифратором 62, который на трех своих выходах последовательно формирует управВИИ управляющего сигнала на управляющем входе распределителя 38 сигналом с- выхода элемента НЕ 64 подготовлены к открыванию элементы И 66- 1 и 66-4,связаиные с выходами распределителя через элементы- ИЛИ 67-1 и 67-2. Поэтому в данном режиме работы сигналы на выходах распределителя формируются в следующей последовательности: первый сигнал - на первом выходе, второй сигнал - на втором выходе, третий сигнал - на третьем выходе. Сигнал с четвертого выхода дещифратора 62 через формирователь 63, выполненный на мажоритарном элементе с обратной связью, обнуляет счетчик 61, что обеспечивает непрерывную циклическую работу распределителя 38. Импульс с первого выхода распределителя 38 обнуляет регистр 34 и через элемент И 17, подготовленный к открыванию сигналами с инверсных выходов триггеров 32 и 40, обнуляет регистр 28, а через элемент ИЛИ 2 включает блок 3 управления. Блок 3 управления обеспечивает считывание байта информации из блока 16 памяти по адресу, заданному счетчиком 4, и по окончании цикла чтения каждого байта содержимое счетчика 4 увеличивается на единицу. Считанный байт семиэлементной информации из блока 16 памяти записывается в регистр 28 через демультиплексор 20. Каждый символ в семиэлементном коде имеет аналог в пятиэлемеитном коде, но должен быть представлен в нем двумя кодами: кодом соответствующего регистрового признака «русский, «латинский, «цифра и кодом символа, причем в массиве информации, представленном пятиэлементными кодами, перед группой следующих друг за другом символов с одинаковым регистровым признаком, код соответствующего признака формируется один раз перед первым символом этой группы. Такнм образом, для первого сеМиэлементного символа при его преобразовании формируются пятиэлементные коды призиака и символа. С выходов регистра 28 код КОИ-7 подается на дещиф- ратор 29 и первые входы мультиплексора 36. Дещифратор 29 анализирует код по значениям его 6 и 7 разрядов, определяющих регистровую прииадлежность символа и формирует на одном из своих выходах соответствующий сигнал, который поступает на первые входы блока 31 сравнения. Блок 31 сравнивает регистровые признаки предыдущего и последующего символов. Признак предыдущего символа хранится в блоке ЗО задания признаков на соответствующем из триггеров 69. Для первого байта в блоке 30 признаки отсутствуют, триггеры 69 обнулены и поэтому на выходе блока 31 сравнения сигнал отсутствует. При этом мультиплексор 36 подключает выходы дещифратора 29 через элементы ИЛИ 41 к адресным входам блока 42 постоянной памяти. В блоке 42 по адресам, которые задаются дещифратором 29, постоянно записаны пятиэлементные коды признаков «русский, «латинский и «цифра (комбинации № 32, 29, 30 МТК-2) и

управляющие сигналы «русский «латинский, «цифра и «регистр. Коды регистровых признаков записываются в регистр 34, управляющие позиционные сигналы .«русский, «латинский, «цифра фиксируются в

блоке 30 задания признаков, позиционный сигнал «регистр управляет триггером 32. . Импульс со второго выхода распределителя 38 через элемент И 43, подготовленный сигиалом с инверсного выхода триггера 40, поступает на считывающий вход бло5 ка 42 постоянной памяти, из которого считывается пятиэлементный код соответствующего регистрового признака. Этот код через демультиплексор 37 записывается в регистр 34, с выходов которого подается на D-входы накопителя (блока памяти) 18. Импульс с третьего выхода распределителя 38 включает блок 22 управления, который работает аналогично блоку 3. Блок 22 при отсутствии сигнала управления на его втором входе формирует два выходных сигнала:

5 сигнал обращения к памяти и сигнал приращения адреса в счетчике 23. При этом происходит запись кода с регистра 34 в блок 18 памяти по адресу, заданному счетчиком 23. После считывания информации из блока 42 в единичное состояние

0 устанавливается соответствующий триггер 69 в блоке 30 задания признаков и триггер 32, закрывающий элементы И 21 и 17. В следующем цикле работы распределителя 38 формируется пятиэлементный код символа. Импульс с первого выхода распреде5 лителя 38 обнуляет регистр 34, подготавливая его к приему нового кода, а в регистре 28 остается считанный ранее код КОИ-7, так как элемент И 17 закрыт и регистр 28 не обнуляется. Так как в блоке 30 зафиксиQ рован признак на соответствующем триггере 69, то на входах блока 31 сравнения совпадают сигналы дещифратора 29 и блока 30, при этом блок 31 выдает сигнал на управляющий вход мультиплексора 36, в результате чего мультиплексор 36 подклю5 чает выходы регистра 28 через элементы ИЛИ 41 к адресным входам блока 42 постоянной памяти. В блоке 42 по адресам, которые задаются кодами КОИ-7 символов, постоянно записаны эквивалентные пятиэлементные коды этих же символов. Импульс

0 со второго выхода распределителя 38 считывает из блока 42 пятиэлементный код символа и управляющий позиционный сигнал «Символ. Код символа записывается в регистр 34 через демультиплексор 37, а сигнал «Символ устанавливает триггер 32 в «О. Третий импульс распределителя 38 аналогично организует цикл записи пятиэле- ментного кода символа с помощью блока 22 управления из регистра 34 в блок 18 памяти. Аналогично происходит считывание из блока 16 памяти, преобразование с помощью блока 42 и запись в блок 18 памяти других байтов информации. В процессе работы блока 16 памяти адрес с выходов счет- чика 4 непрерывно сравнивается с адресом, записанным в регистре 5, с помощью блока 6 сравнения. После считывания последнего байта массива из блока 16 памяти значения адресов в счетчике 4 и регистре 5 совпадают, в результате чего блок 6 выдаст сигнал, который открывает элемент И 21. Если при обработке последнего байта семи- элементной информации организуются два цикла преобразования с формированием пятиэлементных кодов признака, и символа, то в первом цикле триггер 3.2 устанавливается в «1 и закрывает элементы И 17 и 21, а во втором цикле - в нулевое положение и подготавливает к открыванию элементы И 17 и 21. Сигнал совпадения с выхода блока 6 через элемент И 21 подается на управляющий вход блока 22 управления. Блок 22 аналогично блоку 3 при наличии на втором входе сигнала управления формирует четыре выходных сигнала: первый - сигнал обращения к блоку 18 памяти, второй - сигнал приращения адреса в счетчике 23, третий - сигнал записи текущего адреса со счетчика 23 в регистр 24, четвертый - сигнал сброса счетчиков 4 и 23 через элемент ИЛИ 53 и установки триггера 35 в единичное состояние и триггера 11 через элемент ИЛИ 9 в нулевое состояние. После срабатывания триггера 35 и сброса триггера 11 устройство переходит в режим обмена с внещним устройством кодирования информации. Триггер 11 в нулевом положении задает для блока 16 памяти режим записи, а для блока 18 памяти - режим чтения. Триггер 35 через демультиплексор 20 переключает выход блока 16 памяти к выходу 49 устройства, а через демультиплексор

37 выход блока 42 постоянной памятик

регистру 33. Кроме того, триггер 35 подает сигнал управления на распределитель 38, который подготавливает к открыванию элементы И 66-2 и И 66-3, а через элемент НЕ 64 закрывает элементы И 66-1 и . В этом случае распределитель 38 работает так, что первым формируется сигнал на его третьем выходе через элементы И 66--2 и ИЛИ 57-2, вторым - сигнал на его втором выходе, третьим - сигнал на его первом выходе через элементы И 66-3 и ИЛИ 67-1. В текущем цикле работы распре- делителя 38 сигнал с его третьего выхода обнуляет регистры 8, 15 и 33 и триггер 40 и подает сигнал для запуска блока 22 управления. Блок 22 обеспечивает в одном цикле распределителя 38 считывание из блока 18 памяти пятиэлементного кода по адре- су счетчика 23 и приращение адреса после цикла считывания. Считанный код записывается в регистр 8, с выходов которого

поступает по выходам 51 устройства во внещнее устройство кодирования информации. Внешнее устройство кодирует принятый пятиэлементный код другим пятиэлементным кодом и выдает этот кодированный код по входам 48 в регистр 15. Код в регистре 15 анализируется дешифратором 19, который декодирует регистровые признаки «русский, «латинский и «цифра. При поступлении из внешнего устройства кода регистрового признака на соответствующем выходе дешифратора 19 формируется сигнал, устанавливающий соответствующий триггер 69 в блоке 26 регистровых признаков. Кроме того, сигнал с выхода дешифратора 19 через элемент ИЛИ 27 устанавливает в единичное состояние триггер 40, который закрывает элемент И 43. При этом импульс со второго выхода распределителя 38 не проходит через элемент И 43 для считывания информации из блока 42 постоянной памяти. Если поступивший код в регистр 15 является кодом символа, то на выходах дешифратора 19 сигналы отсутствуют. Код с выходов регистра 15 и сигналы с выходов блока 26 признаков образуют соответственно младшие и старшие разряды кода адреса, который через элементы ИЛИ 41 подается на адресные входы блока 42. В блоке 42 по указанным адресам записаны семмэлементные коды эквивалентных символов. Таким образом, если в регистре 15 находится код признака, то формируются старшие разряды кода адреса, но считывания информации из блока 42 не происходит. После записи в регистр 15 кода символа формируется полный адрес, поступающий на блок 42 и в этом же цикле триггер 40 устанавливается в «О сигналом с третьего выхода распределителя 38, а сигнал со второго его выхода обеспечивает считывание через элемент И 43 из блока 42 семиэлементного кода соответствующего символа, который записывается в регистр 33. С выходов регистра 33 этот код подается через группу элементов ИЛИ 1 на D-входы блока 16 памяти. Сигнал с первого выхода распределителя 38 через элементы И 17 и ИЛИ 2 запускает блок 3 управления, в результате чего происходит запись семиэлементного кода в блок 16 памяти. В процессе считывания пятиэлементных кодов из блока 18 памяти текущий адрес счетчика 23 непрерывно сравнивается с адресом, записанным в регистре 24. После считывания последнего кода блок 25 выдает сигнал совпадения, который устанавливает в единичное состояние триггер 13 и через элемент ИЛИ 10 триггер 12, который подает управляющий сигнал на второй вход блока 3. Триггер 13 готовит к открыванию элементы И 14 и 7 и закрывает элемент И 39, отключив цепи запуска распределителя 38. Аналогично выщеописанно- му блок 3 формирует четыре управляющих сигнала, обеспечивающие обращение к блоку 16 памяти, приращение адреса в счетчике 4 и запись конечного адреса в регистр 5, после чего сигнал с четвертого выхода блока 3 через элемент ИЛИ 53 обнуляет счетчики 4 и 23, устанавливает в единичное состояние триггер 11 и через элемент И 14 по выходу 52 выдает сигнал «Данные готовы во внещнее устройство, которое в ответ посылает импульсы обращения (считывания) по входу 45 устройст- ва. Триггер 11 в сработанном положении снова устанавливает режим чтения для блока 16 памяти. Импульсы с входа 45 устройства через элемент ИЛИ 2 запускают блок 3 управления, обеспечивающий считывание семиэлементной кодированной информации, которая через демультиплексор 20 выдается по выходам 49 во внешнее устройство. После считывания всего массива информации блок 6 выдает сигнал сравнения адресов, который через элемент И 7 и выход 50 выдается во внешнее устройство в виде сигнала «Конец передачи. Для осуществления нового цикла связи с кодированием другого массива информации ВУ снова выдает импульсный сигнал «Записать по входу 46. Этот сигнал обнуляет счетчики 4 и 23 адреса и триггеры 11, 13 и 35, возвращая устройство в исходное положение для записи новой информации в блок 16 памяти. Затем работа устройства повторяется.

Устройство обеспечивает прием и обработку информации безрегистровых и многорегистровых кодов с их взаимным преобразованием для массивов произвольного формата при сопряжении с внешними устройствами, содержащими и не содержащими внутреннюю буферную память, что расширяет область применения устройства. Кроме того, устройство позволяет производить многократные считывания, обращения к накопителям, содержащим преобразованные данные для их сравнения, что повышает до- стоверность обработанной информации.

Формула изобретения

1. Устройство для приема и обработки информации, содержащее первый регистр, выходы которого соединены с первыми информационными входами первого мультиплексора и входами первого дешифратора, выходы последнего подключены к вторым входам первого мультиплексора и к первым входам первого блока сравнения, вторые входы которого подключены к выходам первого блока задания признаков, второй регистр, входы которого являются первыми информационными входами устройства, а выходы подключены к входам второго дешифра- тора, входь второго блока задания признаков объединены с одноименными входами первого элемента ИЛИ, выход которого подключен к 5-входу первого триггера, инверсный выход которого подключен к первому входу первого элемента И, второй вход которого подключен к первому выходу распределителя импульсов, второй триггер, / -вход которого объединен с первым входом второго элемента ИЛИ и является первым управляющим входом устройства, выход второго триггера подключен к первому входу второго элемента И, выход которого является первым управляющим выходом устройства, третий и четвертый триггеры, третий, четвертый и пятый элементы И, первый демультиплексор, первые выходы которого являются первыми информационными выходами устройства, отличающееся тем, что, с целью расширения области применения, в него введены первый и второй блоки памяти, первый и второй блоки управления, первый и второй счетчики, третий - седьмой регистры, пятый и шестой триггеры, первый и второй блоки элементов ИЛИ, третий - пятый элементы ИЛИ, шестой элемент И, второй и третий блоки сравнения, второй демультиплексор, третий блок памяти, входы первой группы первого блока элементов ИЛИ являются вторыми информационными входами устройства, выходы первого блока элементов ИЛИ подключены к информационным входам первого блока памяти, выходы которого подключены к входам первого демуль- типлексора, вторые выходы которого подключены к информационным входам первого регистра, выход первого блока сравнения подключен к управляющему входу первого мультиплексора, выходы которого подключены к входам первой группы второго блока элементов ИЛИ, выходы которого подключены к информационным входам третьего блока памяти, выходы которого подключены к информационным входам второго демультиплексора, первые выходы которого подключены к информационным входам третьего регистра, выходы которого подключены к входам второй группы первого блока элементов ИЛИ, вторые выходы второго демультиплексора подключены к входам первого блока задания признаков и к информационным входам четвертого регистра, выходы которого подключены к информационным входам второго блока памяти, выходы которого подключены к информационным входам пятого,регистра, выходы которого являются вторыми информационными выходами устройства, выходы второго регистра и выходы второго блока задания признаков подключены к соответствующим входам второй группы второго блока элементов ИЛИ, выходы второго дешифратора подключены к входам второго блока задания признаков, первый и второй выходы второго демультиплексора подключены соответственно к S- и R-EXO- дам третьего триггера, инверсный выход которого подключен к первым входам третье

го и четвертого элементов И, выход последнего подключен к управляющему входу первого регистра и к первому входу третьего элемента ИЛИ, второй вход которого является синхронизирующим входом устройства, выход третьего элемента ИЛИ подключен к первому входу первого блока управления, с первого по четвертый выходы которого подключены соответственно к тактовому входу первого блока памяти, к счетному входу первого счетчика, к тактовому входу щестого регистра, к объединенным первому входу четвертого элемента ИЛИ, S- входу четвертого триггера, второму входу второго элемента И и первому входу пятого элемента И, выходы первого счетчика под- ключены к адресным входам первого блока памяти, первым входам второго блока сравнения и к информационным входам шестого регистра, выходы которого подключены к вторым входам второго блока сравнения, выход которого подключен к первому входу щестого элемента И и второму входу третьего элемента И, выход которого подключен к первому входу второго блока управления, с первого по четвертый выходы которого подключены соответственно к тактовому вхо- ду второго блока памяти, счетному входу второго счетчика, к тактовому входу седьмого регистра, к объединенным 5-входу пятого триггера и вторым входам второго и четвертого элементов ИЛИ, / -вход пятого триггера и третий вход четвертого эле- мента ИЛИ объединены с первым вхо- дом второго элемента ИЛИ, выход которого подключен к / -входу четвертого триггера, выход которого подключен к управляющему входу первого блока памяти и -входу щестого триггера, инверсный выход четвертого триггера подключен к управляющему входу второго блока памяти, выходы второго счетчика подключены к адресным входам второго блока памяти, к первым входам третьего блока сравнения и к информационным входам седьмого регистра, вы- ходы которого подключены к вторым входам третьего блока сравнения, выход которого подключен к первому входу пятого элемента ИЛИ и 5-входу второго триггера, выход которого подключен к второму входу щестого элемента И, выход которого явля0

0 о 5

ется вторым управляющим выходом устройства, выход пятого триггера подключен к управляющим входам первого и второго де- мультиплексоров и к первому входу распределителя импульсов, второй и третий выходы последнего, подключены соответственно к объединенным управляющему входу четвертого регистра и второму входу четвертого элемента И, объединенным управляющим входам второго, третьего и пятого регистров, / -входу первого триггера и второму входу второго блока управления, первый вход первого элемента И объединен с третьим входом четвертого элемента И, инверсный выход второго триггера подключен к второму входу пятого элемента И, выход которого подключен к второму входу распределителя импульсов, третий вход которого подключен к выходу второго элемента И, второй вход пятого элемента ИЛИ являeтdя вторым управляющим входом устройства, выход пятого элемента ИЛИ подключен к S-входу щестого триггера, выход которого подключен к второму входу первого блока управления, выход четвертого элемента ИЛИ подключен к установочным входам первого и второго счетчиков.

2. Устройство по п. 1, отличающееся тем, что каждый блок управления содержит триггер, формирователь импульсов, элементы задержки и элементы И, S-вход триггера является первым входом блока управления, выход триггера через формирователь импульсов подключен к входу первого элемента задержки, выход которого подключен к входу второго элемента задержки и является первым выходом блока управления, выход второго блока задержки подключен к R- входу триггера, к входу третьего элемента задержки и является вторым выходом блока управления, выход третьего элемента задержки подключен к первому входу перво- . го элемента и непосредственно и через четвертый элемент задержки к первому входу второго элемента И, вторые входы первого и второго элементов И объединены и являются вторым входом блока управления, выходы первого и второго элементов И являются соответственно третьим и четвертым выходами блока управления.

От ЗА. 2 /7yc/i

От эл-та 12 УлраВл. сигнал

(21)

г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обработки информации | 1987 |

|

SU1444856A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1374279A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для ввода и вывода информации | 1990 |

|

SU1709295A1 |

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

Изобретение относится к автоматике, телемеханике и вычислительной технике и может быть использовано для приема и обработки информации. Цель изобретения - расширение области применения. Устройство содержит блоки элементов ИЛИ, элементы ИЛИ, блоки управления, счетчики, регистры, блоки сравнения, элементы И, триггеры, блоки памяти, дешифраторы, демультиплексоры, блоки задания признаков, мультиплексор, распределитель, дешифратор 29. Устройство позволяет производить прием и обработку информации безрегистровых и многорегистровых кодов с их взаимным преобразованием для массивов произвольного формата. 1 з.п. ф-лы, 5 ил.

Фиг.г

Фиг..

ФиеЛ

Фиг.5

| Устройство для приема и обработки информации | 1987 |

|

SU1444856A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1990-10-30—Публикация

1989-01-30—Подача