1

(61) 1247906

(21)4704945/24

(22)27.04.89

(46) 23.04.91. Ниш. I 15

(-71) Ленинградский политехнический

институт им. М.И.Калинина

(72) А.И.Таджибаев, С.В.Чурсин

и Ю.А.Ротачев

(53)681.3(088.8)

(56)Авторское свидетельство СССР У 1247906, кл. G 06 G 7/62, 1986.

(54)УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧНОЙ СОСТАВЛЯЮЩЕЙ ТРЕХФАЗНЫХ ЦЕПЕЙ

(57)Изобретение относится к вычислительной технике и может быть использовано для автоматизации контроля режимов трехфазных электрических цепей. Цель изобретения - повышение точности вычисления. Устройство содержит блоки 1 и 2 вычисления разности фазных величин, выполненные в виде дифференциальных усилителей, первый сумматор 3, основную 4 и дополнительную 5 фазосдвигающие цепи, второй сумматор 6, блок задержки 7, резонансный усилитель 8, фазовращатель 9, преобразователь фаза-код 10, умножающий цифроаналоговый пребразо- ватель 11 и блок регистрации 12. Преобразователь фаза-код 10 состоит из фазового детектора 13, первого 14 и второго 15 элементов задержки, генератора стабильной частоты 16, счетчика 17 импульсов и регистра памяти 18. Достижение поставленной цели обеспечено благодаря введению в уст ройство дополнительной фазосдвигаю- щей цепи, умножающего цифроаналого- вого преобразователя и преобразователя фаза-код. 1 ил.

1

W

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемое фазосдвигающее устройство | 1980 |

|

SU907460A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2004 |

|

RU2262190C1 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| УСТРОЙСТВО МОНИТОРИНГА ВЫСОКОВОЛЬТНЫХ ВВОДОВ И СИГНАЛИЗАЦИИ О СОСТОЯНИИ ИХ ИЗОЛЯЦИИ | 2006 |

|

RU2328009C1 |

| Система связи с относительной фазовой и фазоимпульсной модуляцией | 1987 |

|

SU1559421A1 |

| Устройство для моделирования сигнала короткого замыкания | 1986 |

|

SU1309055A1 |

| Способ защиты от повышения напряжения трехфазной линии электропередачи | 1991 |

|

SU1781762A1 |

| Устройство для измерения параметров трехфазной сети | 1985 |

|

SU1307396A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ РЫХЛОСТИ ЭПИТЕЛИАЛЬНОЙ ТКАНИ КИШЕЧНО-ЖЕЛУДОЧНОГО ТРАКТА | 1991 |

|

RU2026004C1 |

Изобретение относится к вычислительной технике и может быть использовано для автоматизации контроля режимов трехфазных электрических цепей.

Цель изобретения - повышение точности вычисления.

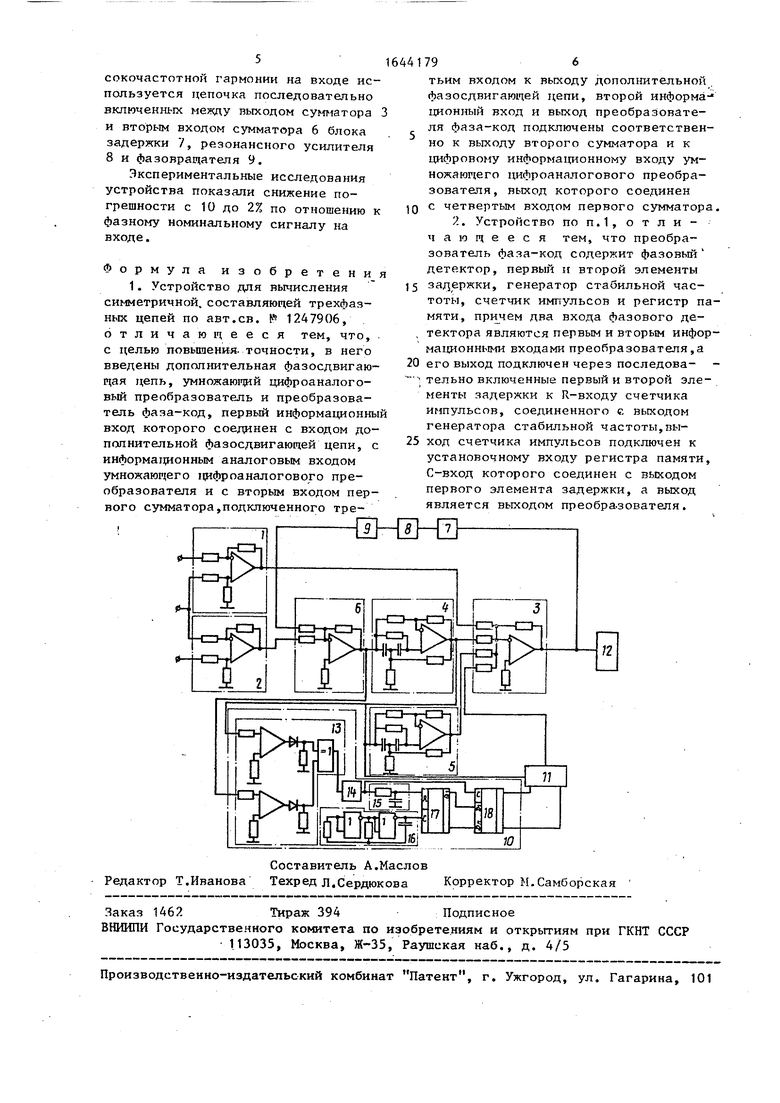

На чертеже представлена схема устройства для вычисления симметричной составляющей трехфазных цепей (например, обратной последовательности) .

Устройство содержит блоки 1 и 2 вычисления разности фазных величин,

выполненные в виде дифференциальных усилителей, первый сумматор 3, основную 4 и дополнительную 5 фаэо- сдвигающие цепи, второй сумматор 6, блок задержки 7, резонансный усилитель 8, фазовращатель 9, преобразователь фаза-код 10, умножающий цифроаналоговый преобразователь (НАЛ) 11 и блок регистрации 12.

Преобразователь фаза-код 10 состоит из фазового детектора 13,первого 14 и второго 15 элементов задержки генератора стабильной частоО54 Јь

ч|

rf

ГЧ

ты 16, счетчика 17 импульсов и регистра памяти 18.

Устройство работает следующим образом.

Напряжение II, с выхода блока 1 поступает непосредственно на первый вход сумматора 3, а напряжение Ц- с выхода блока 2 - на второй вход того же сумматора через фазосдвигаю- щую цепь 4. Введение дополнительной фазосдвигающей цепи 5 позволяет путем изменения коэффициента передачи по четвертому входу сумматора 3 обеспечить на его выходе нулевой уро вень сигнала при отклонении частоты от номинальной. В комплексной форме можно записать

UZ U1 + U2 e

Ю „Л -J5T«60

+ U4 е

-)&240

Напряжение на четвертом входе сумматора 3 равно

Ufc-Ц-М0,

где U - напряжение на выходе фа-

зосдвигающей цепи 4; М - коэффициент деления умножающего ЦАП 11.

При этом

Л

горА ггн

где Ј фд СО Alf длительность импульса нулевого уровня на ззыходе фазового детектора 13; ДСр - сдвиг по фазе сигналов

на его входе;

СО - угловая частота контролируемого сигнала; f r H - частота следования им-

пульсов генератора 16; К - коэффициент деления счетчика 17.

При номинальной частоте на входах фазового детектора 13 сигналы сдвину ты по фазе на угол &(|)н , и на его выходе формируется сигнал нулевого уроня длительностью Јц. Этот сигнал через первый элемент задержки 14 подается на С-вход регистра памяти 18 и дополнительно через второй элемент задержки 15 - на R-вход счетчика импульсов 17. При этом код MJJ на выходе счетчика импульсов 17 соотЮ15

0

5

0

35

40

45

сп „

ветствует величине t . Второй элемент задержки 15 производит задержку обнуления счетчика импульсов 17, что позволяет регистру памяти 18 надежно считывать код MD с выхода счетчика 17. Код М.р запоминается регистром памяти 18 и подается на цифровой вход ЦАП 11, на выходе которого формируется U.

При отклонении частоты от номинальной и симметрии напряжений на входе блоков J и 2 изменяется фаза сигналов на втором и третьем входах сумматора 3, а также фаза сигналов на входах фазового детектора 13, что приводит к появлению на его выходе сигнала нулевого уровня длительностью С Ји. Этому сигналу будет соответствовать другое значение коэффициентов: К на выходе счетчика 17, И на выходе регистра памяти 18 и соответственно новое значение напряжения U на четвертом входе сумматора 3, что позволяет компенсировать отклонение напряжений на втором и третьем входах сумматора 3 и тем самым поддерживать нулевой уровень напряжения на его выходе.

Отличительной особенностью преобразователя фаза-код является то, что в него введены второй элемент задержки импульсов 15, задерживающий обнуление счетчика 17 и позво- . ляющий тем самым регистру памяти 18 надежно считать показания счетчика 17, и первый элемент задержки 14, позволяющий отстроиться от переходных процессов в фазосдвигающих цепях 4 и 5.

При возникновении несимметрии на входах блоков 1 и 2 появляется отклонение фазы напряжений на втором и третьем входах сумматора 3. Преобразователь фаза-код 10 из-за наличия первого элемента задержки 14 не успевает скомпенсировать это отклонение, и на выходе сумматора 3 появляется сигнал, пропорциональ- ный симметричной составляющей обратной последовательности, который фиксируется блоком регистрации 12.

При необходимости фиксации симметричной составляющей прямой последовательности необходимо поменять местами два напряжения на входах блоков 1 и 2.

Для подавления трансформированной погрешности из-за наличия высокочастотной гармонии на входе используется цепочка последовательно включенных между выходом сумматора 3 и вторым входом сумматора 6 блока задержки 7, резонансного усилителя 8 и фазовращателя 9.

Экспериментальные исследования устройства показали снижение погрешности с 10 до 2% по отношению к фазному номинальному сигналу на входе.

Формула изобретения

тьим входом к выходу дополнительной фазосдвигающей цепи, второй информа- ционный вход и выход преобразователя фаза-код подключены соответственно к выходу второго сумматора и к цифровому информационному входу умножающего цифроаналогового преобразователя, выход которого соединен с четвертым входом первого сумматора,

).. Устройство по п.отличающееся тем, что преобразователь фаза-код содержит фазовый детектор, первый и второй элементы

задержки, генератор стабильной частоты, счетчик импульсов и регистр памяти, причем два входа фазового детектора являются первым и вторым информационными входами преобразователя,а

его выход подключен через последова тельно включенные первый и второй элементы задержки к R-входу счетчика импульсов, соединенного к. выходом генератора стабильной частоты,вы-

ход счетчика импульсов подключен к установочному входу регистра памяти, С-вход которого соединен с выходом первого элемента задержки, а выход является выходом преобразователя.

Авторы

Даты

1991-04-23—Публикация

1989-04-27—Подача