Изобретение относится к радиотехнике, в частности к технике цифрового вычислительного синтеза частот, и может быть использовано для формирования сетки частот в радиопередающих и радиоприемных устройствах, а также в устройствах синхронизации различного применения.

Известен цифровой синтезатор частот (Техника средств связи, серия ТРС, выпуск 9, 1983 г., с.66-71), содержащий последовательно соединенные накопитель кода, информационный вход которого соединен с входной шиной кода установки частоты, тактовый вход - с шиной опорного сигнала, фазосдвигающий сумматор, первый вход которого соединен с выходом накопителя кода, второй вход - с входной шиной кода установки фазы, постоянное запоминающее устройство, вход которого соединен с выходом фазосдвигающего сумматора, цифроаналоговый преобразователь, вход которого соединен с выходом постоянного запоминающего устройства, и фильтр низких частот, вход которого соединен с выходом цифроаналогового преобразователя, а выход - с выходной шиной устройства.

Недостатком данного цифрового синтезатора частот является ограниченный со стороны высоких частот диапазон синтезируемых колебаний. В известном синтезаторе частот максимальная выходная частота ограничена быстродействием накопителя кодов, поскольку код на выходе накопителя изменяется с тактовой частотой, равной частоте опорного (тактового) генератора f0.

Наиболее близким к предлагаемому изобретению является цифровой синтезатор частот (патент SU №1689937 А1), содержащий накопитель кода, блок памяти амплитуд, цифроаналоговый преобразователь, фильтр низких частот, выходную шину устройства, опорный генератор, блок синхронизации устройства, коммутатор, умножитель, N-1 блоков фазового сдвига, N регистров и N фазосдвигающих сумматоров, где N - число каналов синтезатора, входную шину кода установки частоты и входную шину формирования фазоманипулированного сигнала, причем входная шина кода установки частоты синтезатора подключена к входам кода установки частоты N-1 блоков фазового сдвига и к входу умножителя, выход которого подключен к входу накопителя кодов, выход которого подключен к информационному входу регистра первого канала и к входам кода фазы N-1 блоков фазового сдвига, выходы N-1 блоков фазового сдвига подключены к соответствующим информационным входам регистров с второго по N-ый, выходы регистров с 1-го по N-ый подключены к вторым входам соответствующих фазосдвигающих сумматоров, входная шина кода формирования фазоманипулированного сигнала синтезатора подключена к первому входу фазосдвигающих сумматоров, выходы которых подключены к соответствующим информационным входам коммутатора, выход опорного генератора подключен к входу блока синхронизации, первый выход которого подключен к входу синхронизации накопителя кода и входам синхронизации регистров, а группа выходов блока синхронизации подключена к управляющим входам коммутатора, выход которого подключен к входу блока памяти амплитуд, выход которого подключен к выходу синтезатора.

В данном N-канальном синтезаторе удается обеспечить время формирования кодов в каждом блоке фазового сдвига равное, N·T0, T0=1/f0, a тактовая частота накопителя кодов понижается в N раз и становится равной f0/N, что создает предпосылки к увеличению выходной частоты синтезатора в N раз за счет повышения частоты синхронизации устройства f0 при сохранении тактовой частоты работы накопителя кодов.

Однако недостатком данного синтезатора являются крайне жесткие требования к быстродействию фазосдвигающего сумматора первого канала, искажение формы синтезируемого сигнала и, как следствие, ухудшение его спектральной чистоты. В конце цикла синтеза коммутатор передает код выборки с выхода фазосдвигающего сумматора N-го канала на вход блока памяти амплитуд, а блок памяти амплитуд формирует код амплитуды, в соответствии с которым цифроаналоговый преобразователь формирует уровень синтезируемого сигнала. Далее блок синхронизации устройства переходит к новому циклу синтеза, для чего формирует на первом выходе тактовый импульс, по которому новые коды фаз записываются в регистры N каналов синтезатора и поступают на входы N фазосдвигающих сумматоров, которые начинают вычислять новые значения N кодов выборки. Одновременно с этим блок синхронизации устройства формирует сигналы управления коммутатором, по которым коммутатор на время Т0 коммутирует выход фазосдвигающего сумматора первого канала на вход блока памяти амплитуд. При этом на время выполнения операции суммирования T∑ в фазосдвигающем сумматоре первого канала на входе и выходе блока памяти амплитуд возникают неверные коды, а, в конечном итоге, сигнал на выходе цифроаналогового преобразователя в течение времени T∑ будет иметь ложный уровень (выброс) и только в течение времени (Т0-Т∑) - верное значение. Далее, через время Т0, 2Т0,...(N-1)T0 после начала цикла синтеза, выходы фазосдвигающих сумматоров со второго по N-ый каналов, уже завершивших операцию суммирования, с помощью коммутатора последовательно подключаются к входу блока памяти амплитуд, вследствие чего цифроаналоговый преобразователь сформирует соответствующую последовательность уровней синтезируемого сигнала без ложных выбросов и задержек. Так как T∑ сопоставима с величиной Т0, подавление фильтром низких частот искажений выходного сигнала цифроаналогового преобразователя на первом такте цикла синтеза неэффективно, что приводит к существенному искажению выходного сигнала синтезатора и ухудшению его спектральных характеристик.

Кроме того, выполнение условия T∑≪Т0, в силу конечного значения T∑, определенного современными схемотехническими и технологическими возможностями, ограничивает верхнее значение тактовой частоты f0, диапазон синтезируемых колебаний со стороны высоких частот и, как следствие, быстродействие устройства в целом.

Изобретением решается задача повышения спектральной чистоты выходного сигнала, синтезируемого устройством, при снижении требований к быстродействию фазосдвигающих сумматоров.

Для достижения этого технического результата в цифровой синтезатор частот, содержащий накопитель кода, блок памяти амплитуд, цифроаналоговый преобразователь, фильтр низких частот, выходную шину устройства, опорный генератор, блок синхронизации устройства, коммутатор, умножитель, входную шину кода установки частоты, входную шину кода формирования фазоманипулированного сигнала, N-1 блоков фазового сдвига, N фазосдвигающих сумматоров и N регистров, где N - число каналов синтезатора, причем входная шина кода установки частоты синтезатора подключена к входам кода установки частоты N-1 блоков фазового сдвига и к входу умножителя, выход которого подключен к входу накопителя кодов, выход которого подключен к информационному входу регистра первого канала и к входам кода фазы N-1 блоков фазового сдвига, выходы N-1 блоков фазового сдвига подключены к соответствующим информационным входам регистров с второго по N-ый, выходы регистров с 1-го по N-ый подключены к вторым входам соответствующих фазосдвигающих сумматоров, входная шина кода формирования фазоманипулированного сигнала синтезатора подключена к первому входу фазосдвигающих сумматоров, выходы которых подключены к соответствующим информационным входам коммутатора, выход опорного генератора подключен к входу блока синхронизации, первый выход которого подключен к входу синхронизации накопителя кода и входам синхронизации регистров, группа выходов блока синхронизации подключена к управляющим входам коммутатора, выход блока памяти амплитуд подключен к выходу синтезатора и дополнительно введен регистр памяти, вход синхронизации которого подключен ко второму выходу блока синхронизации, информационный вход подключен к выходу коммутатора, а выход подключен к входу блока памяти амплитуд.

Отличительными признаками предлагаемого изобретения от указанного прототипа являются дополнительно введенный в него регистр памяти, вход которого подключен к выходу коммутатора, вход синхронизации подключен ко второму выходу блока синхронизации устройства, информационный выход подключен к входу блока памяти амплитуд.

Благодаря наличию этих признаков, фазосдвигающий сумматор первого канала формирует код выборки последующего цикла синтеза во время последнего такта предыдущего цикла синтеза, что позволяет исключить ложные значения и задержки синтезируемого сигнала и соответственно повысить его спектральную чистоту. При таком построении устройства время суммирования фазосдвигающего сумматора первого канала не должно превышать периода тактовой частоты Т0.

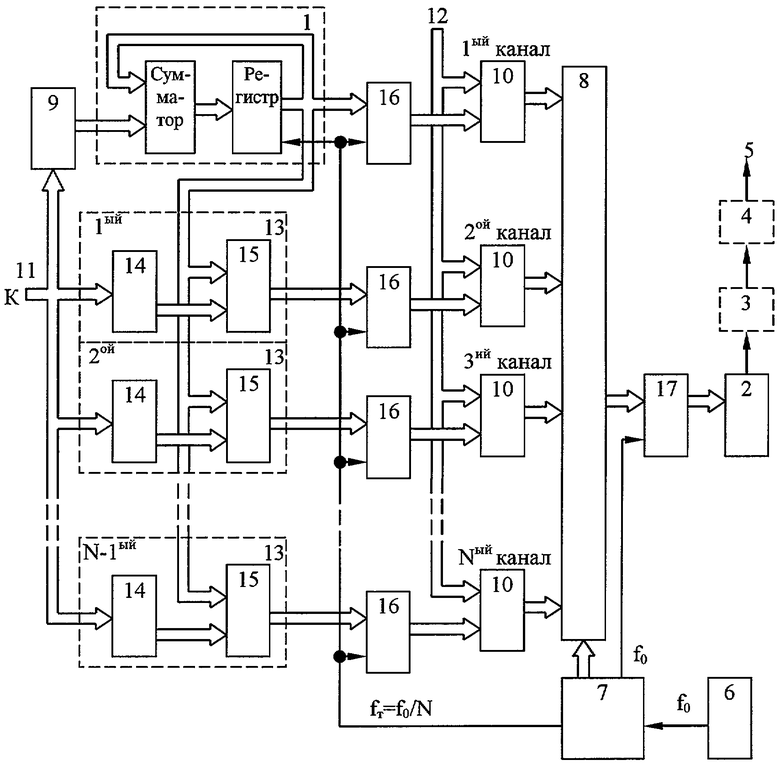

На чертеже представлена структурная схема цифрового синтезатора частот.

Цифровой синтезатор частот содержит накопитель 1 кода, блок 2 памяти амплитуд, цифроаналоговый преобразователь 3, фильтр нижних частот 4, выходную шину 5 устройства, опорный генератор 6, блок 7 синхронизации устройства, коммутатор 8, умножитель 9, N фазосдвигающих сумматоров 10, входную шину 11 кода установки частоты, входную шину 12 кода формирования фазоманипулированного сигнала, N-1 блоков 13 фазового сдвига, каждый из которых содержит формирователь 14 весового коэффициента сдвига и сумматор-вычислитель 15, N регистров 16 и регистр 17 памяти.

Принцип действия предлагаемого цифрового синтезатора частот, как и устройства-прототипа, основан на одновременном формировании кодов N точек отсчета фазы синтезируемого колебания (выборок из памяти амплитуд), дискретно сдвинутых друг относительно друга на определенную величину, с последующим выбором кодов данных точек отсчета фазы в определенной последовательности в фиксированные моменты времени для получения требуемой формы выходного синтезируемого колебания.

Синтезатор частот работает следующим образом.

На входной шине 11 кода установки частоты устанавливается кодированное значение синтезируемой частоты К (код установки частоты). Это число поступает на вход умножителя 9, на выходе которого формируется код числа, равный K·N, где N - число каналов устройства. По тактовым импульсам с первого выхода блока 7 синхронизации устройства, формируемого с частотой fT=f0/N, где f0 - частота опорного генератора 6, накопитель 1 кода накапливает код K·N, в результате чего на его выходе в каждый тактовый момент времени tT=i·TT=i/fT (i=0, 1, 2, 3...) формируется пропорциональный фазе синтезируемого колебания код числа, который с выхода накопителя 1 кода поступает на входы сумматоров-вычислителей 16 N-1 блоков 13 фазового сдвига.

Код К установки частоты одновременно поступает на входы формирователей 14 весового коэффициента сдвига N-1 блоков 13 фазового сдвига. Формирователь 14 весового коэффициента сдвига выполняет операцию умножения кода К установки частоты на постоянный коэффициент, равный номеру блока фазового сдвига, в результате чего на его выходе образуются коды чисел, равные, по каждому каналу соответственно, К, 2К...(N-1)K, которые в сумматорах-вычислителях 16 добавляются к выходному коду накопителя 1 кода.

Таким образом, на выходе блоков 13 фазового сдвига в тактовые моменты времени tT формируются N-1 кодов чисел, пропорциональных фазе синтезируемого колебания, но смещенных относительно выходного кода накопителя 1 кода соответственно на К, 2К...(N-1)K.

Выход накопителя 1 кода и выходы N-1 блоков 13 фазового сдвига подключены к информационным входам регистров 16. Регистры 16 по тактовым импульсам с первого выхода блока 7 синхронизации устройства с частотой fT=f0/N переписывают информацию с входа на выход, которая далее поступает на входы фазосдвигающих сумматоров 10.

На выходах фазосдвигающих сумматоров 10 формируется N кодов чисел (кодов выборки), соответствующих фазе синтезируемого колебания с учетом сдвига фазы ϕ, заданного кодом формирования фазоманипулированного сигнала, и, начиная со второго, смещенных относительно выходного кода накопителя 1 кода соответственно на К, 2К...(N-1)K, которые поступают на входы коммутатора 8 из N в один.

Коммутатор 8 с частотой синхронизации f0 в последовательности, задаваемой блоком 7 синхронизации устройства, пропускает на выход коды выборки таким образом, что за один цикл синтеза с временем TT=N·T0 (время одного такта работы накопителя 1 кода, блоков 13 фазового сдвига и регистров 16) на его выходе формируется последовательность из N кодов выборки, соответствующая фазовым точкам синтезируемого колебания: 0+ϕ, К+ϕ, 2К+ϕ,...(N-1)·K+ϕ - в первый цикл синтеза, N·K+ϕ, (N+1)·K+ϕ, (N+2)·K+ϕ,...(2N-1)·K+ϕ - во второй цикл, 2N·K+ϕ, (2N+1)·K+ϕ,... (3N-1)·К+ϕ - в третий цикл и т.д., т.е. на выходе коммутатора 8 в каждый тактовый момент времени t0=i·T0 (i=0, 1, 2, 3...) код выборки изменяется на величину, равную коду частоты К, в то время как на выходах накопителя 1 кода и блоков 13 фазового сдвига информация меняется на величину N·K и только к моменту времени tT=i·TT, TT=T0·N.

Таким образом, тактовая частота работы накопителя 1 кода и блоков 13 фазового сдвига синтезатора, представленного на структурной схеме, и устройства-прототипа одинаковы.

С выхода коммутатора 8 код выборки по тактовым импульсам со второго выхода блока 7 синхронизации устройства с частотой f0 сохраняется в регистре 17 памяти и поступает с выхода регистра 17 памяти на вход блока 2 памяти амплитуд.

Блок памяти амплитуд представляет собой фазосинусный преобразователь и осуществляет переход от отсчетов кода фазы к отсчетам кода амплитуды синтезируемого колебания, который в цифроаналоговом преобразователе 3 преобразуется в аналоговую величину, т.е. в напряжение, соответствующее входным кодам. Ступенчатый сигнал с выхода ЦАП 3 сглаживается фильтром 4.

В устройстве-прототипе в N раз снижены требования к быстродействию блоков фазового сдвига. При этом точность формирования выходного сигнала и, как следствие, его спектральная чистота определяются быстродействием фазосдвигающего сумматора первого канала, потому что на время формирования им кода выборки на выходе синтезатора возникают ложные выбросы, обусловленные неверными (переходными) значениями кода выборки. Требования к быстродействию остальных фазосдвигающих сумматоров неодинаковы по каналам и изменяются от Т0 для фазосдвигающего сумматора второго канала до (N-1)·T0 для фазосдвигающего сумматора N-го канала. В результате этого точность формирования выходного сигнала устройства-прототипа ограничена быстродействием фазосдвигающего сумматора первого канала и обеспечивается только в том случае, если время суммирования первого фазосдвигающего сумматора будет много меньше, чем Т0.

В предлагаемом синтезаторе в тактовый момент времени tT коммутатор 8 передает код выборки с выхода фазосдвигающего сумматора N-го канала на вход регистра 17, хранящего и формирующего на входе блока 2 памяти амплитуд N-1-ый код выборки. По тактовым импульсам с первого и второго выходов блока 7 синхронизации устройства регистр 17 памяти сохраняет и выдает на вход блока 2 памяти амплитуд код выборки с выхода фазосдвигающего сумматора 10 N-го канала, регистры 16 сохраняют и передают на входы фазосдвигающих сумматоров 10 N новых значений кодов фаз, фазосдвигающие сумматоры 10 начинают вычисление N новых кодов выборки, а накопитель 1 кода и N-1 блоков 13 фазового сдвига начинают вычисление N кодов фаз для следующего цикла синтеза. Одновременно, по сигналам управления коммутатор 8 коммутирует выход фазосдвигающего сумматора 10 первого канала с входом регистра 17 памяти. Через время Т0 после момента времени tT по тактовому импульсу со второго выхода блока 7 синхронизации устройства регистр 17 памяти сохраняет и передает на вход блока 2 памяти амплитуд новый код выборки, вычисленный фазосдвигающим сумматором 10 первого канала, а коммутатор 8 подключает к входу регистра 17 памяти выход фазосдвигающего сумматора 10 второго канала. Аналогичным образом, на вход блока 2 памяти амплитуд через время 2Т0, 3T0,...(N-1)·T0 после момента времени tT поступят новые коды выборки, сформированные фазосдвигающими сумматорами второго, третьего, ...(N-1) каналов, после чего цикл синтеза повторяется.

Введение дополнительного регистра 17 памяти, включенного между коммутатором 8 и блоком 2 памяти амплитуд и работающего на частоте синхронизации f0 позволяет снизить требования по быстродействию до Т0 для фазосдвигающего сумматора 10 первого канала, до 2Т0 - второго канала и т.д. до N·T0 для фазосдвигающего сумматора 10 N-го канала, полностью исключить передачу на вход блока 2 памяти амплитуд неверных кодов выборки и формирование на выходе синтезатора ложных уровней сигнала, а, в конечном итоге, повысить спектральную чистоту синтезируемого сигнала по сравнению с устройством-прототипом.

Литература

1. Техника средств связи, серия ТРС, выпуск 9, 1983 г., стр.66-71.

2. Патент SU №1689937 A1.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1998 |

|

RU2153698C2 |

| Цифровой синтезатор частот | 1989 |

|

SU1689937A1 |

| Цифровой синтезатор частот | 1988 |

|

SU1517016A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2007 |

|

RU2344541C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2030092C1 |

| Цифровой синтезатор частот | 1978 |

|

SU813675A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2012 |

|

RU2490789C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО- И ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2007 |

|

RU2358384C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2149503C1 |

| Цифровой синтезатор частот | 1988 |

|

SU1589366A1 |

Изобретение относится к радиотехнике, к технике цифрового вычислительного синтеза частот, и может использоваться в радиопередающих и радиоприемных устройствах. Достигаемый технический результат - повышение спектральной чистоты выходного сигнала. Цифровой синтезатор частот содержит накопитель кода, блок памяти амплитуд, цифроаналоговый преобразователь, фильтр низких частот, опорный генератор, блок синхронизации устройства, коммутатор, умножитель, N-1 блоков фазового сдвига, N регистров, N фазосдвигающих сумматоров, регистр памяти. 1 ил.

Цифровой синтезатор частот, содержащий накопитель кода, блок памяти амплитуд, цифроаналоговый преобразователь, фильтр низких частот, выходную шину устройства, опорный генератор, блок синхронизации устройства, коммутатор, умножитель, входную шину кода установки частоты, входную шину кода формирования фазоманипулированного сигнала, N-1 блоков фазового сдвига, N фазосдвигающих сумматоров и N регистров, где N - число каналов синтезатора, причем входная шина кода установки частоты синтезатора подключена к входам кода установки частоты N-1 блоков фазового сдвига и к входу умножителя, выход которого подключен к входу накопителя кодов, выход которого подключен к информационному входу регистра первого канала и к входам фазы N-1 блоков фазового сдвига, выходы N-1 блоков фазового сдвига подключены к соответствующим информационным входам регистров с второго по N-ый, выходы регистров с первого по N-й подключены к вторым входам соответствующих фазосдвигающих сумматоров, входная шина кода формирования фазоманипулированного сигнала синтезатора подключена к первому входу фазосдвигающих сумматоров, выходы которых подключены к соответствующим информационным входам коммутатора, выход опорного генератора подключен к входу блока синхронизации, первый выход которого подключен к входу синхронизации накопителя кода и входам синхронизации регистров, а группа выходов блока синхронизации подключена к управляющим входам коммутатора, выход блока памяти амплитуд подключен к выходу синтезатора, отличающийся тем, что в него дополнительно введен регистр памяти, вход синхронизации которого подключен ко второму выходу блока синхронизации, информационный вход подключен к выходу коммутатора, а выход подключен к входу блока памяти амплитуд.

| Цифровой синтезатор частот | 1989 |

|

SU1689937A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2143173C1 |

| Цифровой синтезатор частот | 1990 |

|

SU1774464A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1771059A1 |

| US 5034977, 23.07.1991 | |||

| US 4484296, 20.11.1984. | |||

Авторы

Даты

2005-10-10—Публикация

2004-04-26—Подача