Изобретение относится к радиотехнике и может быть использовано в возбудителях .радиопередающих устройств с частотной модуляцией.

Целью изобретения является повышение быстродействия.

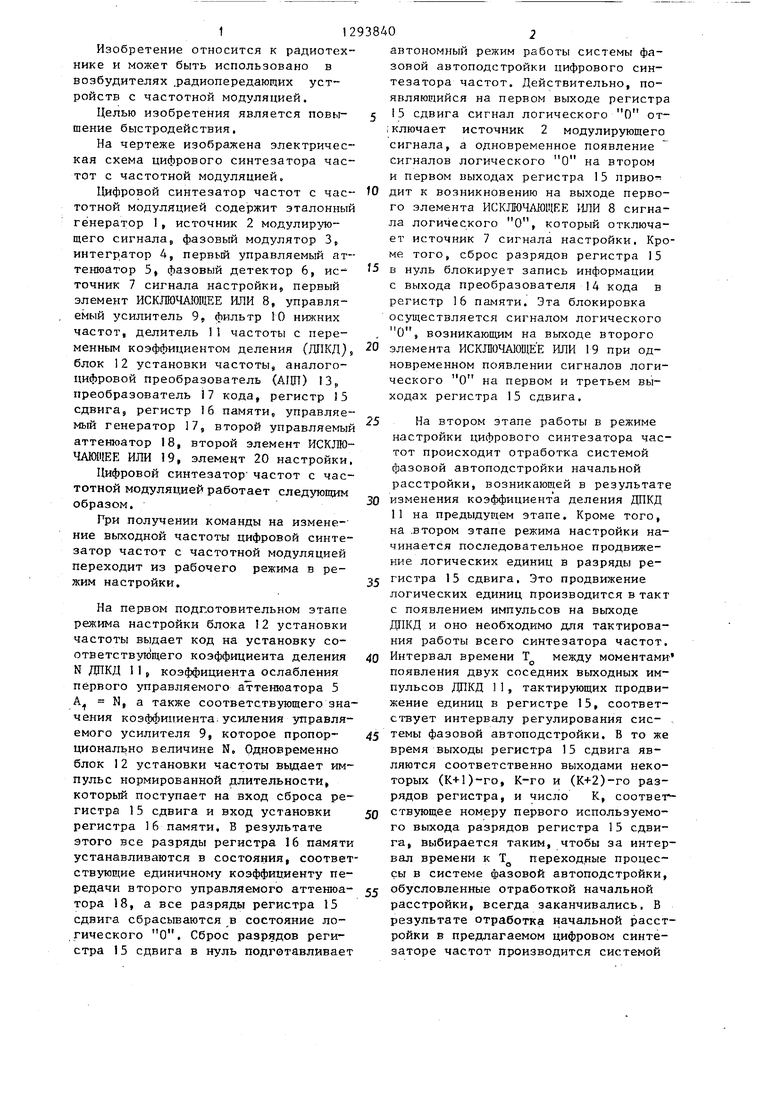

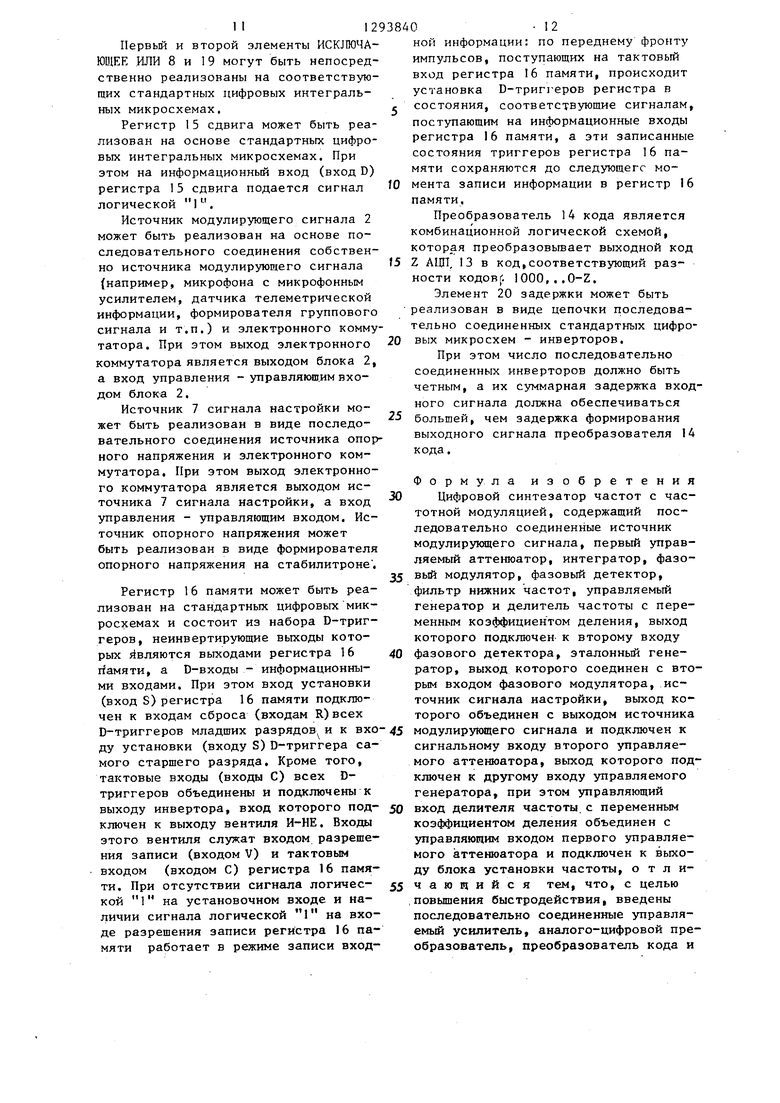

На чертеже изображена электрическая схема цифрового синтезатора частот с частотной модуляцией.

Цифровой синтезатор частот с частотной модуляцией содержит эталонный генератор I, источник 2 модулирующего сигналар фазовый модулятор 3( интегратор 4, первый управляемый аттенюатор 5, фазовый детектор 6, ис- точник 7 сигнала настройки, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8, управляемый усилитель 9, фильтр 10 нижних частот, делитель 11 частоты с переменным коэффициентом деления (Д1КД} j блок 12 установки частоты, аналого- цифровой преобразователь (АЦП) 13,, преобразователь 17 кода, регистр 15 сдвига, регистр 16 памяти управляемый генератор 17, второй управляемый аттенюатор 18, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19, элемент 20 настройки

Цифровой синтезатор частот с частотной модуляцией работает следующим образом.

При получении команды на изменение выходной частоты цифровой синтезатор частот с частотной модуляцией переходит из рабочего режима в режим настройки.

На первом подготовительном этапе режима настройки блока 12 установки частоты выдает код на установку со- ответству1ощего коэффициента деления N ДПКД 1 1 р коэффициента ослабления первого управляемого а ттенюатора 5 А N, а также соответствующего значения коэффициента;усиления управляемого усилителя 9, которое пропор- ционал1;но величине N. Одновременно блок 12 установки частоты вьщает импульс нормированной длительности, который поступает на вход сброса регистра 15 сдвига и вход установки регистра 16 памяти, В результате этого все разряды регистра 16 памяти устанавливаются в состояния, соответствующие единичному коэффициенту передачи второго управляемого аттенюа- тора 18, а все разряды регистра 15 сдвига сбрасываются в состояние логического О, Сброс разрядов регистра 15 сдвига в нуль подготавливает

5

О

автономный режим работы системы фазовой автоподстройки цифрового синтезатора частот. Действительно, появляющийся на первом выходе регистра 15 сдвига сигнал логического О от- ;ключает источник 2 модулирующего сигнала, а одновременное появление сигналов логического О на втором и первом выходах регистра 15 приводит к возникновению на выходе первого элемента ИСКЛЮЧАМЦЕЕ ИЛИ 8 сигнала логического О, который отключает источник 7 сигнала настройки. Кроме того, сброс разрядов регистра 15 в нуль блокирует запись информации с выхода преобразователя 14 кода в регистр 16 памяти. Эта блокировка осуществляется сигналом логического О, возникающим на вьгходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 при одновременном появлении сигналов логического О на первом и третьем выходах регистра 15 сдвига.

На втором этапе работы в режиме настройки цифрового синтезатора частот происходит отработка системой фазовой автоподстройки начальной расстройки, возникающей в результате изменения коэффициента деления ДПКД 11 на предыдущем этапе. Кроме того, на .втором этапе режима настройки начинается последовательное продвижение логических единиц в разряды ре- гистра 15 сдвига. Это продвижение логических единиц производится в такт с появлением импульсов на выходе ДПКД и оно необходимо для тактирования работы всего синтезатора частот.

Интервал времени Т между моментами появления двух соседних выходных импульсов ДПКД 11, тактирующих продвижение единиц в регистре 15, соответствует интерв шу регулирования сие- темы фазовой автоподстройки, В то же время выходы регистра 15 сдвига являются соответственно выходами некоторых (К+1)-го, К-го и (К+2)-го разрядов регистра, и число К, соответ ствующее номеру первого используемого выхода разрядов регистра 15 сдвига, выбирается таким, чтобы за интервал времени к Т переходные процессы в системе фазовой автоподстройки, обусловленные отработкой начальной расстройки, всегда заканчивались, В результате отработка начальной расстройки в предлагаемом цифровом синтезаторе частот производится системой

фазовой автоподстройки, работающей в автономном режиме, так как на всем протяжении переходного процесса по отработке начальной расстройки на выходах регистра 15 сдвига поддержи- ваются сигналы логических нулей и, соответственно, источники возмуг-ений системы фазовой автоподстройки (источник 2 модулирующего сигнала и источник 7 сигнала нacтpoйкиj отключе- ны. Второй этап работы заканчивается установлением в системе фазовой автоподстройки некоторого стационарного значения разности фаз, а на выходе фазового детектора 6 - соответствую- щего установившегося значения выходного напряжения.

На третьем этапе работы в режиме настройки производится вьмисление такого значения коэффициента ослабле- ния А второго управляемого аттенюатора 18, установка которого обеспечивает достижение требуемого качества частотной модуляции выходного колебания синтезатора. Для неискажен- ной частотной модуляции значение коэффициента ослабления А, должно соответствовать равенству между значением крутизны управления частотой опорного сигнала системы фазовой автоподстройки посредством последовательно соединенных первого управляемого аттенюатора 5, интегратора 4 и фазового модулятора 3, с одной стороны, и значением крутизны управ- Ленин частотой выходного сигнала ДПК 11 посредством последовательно соединенных второго управляемого аттенюатора 18 и управляемого генератора 17 с другой стороны. Отсюда следует, что для неискаженной частотной модуляции необходимо обеспечить А Sg/Sy , где 8д - крутизна управления частотой опорного сигнала посредством последовательно соединенных интегратора 4 и фазового модулятора. 3, а Sy - крутизна управления частотой управляемого генератора 17 по входу, подключенному к выходу второго управляемого аттенюатора 18, Од- нако в результате воздействия на управляемый генератор 17 различных дестабилизирующих факторов, а также вследствие нелинейности и разброса характеристик управления частотой управляемого генератора 17, точное значение крутизны 8,, для конкретного синтезатора и конкретной рабочей частоты неизвестно. Поэтому значение

коэффициента ослабления А , обеспечивающее неискаженную модуляцию, также неизвестно. Для оценки неизвестного значения А производится идентификация значения крутизны управления частотой управляемого генератора 17 на основе введения пробного возмущения от источника 7 сигнала настройки. Для этого по переднему фронту К-го выходного импульса ДПКД 1I происходит продвижение логической 1 в К7разряд тактирующего регистра 15 сдвига. Появление логической 1 в, К-ом разряде регистра 15 сдвига соответствует появлению на втором выходе этого регистра сигнала логической 1. Этот сигнал поступает на вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 и вместе с сигналом логического О, поступающим на другой вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, приводит к появлению на его выходе сигнала логической 1. В свбю очередь этот сигнал логической 1 включает источник 7 сигнала настройки. В результате по переднему фронту К-го выходного импульса ДПКД 11 на объединенные входы первого и второго управляемых аттенюаторов 5 и 18 от источника 7 сигнала настройки поступает перепад напряжения амплитудой . Этот перепад х приводит к отклонению разности фаз в системе фазовой автоподстройки цифрового синтезатора .от установившегося ранее стационарного значения, К моменту появления на выходе ДПКД 11 следующего (К+1)-го импульса величина этого отклонения разности фаз от стационарного значения определяется ностью дополнительных набегов фаз за интервал времени Т сигналов, поступающих на вход фазового детектора ,6, Величина дополнительного набега фазы опорного сигнала за время T,j в данном случае определяется модуляцией частоты эталонного генератора Г перепадом х посредством последовательно соединенных первого управляемого аттенюатора 5, интегратора 4 и фазового модулятора 3 и составляет величину, равную . Дополнительный набег фазы выходного сигнала ДПКД 11 за время Т„ в рассматриваемом случае обусловлен модуляцией частоты управляемого генератора 17 перепадом х. , поступающим на вход второго управляемого аттенюатора 18, и составляет величину Xo Syp To/N,

В результате к моменту появления на выходе ДПКД II (К+1)-го импульса разность фаз в системе ФАЛ отклоняется от Стационарного значения на величи- ну X/-S, -Т,- ( )/N.

Соответствующее этому отклонению разности фаз отклонение выходного напряжения фазового детектора 6 от стационарного значения составляет величину

F -SO-T CI-S,,/s,)/N,

где F - крутизна ДИСКРИМИНАЦИОННОЙ характеристики фазового детектора 6. Коэффициент усиления управляемого усилителя 9 в соответствии с полученным от блока 12 установки частоты КОДОМ, равен N/F, S х Т,, На выходе управляемого усилителя 9 имеется разделительный конденсатор (не пока- зан, емкость которого выбрана соответствующей выделению из выходного напряжения фазового детектора 6 непосредственно величины отклонения этого напряжения от установившегося ранее значения, В результате в момент появления на выходе ДПКД 1 (К+1)-го импульса на выходе управляемого усилителя 9 формируется перепад напря жения амплитудой, равной величине

(1-S ,j|./S ), Исходя из этой величины, 30 щий на втором выходе АЦП 13 в момент

окончания цикла преобразования, проходя через элемент 20 задержки, поступает на тактовый вход (вход С) регистра 16 памяти в момент времени, 35 когда формирование цифрового кода, соответствующего величине Sy /S, на выходе преобразователя 14 кода уже закончено, В результате код, сонесложно вычислить значение коэффициента ослабления А , которое соответствует неискаженной частотной модуляции выходного сигнала синтезатора. Поэтому с появлением на выходе ДПКД 11 (K-i-l)-ro импульса источник 7 сигнала настройки отключается и начинаются вычисления требуемого значения коэффициента ослабления Aj, Кроме того, практически сразу после появления на выходе ДПКД П (К+)-го импульса выдается сигнал на разрешение записи результатов вычисления требуемого значения А „ в регистр 6 памяти и включение источника модулирующего сигнала 2, поскольку быстродействие устройств, принимающих участие в вычислениях требуемого значе- ния А , всегда можно обеспечит достаточно высоким. Все эти операции производятся в предлагаемом синтезаторе следующим образом,

С появлением на выходе ДПКД 11 (К+1)-го импульса в (К+1)-й разряд

40

ответствующи величине S , записывается в регистр 16 памяти и поступает на управляющий вход второго управляемого аттенюатора 18, Этот код формируется на входе второго управляемого аттенюатора 18 практичес45 ки сразу после появления на выходе ДПКД 11 (К+1)-го импульса, поскольку при реализации АЦП 13, преобразователя 14 кода, регистра 15 сдвига, регистра 16 памяти и второго элемен50 та ИСКЛЮЧАЮЩЕЕ ИЛИ 19 на современной элементной базе длительность интервала временир необходимого для формирования этого кода, может быть обеспечена много меньшей, чем длирегистра 15 «сдвига продвигается логи- 55 тельность интервала регулирования Т

ческая 1 и за счет этого на первом выходе регистра 15 появляется сигнал . логической 1, С появлением (K-M)-roj выходного импульса ДПКД 11 на входе

АЦП 13 формируется напряжение величиной ( /So) , Этот же (К-И)-й импульс, поступая на вход Пуск АЦП 13, запускает процесс преобразования аналоговой величины (1-S /S) в соответствующий цифровой код. За счет обеспечения соответствующего быстродействия АЦП 13 напряжение на его входе можно считать практически

неизменным на протяжении одного цикла преобразования. Результат преобразования - цифровое представление величины (,jj /SQ) поступает на вход преобразователя 14 кода, на выходе

которого формируется цифровой код, соответствующий величине , Одновременно с этими процессами появившийся на первом выходе регистра 15 сдвига сигнал логической 1, поступая на один из входов второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19, переключает его выходной сигнал на сигнал логической 1, который поступает на вход разрешения записи (вход V) ре

гистра 16 памяти и разрешает запись в регистр 16 памяти кода, поступающего на вход этого запоминающего регистра с выхода преобразователя 14 кода. Кроме того, сигнал, возникаю40

ответствующи величине S , записывается в регистр 16 памяти и поступает на управляющий вход второго управляемого аттенюатора 18, Этот код формируется на входе второго управляемого аттенюатора 18 практичес45 ки сразу после появления на выходе ДПКД 11 (К+1)-го импульса, поскольку при реализации АЦП 13, преобразователя 14 кода, регистра 15 сдвига, регистра 16 памяти и второго элемен50 та ИСКЛЮЧАЮЩЕЕ ИЛИ 19 на современной элементной базе длительность интервала временир необходимого для формирования этого кода, может быть обеспечена много меньшей, чем длисистемы фазовой автоподстройки, В соответствии с этим одновременно с вычислением кода, соответствующего величине S.,f /S,, , происходит отклю

чение источника 7 сигнала настройки и включение источника 2 модулирующего сигнала. Эта коммутация осутцеств ляется сигналом логической 1, возникающим на первом выходе регистра 15 сдвига при появлении на выходе ДПКД II (К+1)-го импульса. Этот сигнал 1 поступает с первого выхода регистра 15 сдвига на управляющий вход источника 2 модулирующего сиг- нала и включает его. Кроме того, этот же сигнал логической 1 поступает на один из входов первого элемента ИСКЛЮЧАЮ1ЦЕЕ ИЛИ 8 и переключает его выходной сигнал с сигнала логической 1 на сигнал логическог О. Тем самым источник 7 сигнала настройки отключается. Таким образом, третий этап работы предлагаемого цифрового синтезатора частот в режиме настройки начинается с появлением на выходе ДПКД 11 К-го импульса (т.е. сразу после окончания отработки начальной расстройки системой фазовой автоподстройки) и заканчивается практически сразу после появления на выходе Д11КД 1 1 следующего (К+1)-го импульса формированием на управляющем входе второго управляемого аттенюатора 18 такого кода, который обеспечивает значение его коэффициента ослабления, соответству ющег о требуемым малым искажением частотной модуляции выходного колебания. Соответственно длительность этого этапа работы практически равны длительности одного интервала регулирования системы фазовой автоподстройки (с точностью до быстродействия примененной при реализации синтезатора элементной базы). В предлагаемо синтезаторе значение коэффициента ослабления Aj второго управляемого аттенюатора 18, соответствующее неискаженной частотной модуляции, выставляется не точно, а с ошибкой, которая обусловлена конечной разрядностью представления входных аналоговых сигналов в АЦП 13 (так называемой ощибкой квантования) .

Сразу после установки требуемого значения коэффициента ослабления второго управляемого аттенюатора 18 и включения источника 2 модулирующе- го сигнала начинается последний, четвертый этап работы цифрового синтезатора в режиме настройки. На протяжении этого этапа в системе фазовой

5

0

5

5 0 0

5

0

5

0

5

автоподстройки происходит переходный процесс по отработке оставшегося к моменту отключения источника 7 сигнала настройки отклонения разности фаз от стационарного значения. Кроме того, в начале четвертого этапа (К+2)-й выходной импульс ДПКД 11 блокирует запись информации в регистре 16 памяти. Эта блокировка происходит следуюгшм образом ;(К+2)-й выходной импульс ДПКД 11 продвигает логическую 1 в ()-й разряд регистра 15 сдвига и в результате этого на тр.етьем выходе регистра 15 сдвига появляется сигнал логической этот сигнал логической I, поступая на один из входов второго вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ 19, переключает его выходной сигнал с сигнала логической I на сигнал логического О, который в свою очередь поступает на вход разрешения записи (вход V) регистра 16 памяти и блокирует запись информации в него. Длительность четвертого этапа режима настройки определяется величиной остаточного отклонения разности фаз и инерционностью системы фазовой автоподстройки, т.е. длительностью процесса отработки остаточного отклонения разности фаз. По окончании четвертого этапа режима настройки достигается заданное качество частотной модуляции выходного колебания и цифровой синтезатор частот переходит из режима настройки в режим нормальной работы, который продолжается до тех пор, пока блок 12 установки частоты не выдаст новой команды на изменение частоты выходного колебания.

Благодаря сокращению длительности процесса подстройки коэффициента ослабления второго управляемого атте-- нюатора 18 практически до длительности одного интервала регулирования системы фазовой автоподстройки при сохранении длительности остальных этапов режима настройки, а также достигаемой степени точности подстройки ослабления значительно сокращается суммарная длительность режима настройки. Повыщается быстродействие цифрового синтезатора частот. Длительность процесса подстройки коэффициента ослабления второго управляемого аттенюатора 18 практически равна одному интервалу регулирования системы фазовой автоподстройки. Крое того, длительность подготовителього этапа режима настройки и длительность аналогичного этапа работы известного устройства одинаковы, поскольку определяются быстродействием одинаковых блоков - скоростью управления источниками модулирующего игнала и сигнала настройки, скоростью становки коэффициента деления делите- я частоты с переменным коэффициентом еления, коэффициентов ослабления правляемых аттенюаторов и т.д. Длительность второго этапа настрбйки ифрового синтезатора частот также не превышает длительности соответствующего этапа работы известного устройства, поскольку не исключается автономный режим работы системы фазовой автоподстройки при отработке начальной частотной расстройки, а инерционность системы фазовой автоподстройки и диапазон возможных значений начальной расстройки и в известном синтезаторе, и в предлагаемом цифровом синтезаторе частот одинаковы при одинаковой реализации блоков систем фазовой автоподстройки, Кроме того, при соответствующем выборе размаха выходного сигнала источника настройки величина отстающего к моменту отключения источника сигнала настройки отклонения разности фаз в системе фазовой автоподстройки от стационарного значения в предлагаемом цифровом синтезаторе частот не выходит за пределы диапазона возможных значений остаточного отклонения разности фаз известного синтезатора и при одинаковой реализации блоков длительность последнего, четвертого этапа работы предлагаемого цифрового синтезатора частот в режиме настройки не превосходит длительности такого же этапа работы известного синтезатора. Наконец, независимо от выбора размаха выходного сигнала источника сигнала настройки и конкретного способа реализации блоков предлагаемого синтезатора частот при соответствующем выборе |числа уровней квантования входного аналогового напряжения в АЦП 13 ошибка вычисления коэффициента ослаблеУправляем1з1й усилитель 9 может быть вьшолнен в виде декадного умножающего цифроаналогового преобразователя, причем входом управляемого усилителя 9 является точка подключения источника опорного напряжения к декадному цифроаналоговому преобразователю и к этой точке входа усилителя подключен соответствующий разделительный конденсатор (не показан, Емкость этого разделительного конденсатора выбирается такой величины, чтобы постоянная времени переходных процессов, возникающих на входе управляемого усилителя 9, была с одной СТС1РОНЫ много меньше, чем длительность интервала регулирования системы фазовой автоподстройки, а с другой стороны - много больше, чем длительность процессов преобразования входного напряжения АЦП 13 в его выходной код. Управляющим входом управляемого усилителя 9 является шина подачи цифрового кода на вход умножающего цифроаналогового преобразователя. Первый и второй управляемые аттенюаторы 5 и 18 могут быть вьтол- нены в виде соответствующих цифро- аналоговых преобразователей для деления . При этом выходом управляемых аттенюаторов 5 и 18 является точка подключения к цифроаналоговому преобразователю для деления источника опорного напряжения. Включенный в цепь йбратной связи цифроаналогового преобразователя для деления умножающий цифроаналоговьш преобразователь при реализации первого управляемого аттенюатора 5 имеет декадную структуру, а при реализации второго управляемого аттенюатора 18 - двоичную

ния второго управляемого аттенюатора

18 к концу режима настройки для пред-55структуру.

лагаемого цифрового синтезатора час- АЩ 13 может быть выполнен в виде

тот не превышает ошибки подстройкианалого-цифрового преобразователя

козффипиента ослабления второго уп-последовательного приближения.

5

0

5

0

5

0

5

0

равляемого аттенюатора в конце режима настройки известного синтезатора.

Последовательно соединенные интегратор 4 и фазовый модулятор 3 вместе с подключенным к другому входу фазового модулятора эталонным генератором 1 , предназначенные для формирования частотно-модулированного опорного колебания системы фазовой автоподстройки, могут быть реализованы на основе кварцевого генератора, частота колебаний которого управляется напряжением.

Управляем1з1й усилитель 9 может быть вьшолнен в виде декадного умножающего цифроаналогового преобразователя, причем входом управляемого усилителя 9 является точка подключения источника опорного напряжения к декадному цифроаналоговому преобразователю и к этой точке входа усилителя подключен соответствующий разделительный конденсатор (не показан, Емкость этого разделительного конденсатора выбирается такой величины, чтобы постоянная времени переходных процессов, возникающих на входе управляемого усилителя 9, была с одной СТС1РОНЫ много меньше, чем длительность интервала регулирования системы фазовой автоподстройки, а с другой стороны - много больше, чем длительность процессов преобразования входного напряжения АЦП 13 в его выходной код. Управляющим входом управляемого усилителя 9 является шина подачи цифрового кода на вход умножающего цифроаналогового преобразователя. Первый и второй управляемые аттенюаторы 5 и 18 могут быть вьтол- нены в виде соответствующих цифро- аналоговых преобразователей для деления . При этом выходом управляемых аттенюаторов 5 и 18 является точка подключения к цифроаналоговому преобразователю для деления источника опорного напряжения. Включенный в цепь йбратной связи цифроаналогового преобразователя для деления умножающий цифроаналоговьш преобразователь при реализации первого управляемого аттенюатора 5 имеет декадную структуру, а при реализации второго управляемого аттенюатора 18 - двоичную

Первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 8 и 19 могут быть непосредственно реализованы на соответствующих стандартных цифровых интегральных микросхемах.

Регистр 15 сдвига может быть реализован на основе стандартных цифровых интегральных микросхемах. При этом на информационный вход (вход D) регистра 15 сдвига подается сигнал логической 1.

Источник модулирующего сигнала 2 может быть реализован на основе последовательного соединения собственно источника модулирующего сигнала (например, микрофона с микрофонным усилителем, датчика телеметрической информации, формирователя группового сигнала и т.п.) и электронного коммутатора. При этом выход электронного коммутатора является выходом блока 2, а вход управления - управляющим входом блока 2.

Источник 7 сигнала настройки может быть реализован в виде последовательного соединения источника опорного напряжения и электронного коммутатора. При этом выход электронного коммутатора является выходом источника 7 сигнала настройки, а вход управления - управляющим входом. Источник опорного напряжения может быть реализован в виде формирователя опорного напряжения на стабилитроне ,

Регистр 16 памяти может быть реализован на стандартных цифровых микросхемах и состоит из набора D-триг- геров, неинвертирующие выходы которых Являются выходами регистра 16 Iiaмяти, а D-входы - информационными входами. При этом вход установки (вход S) регистра 16 памяти подключен к входам сброса (входам R)всех D-триггеров младших разрядов и к вхо ду установки (входу S) D-триггера самого старшего разряда. Кроме того, тактовые входы (входы С) всех D- триггеров объединены и подключены к выходу инвертора, вход которого под- ключен к выходу вентиля И-НЕ, Входы этого вентиля служат входом разрешения записи (входом V) и тактовым входом (входом С) регистра 16 памяти. При отсутствии сигнала логичес- кой 1 на установочном входе и наличии сигнала логической 1 на входе разрешения записи регистра )6 памяти работает в режиме записи вход5

5

О

0

5

0 5 0 5

ной информации: по переднему фронту импульсов, поступающих на тактовый вход регистра 16 памяти, происходит установка D-триггеров регистра в состояния, соответствующие сигналам, поступающим на информационные входы регистра 16 памяти, а эти записанные состояния триггеров регистра 16 памяти сохраняются до следующего момента записи информации в регистр 16 памяти.

Преобразователь 14 кода является комбинационной логической схемой, которая преобразовывает выходной код Z АЦП, 13 в код,соответствующий разности кодов г. 1000,,.0-Z,

Элемент 20 задержки может быть реализован в виде цепочки последовательно соединенных стандартных цифровых микросхем - инверторов.

При этом число последовательно соединенных инверторов должно быть четным, а их суммарная задержка входного сигнала должна обеспечиваться большей, чем задержка формирования выходного сигнала преобразователя 14 кода.

Формула изобретения Цифровой синтезатор частот с частотной модуляцией, содержащий последовательно соединенные источник модулирукяцего сигнала, первый управляемый аттенюатор, интегратор, фазовый модулятор, фазовый детектор, фильтр нижних частот, управляемый генератор и делитель частоты с переменным коэЛя})ициентом деления, выход которого подключен- к второму входу фазового детектора, эталонный генератор, выход которого соединен с вторым входом фазового модулятора, источник сигнала настройки, выход которого объединен с выходом источника модулирующего сигнала и подключен к сигнальному входу второго управляемого аттенюатора, выход которого подключен к другому входу управляемого генератора, при этом управляющий вход делителя частоты, с переменным коэффициентом деления объединен с управляющим входом первого управляемого аттенюатора и подключен к выходу блока установки частоты, отличающийся тем, что, с целью повышения быстродействия, введены последовательно соединенные управляемый усилитель, аналого-цифровой преобразователь, преобразователь кода и

13 129384014

регистр памяти, а также первый эле-мента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход мент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй элементкоторого объединен с первым входом ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент задержки ипервого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с регистр сдвига, при этом сигнальныйуправляющим входом источника модули- вход управляемого усилителя подклю-5 сигнала и подключены к перчен к выходу фазового детектора, вы-вому выходу регистра сдвига, второй ход регистра памяти соединен с уп-выход которого подключен к второму равляющим входом второго управляе-входу первого элемента ИСКЛЮЧАЮЩЕЕ мого аттенюатора, тактовьш вход ре-ИЛИ, выход которого соединен с уп- гистра сдвига и вход Пуск знало- О равляющим входом источника сигнала го-цифрового преобразователя сое-настройки, третий выход регистра динекы и подключены к выходу дели-сдвига подключен к второму входу вто- теля частоты с переменным коэффици-рого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход ентом деления, вход и выход элемента за-установки регистра памяти объединен держки подключены соответственно к ВТО- с входом сброса регистра сдвига рому выходу аналого-цифрового преобра-и с управляющим входом управляе- зователя и к тактовому входу регистрамого усилителя и подключен к вы- памяти, вход разрешения записи кото-.ходу блока установки часто - рого соединен с выходом второго эле-ты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот с частотной модуляцией | 1988 |

|

SU1538253A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Синтезатор частот с широкополосной модуляцией | 2019 |

|

RU2713569C1 |

| Цифровой синтезатор частот с частотной модуляцией | 1990 |

|

SU1774465A2 |

| Синтезатор частот | 1986 |

|

SU1394434A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

Изобретение относится к радиотехнике. Цель изобретения - повьше- - ние быстродействия, Устр-во содержит эталонный генератор 1,источник 2 модулирующего сигнала, фазовый модулятор 3, интегратор 4, два управляемых аттенюатора 5 и 18, фазовый детектор 6, источник 7 сигнала настройки, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 и 19, управляемый усилитель 9, фильтр 10 нижних частот, делитель 11 частоты с переменным коэф,деления, блок установки 12 частоты, АЦП 13, преобразователь кода 14, регистр 15 сдвига, регистр 16 памяти, управляемый генератор 17 и эл-т.настройки 20. При получении команды из блока установки 12 на изменение выходной частоты устр-во переходит из рабочего режима в режим настройки, осуществляемый в четыре этапа. По окончании четвертого этапа режима настройки достигается заданное качество частотной модуляции выходного колебания и устр-во снова переходит в режим нормальной работы. Цель достигается путем сокращения суммарной длительности режима настройки, 1 ил. с 9 (Л

| Цифровой синтезатор частоты с частотной модуляцией | 1980 |

|

SU919040A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1982 |

|

SU1035776A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-28—Публикация

1985-10-24—Подача