мента И, выходом соединенного с суммирующим входом реверсивного счетчика, у которого вычитающий вход соединен с выходом четвертого элемента ,И, информациоиньй вход - с вторым выходом блока памяти и шиной цифрового выхода, управляющий вход - с выходом третьего элемента И, первьй R -вход - с первым выходом второго элемента управления, второй R -входс первым выходом первого элемента управления, выход второго элемента И соединен с третьим входом элемента Ш1И, третий выход первого элемента управления подключен к входу запуска аналого-цифрового преобраэователя, угравляющий выход которого соединен с С-входом первого регистра хранения, третий выход второго элемента управления подключен к шине запуска развертки, а четвертый выход - к адресному входу блока; памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Фильтр симметричных составляющих системы фазных сигналов | 1982 |

|

SU1083342A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1990 |

|

SU1781625A1 |

| Измерительный прибор | 1989 |

|

SU1661653A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Устройство для фазового управления инвертором тока с компенсирующим звеном | 1982 |

|

SU1066028A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Многоканальное устройство для до-пуСКОВОгО КОНТРОля пАРАМЕТРОВ | 1979 |

|

SU840819A1 |

| Устройство для управления преобразователем частоты с непосредственной связью и широтно-импульсным регулированием | 1989 |

|

SU1624629A1 |

ЦИФРОВОЙ РЕГИСТРАТОР, содержащий аттенюатор, фипьтр низких частот, аналого-цифровой преобразователь, два регистра хранения и . блок сравнения, соединенные последовательно, элемент ИЛИ, два элемента управления, блок памяти, генератор тактовых импульсов, делитель частоты и цифроаналоговый преобразователь, причем R-входы регистров хранения соединены с первым выходом первого элемента управления, второй вход блока сравнения соединен с выходом первого регистра хранения и первьо4 информационным входом блока памяти, первьй выход которого подключен к шине цифрового выхода и через цифроаналоговый преобразователь - к шине аналогового выхода, выход блока . ; сравнения соединен с С - входом вто- рого регистра хранения и первым вхоцом элемента ИЛИ, выходом соединенного с входом второго элемента управления, первый выход которого подключен к управляющему V-входу блока памяти, а второй выход - к первому входу первого элемента управления, генератор тактовых импульсов и делитель частоты соединены последовательно, причем первый выход последнего подключен к второму входу первого элемента управления, третий и четвертый входы которого соответственно подключены к шинам сигналов Сброс и Пуск, о т л и ч а ющ и и с я тем, что, с целью расширения функциональных возможностей, в него введены распределитель импульсов, пять элементов И, элемент НЕ и реверсивный счетчик, информационным выходом соединенньш с вторым информационным входом блока памяти, при(Л чем выход старшего разряда счетчика с соединен также с первым входом первого элемента И, выходом соединенного с вторым входом элемента ИЛИ, выход обратного переноса реверсивного счетчика соединен с первыми вхоо дами второго и третьего элементов И, 4; вторые входы которых подключены соел ответственно к первому и второму вы..( ходам распределителя импульсов, третий выход которого подключен к пер вому входу четвертого элемента И, второй выход первого элемента управления соединен с вторым входом первого элемента И, с входом разрешения записи блока памяти, первым входом пятого элемента И и через элемент НЕс вторым входом четвертого элемента И и стробирующим входом распределителя импульсов, . счеткьгй: вход которого соединен с вторым выходом делителя частоты, первый выход которого подключен к второму входу пятого эле

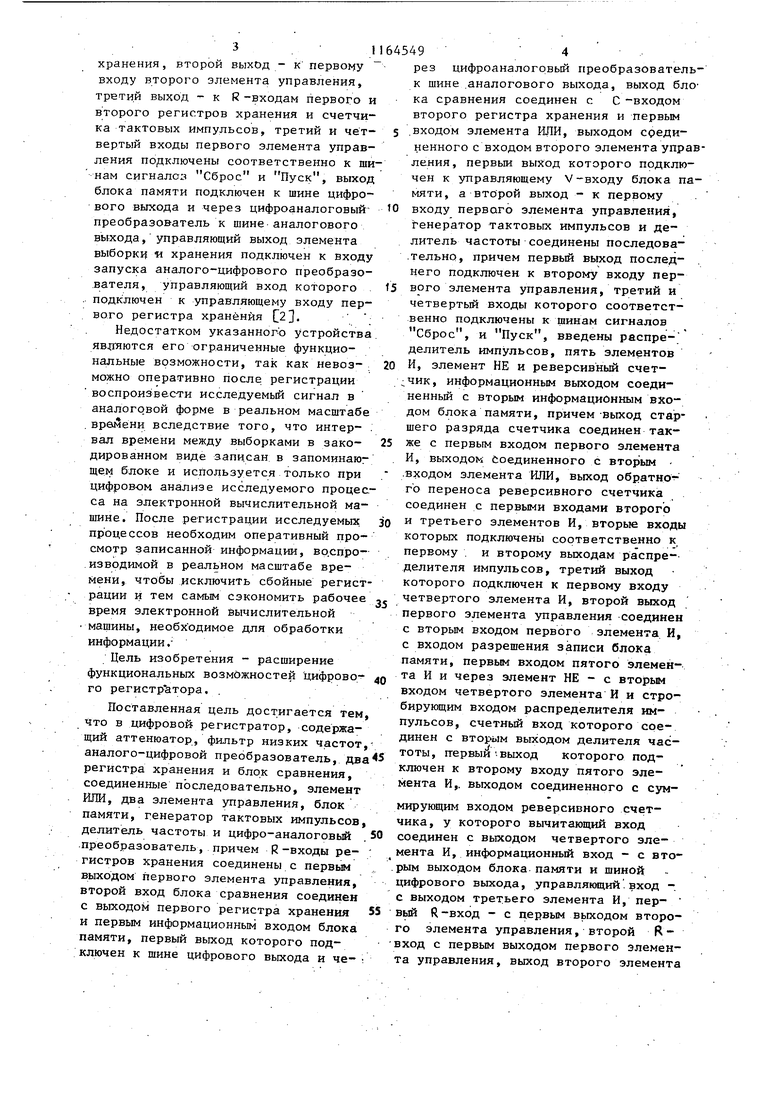

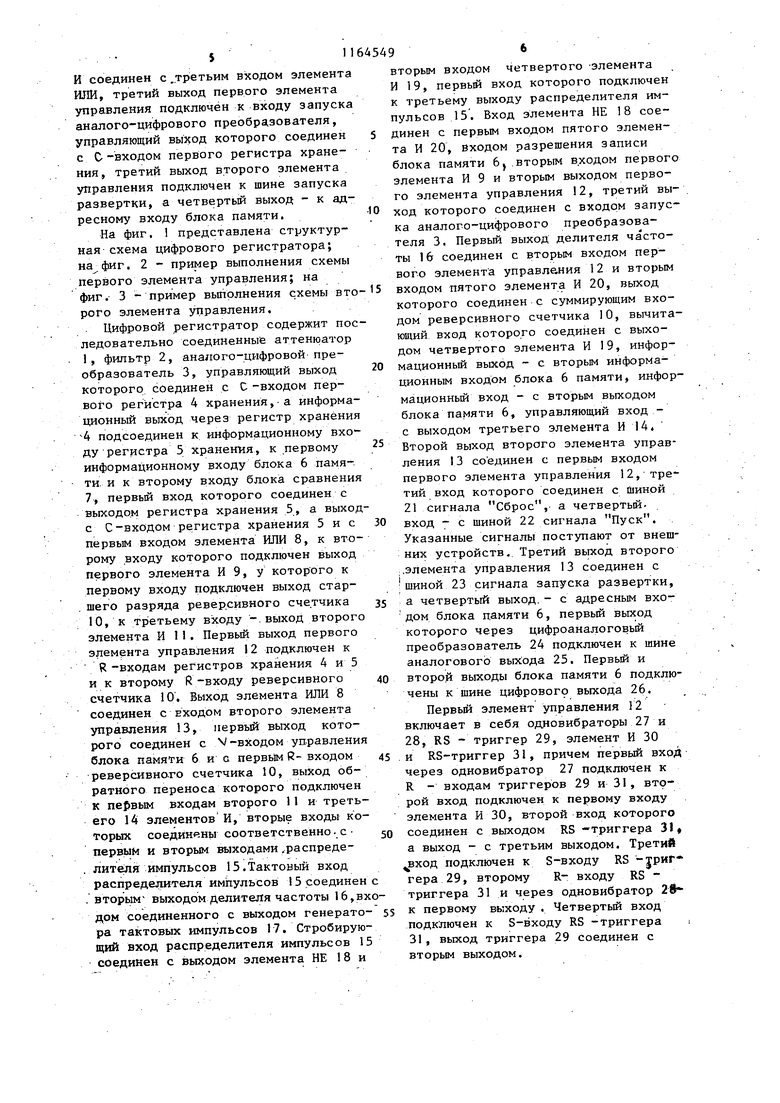

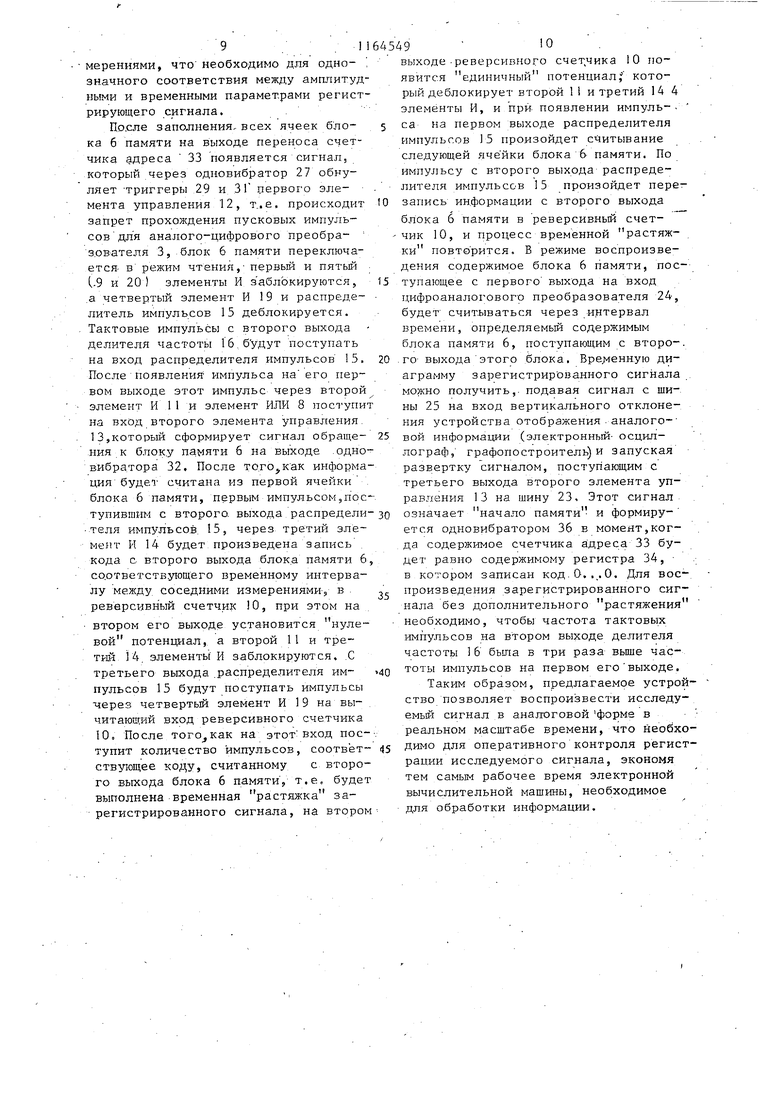

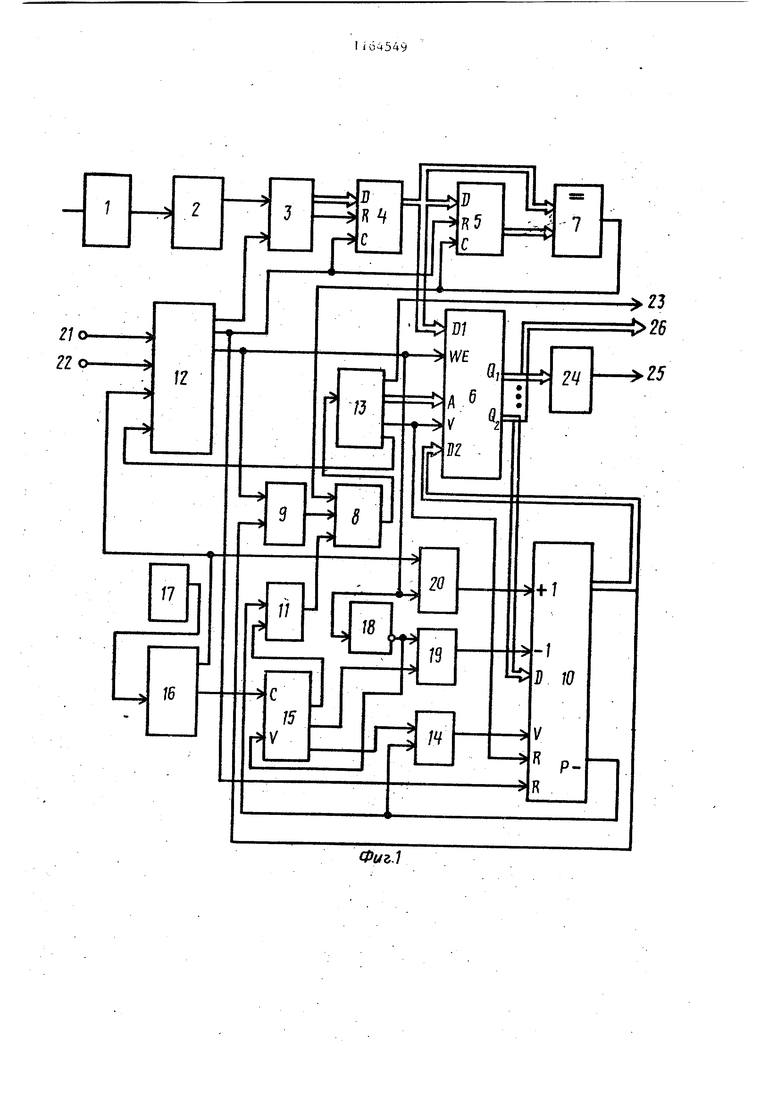

Изобретение относится к электроизмерительной технике и может быть использовано для измерения амплитудных и временных параметров, а также анализа статистических характеристик быстропротекающих процессов Известен цифровой регистратор, содержащий последовательно соединенные аттенюатор, входной фильтр низких частот, элемент выборки и хране ния; аналого-цифровой преобразователь, селектор вида запоминаемой информации, запоминающий блок, цифроаналоговьй преобразователь, выходной фильтр низких частот, промежуточный запоминающий блок, элементы управления запоминающим блоком и самописцем генератор-делитель тактирующих импульсов, выходную управляющую цепь цепь управления частотой выборки воспр изводимого сигнала и селектор приемного блока с переходным элементом, элемент управления самописцем содержит цепь управления запуском, входную цепь управления пусковым уровнем и наклоном пускового импульса и цепь управления частотой выборки регистрируемого сигнала, элемент управления запоминающим блоком со держит цепь управления запоминающим блоком, цепь управления режимом работы, счетчик слов и счетчик обра щения l. Недостатком данного устройства является низкое быстродействие,обусловленное постоянным периодом времени выборок входного сигнала в запоминающий блок, не зависящим от скорости изменения входного сигнала Наиболее близким по технической сущности к изобретению является цифровой регистратор, содержащий последовательно соединенные аттенюатор, фильтр низких частот, элемент выборки и хранения, аналого-цифровой преобразователь, информационный выход которого через первый регистр хранения подсоединен к информационному входу второго регистра хранения, первому информационному входу блока памяти и первому входу блока сравнения , к второму входу которого подключен выход второго регистра хранения, выход блока сравнения подключен к управляющему входу второго регистра хранения и к одному из входов логического элемента ИЛИ, к другому входу которого подключен выход старшего разряда счетчика тактовых импульсов, при этом выходы всех разрядов счетчика тактовых импульсов подключены к второму информационному ВХОДУ блока памяти, выход элемента ИЛИ подключен к R-входу счетчика тактовых импульсов и к второму входу второго элемента управления, первьй выход которого подключен к первому входу первого элемента управления, а второй выход - к управляющему входу блока памяти, при этом второй вход первого элемента управления подключен к счетному входу счетчика тактовых импульсов и к выходу делителя частоты, вход которого подклю-f чен к выходу генератора тактовых импульсов, первый выход первого эле- мента -управления подключен к управляющему входу элемента выборки и 31 хранения, второй выход - к первому входу второго элемента управления, третий выход - к R-входам первого и второго регистров хранения и счетчика тактовых импульсов, третий и четвертый входы первого элемента управления по/1ключены соответственно к ши нам сигналов Сброс и Пуск, выход блока памяти подключен к шине цифрового выхода и через цифроаналоговый преобразователь к шине аналогового выхода, управляющий выход элемента выборки я хранения подключен к входу запуска аналого-цифрового преобразователя, управляющий вход которого подключен к управляющему входу первого регистра хранения С23. Недостатком указанного устройства являются его ограниченные функциональные возможности, так как невозможно оперативно после регистрации воспроизвести исследуемый сигнал в аналоговой форме в реальном масщтабе .времени вследствие того, что интервал времени между выборками в закодированном виде записан в запоминающе у1 блоке и используется только при цифровом анализе исследуемого процес са на электронной вычислительной машине. После регистрации исследуемых процессов необходим оперативный просмотр записанной информации, во.спроизводимой в реальном масштабе времени, чтобы исключить сбойные регист рации и тем самым сэкономить рабочее время электронной вычислительной машины, необходимое для обработки информации. Цель изобретения - расширение функциональньк возможностей цифрового регистратора. . Поставленная цель достигается тем что в цифровой регистратор, содержащий аттенюатор, фильтр низких частот аналого-цифровой преобразователь, два регистра хранения и блок сравнения, соединенные последовательно, элемент ИЛИ, два элемента управления, блок памяти, генератор тактовых импульсов делитель частоты и цифро-аналоговый преобразователь, причем R-входы регистров хранения соединены с первым выходом первого элемента управления, второй вход блока сравнения соединен с выходом первого регистра хранения и первым информационным входом блока памяти, первый выход которого подключен к шине цифрового выхода и че49 4 . рез цифроаналоговый преобразовательк шине .аналогового выхода, выход блока сравнения соединен с С -входом второго регистра хранения и первым .входом элемента ИДИ, выходом соединенного с входом второго элемента управления, первый выход которого подключен к управляющему V-входу блока памяти, а второй выход - к первому входу первого элемента управления, генератор тактовых импульсов и делитель частоты соединены последова.тельно, причем первый выход послед- . него подключен к второму входу первого элемента управления, третий и четвертый входы которого соответственно подключены к шинам сигналов Сброс, и Пуск, введены распределитель импульсов, пять элементов И, элемент НЕ и реверсивный счетЧик, информационным выходом соединенньй с вторым информационным входом блока памяти, причемВыход старшего разряда счетчика соединен также с первым входом первого элемента И, выходом Соединенного с вторым .входом элемента ИЛИ, выход обратного переноса реверсивного счетчика соединен с первыми входами второго и третьего элементов И, вторые входы которых подключены соответственно к первому . и второму выходам распре-делителя импульсов, третий выход которого подключен к первому входу четвертого элемента И, второй выход первого элемента управления соединен с вторым входом первого элемента. И, с входом разрешения записи блока памяти, первым входом пятого элемента И и через элемент НЕ - с вторым входом четвертого элемента И н стробирующим входом распределителя импульсов, счетный вход которого соединен с вторым выходом делителя час- тоты, п ервый.выход которого подключен к второму входу пятого элемента И,, выходом соединенного с суммирующим входом реверсивного счетчика, у которого вычитающий вход соединен с выходом четвертого элемента И, информационный вход - с вторым выходом блока, памяти и шиной цифрового выхода, управляющий.вход с выходом третьего элемента И, первый R-вход - с п;ервым вьгходом второго элемента управления, второй R вход с первым выходом первого элемента управления, выход второго элемента И соединен с ..третьим входом элемента ИЛИ, третий выход первого элемента управления подключён к входу запуска аналого-цифрового преобразователя, управляющий выход которого соединен с С-входом первого регистра хранения, третий выход второго элемента управления подключен к шине запуска развертки, а четвертый выход - к адресному входу блока памяти. На фиг, 1 представлена структурная схема цифрового регистратора; на фиг. 2 - пример выполнения схемы первого элемента управления; на фиг. 3 - пример выполнения схемы вто рого элемента управления. Цифровой регистратор содержит пос ледовательно соединенные аттенюатор 1, фильтр 2, аналого-цифровой преобразователь 3, управляющий выход которого соединен с С -входом первого регистра 4 хранения,-а информационный выход через регистр хранения Ч подсоединен к информационному входу регистра 5 хранения, к первому информационному входу блока 6 памя-. ти. и к второму входу блока сравнения 7, первый вход которого соединен с выходом регистра хранения 5, а выход с С-входом регистра хранения 5 и с первым входом элемента ИЛИ 8, к второму входу которого подключен выход первого элемента И 9, у которого к первому входу подключен выход стар. шего разряда реверсивного счетчика 10, к третьему входу -.выход второго элемента И 11, Первый выход первого элемента управления 12 подключен к R -входам регистров хранения 4 и 5 и к второму R-входу реверсивного счетчика 10, Выход элемента ИЛИ 8 соединен с ЕХОДОМ второго элемента управления 13, первый выход которого соединен с Л/-входом управления блока памяти 6 и с первь М R- входом реверсивного счетчика 10, выход обратного переноса которого подключен к первым входам второго П и третьего 14 элементов И, вторые входы которых соединены соответственно.с первым и вторым выходами .распреде. лителя импульсов 15.Тактоньш вход распределителя импульсов 15 соединен . вторым выходом делителя частоты 16,вх дом соединенного с выходом генератоpa тактовых импульсов 17, Стробирующий вход распределителя импульсов 15 соединен с выходом элемента НЕ 18 и вторым входом четвертого -элемента И 19, первый вход которого подключен к третьему выходу распределителя импульсов 15. Вход элемента НЕ 18 соединен с первым входом пятого элемента И 20, Входом разрешения записи блока памяти 6j .вторым в.ходом первого элемента И 9 и вторым выходом первого элемента управления 2, третий выход которого соединен с входом запуска аналого-цифрового преобразователя 3, Первый выход делителя частоты 16 соединен с вторым входом первого элемента управления 12 и вторым входом пятого элемента И 20, выход которого соединен с суммирующим входом реверсивного счетчика 10, вычитающий вход которого соединен с выходом четвертого элемента И 19, информационный выход - с вторым информационным входом блока 6 памяти, информационный вход - с вторым выходом блока памяти 6, управляющий вход с выходом третьего элемента И 14. Второй выход второго элемента управления 13 соединен с первым входом первого элемента управления 12, третий вход которого соединен с шиной 21 сигнала Сброс, а четвертыйвход - с шиной 22 сигнала Пуск. Указанные сигналы поступают от внешних устройств. Третий вьтход второго ;,элемента управления 13 соединен с :шиной 23 сигнала запуска развертки, а четвертый выход. - с адресным входом блока памяти 6, первый выход которого через цифроаналоговьй преобразователь 24 подключен к шине аналогового выхода 25. Первый и второй выходы блока памяти 6 подключены к шине цифрового выхода 26. Первьй элемент управления 12 включает в себя одновибраторы 27 и 28, RS - триггер 29, элемент И 30 и RS-триггер 31, причем первый вхоД через одновибратор 27 подключен к R - входам триггеров 29 и 31, второй вход подключен к первому входу элемента И 30, второй вход которого соединен с выходом RS -триггера 31 а выход - с третьим выходом. Третий вход подключен к S-входу RS -триг гера 29, второму R- входу RS триггера 31 и через одновибратор 28 к первому выходу . Четвертый вход подключен к S-входу RS -триггера i 31, выход триггера 29 соединен с вторым выходом.

71

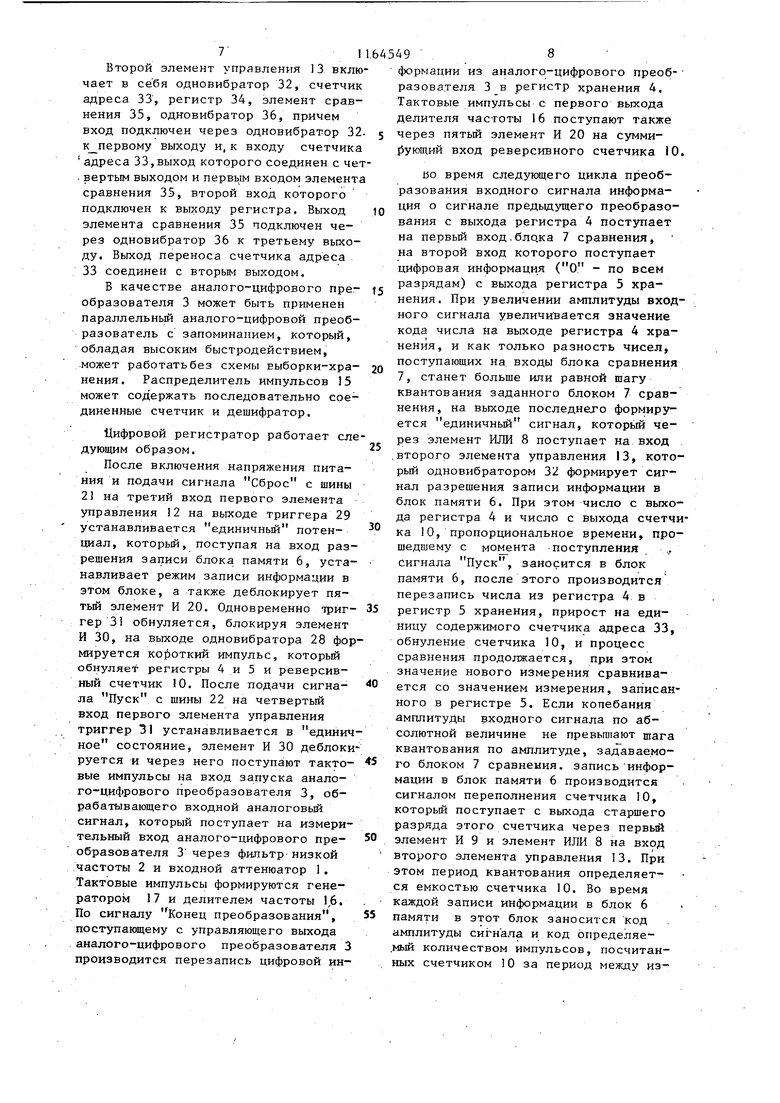

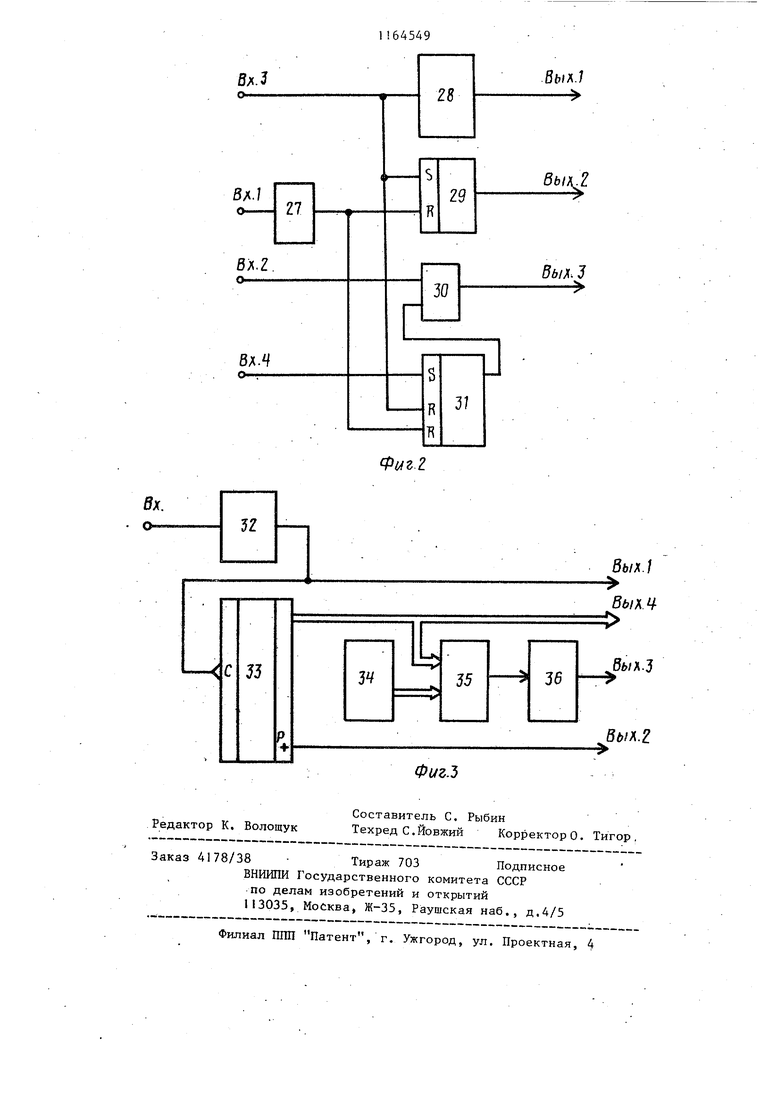

Второй элемент управления 13 включает в себя одновибратор 32, счетчик адреса 33, регистр 34, элемент сравнения 35, одновибратор 36, причем вход подключен через одновибратор 32 к первому выходу и, к входу счетчика адреса 33,выход которого соединен с чет. вертым выходом и первым входом элемента сравнения 35, второй вход которого подключен к выходу регистра. Выход элемента сравнения 35 подключен через одновибратор 36 к третьему выходу. Выход переноса счетчика адреса 33 соединен с вторым выходом.

В качестве аналого-цифрового преобразователя 3 может быть применен параллельный аналого-цифровой преобразователь с запоминанием, который, обладая высоким быстродействием, может работать без схемы выборки-хранения. Распределитель импульсов 15 может содержать последовательно соединенные счетчик и дешифратор.

Цифровой регистратор работает следующим образом.

После включения напряжения питания и подачи сигнала Сброс с шины 21 на третий вход первого элемента управления 12 на выходе триггера 29 устанавливается единичньй потенциал, который, поступая на вход разрешения записи блока памяти 6, устанавливает режим записи информации в этом блоке, а также деблокирует пятый элемент И 20. Одновременно триггер 31 обнуляется, блокируя элемент И 30, на выходе одновибратора 28 формируется ко)откий импульс, который обнуляет регистры 4 и 5 и реверсивный счетчик 10. После подачи сигнала Пуск с шины 22 на четвертьм вход первого элемента управления триггер 31 устанавливается в единичное состояние, элемент И 30 деблокируется и через него поступают тактовые импульсы на вход запуска аналого-цифрового преобразователя 3, обрабатывающего входной аналоговьй сигнал, который поступает на измерительный вход аналого-цифрового преобразователя 3 через фильтр низкой частоты 2 и входной аттенюатор 1. Тактовые импульсы формируются генератором 17 и делителем частоты 1,6. По сигналу Конец преобразования, поступающему с управляющего выхода аналого-цифрового преобразователя 3 производится перезапись цифровой ин45498

формации из аналого-цифрового преоб- разова.теля 3 в регистр хранения 4. Тактовые импульсы с первого выхода делителя частоты 16 поступают также 5 через пятьй элемент И 20 на сумми15ующий вход реверсивного счетчика 10.

во время следующего цикла преобразования входного сигнала информация о сигнале предыдущего преобразования с выхода регистра 4 поступает на первый вход.бло.ка 7 сравнения, на второй вход которого поступает цифровая информация (О - по всем разрядам) с выхода регистра 5 хранения . При увеличении амплитуды входного сигнала увеличивается значение кода числа на выходе регистра 4 хранения, и как только разность чисел, поступающих на входы блока сравнения 7, станет больше или равной шагу квантования заданного блоком 7 сравнения, на выходе последнего формируется единичньй сигнал, которьм через элемент ИЛИ 8 поступает на вход второго элемента управления 13, который одновибратором 32 формирует сигнал разрешения записи информации в блок памяти 6. При этом число с выхода регистра 4 и число с выхода счетчика 10, пропорциональное времени, прошедшему с момента -поступления ,, сигнала Пуск, заносится в блок памяти 6, после этого производится перезапись числа из регистра 4 в регистр 5 хранения, прирост на единицу содержимого счетчика адреса 33, обнуление счетчика 10, и процесс сравнения продолжается, при этом значение нового измерения сравнивается со значением измерения, записанного в регистре 5. Если колебания амплитуды входного сигнала по абсолютной величине не превьшгают шага квантования по амплитуде, задаваемого блоком 7 сравнения, записьинформации в блок памяти 6 производится сигналом переполнения счетчика 10, которьй поступает с выхода старшего разряда этого счетчика через первьй

элемент И 9 и элемент ИЛИ 8 на вход второго элемента управления 13. При этом период квантования определяется емкостью счетчика 10. Во время

каждой записи информации в блок 6

памяти в этот блок заносится код амплитуды сигнала и код определяе.мьй количеством импульсов, посчитанных счетчиком 10 за период между измерениями, что необходимо для одно- , значного соответствия между амплитудными и временными параметрами регистрирующего сигнала. .

После заполнения, всех ячеек блока 6 памяти на выходе переноса счетчика адреса 33 появляется сигнал, который через одновибратор 27 обнуляет Триггеры 29 и ЗГ цервого элемента управления 12, т..е, происходит запрет прохождения пусковых импульсов для аналого-цифрового преобраз.ователя 3, блок 6 памяти переключается в режим чтения,- первый и пятьй (.9 и 20 1 элементы И заблокируются, .а четвертый элемент И 19 и распределитель импульсов 15 деблокируется. Тактовые импульсы с второго выхода делителя частоты 1б.бУдут поступать на вход распределителя импульсов 15, После появления импульса на его первом выходе этот импульс через второй элемент И 11 и элемент ИЛИ 8 поступит на вход второго элемента управления. 13,который сформирует сигнал обращения к блоку памяти 6 на выходе .одновибратора 32, После информация будет считана из первой ячейки . блока 6 памяти, первым импульсомjnoc тупившим с второго, выхода распределителя импульсов. 15, через третий зле мелт И 14 будет произведена запись . кода с второго выхода блока памяти 6 соответствующего временному интервалу между соседними измерениями, в ревврсивньй счетчик 10, при этом на втором его выходе установится нулевой потенциал, а второй 1 1 и тре- тий 14, элементы И заблокируются. .С третьего выхода .распределителя импульсов 15 будут поступать импульсы через четвертьй элемент И 19 на вы- . читающий вход реверсивного счетчика 0. После на этотвход поступит количество импульсов, соотвётствующее коду, считанному с второ-го выхода блока 6 памяти , т.е. будет выполнена временная растяжка зарегистрированного сигнала, на втором

выходе .реверсивного счет,чика 10 появится единичный потенциал, который деблокирует второй 11 и третий 14 4 элементы И, и при появлении импуль- са на первом выходе распределителя импульсов 15 произойдет считывание следующей ячейки блока 6 памяти. По импульсу с второго выхода распределителя импульсов 15 произойдет перезапись информации с второго выхода блока 6 памяти в реверсивный счетчик 10, и процесс временной растяжки повторится, В режиме воспроизведения содержимое блока 6 памяти, поступающее с первого выхода на вход цифроаналогового преобразователя 24, будет считываться через интервал времени, определяемьм содержимым блока памяти 6, поступающим с второ-.

го выхода этого блока. Вре.менн.ую диаграмму зарегистрированного сигнала . получить,, подавая сигнал с шины 25 на вход вертикального отклонения устройства отображения.аналоговой информации (электронный- осциллограф, графопостроитель) и запуская развертку сигналом, поступающим с третьего выхода второго элемента управления 13 на шину 23, Этот сигнал означает начало памяти и формируется одновибратором 36 в момент,когда содержимое счетчика а дреса 33 будет равно содержимому регистра 34, в котором записан код.О. .,.0. Для вое-, произведения зарегистрированного сигнала без дополнительного растяжения необходимо, чтобы частота тактовых импульсов на втором выходе делителя частоты 1 6 бьша в три раза вьщ1е частоты импульсов на первом еговыходе.

Таким образом, предлагаемое устройство позволяет воспроизвести исследуемьш сигнал в аналоговой форме в реальном масштабе времени, что необходимо для оперативного контроля регистрации исследуемого сигнала, экономя тем самым рабочее время электронной вычислительной машины, необходимое для обработки информации.

0иг.1

5л.

Вык.1

.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ получения водорода или азотоводородных смесей из углеводородов или газовых смесей | 1926 |

|

SU7502A1 |

| Описание и применение | |||

| Фирма | |||

| Бриаль и.Къер, Дания, 1972 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой регистратор | 1980 |

|

SU920379A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-06-30—Публикация

1984-01-09—Подача