Изобретение относится к вычислительной технике и автоматике и может быть использовано при конструировании устройств управления коммутационной техники.

Цель изобретения - расширение функциональных возможностей за счет логических операций в выбранном языке.

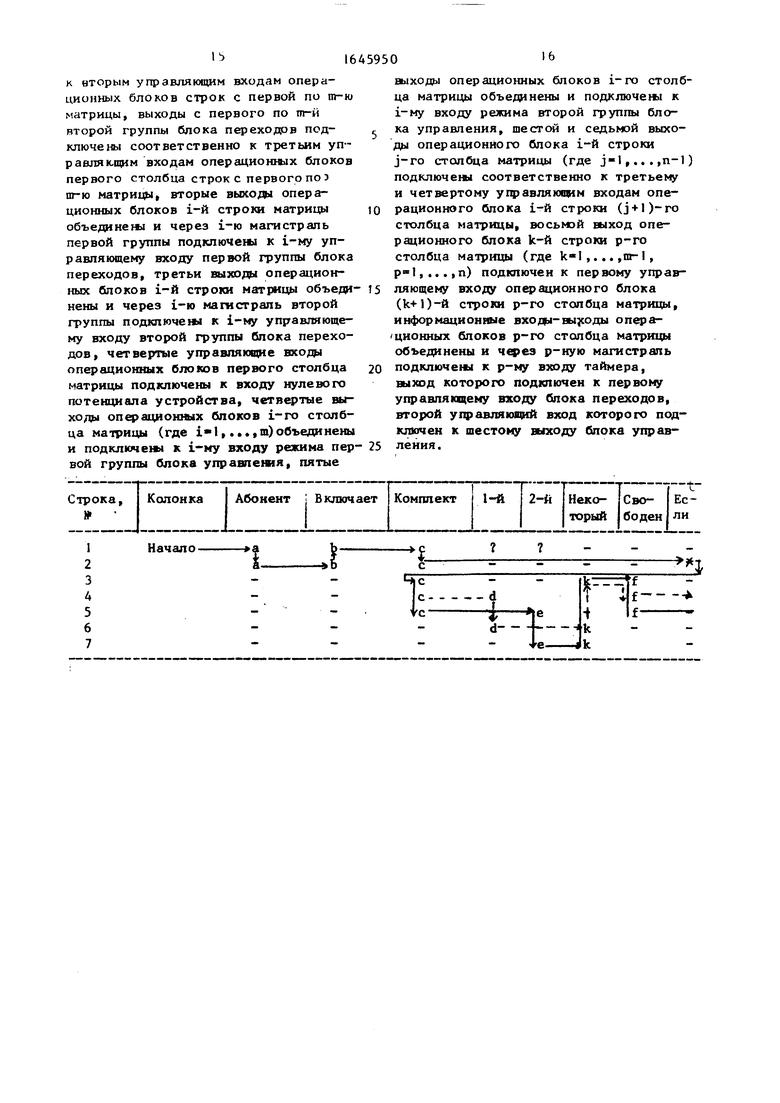

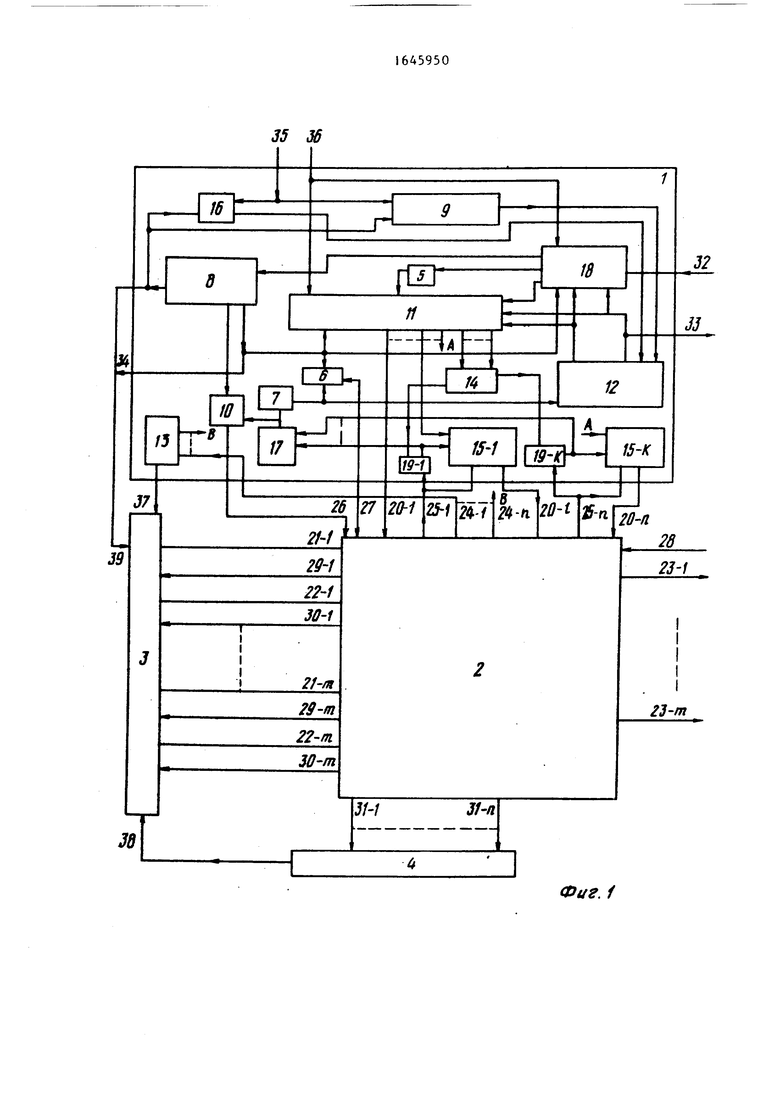

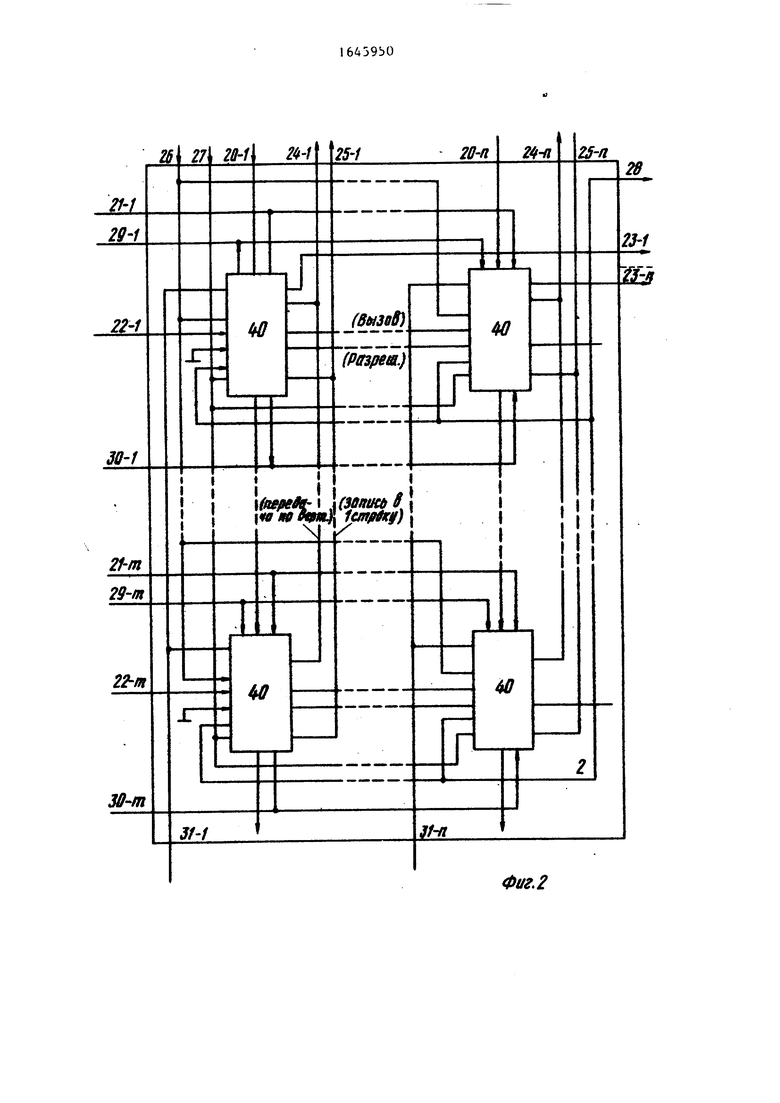

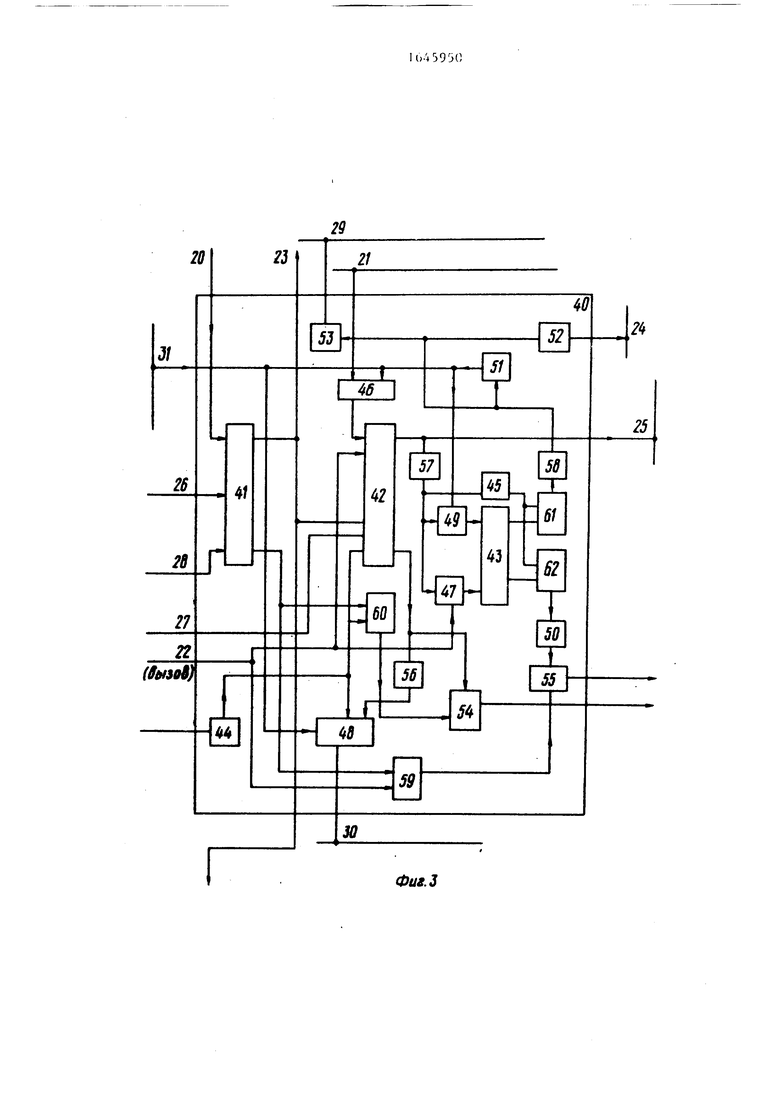

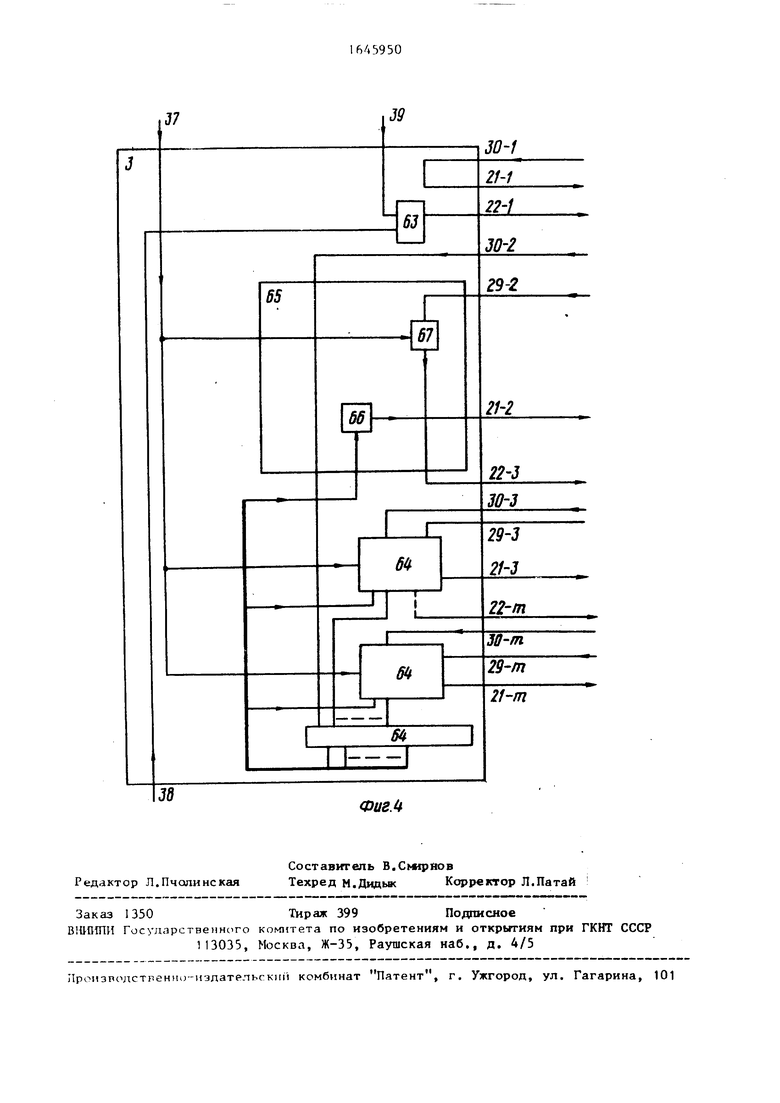

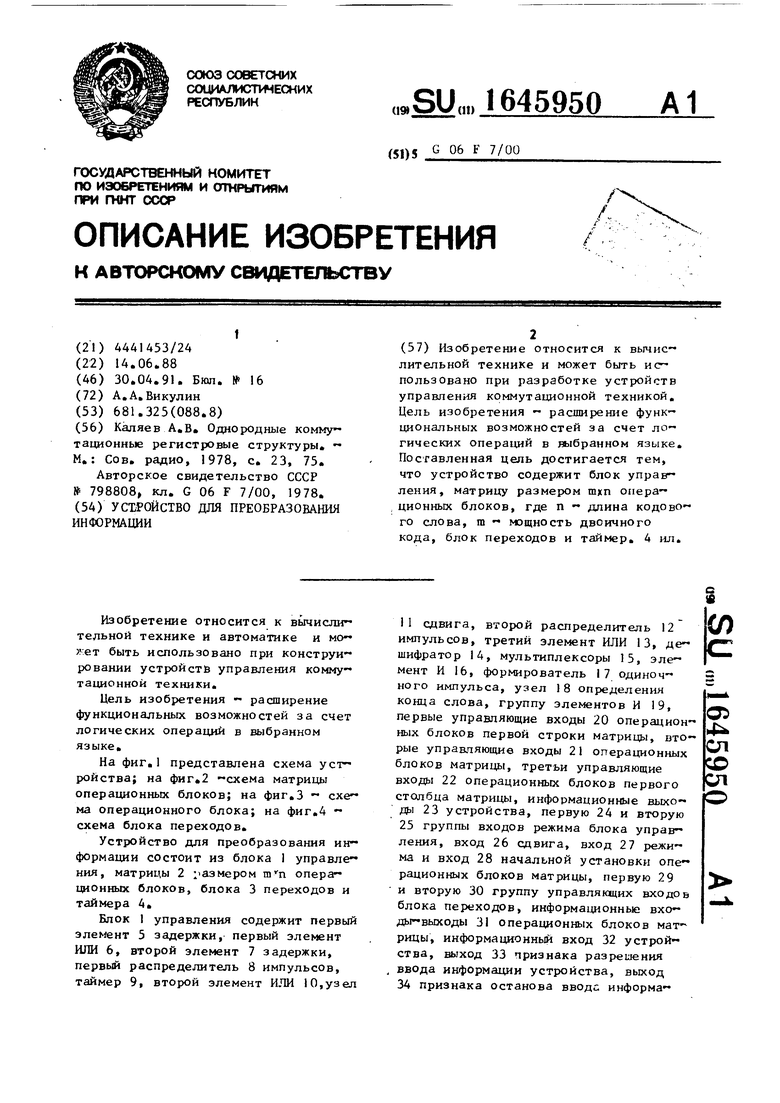

На фиг.1 представлена схема устройства; на фиг.2 -схема матрицы операционных блоков; на фиг.З - схема операционного блока; на фиг.4 - схема блока переходов.

Устройство для преобразования информации состоит из блока 1 управления, матрицы 2 размером ш п операционных блоков, блока 3 переходов и таймера 4.

Блок 1 управления содержит первый элемент 5 задержки, первый элемент ИЛИ 6, второй элемент 7 задержки, первый распределитель 8 импульсов, таймер 9, второй элемент ИЛИ 10,уз ел

11 сдвига, второй распределитель 12 импульсов, третий элемент ИЛИ 13, дешифратор 14, мультиплексоры 15, элемент И 16, формирователь 17 одиночного импульса, узел 18 определения конца слова, группу элементов И 19, первые управляющие входы 20 операционных блоков первой строки матрицы, вторые упраапяющие входы 21 операционных блоков матрицы, третьи управляющие входы 22 операционных блоков первого столбца матрицы, информационные выходы 23 устройства, первую 24 и вторую 25 группы входов режима блока управления, вход 26 сдвига, вход 27 режима и вход 28 начальной установки one рационных блоков матрицы, первую 29 и вторую 30 группу управляющих входов блока переходов, информационные входы-выходы 31 операционных блоков мат рицы, информационный вход 32 устройства, выход 33 признака разрешения ввода информации устройства, выход 34 признака останова вводе информаi СЛ

оэ -и

СП

со ел

ций устройства, вход 35 режима уст ройства, тактовьй вход 36 устройства, информационный вход 37, первый 38 и второй 39 управляющие входы блока переходов.

Матрица операционных блоков выпол- нена на операционных блоках 40.

Операционный блок содержит с пер вого по третий триггеры 41-43, два элемента НЕ 44 и 45, с первого по четвертый элементы И 46-49, с перво- го по четвертый формирователи 50-53 одиночного импульса, первый 54 и второй 55 элементы ИЛИ, первый 56, второй 57 и третий 58 элементы задержки, а также с первого nd четвертый элементы И-НЕ 59-62.

Блок 3 переходов состоит из элемента ИЛИ 63, узла 64 указания старшей эдиницы и узлов 65 интегрирования , каждый из которых содержит интегратор 66 и элемент И 67.

Рассмотрим множество двоичных слов длиной п.

Каждое кодовое слово, представляющее собой кортеж символов а.,...,а (где . . . , а п могут принимать значения О и 1), рассмотрим как вектор в п-мерном векторном пространст- ве, при этом символы а.,...,а компоненты этого вектора.

Для наглядности компоненты вектора, имеющие значение 1, обозначим буквами О,Ь,Ј,.... Если значение ком- понента равно нулю, ставим прочерк (-) или делаем пропуск.

Поскольку кодовые слова рассматриваем как векторы, то при преобразовании могут сопоставляться только идентичные компоненты векторов. Например, если имеется кодовое слово А (Q Ьс - - -) и разрешенное кодовое слово В (О Ьс - -), то, сопоставив идентичные компоненты этих кодовых слов (векторов), можно сделать

вывод, что кодовое слово A (qbc

также входит в множество разрешенных слов.

Пусть требуется определить истинность высказывания A (obc - ) если известны высказывания В

(obC), С (- -С- -Ј -) и

D (- - С- i -) i причем В выполняется (имеет смысл) только в том случае если выполняется С (истинность В зависит от наличия С).

Запишем эту зависимость как В С ,

где знак и

И.. 1

означает если или к

при условии выполнения

Истинность высказывания С проверяется с помощью высказывания D.

Запишем процесс проверки истинности высказывания А в виде: Номер

(I)

а Ьс

а be - - -с- - - с -

строки

1

2

А В С

5

0

5

0

35

40

4АаЬс

При преобразовании (1) производятся две проверки: вначале по компонентам а Ь С устанавливается соответствие между высказываниями аЬ с - - - - и obc - - - в первой и во второй строках, а затем по компонентам С и Ј устанавливается соответствие между высказываниями - - С - - i во второй и третьей строках. Признаком второй проверки служит знак В четвертой строке записан результат преобразования Только при наличии соответствующих компонентов в строках 1 и 2, 2 и 3 можно получить утвердительный ответ, что высказывание Qbc истинно, т.е. высказывание А истинно, если истинно высказывание В, а высказывание В истинно, если выполняется условие С, которое выполняется при наличии высказывания D.

Строку 2 можем записать в виде строчки так, чтобы в одной колонке находились одни и те же компоненты вектора таким образом: Номер

5

строки

1

2 3 4

а Ь с

а Ь с

- -сi

сf

а Ь с

(2)

В этом случае при преобразовании в соответствии с (2) вначале производится сопоставление наличия идентичных компонентов векторов в строках 1 и 2. В случае полного совпадения компонентов соответствующих векторов в этих строках производится сопоставление наличия идентичных компонентов в строках 3 и 4. Если и в этом случае выявлено полное совпадение идентичных компонентов векторов, то можно утверждать, что высказывание А истинно потому, что оно соответствует высказыванию В и условию , причем С истинно, так как существует D.

Представление символов кодовых слов как компонентов соответствуемых векторов позволяет использовать указанные символы для обозначения некоторых смысловых единиц. Пусть, например, в преобразовании (2) введенные символы несут следующую смысловую нагруз ку:

-символ а обозначает Абонент

-символ в - Включает

-символ с - Канальный комплект ;

- символ V

- символ

II 11 И

Свободен.

При этих обозначениях преобразование (2) записывается следующим образом:

абонент включает комплект абонент включает комплект если

комплект свободен(3) комплект свободен

абонент

включает

комплект

Таким образом, на смысловом уровне преобразование (3) позволяет установить истинность первой посыпки: абонент включает комплект

Пусть имеется несколько канальных комплектов (комплектов), один из которых, если он свободен, должен включить абонент. В связи с этим дополнительно введем следующие обозначен кия:

-символ d означает 1-й;

-символ е - 2-ii;

-символ k - некоторый.

Требуется определить, какой из канальных комплектов может включить абонент.

Это выражение запишем в виде высказывания:

А (аЬс ),(4)

где знак означает, что символы, следующие за символом с, подлежат уточнению, определению..

Ответ на поставленный вопрос получают с помощью преобразования, приведенного в таблице.

Но записи преобразования (см. таблицу) можно проследить процесс фор

мирования новых кодовых слов, записанных в строках 8 и 9.

Стрелками показана последовательность сравнения символов разных кодовых слов. В соответствии со всеми символами, показанными в таблице, можно сформировать поле первичных сигналов, причем координата записи

каждого первичного сигнала должна определяться расположением соответ- ствукщего символа в преобразовании по таблице.

Далее начинается процесс решения,

5 который заключается в том, что последовательно формируют пиле вторичных сигналов, определяющее решение поставленной задачи. Вторичные сигналы изображены стрелками. Каждый

0 последующий вторичный сигнал формируется при сопоставлении предыдущего вторичного сигнала с очередным первичным сигналом, причем при формировании каждого вторичного сигнала

5 производится изменение направления распространения сигнала.

При этом каждый последующий вторичный сигнал может быть сформирован только если предварительно был сфор0 мирован предыдущий вторичный сигнал в упорядоченной группе сигналов.

В соответствие с таблицей имеется следующая последовательность операций преобразования.

с Вторичный сигнал, соответствующий стрелке Начало, сопоставляется с сигналом, соответствующим символу q первой строки, в результате чего формируют следующий, вторичный сигнал,

о который распространяется в своем столбце. Этот вторичный сигнал сопоставляется с первичным сигналом, соответствующим символу q, расположенному в первом столбце на второй

5 строке, при этом формируется новый вторичный сигнал, распространяющийся по второй строке. Далее вторичные сигналы последовательно формируются при сопоставлении с первичными сигС налами символов Ь второй строки, V первой строки, с первой строки, с второй строки, второй строки.

Затем по вторичному сигналу, со5 ответствующему знаку V, производится смена строки распространения сигнала, сигнал начинает распространяться по третьей строке, где по сопоставлению вторичного сигнала с

первичным, соответствующим символу с третьей строки, формируется но- вторичный сигнал, распространякг- щийся по вертикали.

Далее вторичный сигнал может распространяться по двум путям. Первый путь распространения сигнала образуется при последовательном формировании вторичных сигналов, соответствующих символам с четвертой строки, J четвертой строки, d шестой строки, шестой строки, | третьей строки, f третьей строки, f четвертой строки.

Второй путь распространения сигнг ла образуется при последовательном формировании вторичных сигналов, соответствующих символам с пятой строки, е пятой строки, е седьмой строки, V седьмой строки, k третьей строки, f третьей строки, f пятой строки.

Концом преобразования является формирование вторичных сигналов в соответствии со всеми первичными сигналами в соответствующей сроке. В преобразовании по таблице такой строкой является строка 3. Результат данного преобразования используется следующим образом: необходимо вместо одного из знака в первой строке записать символы, найденные в результате преобразования. Пусть, например, решение задачи проведено по первому пути, т.е. найден символ d. Этот символ должен быть записан в первую строку вместо знака , расположенного в том же столбце, что и найденный символ d. На основании этих преобразований формируется соответствующий первичный сигнал.

4 Устройство работает следующим образом.

В исходном состоянии триггеры 41 и 42 в блоках 40 устанавливаются в нулевое состояние. На вход 33 подается импульсный сигнал Пуск извне.

Поступающая на вход 32 блока 1 информация через узел 18 подается на информационный вход узла 11 сдвига. Одновременно через вход 36 блока 1 на тактовый вход блока 11 поступают тактовые импульсы. Таким образом, в узел 11 сдвига по мере поступления информации происходит последовательная запись соответствующих кодовых

10

15

6459508

слов. Окончание каждого кодового слова фиксируется узлом 18, который через элемент 5 задержки выдает сигнал на подключение очередного незаполненного сдвигающего регистра узла 11. Окончание передачи смысловой конструкции также фиксируется узлом 18, который при этом воспринимает кодовую комбинацию, соответствующую знаку препинания в выбранном языке, и выдает сигнал на включение распределителя 8.

Сообщение может состоять из нескольких слов, отделяемых1 друг от друга промежутками. В этом случае узел 18 должен фиксировать эти промежутки, например, в случае четырехбуквенного кода промежуток может 2Q кодироваться 0000. Команда на начало записи в этом случае подается из узла 18 по фиксации промежутка между кодовыми словами.

Сигнал с первого выхода распределителя 8 обеспечивает прекращение записи в сдвигающие регистры сдвига узла 1 1 новых символов и его останов, останов определителя 18, установку в исходное состояние всех триггеров 42 в блоках 40.

Импульс с второго выхода распределителя 8 через элемент ИЛИ 10 поступает на соответствующие входы всех триггеров 41. Одновременно иное Формация из узла 11 сдвига поступает на информационные входы триггеров 41. При этом происходит сдвиг всей информации, записанной на триггерах 41 таким образом, что информация из первой строки матрицы 2 переписывается во вторую строку, из второй - в третью и т.д., а в первую строку матрицы записывается информация, снимаемая с выходов узла 11 сдвига.

В матрицу 2 предварительно записывается программа. Эта программа образуется полем первичных сигналов, каждый из которых отождествляется с включением триггера 41 в соответствующем блоке 40.

25

30

40

45

50

Программа в устройство вводится через вход 32 устройства. Для принудительной записи информации на вход 35 устройства поступает сигнал, который поступает на таймер 9, запрещая его работу, и на соответствующий вход элемента И 16, разрешая его работу.

При этом сигнал с выхода элемента И 16 поступает на второй вход режима распределителя 12. Импульс с первого выхода производит установку в исходное состояние узла 11 сдвига и узла 18, а импульс с второго выхода разрешает работу узлов 11 и 18, и, таким образом, процесс записи информации возобновляется.

Процесс записи информации в матрицу 2 (программирование ее) происходит и при решении каких-либо конкретных задач. После того, как информация, соответствующая некоторой смысловой конструкции, записалась в узел 11, запускается распределитель 8, импульс с выхода которого останавливает движение информации в узлах I1 и 18. По импульсу с второго выхода в первую строку матрицы 2 записывается информация, снимаемая с выходов узла 11 сдвига. Следующий импульс с третьего выхода распределителя 8 обеспечивает запуск таймера 9, поступает на вход элемента И 16 и на вход 39 блока 3 и через элемент ИЛИ 63 обеспечивает начало процесса преобразования сигнала в матрице 2.

Импульсный сигнал через вход 22-1 поступает на соответствующий вход триггер 42 блока 40 первой строки матрицы.

При этом триггер 42 может изменить свое состояние только в том случае, если триггер 41 переведен в единичное состояние. В том случае, если триггер 41 находится в нулевом состоянии, сигнал с инверсного выхода триггера 41 поступает на первый вход элемента И-НЕ 58, разрешая прохождение через этот элемент сигнала вызова. При этом сигнал вызова, поступивший через вход 22, проходит через элементы И-НЕ 59 и ИЛИ 55 и поступает на выход вызова. Далее сигнал поступает в следующий операционный блок 40 первой строки матрицы 2. Так сигнал вызова проходит по блокам 40 этой строки 1 до тех пор, пока в каком-либо блоке 40 не окажется переведенным в единичное состояние триггер 41. При этом триггер

41этого блока 40 меняет свое состояние.

Когда сигнал с выхода триггера

42через элемент 58 задержки и элемент НЕ 45 поступает на второй вход элемента И-НЕ 60, на его выходе появляется сигнал, которым череч элемент 57 задержки поступает на рклю- чение формирователей 51-53 одиночного импульса.

Сигнал с выхода формирователя 51 поступает на первый вход элемента И 47, на второй вход которого поступает запрещающий сигнал с выхода д элемента 58 задержки.

Сигнал с выхода формирователя 5I поступает также на входы-выходы 31 . В том случае, если в столбце, к которому относится данная магист- 5 раль, есть хотя бы один блок 40, в котором триггер 41 находится в единичном состоянии (т.е. в этот блок записана информация), то создаются условия для срабатывания в этом бло- Q ке триггера 42, поскольку с прямого выхода триггера 41 этого блока на вход триггера 42 поступает сигнал с уровнем 1, разрешая срабатывание триггера 42. При этом импульс- 5 ный сигнал из соответствующей магистрали 31 поступает на первый вход элемента И 48 этого блока.

На второй вход элемента И 48 этого блока через элемент НЕ 44 посту- 0 пает сигнал разрешения (этот сигнал поступает с предыдущего в данной строке блока, при этом для первого в строке блока в качестве такого сигнала используется опорный потенциал).

На третий вход элемента И 48 через элемент 56 задержки поступает разрешающий сигнал с инверсного выхода триггера 42. Таким образом, в рассматриваемом случае на всех входах о элемента И 48 присутствуют разрешающие сигналы.

Элементы И-НЕ 61 и ИЛИ 54 предназначены для передачи на выход сигнала разрешения. В том случае, если 5 триггер 42 сработал, сигнал с его прямого выхода поступает через элемент ИЛИ 54 на выход разрешения. Если же триггер 41 не сработал, то при поступлении на вход разрешения соот- ветствующего сигнала, он передается через эЛементы И-НЕ 61 и элемент ИЛИ 54 на выход разрешения.

При выдаче из соответствующего бло ка 40 сигнала отклика, этот сигнал 5 поступает в блок 3 на входы узла 64.

Узел 64 предназначен для пропускания на его выход только одного из нескольких сигналов, поступивших одновременно на его входы. При этом про5

и

пускается сигнал с наименьшим условным номером. Номер входа узла 64 соответствует номеру входа 30 так, что сигнал , поступающий на предадущий

вход, должен запрещать прохождение

сигналов, поступаюиих на все последующе входы.

Использование узла 64 дает первым ответом тот, который соответствует информации, пришедшей позже, поскольку сигнал с входа 30 с меньшим номером запрещает прохождение сигналов, поступаюиих с входов 30 с большим номером. Сигнал с выхода узла 64

через интегратор 66 поступает на вход 21. Интегратор 66 используется для устранения влияния на работу устройства кратковременных импульсов на выходе узла 64.

С выхода 21 импульс поступает на вход того блока 40 матрицы 2, с которого в узел 64 был послан сигнал отклика.

В этом блоке 40 рассматриваемый сигнал поступает на первый вход элемента И 46, на другой вход которого поступает импульс из магистрали 31, где находится данный блок 40. При этом элемент И 46 срабатывает и сиг- нал с его выхода поступает на соответствующий вход триггера 42, который переводится в единичное состояние.

Кроме того, импульсный сигнал из магистрали 31 поступает через элемент И 47 блока 40 на вход триггера 43.

Триггер 43 изменяет свое состояние, при этом сигнал с соответствую- щего выхода триггера 43 поступает на первый вход элемента И-НЕ 62, подготавливая его срабатывание. Элемент И-НЕ 62 срабатывает, когда на второй его вход поступает сигнал,

который формируется триггером 42.

Сигнал с выхода элемента И-НЕ 62 через формирователь 50 поступает на вход элемента ИЛИ 55, с зыхода которого подается па вход вызова, откуда сигнал а 1зова поступает на вход следующего блока 40 в данной строке матрицы 2, в которой триггер 41 находится в единичном состоянии.

Процесс преобразования сигнала в матрице 2 заканчивается, если во всех блоках 40 соответствующей строки, для всех первичных сигналов про- изведено формирование вторичных сиг

,

ю 15

20

2530

35

40 45

5055, 12этой строки

налов, т.е. для этой строки каждому включенному триггеру 41 должен соответствовать включенный триггер 42. Если на некотором выходе 25 появляется сигнал, соответствующий тому символу кодового слова, который уточняется в процессе решения задачи, то этот сигнал поступает на первые входы соответствующего элемента И 19. На второй вход указанного элемента И 19 поступает сигнал с выхода дешифратора 14. Этот сигнал также соответствует уточняемому символу кодового слова, записанного в узле 11. При этом на выходе элемента И 19 появляется сигнал, который поступает на один из входов формирователя 17, запуская его, и на первый управляющий вход мультиплексора 15, запрещая прохождение сигнала, поступающего с соответствующего выхода узла 11 на информационный вход мультиплексора 15 и разрешая прохождение сигнала, поступающего на вход 25 блока управления. Таким образом, уточненный сигнал поступает через мультиплексор 15 на выход 20. Одновременно на в 1ходе формирователя 17 появляется сигнал, который через элемент ИЛИ 10 поступает на вход 26 блоков 40 матрицы 2. При этом производится сдвиг всей информации в матрице 2 и запись новой информации в первую строку матрицы.

Если с помощью устройства ищется ответ на вопрос, поставленный к одной и той же части смысловой конструкции, то разрешение на выдачу сигнала, поступающего на второй вход элемента И 19, может быть реализовано в дешифраторе 14.

Так, например, если выбранный язык выражает субъективно-объектные отношения, как это имеет место в естественном языке, то вопрос может ставиться постоянно к одной и той же части речи. При этом необходимо заметить, что в этом случае информация, подаваемая на вход 32 устройства, должна быть предварительно соответствующим образом подготовлена. Например, если ставится вопрос: Какой аппарат должен быть включен, то на вход устройства 32 должна подаваться следующая конструкция: Аппарат должен быть включен какой. При этом вопросительное слово кап кой должно фиксироваться дешифратором 14 и при решении задачи заменяться словом, найденном при преобразовании сигнала в матрице. Результат записывается в первую строку и может быть выдан через выходы 23.

Сигнал с выхода формирователя 17 одиночного импульса поступает также на запуск распределителя 12 импульсов.

Сигналом первого выхода осуществляется сброс записанной информации в узлах 11 и 18, а сигналом с второго выхода осуществляется пуск узлов 11 и 18, и работа устройства повторяется.

Таймер 4 сбрасывается каждым импульсом, поступающим через магистрали 3 I на соответствующие его входы. Если таймер 4 досчитает до конца,

то на его выходе появляется импульс вызова, который поступает через элемент ИЛИ 63 блока 3 в первую строку матрицы 2 для возобновления процесса преобразования. Это происходит в том случае, если процесс решения поставленной задачи зашел в тупиковую ветвь дерева решений и импульс на магистрали 31 в течение длительного времени не появляется. Таймер 9 за- пускается распределителем 8 одновременно с началом преобразования сигнала и выдает импульс через более длительный промежуток времени, чем таймер 4. Появление этого импульса означает, что на основе имеющихся данных решение задачи невозможно, так как процесс решения не закончился в течение определенного промежутка времени. По этому импульсу запус- кается распределитель 12, который осуществляет сброс информации в узле 11 сдвига и в узле 18 и последующий запуск этих узлов.

Переход сигнала с данной строки на нижерасположенную строку осуществляется при включении операционного блока 40 данной строки, расположенной в столбце, соответствующему биту информации, являющемуся связкой между смысловыми конструкциями. При этом в этом блоке 40 формирователи 52 и 53 одиночного импульса выдают импульсы, которые поступают соответственно на выхода 24 и 25 (пере- дача ..по вертикали и горизонтали).

Импульсный сигнал через соответствующий выход 29 поступает на элемент И 67 блока 3 переходов, а сигнал

через выход 24 и элемент ИЛИ I3 поступает на вход 37 и далее на вт орой вход элемента И 67, который срабатывает и выдает импульсный сигнал на выход 22 (вызов строки), которая расположена под строкой, из которой был получен сигнал на вход 29.

Устройство позволяет производить логические операции в заранее выбранном языке, осуществлять самопрограммирование матрицы, а также осуществлять форматирование смысловых конструкций, записываемых в матрицу, за счет возможностей записи сложной смысловой конструкции в несколько строк матрицы.

Формула изобретения Устройство для преобразования информации, содержащее матрицу размером пут операционных блоков, где п - длина кодового слова, а т - мощность двоичного кода, отличающе е с я тем, что, с целью расширения Функциональных возможностей за счет логических операций в выбранном языке, оно содержит блок управления, блок переходов и таймер, причем информационный вход, тактовый вход, вход режима и вход начальной установки устройства подключены соответственно к первому входу режима, к тактовому входу, второму входу режима блока управления и входам начальной установки операционных блоков матрицы, информационные выходы с первого по m-й устройства подключены соответственно к первым выходам операционных блоков первой строки с первого по га-й столбцов матрицы, выхода признака разрешения ввода информации и признака останова ввода информации подключены соответственно к первому и второму выходам блока управления, третий выход которого подключен к входам сдвига операционных блоков матрицы, четвертый выход блока управления подключен к входам режима операционных блоков матрицы, пятый выход блока управления подключен к информационному входу блока переходов, выходы, с первого по n-й, блока управления подключены соответственно к первым управляющим входам операционных блоков первой строки с первого по п-и столбцов матрицы, выходы с первого по m-й первой группы блока переходов подключены соответственно

10

к вторым управляющим входам операционных блоков строк с первой по т-ю матрицы, выходы с первого по т-н второй группы блока переходов подключены соответственно к третьим управляющим входам операционных блоков первого столбца строке первого поэ пг-ю матрицы, вторые выходы операционных блоков i-й строки матрицы объединены и через i-ю магистраль первой группы подключены к i-му управляющему входу первой группы блока переходов, третьи выходы операционных блоков i-й строки матрицы объеди- 15 йены и через i-ю магистраль второй группы подключены к i-му управляющему входу второй группы блока переходов, четвертые управляющие входы операционных блоков первого столбца 20 матрицы подключены к входу нулевого потенциала устройства, четвертые выходы операционных блоков 1-го столбца матрицы (где ,...,т)объединены и подключены к i-му входу режима пер- 25 вой группы блока управления, пятые

1645950|6

выходы операционных блоков 1-го столбца матрицы объединены и подключены к i-му входу режима второй группы блока управления, шестой и седьмой выходы операционного блока i-й строки j-ro столбца матрицы (где j-l,...,n-l) подключены соответственно к третьему и четвертому управляющим входам операционного блока i-й строки (j-H)-ro столбца матрицы, восьмой выход операционного блока k-й строки р-го столбца матрицы (где ,...,m-l, ,...,п) подключен к первому управляющему входу операционного блока (k-H)-ft строки р-го столбца матрицы, информационные входы-выходы опера- ционных блоков р-го столбца матрицы объединены и через р-ную магистраль подключены к р-му входу таймера, выход которого подключен к первому управляющему входу блока переходов, второй управляющий вход которого подключен к шестому выходу блока управления .

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Однородная вычислительная среда | 1987 |

|

SU1587485A1 |

| Декодер линейных кодов,исправляющий стирания | 1982 |

|

SU1112554A1 |

| Декодер циклического кода | 1988 |

|

SU1599996A1 |

| Декодер линейного систематического кода | 1987 |

|

SU1534756A1 |

| СПОСОБ СЖАТИЯ ИНФОРМАЦИИ | 2010 |

|

RU2431918C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОГО СООБЩЕНИЯ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2179365C1 |

| Способ передачи факсимильных изображений с распознаванием символов | 1989 |

|

SU1695510A1 |

| Устройство для контроля кодовой комбинации | 1984 |

|

SU1439597A1 |

| УСТРОЙСТВО И СПОСОБ ДЛЯ ДЕКОДИРОВАНИЯ КОДА КОРРЕКЦИИ ОШИБКИ В СИСТЕМЕ СВЯЗИ | 2004 |

|

RU2280323C2 |

Изобретение относится к вычис- лительной технике и может быть ие пользовано при разработке устройств управления коммутационной техникой. Цель изобретения - расширение функциональных возможностей за счет ло- гических операций в выбранном языке. Поставленная цель достигается тем, что устройство содержит блок управления, матрицу размером mxn операционных блоков, где п - длина кодового слова, m - мощность двоичного кода, блок переходов и таймер. 4 ил.

Фиг.З

| Каляев А.В | |||

| Однородные коммутационные регистровые структуры | |||

| - М.: Сов | |||

| радио, 1978, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Однородная вычислительная среда | 1978 |

|

SU798808A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-30—Публикация

1988-06-14—Подача