4 СО СО СП

со

Изобретение относится к цифровой вычислительной технике и может быть использовано в аппаратуре передачи данных с повышенной достоверностью,

Целью изобретен™ является повышение достоверности контроля.

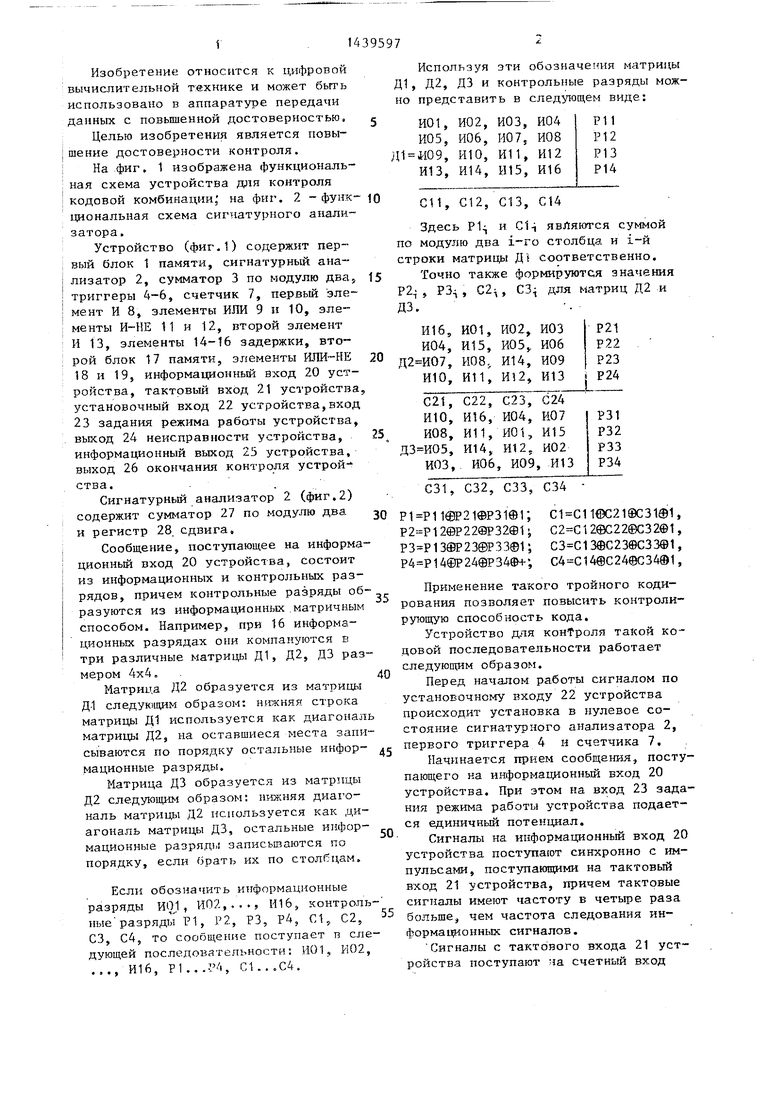

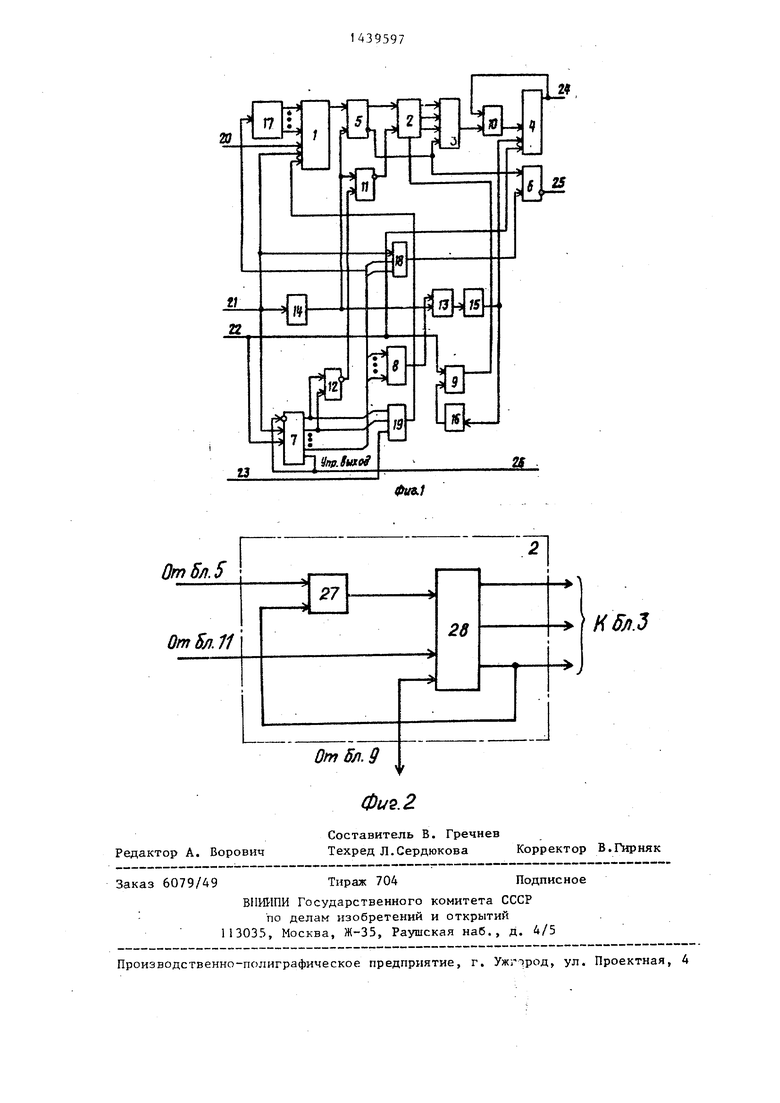

На фиг, 1 Изображена функциональная схема устройства для контроля кодовой комбинации; на фиг. 2 - функ- циональная схема сигнатурного анализатора .

Устройство (фиг,О содержит первый блок 1 памяти, сигнатурный анализатор 2, сумматор 3 по модулю два, триггеры 4-6, счетчик 7, первый элемент И 8, элементы ИЛИ 9 п 10, элементы 11 и 12, второй элемент И 13, элементы 14-16 задержки, второй блок 17 памяти, элементы 18 и 19, информационный вход 20 устройства, тактовый вход 21 устройства установочный вход 22 устройства,вход 23 задания режима работы устройства, выход 24 неисправности устройства, информационный выход 25 устройства, выход 26 окончания контроля устрой ства. .

Сигнатурный анализатор 2 (фиг,2) содержит сумматор 27 по модулю два. и регистр 28 сдвига.

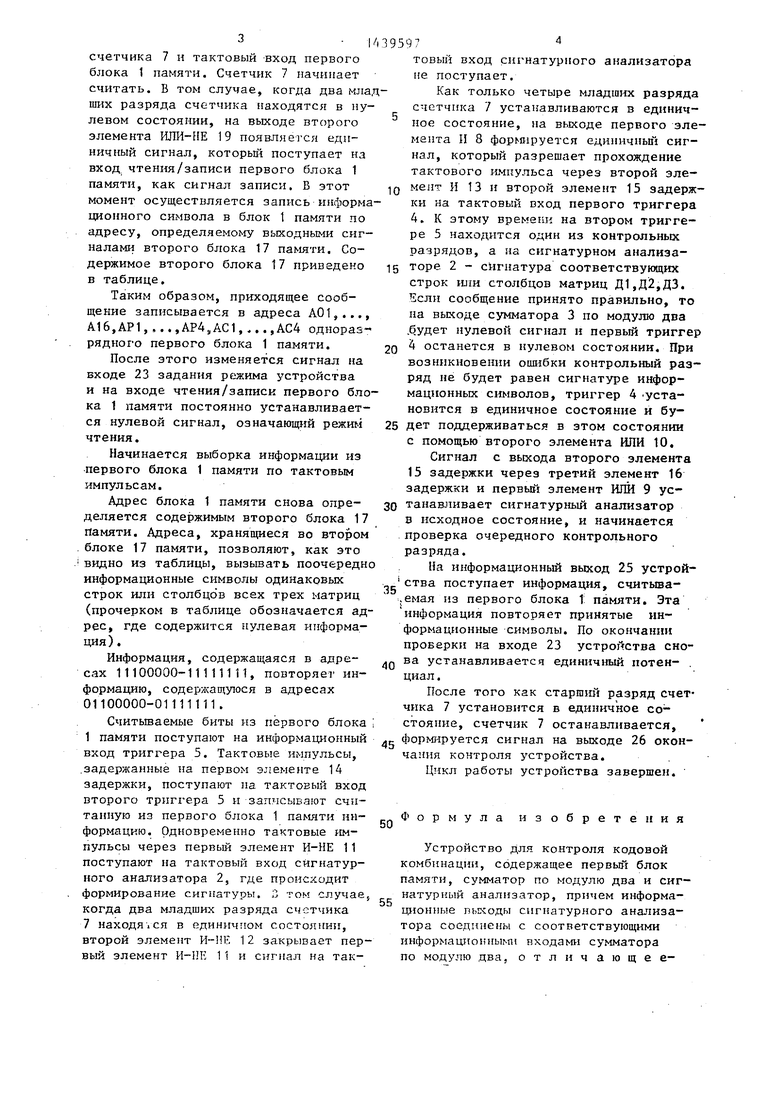

Сообщение, поступающее на информационный вход 20 устройства, состоит из информационных и контрольных разрядов, причем контрольные разряды образуются из информационных.матричным способом. Например, при 16 информационных разрядах они компануются в три различные матрицы Д1, Д2, ДЗ размером 4x4, .

Матрица Д2 образуется из матрицы Д-1 следуюцщм образом: нижняя строка матрицы Д1 используется как диагонал матрицы Д25 на оставшиеся места записываются по порядку остальные инфор- мационные разряды.

Матрица ДЗ образуется из матрицы Д2 следующим образом: диагональ матриЩ) Д2 используется как диагональ матрицы ДЗ, остальные нифор- мационные разряды записьпзаются по порядку, если брать их по столбцам.

Если обозначить информационные разряды HOj , И02,,.., HI 6, контроль ные разряды Р1, Р2, РЗ, Р4, С1, С2, СЗ, С4, то сообщение поступает в следующей последовательности . И01,, И02, ..., И16, Р1..,Р4, С1.,.С4,

Используя эти обозначения матрицы Д1, Д2, ДЗ и контрольные разряды можно представить в следующем виде:

И01, И02, ИОЗ,И04

И05, И06, И07,ИОВ

И09, И10, И11,И12

И13, И14, И15,И16

Р11

Р12 Р13 Р14

С11, С12, 013, С14

Здесь Р1 и C1-i являются суммой по модулю два i-ro столбца и i-й строки матрицы Д| соответственно.

Точно также формируются значения Р2 , РЗ. , С2, СЗ для матриц Д2 и ДЗ.

И01, И02, ИОЗ

И15, ИОЗ И06

H08j И14, И09

Р21 F22 Р23

И10, И11, И12, И13 i Р24

С22, С23, С24 И16, И04, И07 И11, ИО, И15 И14, И12, И02 И06, И09, И13

Р31 Р32 РЗЗ

Р34

€31, С32, СЗЗ, С34 Р1 Р11®Р21ФР31Ф1;С1 С11©С21®С31Ф1,

Р2 Р12®Р22®Р32®1;C2 Ci2®C22®C32©1,

РЗ Р1ЗШР23©РЗЗФ1;СЗ С1ЗФС23ФСЗЗШ1,

Р4 Р14ФР24®Р34Ф+;С4-- С14@С24©С34®1,

Применение такого тройного кодирования позволяет повысить контролирующую способность кода.

Устройство для контроля такой кодовой последовательности работает следуюш 1м образом.

Перед началом работы сигналом по установочному входу 22 устройства происходит установка в нулевое состояние сигнатурного анализатора 2, первого триггера 4 и счетчика 7,

Начинается прием сообщения, поступающего на информационный вход 20 устройства. При этом на вход 23 задания режима работы устройства подается единичный потенциал.

Сигналы на информационный вход 20 устройства поступают синхронно с импульсами, поступающими на тактовый вход 21 устройства, причем тактовые сигналы имеют частоту в четыре раза больше, чем частота следования информационных сигналов.

Сигналы с тактового входа 21 устройства поступают на счетный вход

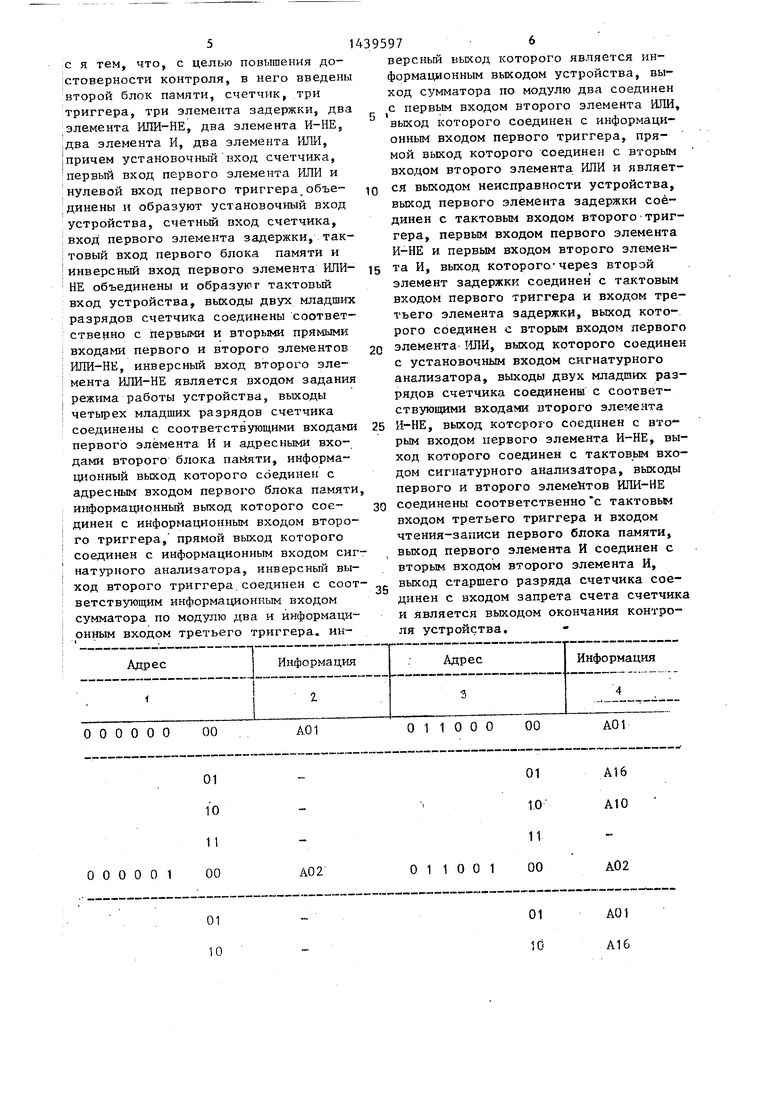

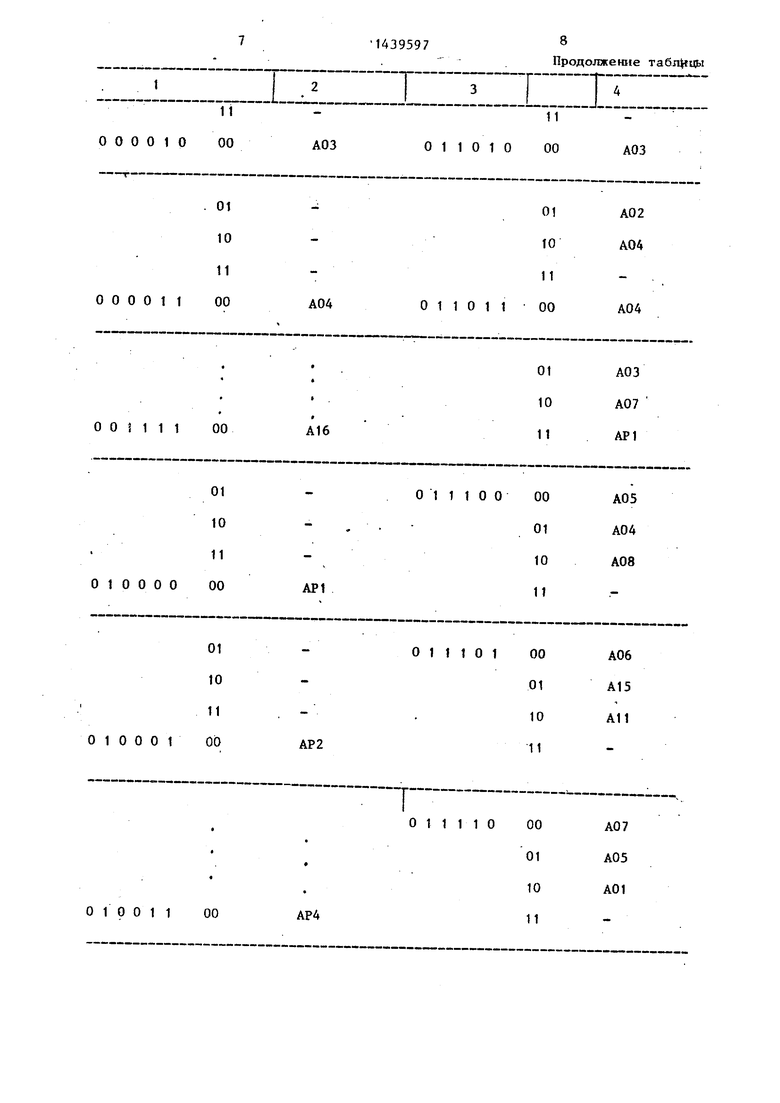

3- I

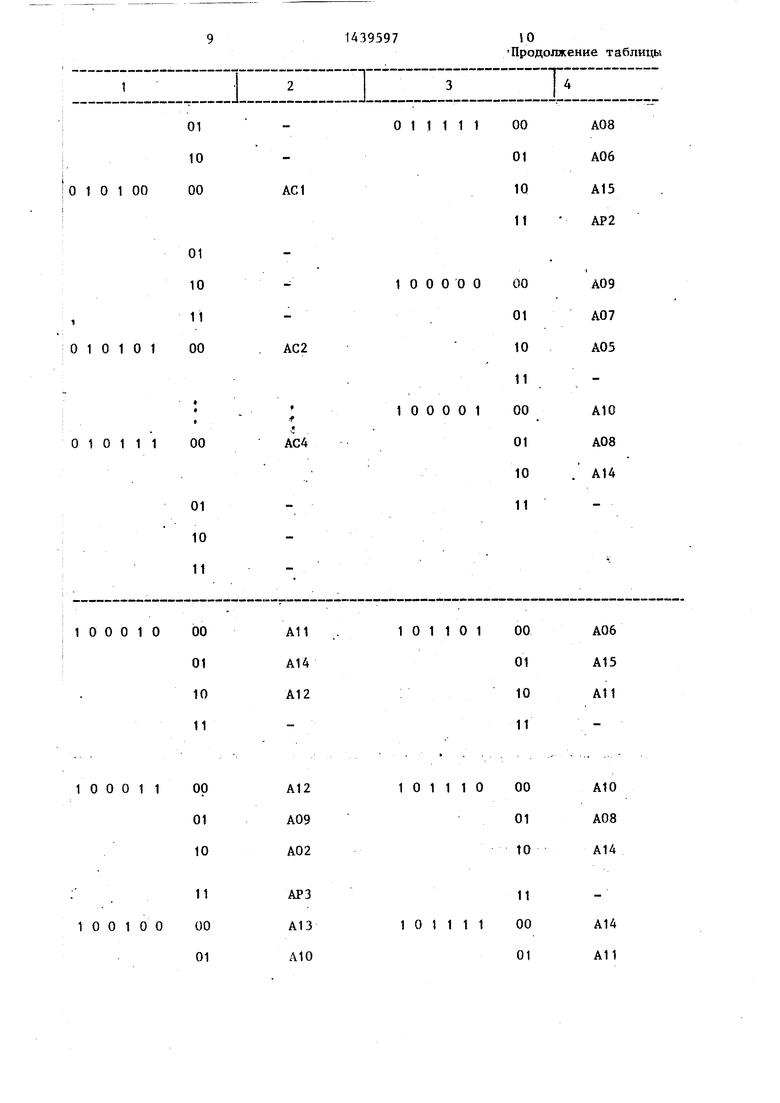

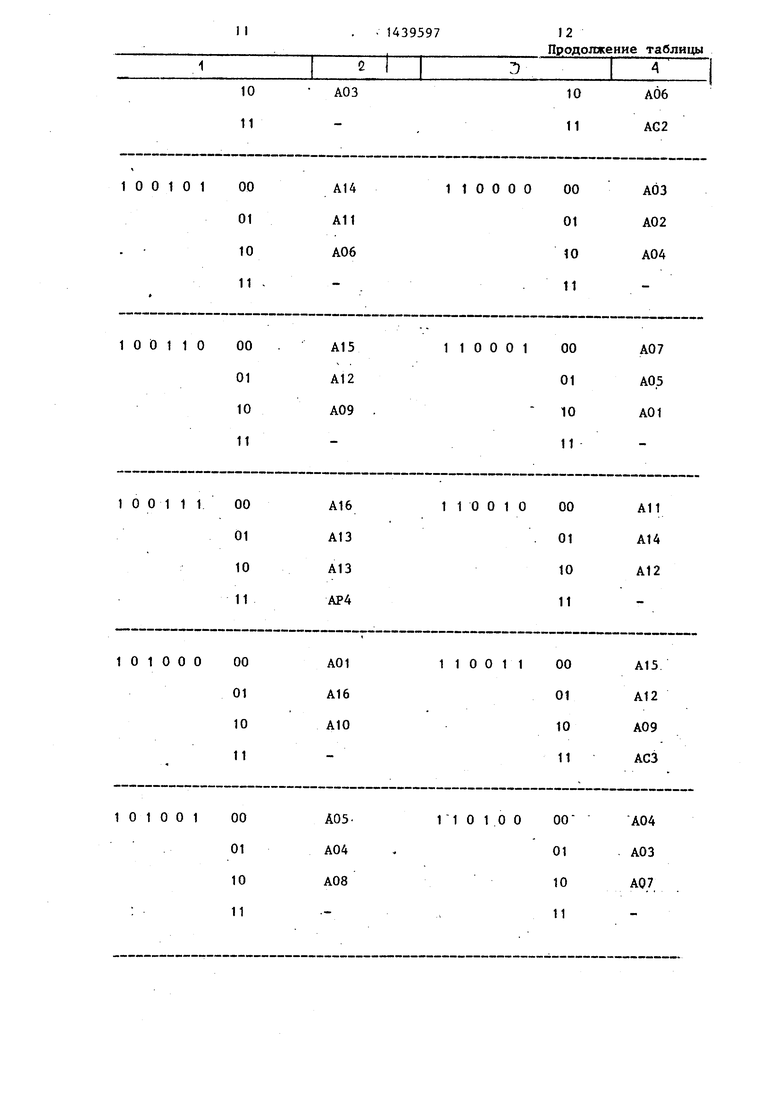

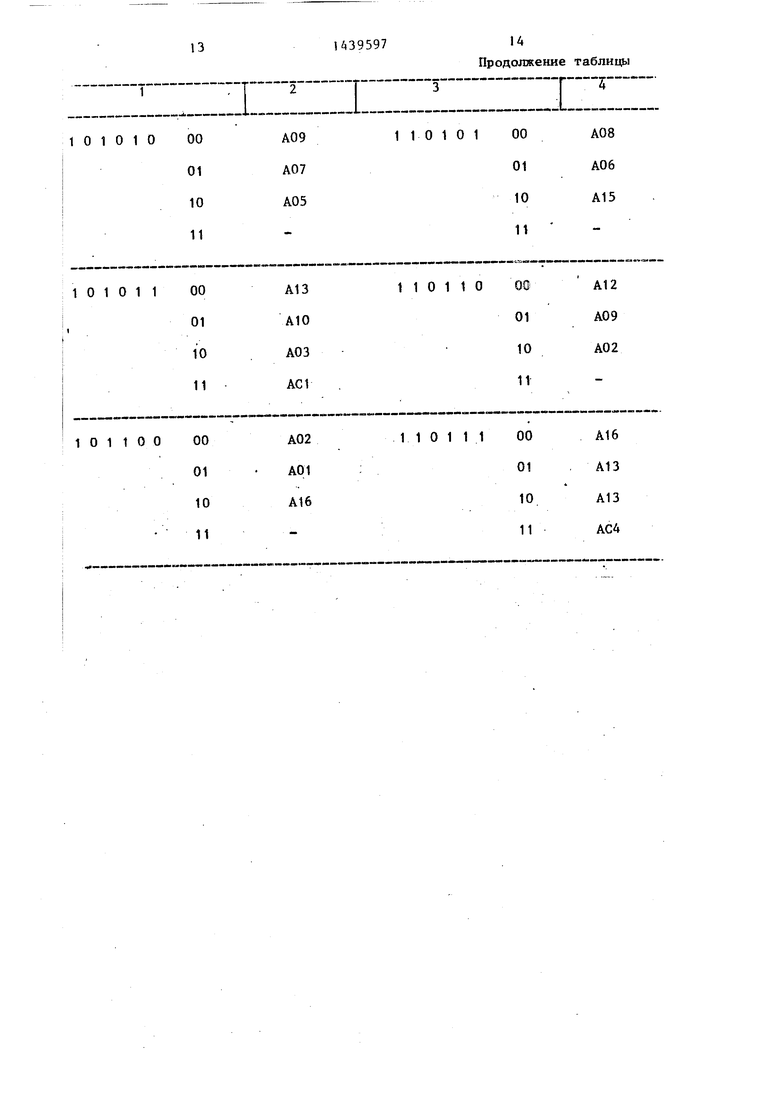

счетчика 7 н тактовый -вход первого блока 1 памяти. Счетчик 7 пачниает считать. В том случае, когда два млаших разряда счетчика находятся в нулевом состоянии, на выходе второго элемента ИЛИ-НЕ 19 появляется единичный сигнал, который поступает на вход, чтения/записи первого блока 1 памяти, как сигнал записи, В этот момент осуществляется запись информационного символа в блок 1 памяти по адресу, определяемому выходными сигналами второго блока 17 памяти. Содержимое второго блока 17 приведено в таблице.

Таким образом, приходящее сообщение записывается в адреса А01,..., А16,АР1,,..,АР4,АС1,.,.,АС4 одноразрядного первого блока 1 памяти.

После этого изменяется сигнал на входе 23 задания режима устройства и на входе чтения/записи первого блока 1 памяти постоянно устанавливается нулевой сигнал, означающий режш-i чтения.

Начинается выборка информации из первого блока 1 памяти по тактовым импульсам.

Адрес блока 1 памяти снова определяется содержимым второго блока 17 Памяти. Адреса, хранящиеся во втором блоке 17 памяти, позволяют, как это видно из таблицы, вызьшать поочередн информационные символы одинаковых строк или столбцов всех трех матриц (прочерком в таблице обозначается адрес, где содержится нулевая информация) .

Информация, содержащаяся в адресах 11100000-11111111, повторяет информацию, содержащуюся в адресах 01100000-01111111.

Считьшаемые биты из первого блока 1 памяти поступают на информационный вход триггера 5. Тактовые импульсы, .задержанные на первом элементе 14 задержки, поступают на тактовый вход второго триггера 5 и зап юывают считанную из первого блока 1 памяти информацию. Одновременно тактовые импульсы через первый элемент И-НЕ 11 поступают на тактовый вход сигнатурного анализатора 2, где происходит формирование сигнатуры. Л том случае когда два младших разряда счетчика 7 находятся в един1гч11ом состоянии, второй элемент И-НЕ 12 закрывает первый элемент И-ПЕ 11 и сигнал на так9597

товый вход сигнатурного анализатора не поступает.

Как только четыре младших разряда счетчика 7 устанавливаются в единичное состояние, на выходе первого элемента И 8 формируется единичньш сигнал, который разрешает прохождение тактового импульса через второй эле- 1Q мент И 13 и второй элемент 15 задержки на тактовый вход первого триггера 4, К этому времени на втором триггере 5 находится один из контрольньгх разрядов, а на сигнатурном анализа- 15 торе 2 - сигнатура соответствутацих строк или столбцов матриц Д1,Д2,ДЗ. Если сообщение принято правильно, то на выходе сумматора 3 по модулю два .будет нулевой сигнал и первый триггер Q 4 останется в нулевом состоянии. При возникновении ошибки контрольный разряд не будет равен сигнатуре информационных символов, триггер 4 уста- новится в единичное состояние и бу- 25 дет поддерживаться в этом состоянии с помощью второго элемента ИЛИ 10.

Сигнал с выхода второго элемента 15 задержки через третий элемент 16 задержки и первый элемент ИЛИ 9 ус- 0 танавливает сигнатурный анализатор в исходное состояние, и начинается проверка очередного контрольного разряда.

На информационный выход 25 устрой- ства поступает информация, считыва- .емая из первого блока Т памяти. Эта информация повторяет принятые информационные символы. По окончании проверки на входе 23 устройства сно- Q ва устанавливается единичный потен- . циал.

После того как старший разряд счетчика 7 установится в единичное состояние, счетчик 7 останавливается, f. формируется сигнал на выходе 26 окончания контроля устройства.

Цикл работы устройства завершен.

50

55

Формула изобретения

Устройство Для контроля кодовой комбинации, содержащее первый блок памяти, сумматор по модулю два и сигнатурный анализатор, причем информационные пькоды сигнатурного анализатора сое.дииены с соответствующими информационными входами сумматора по модулю два, отлич ающее-

с я тем, что, с целью повышения до- :ставерности контроля, в него введены второй блок памяти, счетчик, три триггера, три элемента задержки, два элемента ИЛИ-НЕ, два элемента И-НЕ, |Два элемента И, два элемента ИЛИ, I причем установочный вход счетчика, первый вход первого элемента ИЛИ и нулевой вход первого триггера объе- динены и образуют установочный вход устройства, счетный вход счетчика, :вход первого элемента задержки, так- товый вход первого блока памяти и инверсный вход первого элемента ИЛИ- НЕ объединены и образуют тактовьш вход устройства, выходы двух младших разрядов счетчика соединены соответственно с первыми и вторыми прямыми входаьи первого и второго элементов ИЛИ-НЕ, инверсный вход второго элемента ШШ-НЕ является входом задания режима работы устройства, выходы четьфех младших разрядов счетчика соединены с соответствующими входами первого элемента И и адресными входами второго блока памяти, информационный выход которого соединен с адресным входом первого блока памяти информационный выход которого соединен с информационным входом второго триггера, прямой выход которого соединен с информационным входом сигнатурного анализатора, инверсный выход второго триггера,соединен с соответствующим информационным входом сумматора по модулю два и информационным входом третьего триггера, ин

5

0

5

0

S

версный выход которого является информационным выходом устройства, выход сумматора по модулю два соединен с первым входом второго элемента ИЛИ, выход которого соединен с информационным входом первого триггера, прямой выход которого соединен с вторым входом второго элемента ИЛИ и является выходом неисправности устройства, выход первого элемента задержки соединен с тактовым входом второго триггера, первым входом первого элемента И-НЕ и первым входом второго элемента И, выход которого через второй элемент задержки соединен с тактовым входом первого триггера и входом третьего элемента задержки, выход которого соединен с вторым входом первого элемента I/UIH, выход которого соединен с установочным входом снгнатурного анализатора, выходы двух младших разрядов счетчика соединены с соответствующими входами второго элемента И-НЕ, выход которого соединен с вто рым входом первого элемента И-НЕ, выход которого соединен с тактовым входом сигнатурного анализатора, выходы первого и второго элемег1тов ИЛИ-НЕ соединены соответственно с тактовым входом третьего триггера и входом чтения-записи первого блока памяти, выход первого элемента И соединен с вторым входом второго элемента И, выход старшего разряда счетчика соединен с входом запрета счета счетчика и является выходом окончания контроля устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1667069A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в аппаратуре передачи данных с повышенной достоверностью. Цель изобретения - повышение достоверности контроля, Устройство содержит два блока памяти, сигнатурный анализатор, сумматор по модулю., два, триггеры, счетчик,Информация,, поступающая в устройство, содержит контрольные признаки, образующиеся на матрицах - шифраторах, слова записываются в блок памяти по адресам, хранящимся в другом блоке памяти. Это один режим работы, В режиме выборки информации считывание происходит по тем же адресам, однако адреса позволяют считывать поочередно слова одинаковых строк или столбцов матриц, через которые проходит информационное слово. При возникнове- j НИИ ошибки контрольньй разряд не будет равен сигнатуре информационного слова. 2 ил, 1 табл, . 2 (О

000000

00

А01

01 1000

00

А01

01А05

10AOl

«

О 1 О О 1 1 00АР41110

11

АОЗ

101

00 01 10

11

АН All А06

0110

00 01 10 11

А15 А12 А09

11 1

00 01 10 11

А16 А13 А13 АР4

1000

00 01 10 11

А01 А16 А10

1001

00 01 10 11

А05.

А04

А08

10 11

А06 AG2

10000

00 01 10 11

АОЗ А02 А04

001

00 01 10 11

АО 7 А05 А01

10

00 01 10 11

А11 А14 А12

10011

00 01 10 11

А15 А12 А09 АСЗ

1 О О

00 01 10 11

А04 АОЗ АО 7

От б/. 9

Редактор А. Ворович

Составитель В. Гречнев

Техред Л.Сердюкова Корректор В.Гирняк

.

Фи9.2

| Устройство для исправления ошибок при итеративном кодировании | 1978 |

|

SU746528A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1059629A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-23—Публикация

1984-12-11—Подача