мещающие луч ЭЛТ в место расположения jg ти четвертого стробирующего импульэлектронного маркера.

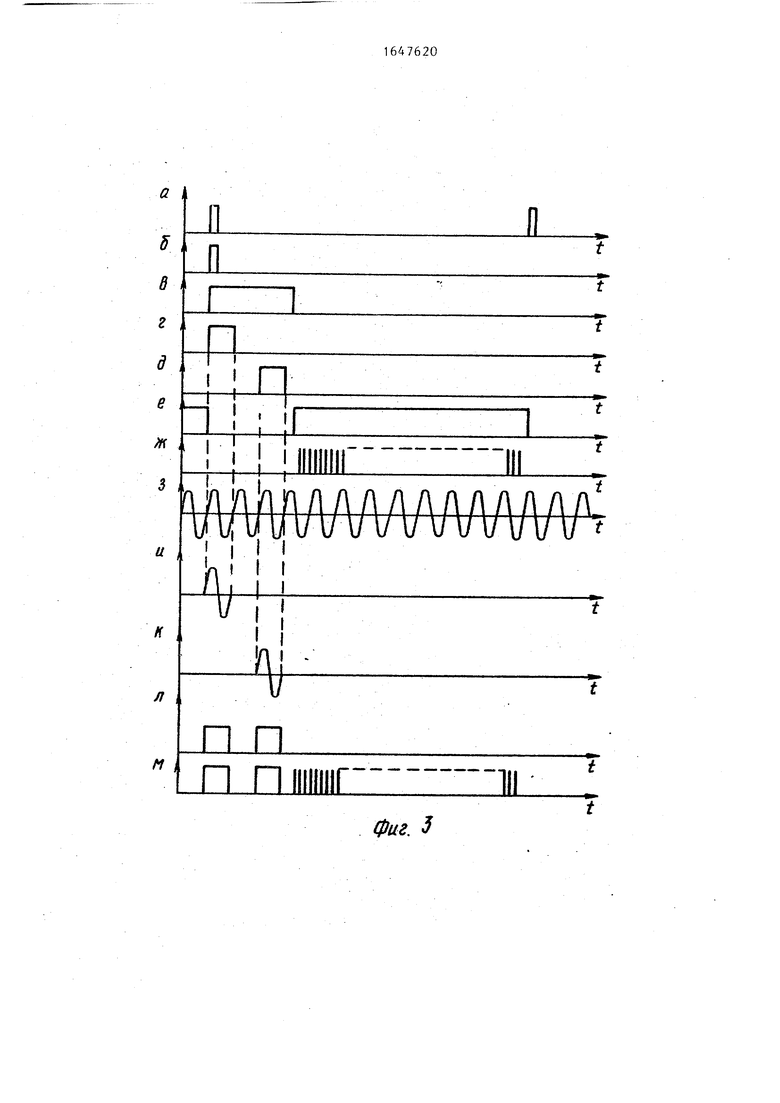

При помощи блока 36 формирования знака маркера вычерчивается знак „ электронного маркера. При выведении луча ЭЛТ в точку, соответствующую координатам электронного маркера, на первый и второй управляющие входы коммутатора 38 поступают со смещением во времени второй (фиг. 3 г) и

третий (фиг.З д) стробирующие импуль- 2Q пряжения строчной развертки заканчисы. Поступая на управляющие входы коммутатора 38, они разрешают прохождение синусоидального напряжения с выхода генератора 37 (фиг. 3 з) на первые входы усилителей 35 блоков 29 и 30 (фиг. 3 и, к).

Синусоидальное напряжение с первого выхода коммутатора 38 (фиг.З и) поступает на первый вход усилителя 35 блока 29. В результате суммирования усилителем 35 напряжения по двум его входам происходит формирование напряжения на выходе 49, отклоняющее луч ЭЛТ вправо и влево относительно точки, координата X которой определяется величиной напряжения на втором его входе. Аналогично синусоидальное напряжение, подаваемое на первый вход усилителя 35 (фиг.З к) блока 30, отклоняет луч ЭЛТ вверх и вниз.

25

30

35

40

вается цикл работы блока 4.

Кадровые синхроимпульсы (фиг.З б) с выхода второго компаратора 46 посту пают также на вход счетчика 40 кадровых синхроимпульсов, на выходе 51 которого формируется код номера кадра магнитофильма. Сброс счетчика 40 кадровых синхроимпульсов осуществляется автоматически перед началом работы устройства при включении питания (схема сброса не представлена) .

На выходе 52 первого элемента ИЛИ

41,на первый, второй и третий входы которого поступают соответственно импульсы Сдвиг X, второй и третий стробирующие импульсы,формируется импульсная последовательность (фиг.З м), предназначенная для формирования импульсов подсветки.

На выходе 53 второго элемента ИЛИ

На временных диаграммах (фиг, 3) показано, что фаза синусоидального напряжения (фиг. 3 з) совпадает с ф зами второго (фиг. 3 г) и третьего (фиг. 3 д) стробирующих импульсов. Условие это не обязательное. Обязательным является условие, что длительность второго (фиг. 3 г) и третьего (фиг. 3 д) стробирующих импульсов по крайней мере равна (но не меньше) периоду синусоидального напряжения (фиг. 3 з). В этом случае независимо от соотношения фаз электронный луч отклонится по горизонтали и вертикали на нужную величину и будет сформирован знак маркера.

са. Вследствие того, что информация двоичного счетчика 31 блока 29 изменяется с приходом каждого импульса Сдвиг X (фиг. 3 ж), на вы- ходе 49 усилителя 35 формируется напряжение строчной развертки. Аналогично на выходе 50 усилителя 35 блока 30 формируется напряжение кадровой развертки. Формированием на2Q пряжения строчной развертки заканчи

25

30

35

40

50

д$

55

вается цикл работы блока 4.

Кадровые синхроимпульсы (фиг.З б) с выхода второго компаратора 46 поступают также на вход счетчика 40 кадровых синхроимпульсов, на выходе 51 которого формируется код номера кадра магнитофильма. Сброс счетчика 40 кадровых синхроимпульсов осуществляется автоматически перед началом работы устройства при включении питания (схема сброса не представлена) .

На выходе 52 первого элемента ИЛИ

41,на первый, второй и третий входы которого поступают соответственно импульсы Сдвиг X, второй и третий стробирующие импульсы,формируется импульсная последовательность (фиг.З м), предназначенная для формирования импульсов подсветки.

На выходе 53 второго элемента ИЛИ

42,на первый и второй входы которого поступают второй и третий стробирующие импульсы, формируется импульсная последовательность (фиг. Зл), предназначенная для формирования видеосигналов горизонтальной и вертикальной составляющих электронного маркера. Информация о текущих координатах X и Y развертки выводится с выходов двоичных счетчиков 31 соот- ветствующих блоков 29, 30 на выходы / соответственно 54 и 55. Информация

о координатах X и Y электронного маркера выводится с выходов реверсивных счетчиков 32 соответствующих блоков 29, 30 соответственно на выходы 56 и 57. Первый (фиг. 3 в) и четвертый (фиг. 3 е) стробирующие- импульсы,

формируемые формирователем 23 управляющих сигналов, выводятся на выходы 58 и 59.

Первый и второй выходы коммутато-. ра 43 сигналов управления перемещением маркера соединены соответственно с входами прямого и обратного счета реверсивного счетчика 32 блока 29, а третий и четвертый выходы - соответственно с входами прямого и обратного счета реверсивного счетчика 32 блока 30,

Наличие импульсных последовательностей на входах 60 - 63 при наличии разрешающего сигнала на входе 64 (сигнал с уровнем логической 1) приводит к изменению информации реверсивных счетчиков 32, блоков 29, 30, в результате чего происходит изменение координат электронного маркера, т.е. его перемещение

Входы. 60 - 63 образуют шину, соединяющую второй выход пульта 1 и первый вход блока 4. Входы 47 и 48 являются третьим и вторым (соответственно) , а выход 64 - четвертым входа- ми блока 4. На выход 65 выводятся кадровые синхроимпульсы, необходимые для работы блока 3. Выход 65 является первым выходом блока 4.

Выходы 56 и 57 образуют шину, соединяющую второй выход блока 4 и третий вход блока 3. Выходы 54 и 55 образуют шину, соединяющую третий выход блока 4 одновременно с четвертым входом блока 3 и первым входом блока 5. Выход 51 образует шину, соединяющую четвертый выход блока 4 с вторым входом блока 5. Выходы 49, 50, 52, 53, 58 и 59 образуют шину, соединяющую пятый выход блока 4 с первым входом блока 6.

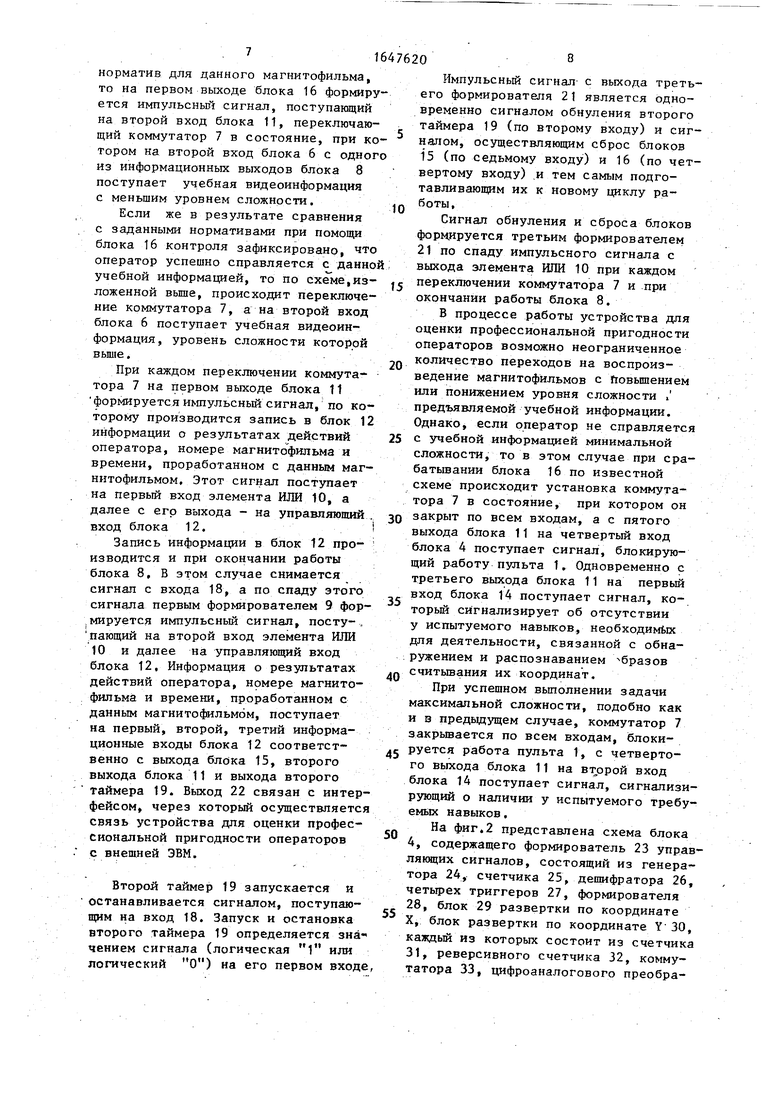

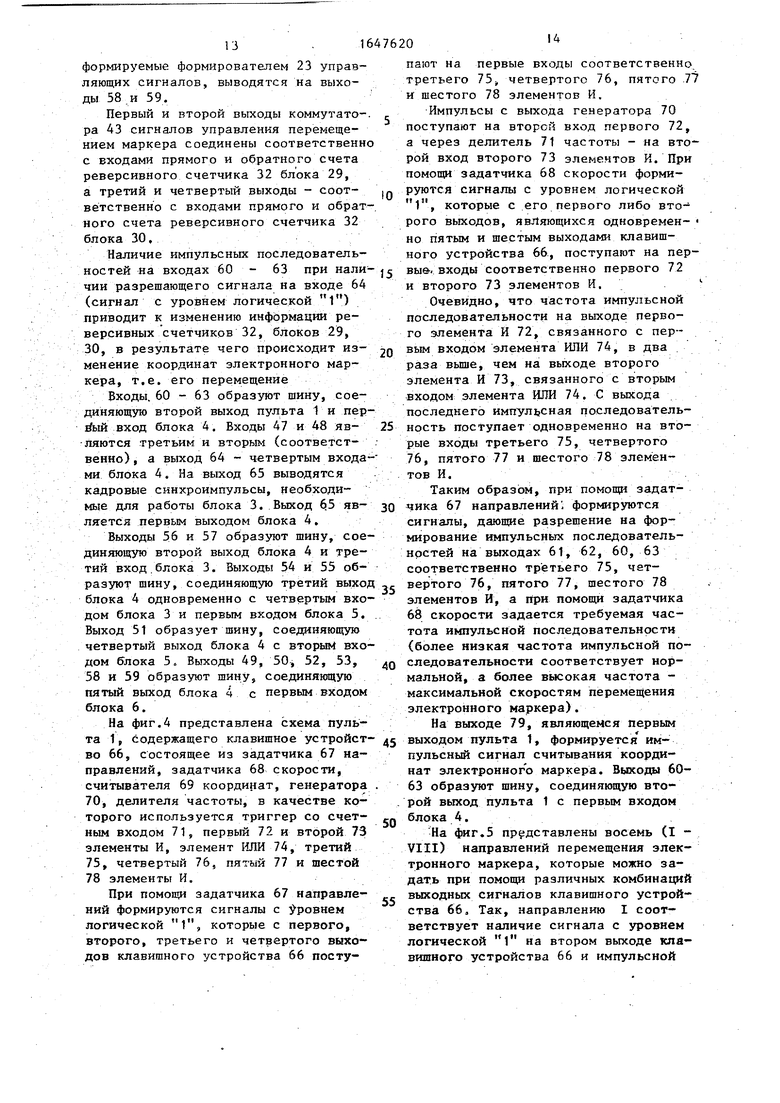

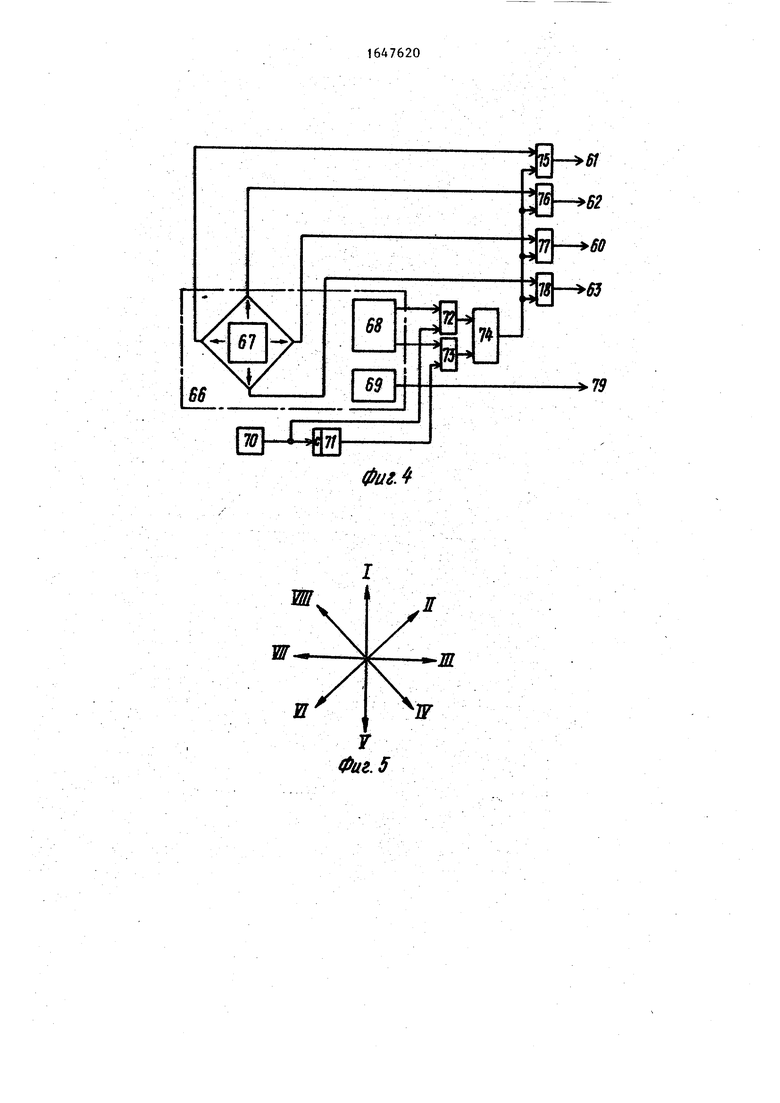

На фиг.4 представлена схема пульта 1, содержащего клавишное устройство 66, состоящее из задатчика 67 направлений, задатчика 68 скорости, считывателя 69 координат, генератора . 70, делителя частоты, в качестве которого используется триггер со счетным входом 71, первый 72 и второй 73 элементы И, элемент ИЛИ 74, третий 75, четвертый 76, пятый 77 и тестой 78 элементы И.

При помощи задатчика 67 направлений формируются сигналы с уровнем логической 1, которые с первого, второго, третьего и четвертого выходов клавишного устройства 66 посту

5

0

5

0

5

0

5

0

5

пают на первые входы соответственно третьего 75, четвертого 76, пятого 77 и шестого 78 элементов И.

Импульсы с выхода генератора 70 поступают на второй вход первого 72, а через делитель 71 частоты - на второй вход второго 73 элементов И. При помощи задатчика 68 скорости формируются сигналы с уровнем логической 1, которые с его первого либо второго выходов, являющихся одновремен- но пятым и шестым выходами клавишного устройства 66, поступают на первые входы соответственно первого 72 и второго 73 элементов И.k

Очевидно, что частота импульсной последовательности на выходе первого элемента И 72, связанного с первым входом элемента ИЛИ 74, в два раза выше, чем на выходе второго элемента И 73, связанного с вторым входом элемента ИЛИ 74. С выхода последнего импульсная последовательность поступает одновременно на вторые входы третьего 75, четвертого 76, пятого 77 и шестого 78 элементов И.

Таким образом, при помощи задатчика 67 направлений формируются сигналы, дающие разрешение на формирование импульсных последовательностей на выходах 61, 62, 60, 63 соответственно третьего 75, четвертого 76, пятого 77, шестого 78 элементов И, а при помощи задатчика 68 скорости задается требуемая частота импульсной последовательности (более низкая частота импульсной последовательности соответствует нормальной, а более высокая частота - максимальной скоростям перемещения электронного маркера).

На выходе 79, являющемся первым выходом пульта 1, формируется импульсный сигнал считывания координат электронного маркера. Выходы 60- 63 образуют шину, соединяющую второй выход пульта 1 с первым входом блока 4.

На фиг.5 представлены восемь (I - VIII) направлений перемещения электронного маркера, которые можно задать при помощи различных комбинаций выходных сигналов клавишного устройства 66, Так, направлению I соответствует наличие сигнала с уровнем логической 1 на втором выходе клавишного устройства 66 и импульсной

последовательности на выходе 62, с которого сигналы поступают на вход прямого счета реверсивного счетчика 32 блока 30, и в этом случае проис- ходит увеличение значения координаты Y электронного маркера. Направлению II соответствует наличие сигналов с уровнем логической 1 одновременно на втором и третьем выхо- дах клавишного устройства 66 и импульсной последовательности на выходах 62 и 60, с которых сигналы поступают на входы прямого счета реверсивных счетчиков 32 соответственно блоков 30, 29, и в этом случае происходит увеличение координат Y и X электронного маркера и т.д. Сигналы с выходов 61 и 63 поступают на вхо- ; ды обратного счета реверсивных счет чиков 32 соответственно блоков 29 и 30.

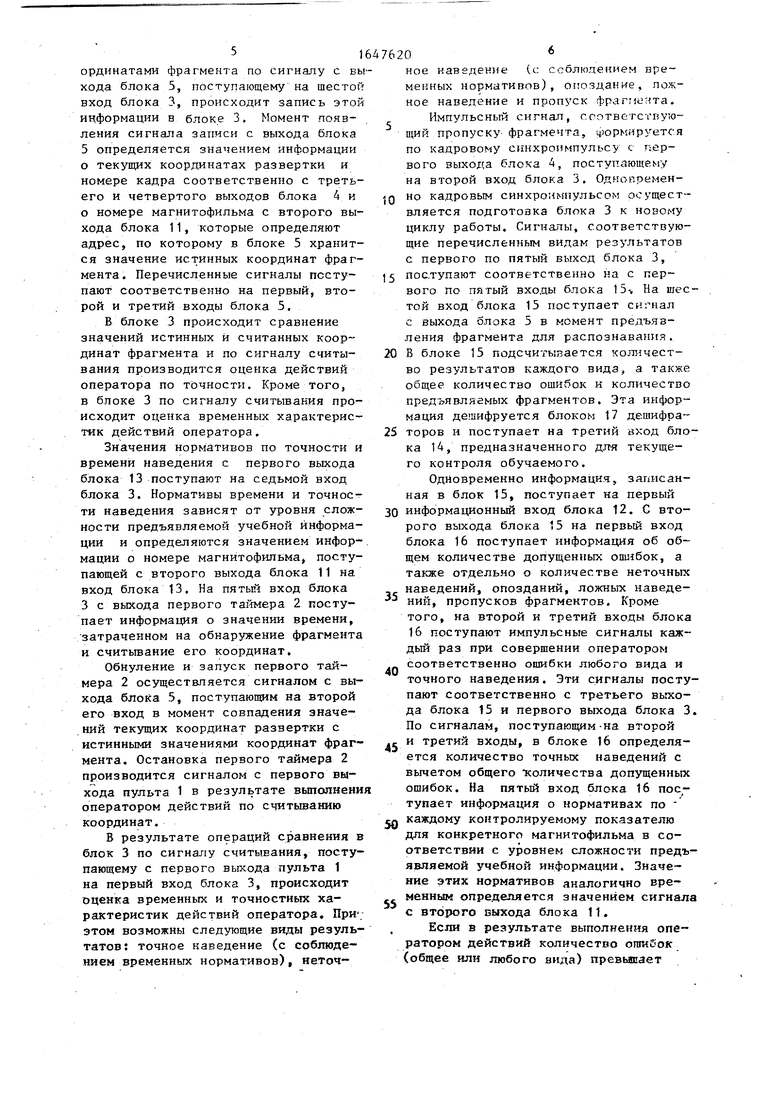

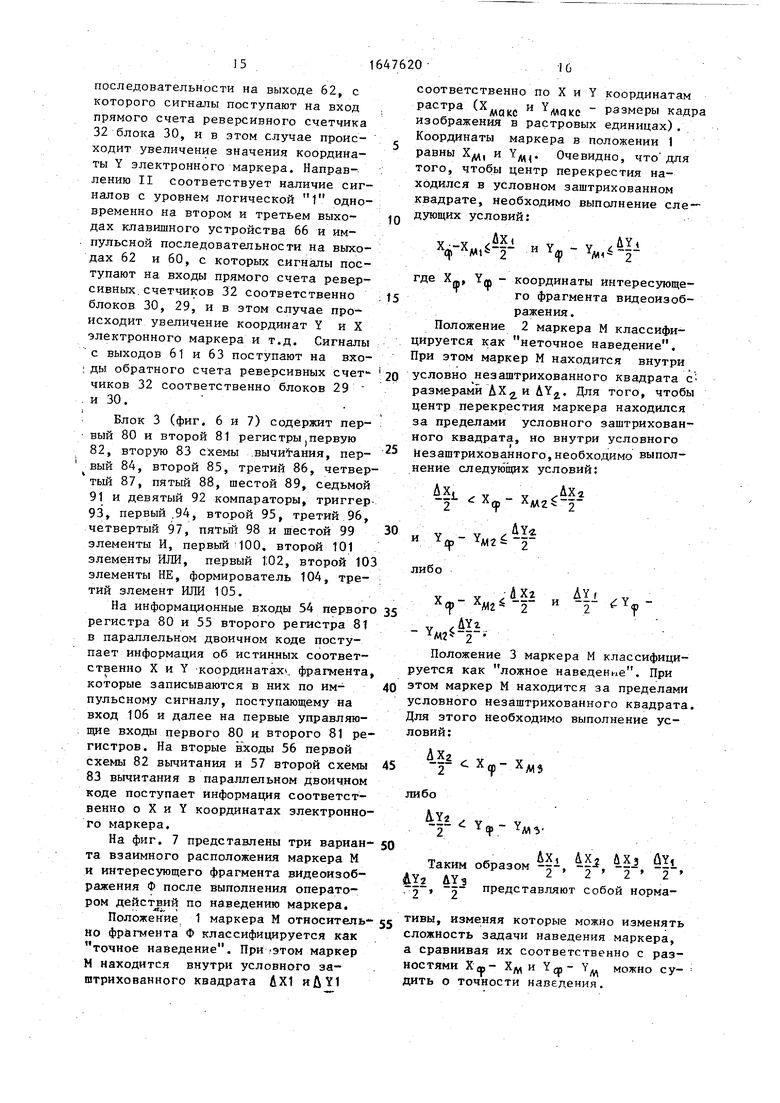

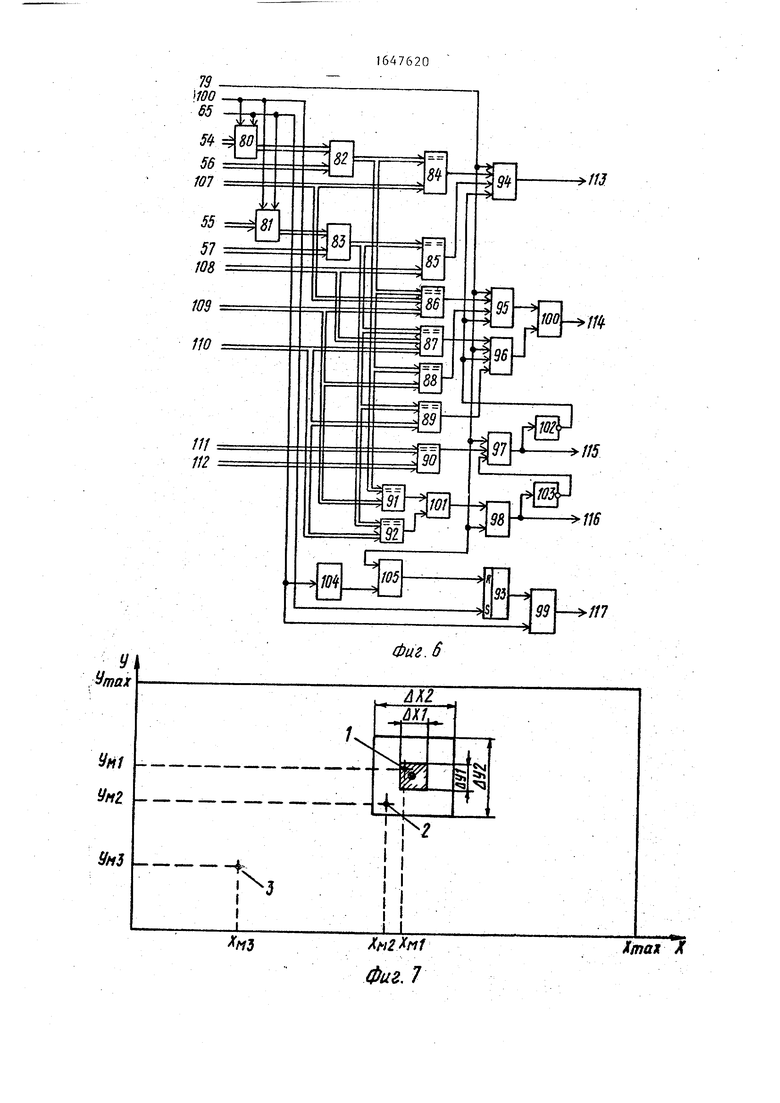

Блок 3 (фиг. 6 и 7) содержит первый 80 и второй 81 регистрыjпервую 82, вторую 83 схемы вычитания, пер- вый 84, второй 85, третий 86, четвер тый 87, пятый 88, шестой 89, седьмой 91 и девятый 92 компараторы, триггер 93, первый .94, второй 95, третий 96, четвертый 97, пятый 98 и шестой 99 элементы И, первый 100, второй 101 элементы ИЛИ, первый 102, второй 10 элементы НЕ, формирователь 104, третий элемент ИЛИ 105.

На информационные входы 54 первог регистра 80 и 55 второго регистра 81 в параллельном двоичном коде поступает информация об истинных соответственно X и Y координатах, фрагмента которые записываются в них по им- пульсному сигналу, поступающему на вход 106 и далее на первые управляющие входы первого 80 и второго 81 регистров. На вторые входы 56 первой схемы 82 вычитания и 57 второй схемы 83 вычитания в параллельном двоичном коде поступает информация соответственно о X и Y координатах электронного маркера.

На фиг. 7 представлены три вариан та взаимного расположения маркера М и интересующего фрагмента видеоизображения Ф после выполнения оператором действий по наведению маркера.

Положение 1 маркера М относитель но фрагмента Ф классифицируется как точное наведение. При этом маркер М находится внутри условного заштрихованного квадрата АХ1 яДУ1

соответственно по X и Y координатам растра (XMQKC и Y,.,, - размеры кадр изображения в растровых единицах). Координаты маркера в положении 1 равны Хдд, и Y. Очевидно, что для того, чтобы центр перекрестия находился в условном заштрихованном квадрате, необходимо выполнение следующих условий:

Х-х Ј& и Y - Y Ш Aq X/M 2 н Y/VH 2

где X., Y-, - координаты интересующего фрагмента видеоизображения .

Положение 2 маркера М классифицируется как неточное наведение. При этом маркер М находится внутри условно незаштрихованного квадрата с размерами АХ Ј и AY2. Для того, чтобы центр перекрестия маркера находился за пределами условного заштрихованного квадрата, но внутри условного Незаштрихованного,необходимо выполнение следующих условий:

ASi

2

OAL у ,

- с. Л.т &Uf}i „

ч

1М2:

и чМгЈ-Г

либо

у у u и Јil / Y rtl AyVI2 ° ° ф

Д X2 AYji

cp ЛМ2 2 2 A f

v Ali

мг5 2

Положение 3 маркера М классифицируется как ложное наведенпе. При этом маркер М находится за пределами условного незаштрихованного квадрата. Для этого необходимо выполнение условий:

4.2 f Y 2 С ХФ

«3

либо

&12 Y V

2 Y Y

MV

„ AX, AX, UX3 UY, Таким образом z-, -z, z n 412 4XJ 222

представляют собой нормативы, изменяя которые можно изменять сложность задачи наведения маркера, а сравнивая их соответственно с разностями Хя,- Хм и Yq,- Y можно судить о точности наведения.

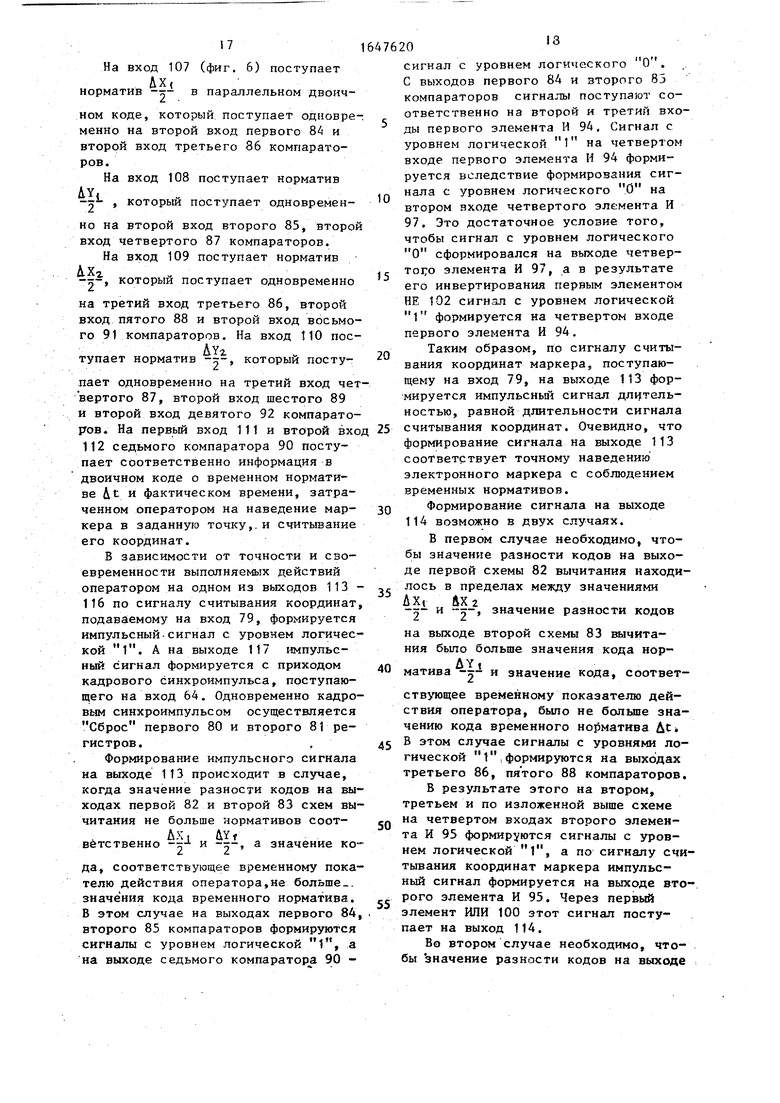

17 На вход 107 (фиг. 6) поступает

в параллельном двоич&Хнорматив -„

ном коде, который поступает одновременно на второй вход первого 84 и второй вход третьего 86 компараторов.

На вход 108 поступает норматив

iYl

, который поступает одновременно на второй вход второго 85, второй вход четвертого 87 компараторов. На вход 109 поступает норматив

Дхг

-о которыи поступает одновременно

на третий вход третьего 86, второй вход пятого 88 и второй вход восьмого 91 компараторов. На вход 110 посAYz

тупает норматив , который поступает одновременно на третий вход четвертого 87, второй вход шестого 89 и второй вход девятого 92 компараторов. На первый вход 111 и второй вход 112 седьмого компаратора 90 поступает соответственно информация в двоичном коде о временном нормативе &t и фактическом времени, затраченном оператором на наведение маркера в заданную точку,, и считывание его координат.

В зависимости от точности и своевременности выполняемых действий оператором на одном из выходов 113 - 116 по сигналу считывания координат, подаваемому на вход 79, формируется импульсный-сигнал с уровнем логической 1. А на выходе 117 импульсный сигнал формируется с приходом кадрового синхроимпульса, поступающего на вход 64. Одновременно кадровым синхроимпульсом осуществляется Сброс первого 80 и второго 81 регистров.

Формирование импульсного сигнала на выходе 113 происходит в случае, когда значение разности кодов на выходах первой 82 и второй 83 схем вычитания не больше нормативов соот45i и Ш

2 И 2

да, соответствующее временному пока- телю действия оператора,не больше., значения кода временного норматива. В этом случае на выходах первого 84, второго 85 компараторов формируются сигналы с уровнем логической 1, а на выходе седьмого компаратора 90

вётственно

а значение ко

10

15

20

30

25

647620 3

сигнал с уровнем логического О. С выходов первого 84 и второго 83 компараторов сигналы поступают соответственно на второй и третий входы первого элемента И 94. Сигнал с уровнем логической 1 на четвертом входе первого элемента И 94 формируется вследствие формирования сигнала с уровнем логического О на втором входе четвертого элемента И 97. Это достаточное условие того, чтобы сигнал с уровнем логического О сформировался на выходе четвер- тог.о элемента И 97, а в результате его инвертирования первым элементом НЕ 102 сигнал с уровнем логической 1 формируется на четвертом входе первого элемента И 94.

Таким образом, по сигналу считывания координат маркера, поступающему на вход 79, на выходе 113 формируется импульсный сигнал длительностью, равной длительности сигнала считывания координат. Очевидно, что формирование сигнала на выходе 113 соответствует точному наведению электронного маркера с соблюдением временных нормативов.

Формирование сигнала на выходе 114 возможно в двух случаях.

В первом случае необходимо, чтобы значение разности кодов на выходе первой схемы 82 вычитания находилось в пределах между значениями ДХ 4X2

35

40

45

50

55

матива

и значение кода, соответ 2 и значение разности кодов

на выходе второй схемы 83 вычитания было больше значения кода нор4li

2

ствующее временному показателю действия оператора, было не больше значению кода временного норматива Дс. В этом случае сигналы с уровнями логической t формируются на выходах третьего 86, пятого 88 компараторов.

В результате этого на втором, третьем и по изложенной выше схеме на четвертом входах второго элемента И 95 формируются сигналы с уровнем логической 1, а по сигналу считывания координат маркера импульсный сигнал формируется на выходе второго элемента И 95. Через первый элемент ИЛИ 100 этот сигнал поступает на выход 114.

Во втором случае необходимо, чтобы значение разности кодов на выходе

первой схемы 82 вычитания было больАх,

ше значения кода норматива у,

значение разности кодов на выходе второй схемы 83 вычитания находилось в

AY, UY2 пределах между значениями и -ти значение кода, соответствующее временному показателю действия операто- ра, было не больше значения кода временного норматива Дt.

В этом случае сигналы с уровнями логической 1 формируются на выхода четвертого 87 и шестого 89 компарато ров. В результате этого на втором, третьем, четвертом входах третьего элемента И 96 формируются сигналы с уровнями логической 1, а по сигналу считывания координат маркера им- лульсный сигнал формируется на выходе третьего элемента И 96, поступающий через элемент ИЛИ 100 на выход 114. Формированию сигнала на выходе 114 соответствует неточное наведение электронного маркера с соблюдением временных нормативов. Компараторы 86 и 87 представляют собой двухуровневые цифровые компараторы, каждый из которых может быть построен из двух одноуровневых компараторов, выходы которых соединены по схеме И.

Формирование сигнала на выходе 115 происходит в случае, когда значение кода временного показателя больше значения кода временного норматива Дс и при условии, что оператором было произведено либо точ

ное, либо неточное наведение. Так как при выполнении оператором действий по считыванию координат маркера возможны три вида результатов по критерию точности наведения, то при точном либо неточном наведении обязательным является условие отсутствия сигнала с уровнем логической 1 на выходе 116, так как формирование на нем сигнала с уровнем логической 1 возможно в случае ложного наведения, что исключает формирование сигналов на выходах 113 и 114.

При таких условиях на выходе седьмого компаратора 90 формируется сигнал с уровнем логической 1, поступающий на второй вход четвертого элемента И 97, на третий вход которого аналогичный сигнал поступает с выхода второго элемента НЕ 103, вход

которого подсоединен к выходу пятого элемента И 98. По сигналу считывания координат маркера с выхода четвертого элемента И 97 сигнал с уровнем логической 1 поступает на -выход 115, что соответствует превышению временного норматива (опозда нию). Одновременно этот сигнал инвертируется первым элементом НЕ 102 и, поступая на соответствующие входы первого 94, второго 95, и третьего 96 элементов И, запрещает формирование сигналов на выходах 113 и 114.

Если значения разностей кодов на выходах первой 82 или второй 83 схем вычитания превышает значения кодов

ДХ2 UY-2 соответственно нормативов - и ,

то сигнал с уровнем логической 1

формируется на выходе восьмого 91 либо девятого 92 компараторов, которые соединены соответственно с первым и вторым входами второго элемента ИЛИ 101. В результате этого на выходе 116 пятого элемента И 98, первый вход которого подсоединен к выходу второго элемента ИЛИ 101, по сигналу считывания координат маркера формируется сигнал с уровнем логической 1, что соответствует ложному наведению маркера. Одновременно сигнал с уровнем логической 1 с выхода пятого элемента И 98 инвертируется вторым инвертором 103, поступает на третий вход четвертого элемента И 97 и запрещает формирование сигнала на выходе 115.

Формирование сигнала, на ыходе

11 при пропуске фрагмента происходит следующим образом.

По сигналу, поступающему на вход 106, триггер 93 устанавливается в состояние, при котором на его выходе формируется сигнал с уровнем логической 1. Если оператором про- изведутся действия по считыванию ко- ординат, то по сигналу, поступающему на вход 79, триггер 93 через третий элемент ИЛИ 105 устанавливается в исходное состояние, а с приходом кадрового синхроимпульса, поступающего на вход 64, на выходе 117 шестого элемента И 99 импульсный

сигнал не формируется.

Если же к приходу кадрового синхроимпульса триггер 93 находится в состоянии, при котором на его выхо- де сигнал логической 1 (отсутствие

сигнала считывания координат в действиях оператора, т.е. пропуск фрагмента), то на выходе 117 формируется импульсный сигнал с уровнем логической 1. По спаду кадрового синхроимпульса формирователем 104 формируется импульс Сброс, который через третий элемент ИЛИ 105 поступает на первый вход триггера 93 и тем са- мым подготавливает его к следующему циклу классификации действий оператора.

Входы 79 и 64 являются соответственно первым и вторым входами бло- ка 3, входы 56 и 57 образуют шину, соединяющую второй выход блока 4 и третий вход блока 3, входы 54 и 55 образуют шину, соединяющую третий выход блока 4 с четвертым входом бло ка 3, вход 112 образует шину, соединяющую выход первого таймера 2 с пятым входом блока 3, вход 116 является шестым входом блока 3, входы 107 - 111, образуют шину, соединяю- щую первый выход блока 3 с седьмым входом блока 3. Выходы 113 - 117 являются соответственно первым, вторым, третьим, четвертым, пятым выходами блока 3.

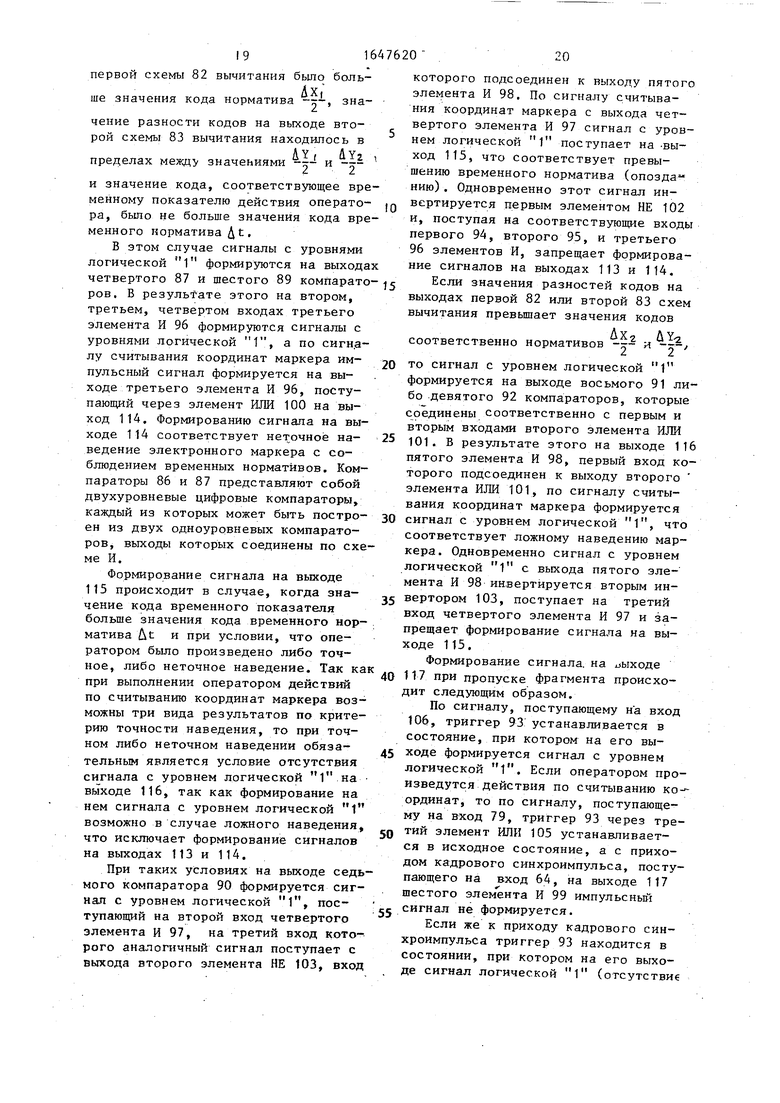

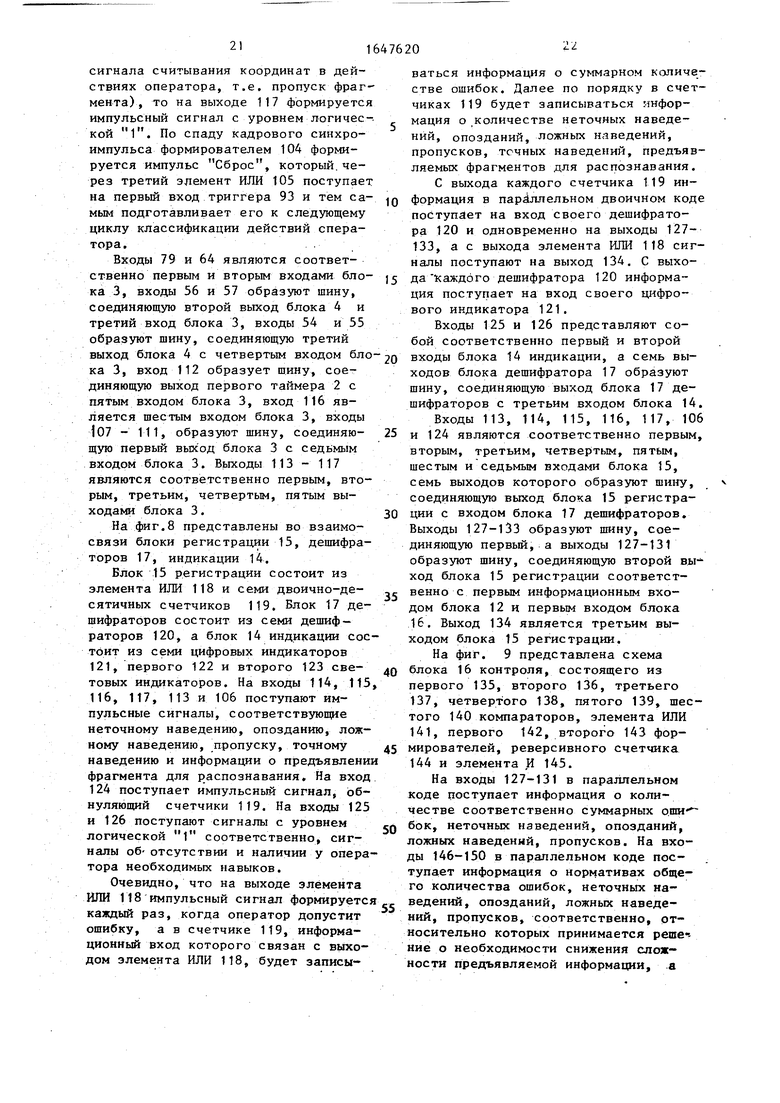

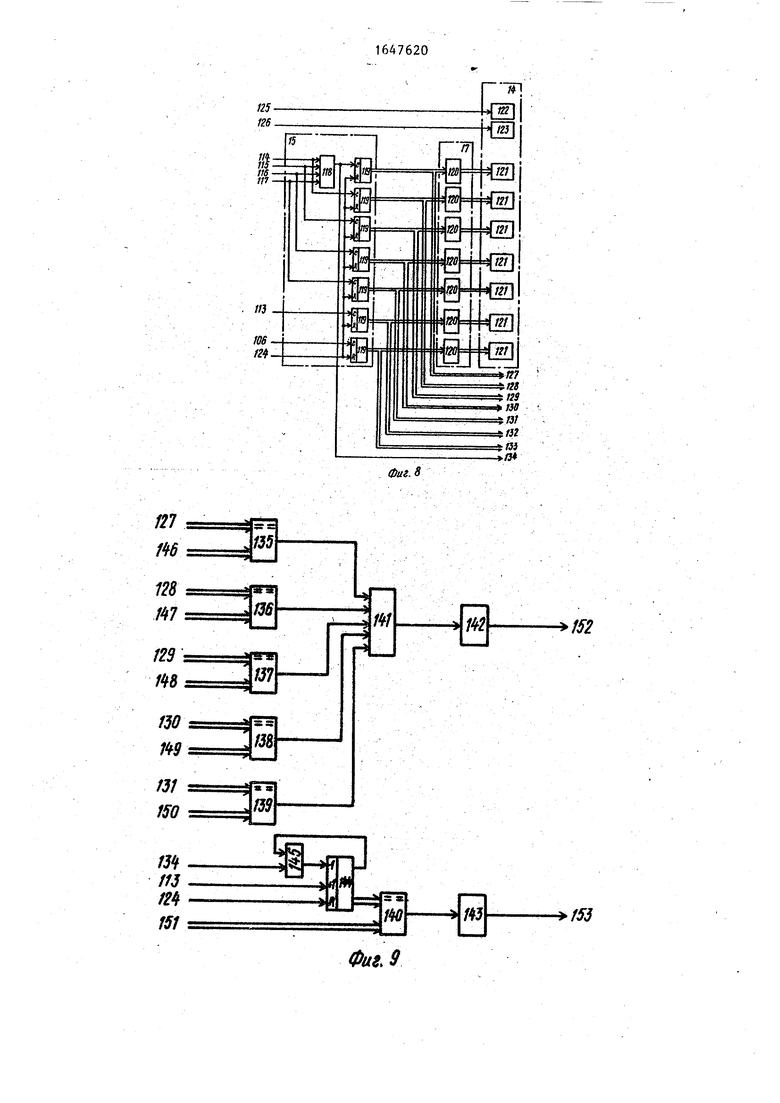

На фиг.8 представлены во взаимосвязи блоки регистрации 15, дешифраторов 17, индикации 14.

Блок 15 регистрации состоит из элемента ИЛИ 118 и семи двоично-десятичных счетчиков 119. Блок 17 дешифраторов состоит из семи дешифраторов 120, а блок 14 индикации состоит из семи цифровых индикаторов 121, первого 122 и второго 123 све- товых индикаторов. На входы 114, 115 116, 117, 113 и 106 поступают импульсные сигналы, соответствующие неточному наведению, опозданию, ложному наведению, пропуску, точному наведению и информации о предъявлении фрагмента для распознавания. На вход 124 поступает импульсный сигнал, обнуляющий счетчики 119. На входы 125 и 126 поступают сигналы с уровнем логической 1 соответственно, сигналы об- отсутствии и наличии у оператора необходимых навыков.

Очевидно, что на выходе элемента ИЛИ 118 импульсный сигнал формируется каждый раз, когда оператор допустит ошибку, а в счетчике 119, информационный вход которого связан с выходом элемента ИЛИ 118, будет записы

Q

Q 5 0

п 5

5

0

5

ваться информация о суммарном количестве ошибок. Далее по порядку в счетчиках 119 будет записываться .чнфор- мация о количестве неточных наведений, опозданий, ложных наведений, пропусков, точных наведений, предъявляемых фрагментов для распознавания.

С выхода каждого счетчика 119 информация в параллельном двоичном коде поступает на вход своего дешифратора 120 и одновременно на выходы 127- 133, а с выхода элемента ИЛИ 118 сигналы поступают на выход 134. С выхода Каждого дешифратора 120 информация поступает на вход своего цифрового индикатора 121.

Входы 125 и 126 представляют собой соответственно первый и второй входы блока 14 индикации, а семь выходов блока дешифратора 17 образуют шину, соединяющую выход блока 17 дешифраторов с третьим входом блока 14.

Входы 113, 114, 115, 116, 117, 106 и 124 являются соответственно первым, вторым, третьим, четвертым, пятым, шестым и седьмым входами блока 15, семь выходов которого образуют шину, соединяющую выход блока 15 регистрации с входом блока 17 дешифраторов. Выходы 127-133 образуют шину, соединяющую первый, а выходы 127-131 образуют шину, соединяющую второй вы-1- ход блока 15 регистрации соответственно с первым информационным входом блока 12 и первым входом блока 16. Выход 134 является третьим выходом блока 15 регистрации.

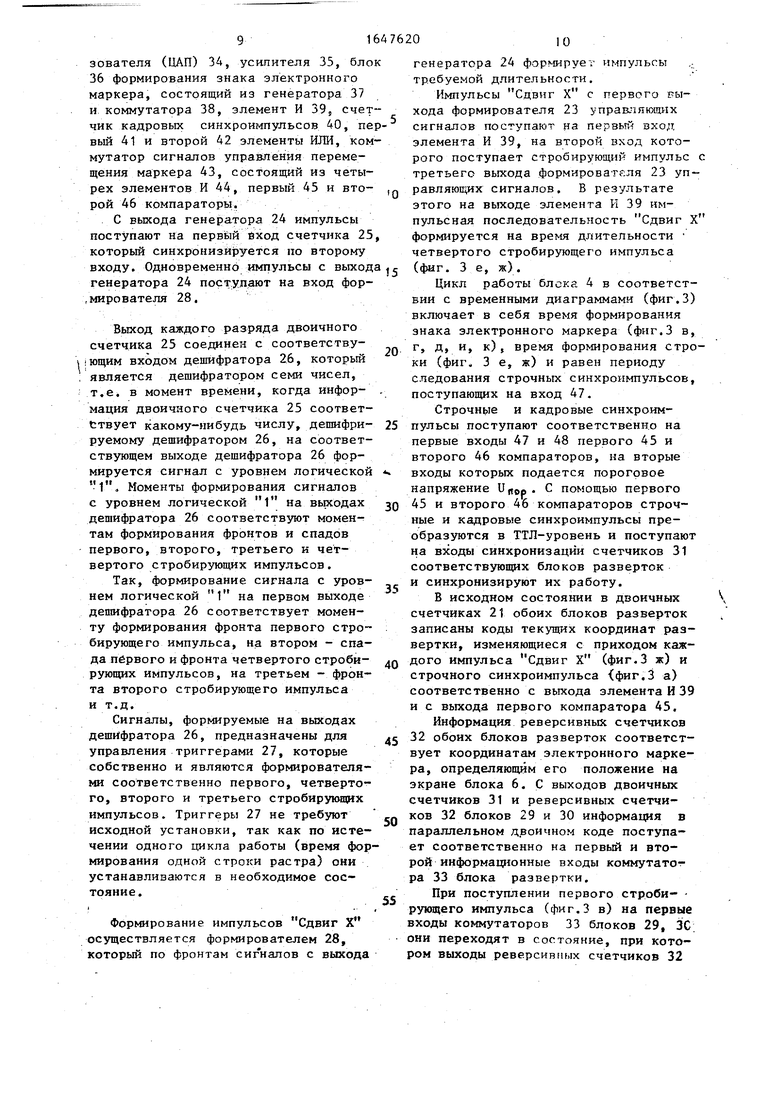

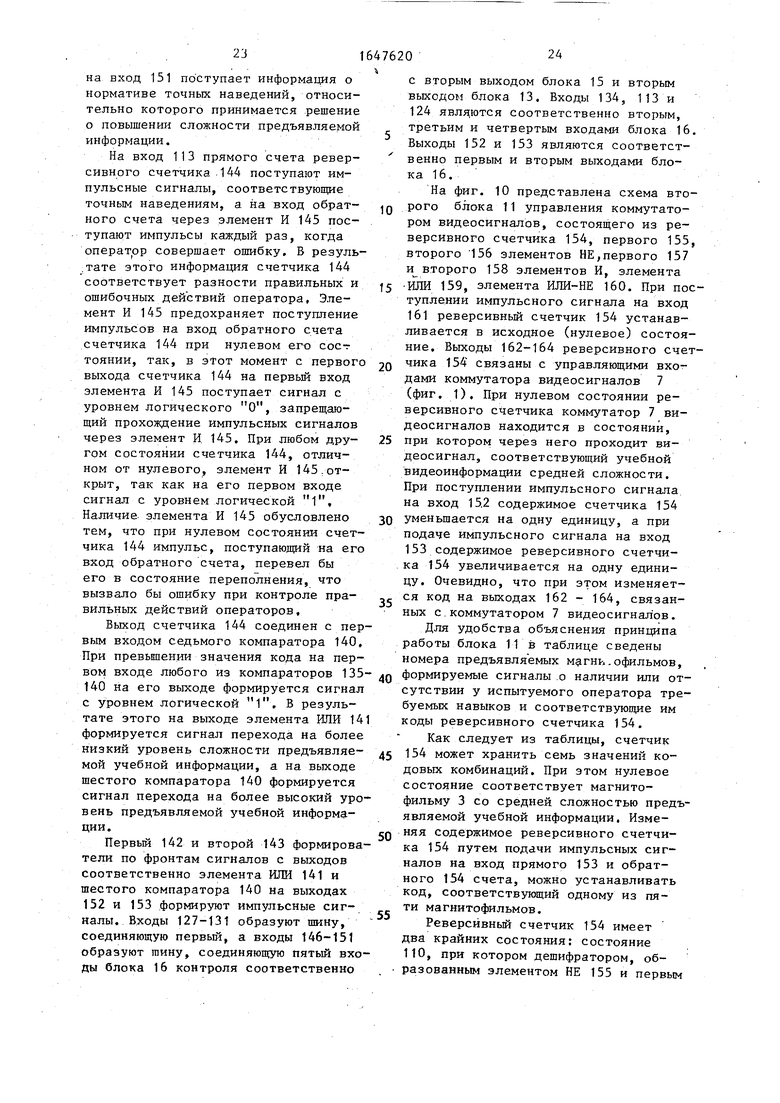

На фиг. 9 представлена схема блока 16 контроля, состоящего из первого 135, второго 136, третьего 137, четвертого 138, пятого 139, шестого 140 компараторов, элемента ИЛИ 141, первого 142, второго 143 формирователей, реверсивного счетчика 144 и элемента И 145.

На входы 127-131 в параллельном коде поступает информация о количестве соответственно суммарных оши- бок, неточных наведений, опозданий, ложных наведений, пропусков. На входы 146-150 в параллельном коде поступает информация о нормативах общего количества ошибок, неточных наведений, опозданий, ложных наведений, пропусков, соответственно, относительно которых принимается решеч ние о необходимости снижения сложности предъявляемой информации, а.

23

на вход 151 поступает информация о нормативе точных наведений, относительно которого принимается решение о повышении сложности предъявляемой информации.

На вход 113 прямого счета реверсивного счетчика 144 поступают импульсные сигналы, соответствующие точным наведениям, а на вход обратного счета через элемент И 145 поступают импульсы каждый раз, когда оператор совершает ошибку. В результате этого информация счетчика 144 соответствует разности правильных и ошибочных действий оператора, Элемент И 145 предохраняет поступление импульсов на вход обратного счета счетчика 144 при нулевом его состоянии, так, в этот момент с первого выхода счетчика 144 на первый вход элемента И 145 поступает сигнал с уровнем логического О, запрещающий прохождение импульсных сигналов через элемент И 145. При любом другом состоянии счетчика 144, отличном от нулевого, элемент И 145 открыт, так как на его первом входе сигнал с уровнем логической 1, Наличие элемента И 145 обусловлено тем, что при нулевом состоянии счетчика 144 импульс, поступающий на его вход обратного счета, перевел бы его в состояние переполнения, что вызвало бы ошибку при контроле правильных действий операторов,

Выход счетчика 144 соединен с первым входом седьмого компаратора 140, При превышении значения кода на первом входе любого из компараторов 135 140 на его выходе формируется сигнал с уровнем логической 1, В результате этого на выходе элемента ИЛИ 14 формируется сигнал перехода на более низкий уровень сложности предъявляемой учебной информации, а на выходе шестого компаратора 140 формируется сигнал перехода на более высокий уровень предъявляемой учебной информации.

Первый 142 и второй 143 формирователи по фронтам сигналов с выходов соответственно элемента ИЛИ 141 и шестого компаратора 140 на выходах 152 и 153 формируют импульсные сигналы. Входы 127-131 образуют шину, соединяющую первый, а входы 146-151 образуют тину, соединяющую пятый входы блока 16 контроля соответственно

оо

р, 5-л 41 е оао

647620

%

24

10

15

20

25

30

35

40

45

50

55

с вторым выходом блока 15 и вторым выходом блока 13. Входы 134, 113 и 124 являются соответственно вторым, третьим и четвертым входами блока 16. Выходы 152 и 153 являются соответственно первым и вторым выходами блока 16.

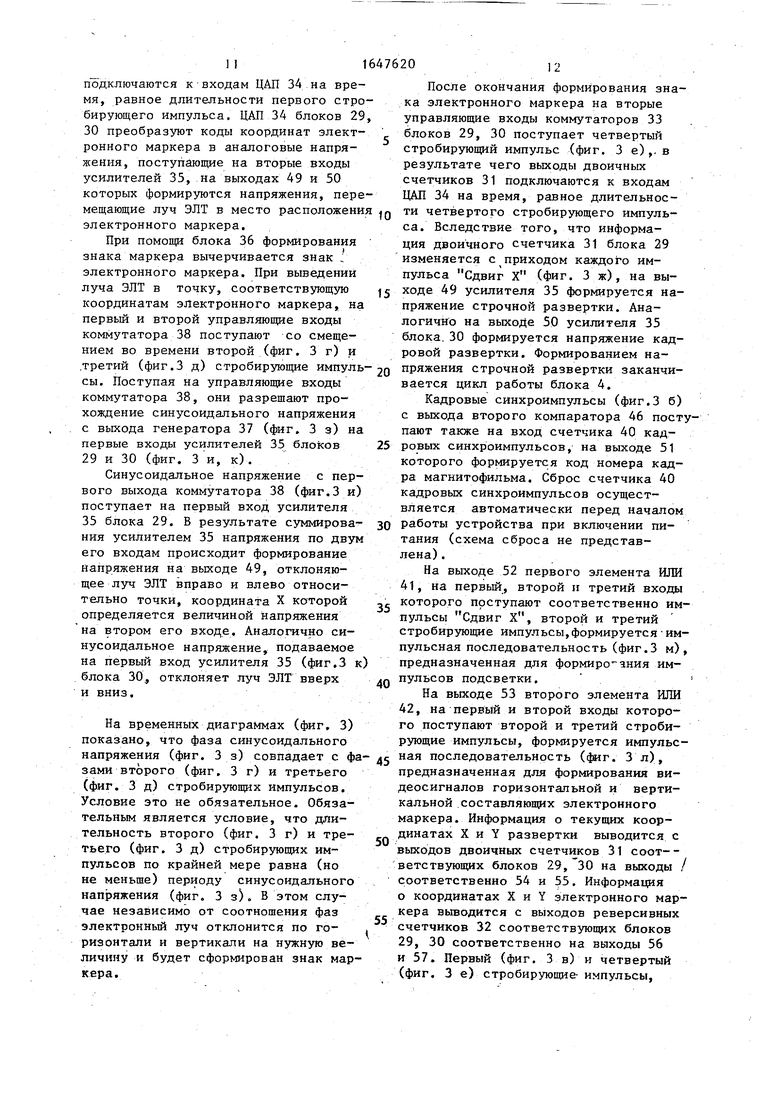

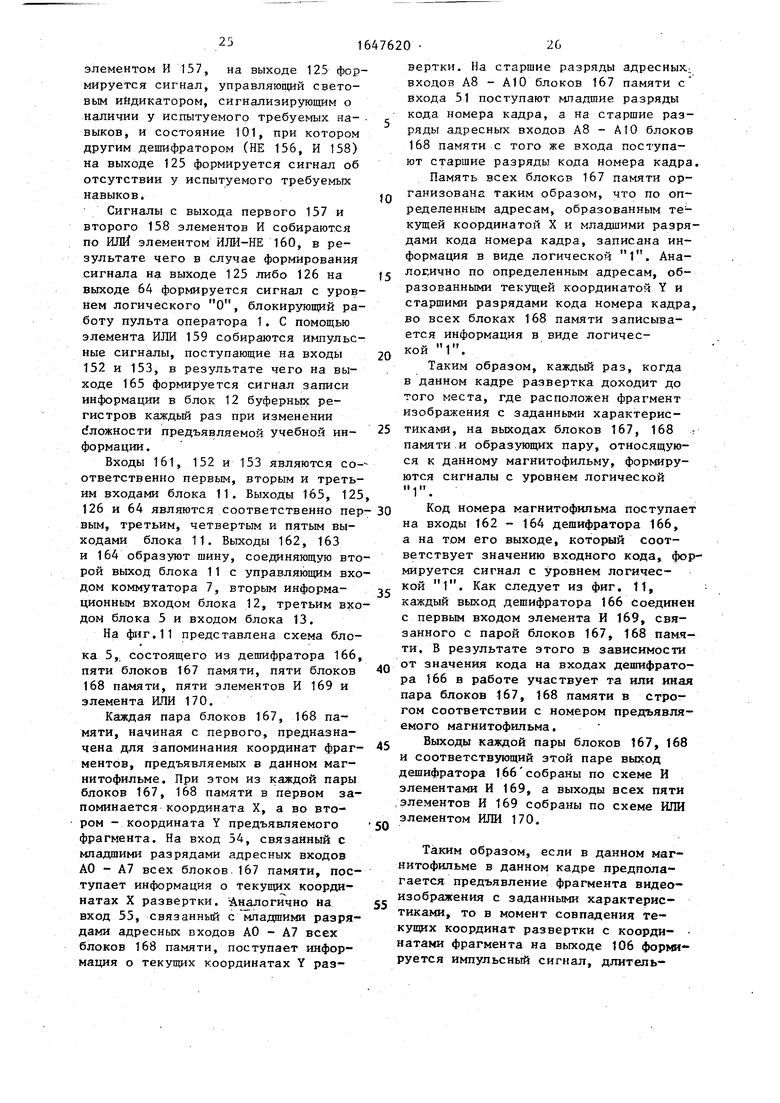

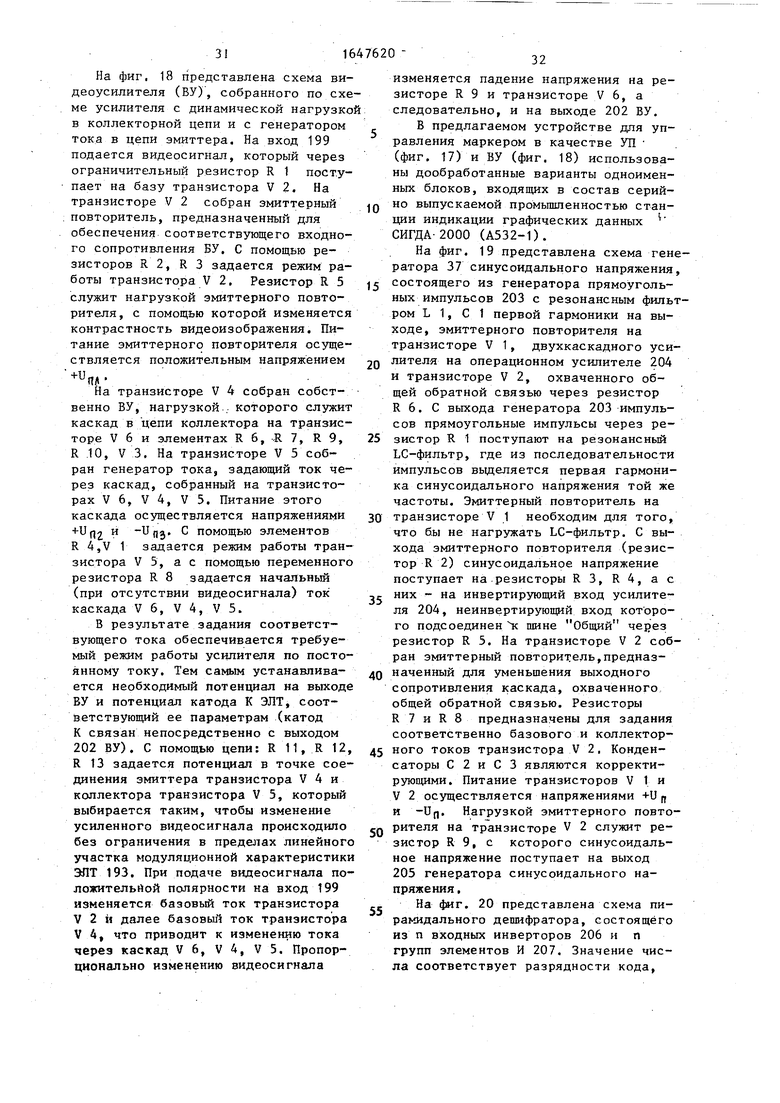

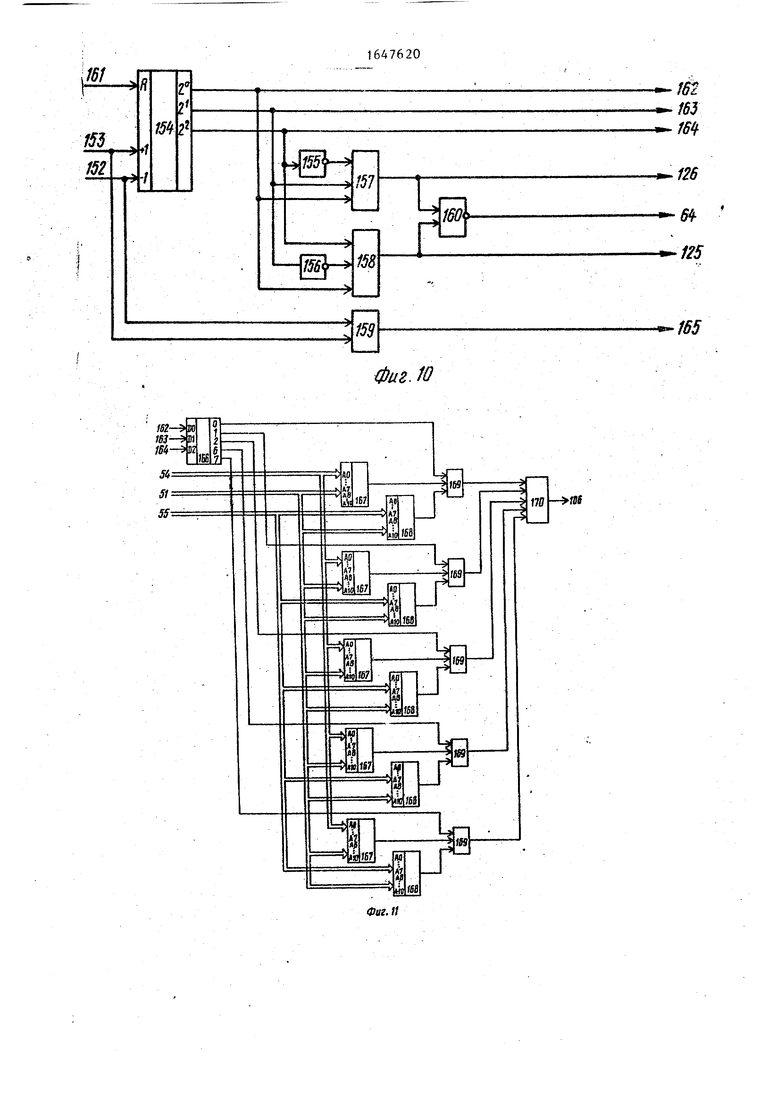

На фиг. 10 представлена схема второго блока 11 управления коммутатором видеосигналов, состоящего из реверсивного счетчика 154, первого 155, второго 156 элементов НЕ,первого 157 и второго 158 элементов И, элемента ИЛИ 159, элемента ИЛИ-НЕ 160. При поступлении импульсного сигнала на вход 161 реверсивньй счетчик 154 устанавливается в исходное (нулевое) состояние. Выходы 162-164 реверсивного счетчика 154 связаны с управляющими входами коммутатора видеосигналов 7 (фиг. 1). При нулевом состоянии реверсивного счетчика коммутатор 7 видеосигналов находится в состоянии, при котором через него проходит видеосигнал, соответствующий учебной видеоинформации средней сложности. При поступлении импульсного сигнала на вход 152 содержимое счетчика 154 уменьшается на одну единицу, а при подаче импульсного сигнала на вход

153содержимое реверсивного счетчика 154 увеличивается на одну единицу. Очевидно, что при этом изменяется код на выходах 162 - 164, связанных с коммутатором 7 видеосигналов.

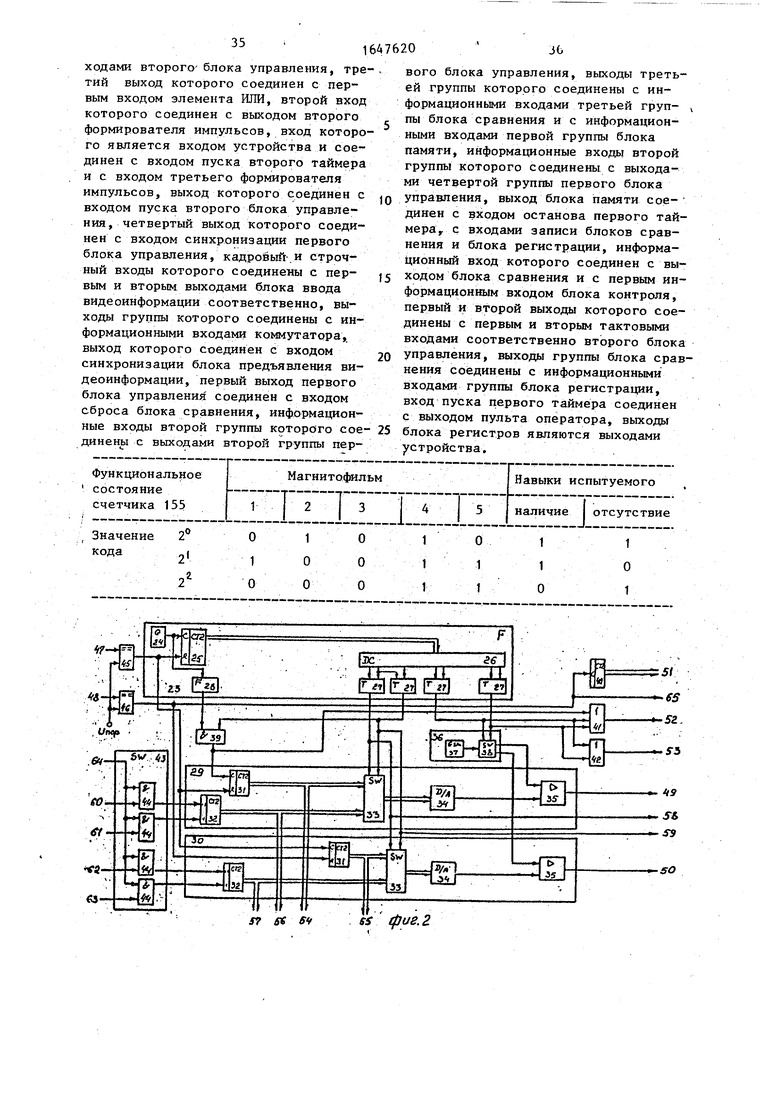

Для удобства объяснения принципа работы блока 11 в таблице сведены номера предъявляемых магнь.офильмов, формируемые сигналы о наличии или отсутствии у испытуемого оператора требуемых навыков и соответствующие им коды реверсивного счетчика 154.

Как следует из таблицы, счетчик

154может хранить семь значений кодовых комбинаций. При этом нулевое состояние соответствует магнито- фильму 3 со средней сложностью предъявляемой учебной информации. Изменяя содержимое реверсивного счетчика 154 путем подачи импульсных сигналов на вход прямого 153 и обратного 154 счета, можно устанавливать код, соответствующий одному из пяти магнитофильмов.

Реверсивный счетчик 154 имеет два крайних состояния: состояние 110, при котором дешифратором, образованным элементом НЕ 155 и первым

элементом И 157, на выходе 125 формируется сигнал, управляющий световым индикатором, сигнализирующим о наличии у испытуемого требуемых яа- выков, и состояние 101, при котором другим дешифратором (НЕ 156, И 158) на выходе 125 формируется сигнал об отсутствии у испытуемого требуемых навыков.

Сигналы с выхода первого 157 и второго 158 элементов И собираются по ИЛИ элементом ИЛИ-НЕ 160, в результате чего в случае формирования сигнала на выходе 125 либо 126 на выходе 64 формируется сигнал с уровнем логического О, блокирующий работу пульта оператора 1. С помощью элемента ИЛИ 159 собираются импульсные сигналы, поступающие на входы 152 и 153, в результате чего на выходе 165 формируется сигнал записи информации в блок 12 буферных регистров каждый раз при изменении Сложности предъявляемой учебной ин- формации.

Входы 161, 152 и 153 являются со- ответственно первым, вторым и третьим входами блока 11. Выходы 165, 125 126 и 64 являются соответственно пер вым, третьим, четвертым и пятым выходами блока 11. Выходы 162, 163 и 164 образуют шину, соединяющую второй выход блока 11с управляющим входом коммутатора 7, вторым информа- ционным входом блока 12, третьим входом блока 5 и входом блока 13.

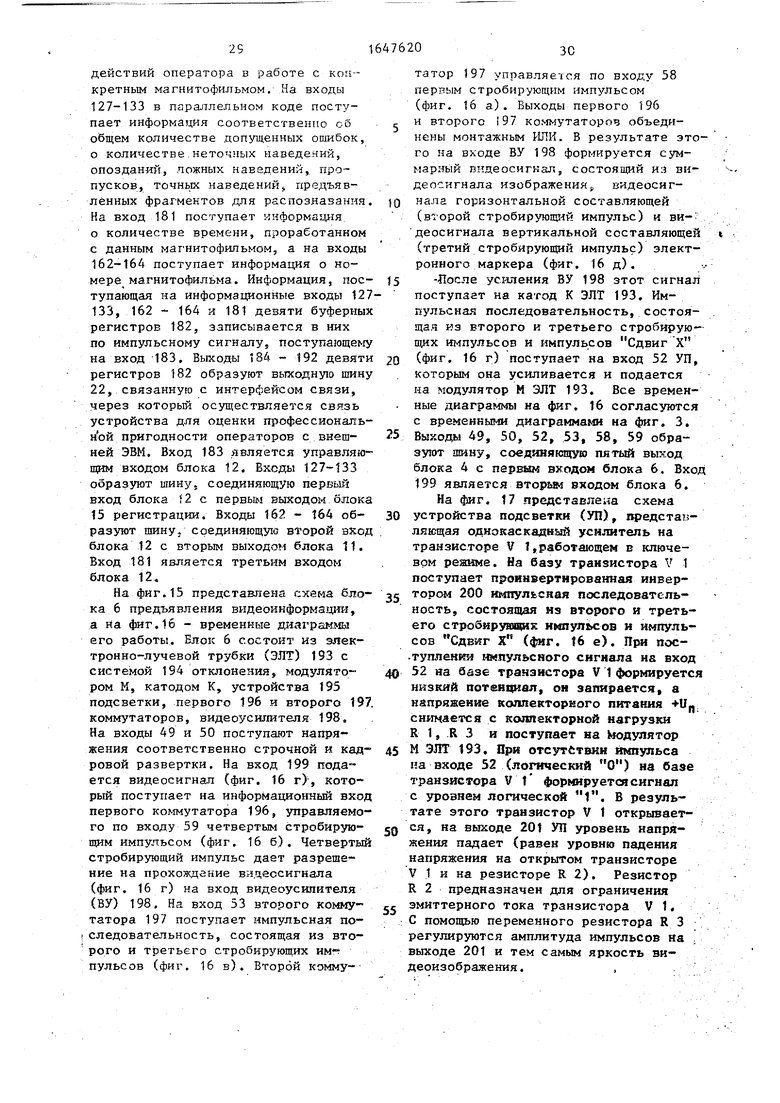

На фиг.11 представлена схема блока 5, состоящего из дешифратора 166, пяти блоков 167 памяти, пяти блоков 168 памяти, пяти элементов И 169 и элемента ИЛИ 170.

Каждая пара блоков 167, 168 памяти, начиная с первого, предназначена для запоминания координат фраг- ментов, предъявляемых в данном маг- нитофильме. При этом из каждой пары блоков 167, 168 памяти в первом запоминается координата X, а во втором - координата Y предъявляемого фрагмента. На вход 54, связанный с младшими разрядами адресных входов АО - А7 всех блоков 167 памяти, поступает информация о текущих координатах X развертки. Аналогично на вход 55, связанный с младшими разрядами адресных входов АО - А7 всех блоков 168 памяти, поступает информация о текущих координатах Y развертки. На старшие разряды адресных, входов А8 - А10 блоков 167 памяти с входа 51 поступают младшие разряды кода номера кадра, а на старшие разряды адресных входов А8 - А10 блоков 168 памяти с того же входа поступают старшие разряды кода номера кадра

Память всех блоков 167 памяти организована, таким образом, что по определенным адресам, образованным текущей координатой X и младшими разрядами кода номера кадра, записана информация в виде логической 1. Аналогично по определенным адресам, образованными текущей координатой Y и старшими разрядами кода номера кадра во всех блоках 168 памяти записывается информация в виде логической 1.

Таким образом, каждый раз, когда в данном кадре развертка доходит до того места, где расположен фрагмент изображения с заданными характеристиками, на выходах блоков 167, 168 памяти и образующих пару, относящуюся к данному магнитофильму, формируются сигналы с уровнем логической

it i it

1 .

Код номера магнитофильма поступает на входы 162 - 164 дешифратора 166, а на том его выходе, который соответствует значению входного кода, формируется сигнал с уровнем логической 1. Как следует из фиг. 11, каждый выход дешифратора 166 соединен с первым входом элемента И 169, связанного с парой блоков 167, 168 памяти. В результате этого в зависимости от значения кода на входах дешифратора 166 в работе участвует та или иная пара блоков 167, 168 памяти в строгом соответствии с номером предъявляемого магнитофильма.

Выходы каждой пары блоков 167, 168 и соответствующий этой паре выход дешифратора 166 собраны по схеме И элементами И 169, а выходы всех пяти элементов И 169 собраны по схеме ШШ элементом ИЛИ 170.

Таким образом, если в данном маг- нитофильме в данном кадре предполагается предъявление фрагмента видеоизображения с заданными характеристиками, то в момент совпадения текущих координат развертки с координатами фрагмента на выходе 106 формируется импульсный сигнал, длитель

ность которого равна длительности импульса Сдвиг X.

Входы 162 - 164 образуют шину, соединяющую третий вход блока 5 с вторым выходом блока 11. Входы 54 и 55 образуют шину, соединяющую первый вход блока 5 с третьим выходом блока 4. Вход 51 и выход 106 являются соответственно вторым входом и выходом блока 5.

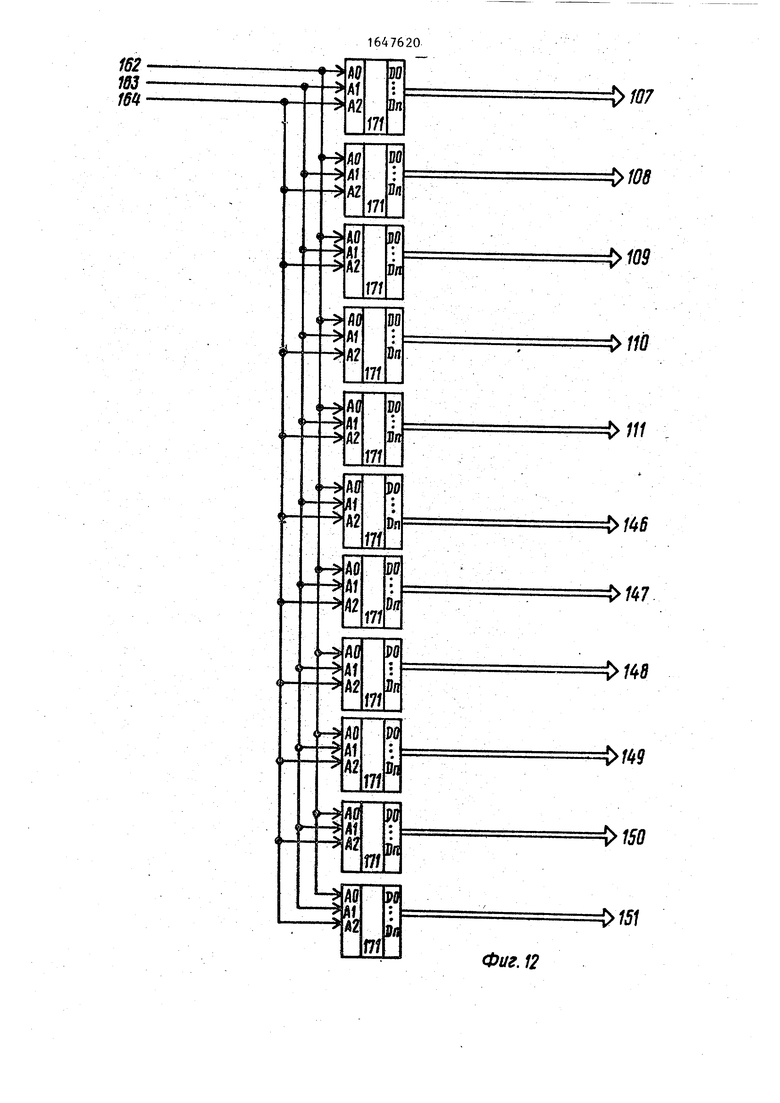

На фиг. 12 представлена схема блока ввода эталонов, состоящего из одиннадцати блоков 171 памяти, каждый из которых предназначен для хранения своего вида эталонов или нормативов. В блоках 171 памяти с первого по одиннадцатый в параллельном двоичном коде хранятся нормативы

АХ, UY, ДХ2 ЙУ2

соответственно -г-, -j-. -s-,

общего количества ошибок, неточных наведений, опозданий, ложных наведений, пропусков, точный наведений На адресные входы всех одиннадцати блоков 171 памяти поступает информация с входов 162 - 164 о номере маг- нитофильма. В каждом блоке 171 памяти по пяти адресам записаны значения данного норматива для пяти маг- нитофильмов в соответствии с уровне сложности предъявляемой информации. Таким образом, в зависимости от значения кода на входах 162 - 164, на входах 107 - 111 146 - 151 выстав- ляются требуемые для данного магнито фильма нормативы. Входы 162 - 164 образуют шину, соединяющую вход блока 13 ввода эталонов с вторым выходо блока 11. Выходы 107 -111 образуют шину, соединяющую первый, а выходы 146 - 151 - шину, соединяющую второй выходы блока 13 соответственно с седьмым входом блока 3 и пятым входом блока 16.

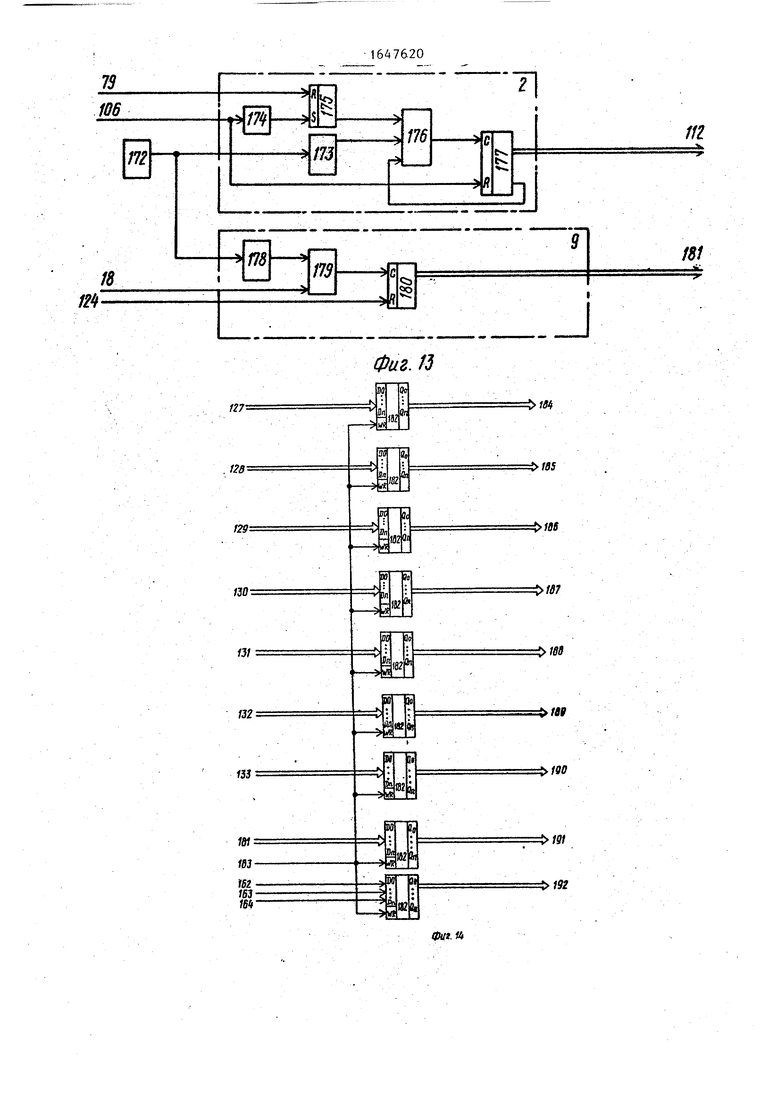

На фиг.13 представлены схемы первого 2 и второго 19 таймеров. Генератор 172 является общим для первого таймера 2, содержащего делитель 173 частоты, формирователь 174, триггер 175, элемент И 176, счетчик 177, и второго таймера 19, содержащего делитель 178 частоты, элемент И и счетчик 180. При поступлении импульсного сигнала на вход 106, являющийся одновременно входом формирователя 174 и входом установки исходного состояния счетчика 177, по следний обнуляется. На выходе фор

0

5

0

5 0 - о

5

0

5

мирователя 174 по спаду его входного импульсного сигнала формируется импульс, устанавливающий триггер 175 в состояние, при котором на его выходе формируется сигнал с уровнем логической 1, В результате этого элемент И 176 открыт (на его третьем входе также сигндл с уровнем логической 1), импульсы с выхода генератора 172 через делитель 173 частоты поступают на счетный вход счетчика 177, При поступлении импульсного сигнала на вход 79 триггер 175 устанавливается в состояние, при котором на его выходе формируется сигнал с уровнем логического О. Элемент И 176 закрывается и прекращает поступление импульсов с выхода генератора 172 на счетный вход счетчика 177. Если же импульсный сигнал на входе 79 отсутствует, то счетчик 177 осущес-твля- ет счет до переполнения. При установке счетчика 177 в состояние переполнения с второго его выхода на третий вход элемента И 176 поступает сигнал с уровнем логического О, запрещающий дальнейший счет.

Коэффициент деления делителя 173 выбран таким, что частота импульсов на его выходе составляет 0,1 Гц. В качестве счетчика 177 используется восьмиразрядный двоично-десятичный счетчик, первая тетрада которого несет информацию о десятых секунды, а вторая тетрада несет информацию о единицах секунд.

Второй таймер 19 осуществляет непрерывный счет при надичш разрешающего сигнала с уровнем логической 1 на входе 18. -На вход 124 поступает импульсный сигнал, обнуляющий счетчик 180, после чего счет возобновляется. В качестве счетчика 180 используется четырехтетрадный двоично- десятичный счетчик, каждая тетрада которого несет информацию соответственно о единицах, десятках секунд, единицах и десятках минут. Входы 79 и 106 являются соответственно первым и вторым входами, а выход 112 является выходом первого таймера 2. Выходы 18 и 24 являются соответственно первым и вторым, а выход 181 является выходом второго таймера 19.

На фиг.14 представлена схема блока 12, содержащего девять буферных регистров 182, предназначенных для хранения информации о результатах

действий оператора в работе с коп - кретным магнитофильмом. На входы 127-133 в параллельном коде поступает информация соответственно с б общем количестве цопущенных ошибок, о количестве неточных наведений, опозданий, ножных наведении, пропусков, точных наведений, предъявленных фрагментов для распознавания. На вход 181 поступает информация о количестве времени, проработанном с данным магнитофильмом, а на входы 162-164 поступает информация о номере магнитофильма. Информация, поступающая на информационные входы 127 133, 162 - 164 и 181 девяти буферных регистров 182, записывается в них по импульсному сигналу, поступающему на вход 183, Выходы 18 - t92 девяти регистров 182 образуют выходную шину 22, связанную с интерфейсом связи, через который осуществляется связь устройства для оценки профессиональной пригодности операторов с внешней ЭВМ. Вход 183 является управляющим входом блока 12. Входы 127-133 образуют шину, соединяющую первый вход блока 12 с первым выходом блока 15 регистрации. Входы 16 - 164 образуют шину соединяющую второй вход блока 12 с вторым выходом блока 11. Вход 181 является третьим входом блока 12.

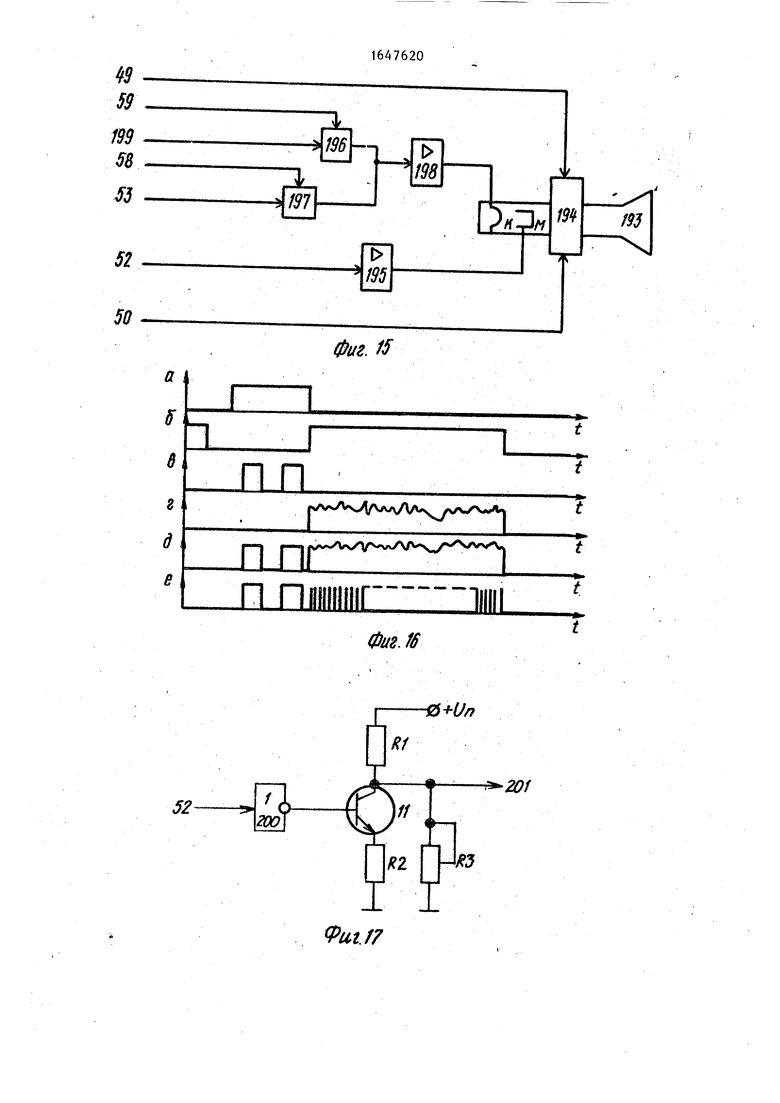

На фиг.15 представлена схема блока 6 предъявления видеоинформации, а на фиг.16 - временные диаграммы его работы. Елок 6 состоит из электронно-лучевой трубки (ЭЛТ) 193 с системой 194 отклонения, модулятором М, катодом К, устройства 195 подсветки, первого 196 и второго 197. коммутаторов, видеоусилителя 198. На входы 49 и 50 поступают напря жения соответственно строчной и кадровой развертки. На вход 199 пода™ ется видеосигнал (фиг. 16 г), который поступает на информационный вход первого коммутатора 196, управляемого по входу 59 четвертым стробирую- щим импульсом (фиг. 16 б). Четвертый стробирующий импульс дает разрешение на прохождение видеосигнала (фиг. 16 г) на вход видеоусилителя (ВУ) 198. На вход 53 второго коммутатора 197 поступает импульсная последовательность, состоящая из второго и третьего стробируюших импульсов (фиг, 16 в). Второй коммутатор 197 управляется по входу 58 первым стробирующим импульсом (фиг. 16 а). Выходы первого 196 и второго 197 коммутаторов объединены монтажным ИЛИ. В результате этого на входе ВУ 198 формируется суммарный видеосигнал, состоящий и.з видеосигнала изображения,, нидеосигнала горизонтальной составляющей (вюрой стробирующий импульс) и видеосигнала вертикальной составляющей i (третий стробирующий импульс) электронного маркера (фиг. 16 д).

5 -После усиления ВУ 198 этот сигнал поступает на катод К ЭЛТ 193, Импульсная последовательность, состоя- щач кз второго и третьего стробирую- щих импульсов и импульсов Сдвиг X

0 (Фиг. 16 г) поступает на вход 52 УП, которым она усиливается и подается на модулятор М ЭЛТ 193. Все времен- - ные диаграммы на фиг, 16 согласуются с временными диаграммами на фиг. 3.

5 Выходы 49, 50, 52, 53, 58, 59 образуют шину, соединяющую пятый выход блока 4 с первым входом блока 6. Вход 199 является вторьв-j входом блока 6. На фиг. 17 представлена схема

0 устройства подсветки (УП), представляющая однокаскадный усилитель на транзисторе V 1,работающем в ключевом режиме. На базу транзистора V 1 поступает проинвертнрсванная инвер5 тором 200 импульсная последовательность, состоящая нэ второго и третьего стробирующик импульсов и импульсов Сдвиг Xм (фиг. t6 e). При пос- тупленки импульсного сигнала на вход

0 52 на базе транзистора V 1 формируется низкий потенциал, он запирается, а напряжение коллекторного питания +U,, снимается с коллекторной нагрузки R 1, R 3 и поступает на модулятор

5 М ЭЛТ 193, При отсутствии импульса на входе 52 (логический О) на базе транзистора V Г формируется сигнал с уровнем логической 1. В результате этого транзистор V 1 открывает0 ся, на выходе 201 УП уровень напряжения падает (равен уровню падения напряжения на открытом транзисторе V 1 и на резисторе R 2). Резистор R 2 предназначен для ограничения

е эмиттерного тока транзистора V 1. С помощью переменного резистора R 3 регулируются амплитуда импульсов на выходе 201 и тем самым яркость ви- деоиз ображе ния. ,

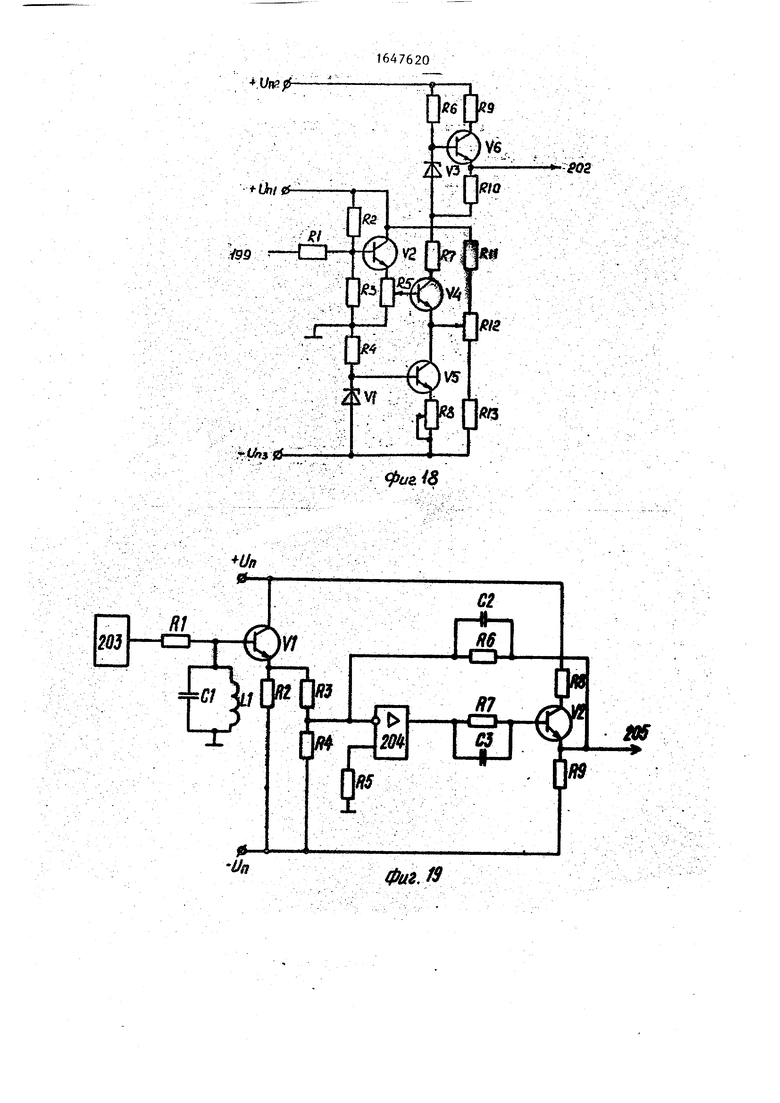

На фиг. 18 представлена схема видеоусилителя (ВУ), собранного по схеме усилителя с динамической нагрузко в коллекторной цепи и с генератором тока в цепи эмиттера. На вход 199 подается видеосигнал, который через ограничительный резистор R 1 поступает на базу транзистора V 2. На транзисторе V 2 собран эмиттерный повторитель, предназначенный для обеспечения соответствующего входного сопротивления БУ. С помощью резисторов R 2, R 3 задается режим работы транзистора V 2. Резистор R 5 служит нагрузкой эмиттерного повторителя, с помощью которой изменяется контрастность видеоизображения. Питание эмиттерного повторителя осуществляется положительным напряжением

+и™

На транзисторе V 4 собран собственно ВУ, нагрузкой которого служит каскад в цепи коллектора на транзисторе V 6 и элементах R6, R7, R9, R 10, V 3. На транзисторе V 5 собран генератор тока, задающий ток через каскад, собранный на транзисторах V 6, V 4, V 5. Питание этого каскада осуществляется напряжениями

+U

П2

и -U

ПЭ«

С помощью элементов

R 4,V 1 задается режим работы транзистора V 5, а с помощью переменного резистора R 8 задается начальный (при отсутствии видеосигнала) ток каскада V 6, V 4, V 5.

В результате задания соответствующего тока обеспечивается требуемый режим работы усилителя по постоянному току. Тем самым устанавливается необходимый потенциал на выходе ВУ и потенциал катода К ЭЛТ, соответствующий ее параметрам (катод К связан непосредственно с выходом 202 ВУ). С помощью цепи: R 11, R 12, R 13 задается потенциал в точке соединения эмиттера транзистора V 4 и коллектора транзистора V 5, который выбирается таким, чтобы изменение усиленного видеосигнала происходило без ограничения в пределах линейного участка модуляционной характеристики ЭЛТ 193. При подаче видеосигнала по- ложитепьйой полярности на вход 199 изменяется базовый ток транзистора V 2 и далее базовый ток транзистора V 4, что приводит к изменению тока через каскад V 6, V 4, V 5. Пропорционально изменению видеосигнала

0

5

0

5

0

5

O

5

изменяется падение напряжения на резисторе R 9 и транзисторе V 6, а следовательно, и на выходе 202 ВУ.

В предлагаемом устройстве для управления маркером в качестве УП (фиг. 17) и ВУ (фиг. 18) использованы дообработанные варианты одноименных блоков, входящих в состав серийно выпускаемой промышленностью станции индикации графических данных СИГДА 2000 (А532-1).

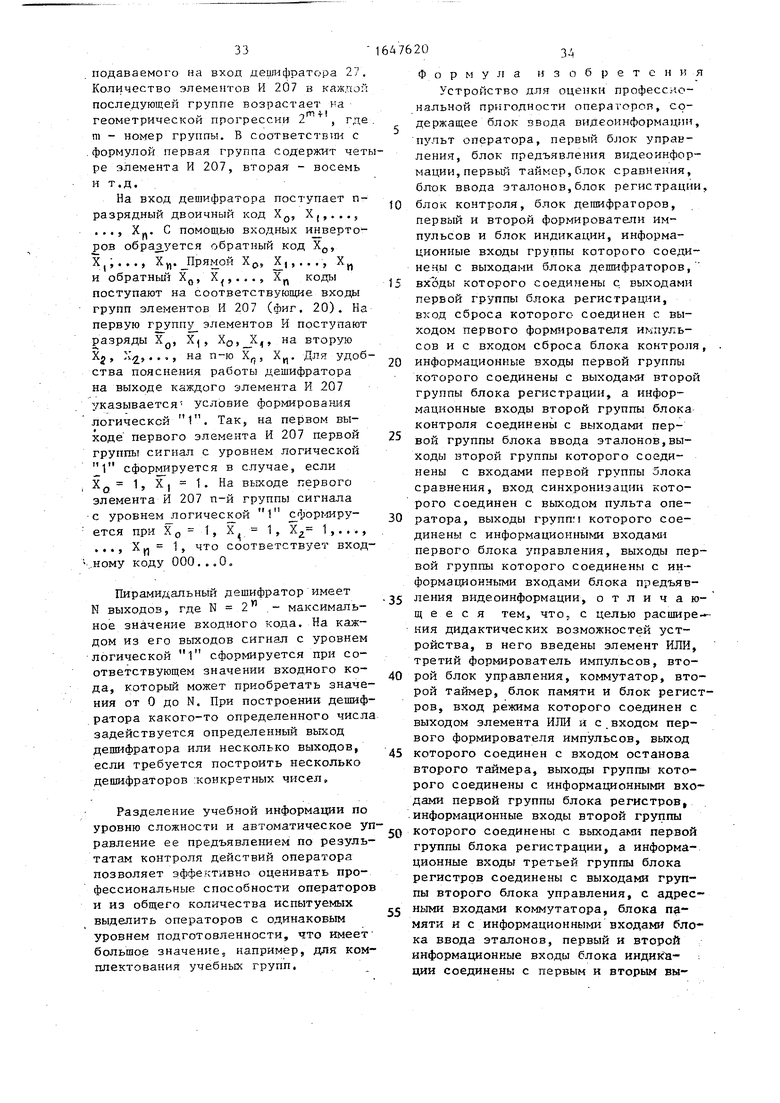

На фиг. 19 представлена схема генератора 37 синусоидального напряжения, состоящего из генератора прямоугольных импульсов 203 с резонансным фильтром L 1, С 1 первой гармоники на выходе, эмиттерного повторителя на транзисторе V 1, двухкаскадного усилителя на операционном усилителе 204 и транзисторе V 2, охваченного общей обратной связью через резистор R 6. С выхода генератора 203 импульсов прямоугольные импульсы через резистор R 1 поступают на резонансный LC-фильтр, где из последовательности импульсов выделяется первая гармоника синусоидального напряжения той же частоты. Эмиттерный повторитель на транзисторе V 1 необходим для того, что бы не нагружать LC-фильтр. С выхода эмиттерного повторителя (резистор R 2) синусоидальное напряжение поступает на резисторы R 3, R 4, а с них - на инвертирующий вход усилителя 204, неинвертирующий вход которого подсоединен к шине Общий через резистор R 5. На транзисторе V 2 собран эмиттерный повторитель,предназначенный для уменьшения выходного сопротивления каскада, охваченного общей обратной связью. Резисторы R 7 и R 8 предназначены для задания соответственно базового и коллекторного токов транзистора V 2. Конденсаторы С 2 и С 3 являются корректирующими. Питание транзисторов V 1 и V 2 осуществляется напряжениями +U и Ufj. Нагрузкой эмиттерного повторителя на транзисторе V 2 служит резистор R 9, с которого синусоидальное напряжение поступает на выход 205 генератора синусоидального напряжения ,

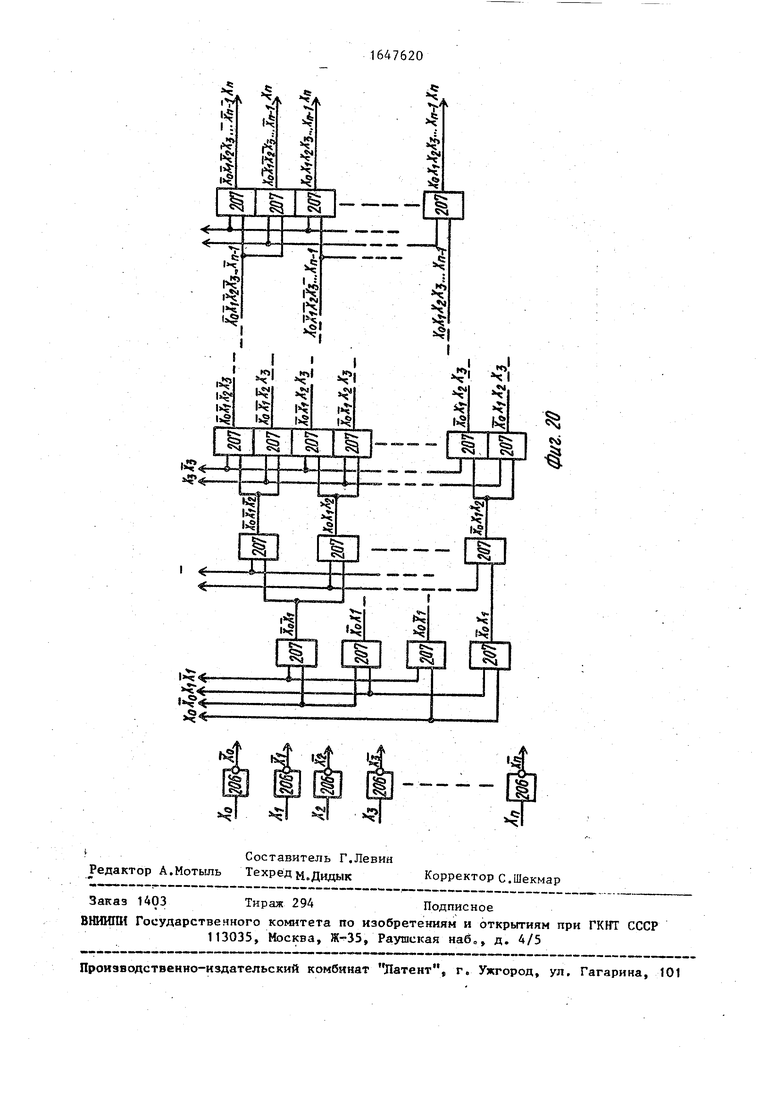

На фиг. 20 представлена схема пирамидального дешифратора, состоящего из п входных инверторов 206 и п групп элементов И 207. Значение числа соответствует разрядности кода,

33

подаваемого на вход дешифратора 11. Копичество элементов И 207 в каждой последующей группе возрастает на геометрической прогрессии 2 , где m - номер группы. В соответствии с формулой первая группа содержит четре элемента И 207, вторая - восемь и т.д.

На вход дешифратора поступает п- разрядный двоичный код XQ, X(,...s ..., X. С помощью входных инверторов образуется обратный код Х0, Х(;..., Хп.Прямой Х0, (,,..., Хп и обратный Х0, Х,. .., Хп коды поступают на соответствующие входы групп элементов И 207 (фиг. 20). На первую элементов И поступают разряды XQ, Xj, ХО,Х,, на вторую Хг , Х,. .., на n-ю Х,р Хп. Для удобства пояснения работы дешифратора на выходе каждого элемента И 207 указывается1 условие формирования логической 1. Так, на первом выходе первого элемента И 207 первой группы сигнал с уровнем логической 1 сформируется в случае, если Х0 1, X, 1. На выходе первого элемента И 207 n-й группы сигнала с уровнем логической Г1 сформируется при X 0 1, X 1 , Х2 1 ,. .., ..., Хп 1, что соответствует входному коду 000...О о

Пирамидальный дешифратор имеет N выходов,, где N 2 - максимальное значение входного кода. На каждом из его выходов сигнал с уровнем логической 1 сформируется при соответствующем значении входного кода, который может приобретать значения от 0 до N. При построении дешифратора какого-то определенного числ задействуется определенный выход дешифратора или несколько выходов, если требуется построить несколько дешифраторов конкретных чисел.

Разделение учебной информации по уровню сложности и автоматическое уравление ее предъявлением по результатам контроля действий оператора позволяет эффективно оценивать профессиональные способности операторо и из общего количества испытуемых выделить операторов с одинаковым уровнем подготовленности, что имеет большое значение, например, для комплектования учебных групп.

3.1

Формула изобретения

Устройство дпя оценки профессиональной пригодности операторов, содержащее блок ввода видеоинформации, пульт оператора, первый блок управления, блок предъявления видеоинформации, первый таймер,блок сравнения, блок ввода эталонов,блок регистрации,

tO блок контроля, блок дешифраторов, первый и второй формирователи импульсов и блок индикации, информационные входы группы которого соединены с выходами блока дешифраторов,

15 которого соединены с выходами первой группы блока регистрации, вход сброса которого соединен с выходом первого формирователя импульсов и с входом сброса блока контроля,

0 информационные входы первой группы которого соединены с выходами второй группы блока регистрации, а информационные входы второй группы блока контроля соединены с выходами первой группы блока ввода эталонов,выходы второй группы которого соединены с входами первой группы блока сравнения, вход синхронизации которого соединен с выходом пульта опе0 ратора, выходы группм которого соединены с информационными входами первого блока управления, выходы первой группы которого соединены с информационными входами блока предъяв- 5 ления видеоинформации, отличающееся тем, что, с целью расширения дидактических возможностей устройства, в него введены элемент ИЛИ, третий формирователь импульсов, вто0 рой блок управления, коммутатор, второй таймер, блок памяти и блок регистров, вход режима которого соединен с выходом элемента ИЛИ и с входом первого формирователя импульсов, выход

5 которого соединен с входом останова второго таймера, выходы группы которого соединены с информационными входами первой группы блока регистров, информационные входы второй группы

0 которого соединены с выходами первой группы блока регистрации, а информационные входы третьей группы блока регистров соединены с выходами группы второго блока управления, с адрес-

5 ными входами коммутатора, блока памяти и с информационными входами блока ввода эталонов, первый и второй информационные входы блока индикации соединены с первым и вторым вы-

ходами второго- блока управления, тре тий выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго формирователя импульсов, вход которо го является входом устройства и соединен с входом пуска второго таймера и с входом третьего формирователя импульсов, выход которого соединен с входом пуска второго блока управления, четвертый выход которого соединен с входом синхронизации первого блока управления, кадровый и строчный входы которого соединены с первым и вторым выходами блока ввода видеоинформации соответственно, выходы группы которого соединены с информационными входами коммутатора, выход которого соединен с входом синхронизации блока предъявления видеоинформации, первый выход первого блока управления соединен с входом сброса блока сравнения, информационные входы второй группы которого сое динены с выходами второй группы первого блока управления, выходы третьей группы которого соединены с информационными входами третьей труп- v

с пы блока сравнения и с информационными входами первой группы блока памяти, информационные входы второй группы которого соединены с выходами четвертой группы первого блока

Ю Управления, выход блока памяти соединен с входом останова первого таймера,, с входами записи блоков сравнения и блока регистрации, информационный вход которого соединен с выJ5 ходом блока сравнения и с первым информационным входом блока контроля, первый и второй выходы которого соединены с первым и вторым тактовыми входами соответственно второго блока

20 управления, выходы группы блока сравнения соединены с информационными входами группы блока регистрации, вход пуска первого таймера соединен с выходом пульта оператора, выходы 25 блока регистров являются выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования видеоизображений | 1988 |

|

SU1603421A1 |

| Устройство для управления маркером | 1988 |

|

SU1522270A1 |

| Устройство для управления маркером на экране электронно-лучевой трубки | 1987 |

|

SU1501133A1 |

| Система управления телескопом | 1984 |

|

SU1188699A1 |

| СПОСОБ НАВЕДЕНИЯ ТЕЛЕОРИЕНТИРУЕМОЙ В ЛУЧЕ РАКЕТЫ И РАКЕТНЫЙ КОМПЛЕКС ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2266509C1 |

| ТРЕНАЖЕР ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ КОРАБЕЛЬНЫХ ПАССИВНЫХ РАДИОЛОКАЦИОННЫХ СИСТЕМ | 1989 |

|

SU1841103A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| ТРЕНАЖЕР ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ КОРАБЕЛЬНЫХ ПАССИВНЫХ РАДИОЛОКАЦИОННЫХ СИСТЕМ | 1989 |

|

SU1841104A1 |

| ТРЕНАЖЕР ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ КОРАБЕЛЬНЫХ ПАССИВНЫХ РАДИОЛОКАЦИОННЫХ СИСТЕМ | 1989 |

|

SU1841105A1 |

| Устройство для считывания графической информации | 1988 |

|

SU1536413A1 |

Изобретение относится к автоматике и вычислительной технике. Цепь изобретения - расширение дидактических возможностей устройства. Устройство содержит пульт оператора 1, первый таймер 2, блок сравнения 3, первый блок управления 4, блок памяти 5, блок предъявления видеоинформации 6, коммутатор 7, блок ввода видеоинформации 8, первый формирователь 9 импульсов, элемент ИЛИ 10, второй блок управления 11, блок 12 регистров, блок 13 ввода эталонов, бпол индикации 14, блок регистрации 15, блок контроля 16, блок 17 дешифраторов, вход 18 устройства, второй . аймер 19, второй и третий формирователи 20, 21 импульсов и лыход 22 устройства. Введением в устройство второго блока упразлекия 11, второго таймера 19, третье:о формирователя 21, коммутатора 7, блока пз.чти 5, liJlll 10 и блика 12 регистров осуществляются раздепсчие учебной информации по уровню сложности II автоматическое управление ее предъявлением, что позволяет более эффективно оценивать профессиональные способности операlopos и аз общего количества испытуемых выделить операторов с одинаковым уровнем подготов- лр.ности4 чтп имеет большое значение, например для комплектования учебных групп, что ведет к расширению дидактических возможностей устройства. 20 ил., 1 табл. ЦЭ

W

f Sf 64

ss фие. 2

иг

линии и L

и и

У

Я

г

Фиг. 5

61

62

79

т

чг

МЗ

Фиг 6

Хн2Хм1

Фиг. 7

Jfmax Л

°

«у

W

01 ПФ

162 W3

т

Фиг. /J

Фиг./7

Фиг. 16

0+Un

2O1

+

/95 tZU

rCfotf

-еог

pu&48

Фиг.Ю

Авторы

Даты

1991-05-07—Публикация

1989-03-20—Подача