Изобретение относится к импульсной технике и может найти применение в корректируемых шкалах времени, генераторах задержанных импульсов и синтезаторах интервалов времени.

Цель изобретения - расширение функциональных возможностей за счет обеспечения реверсивного сдвига информации.

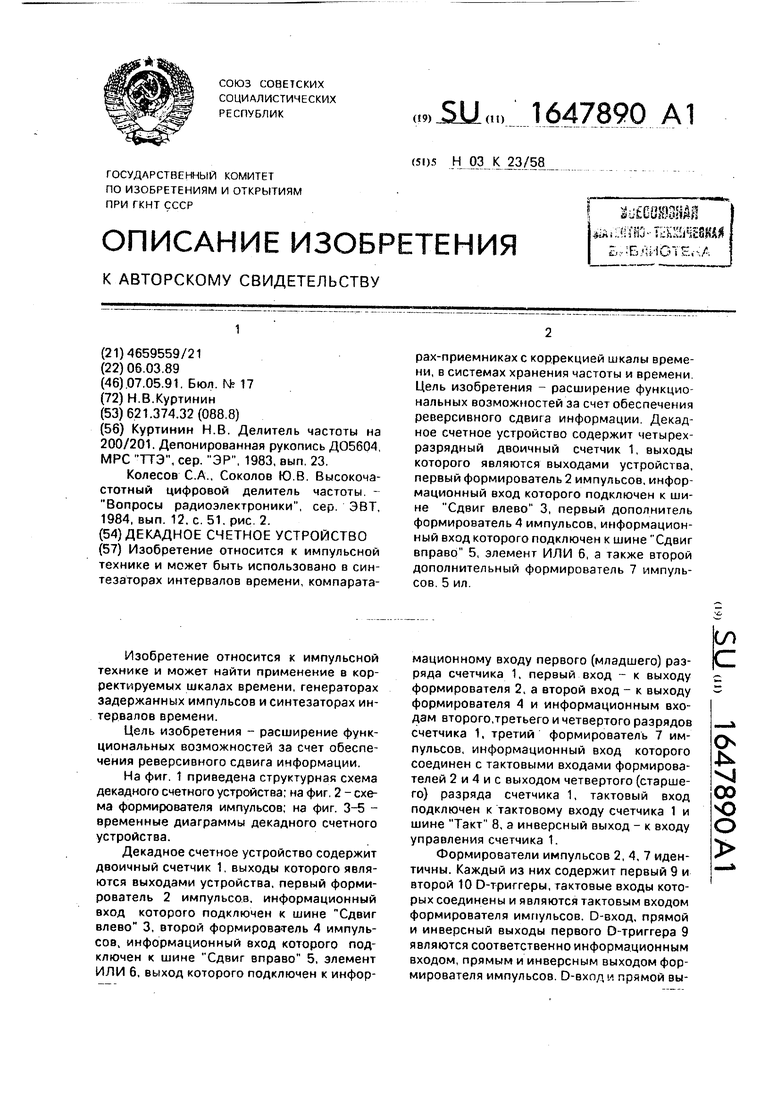

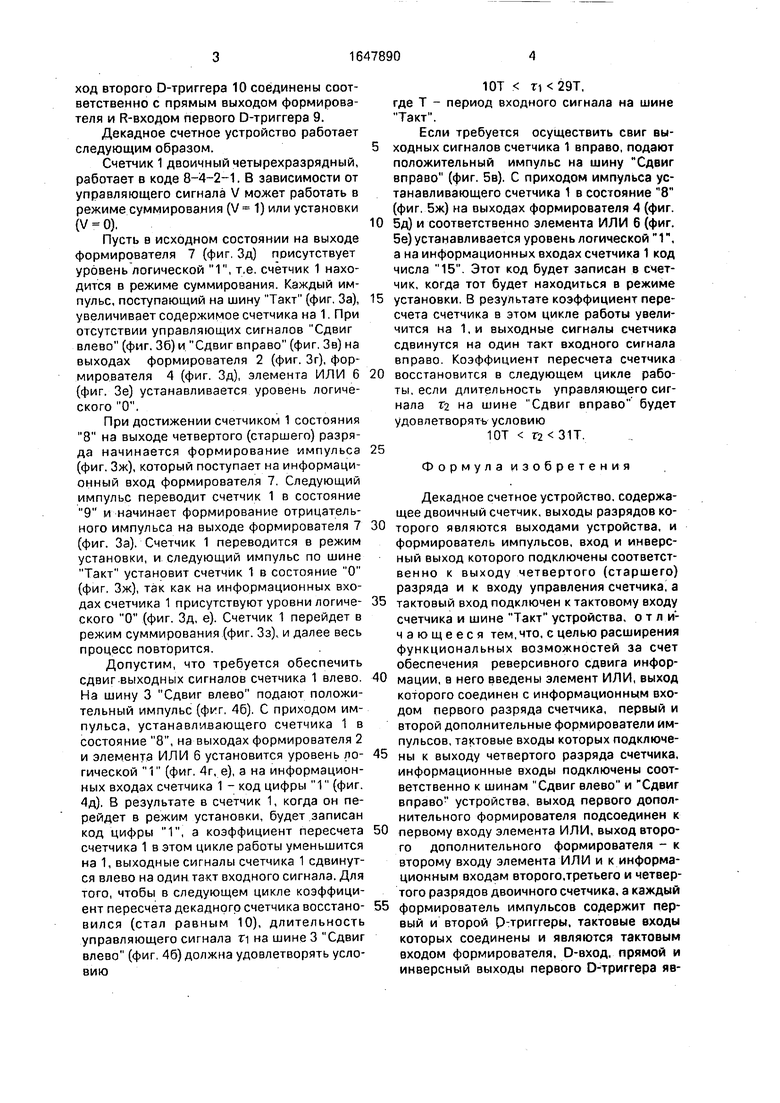

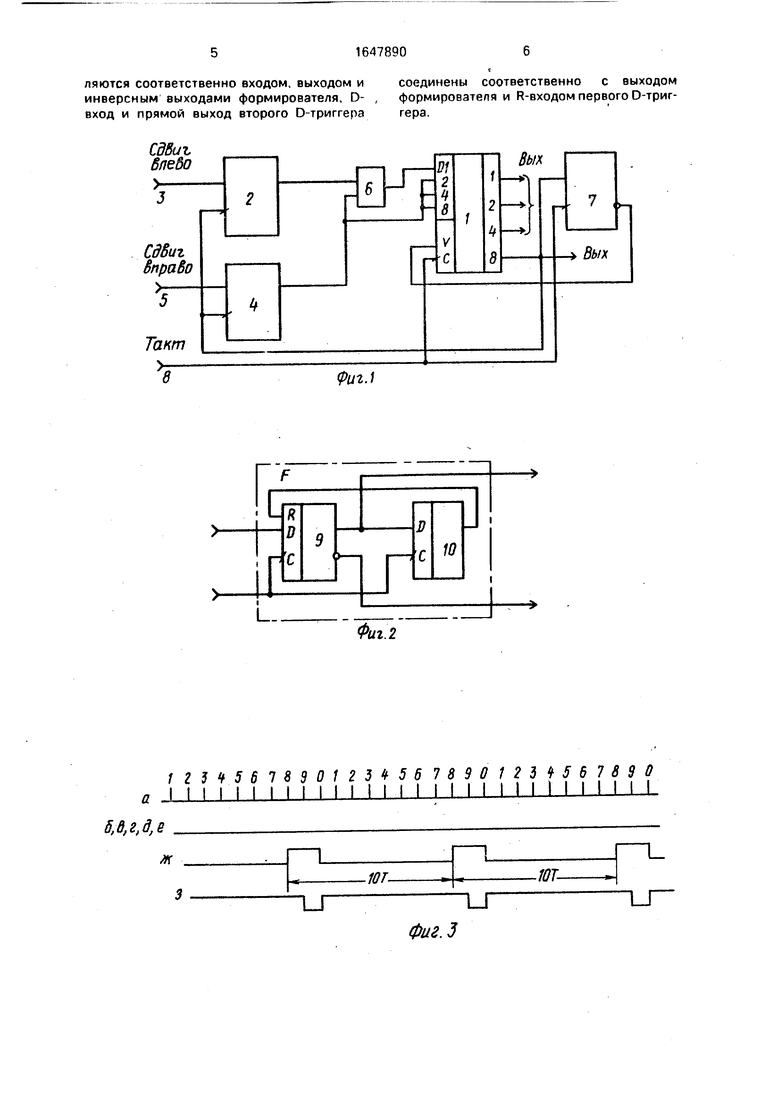

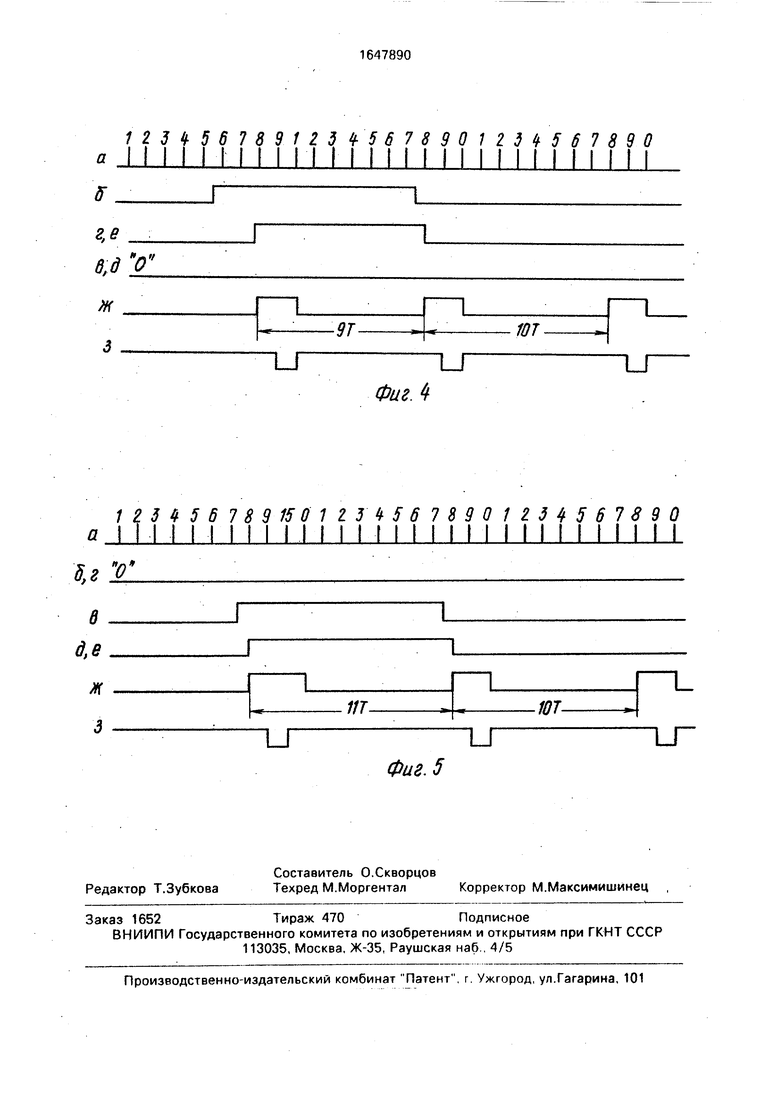

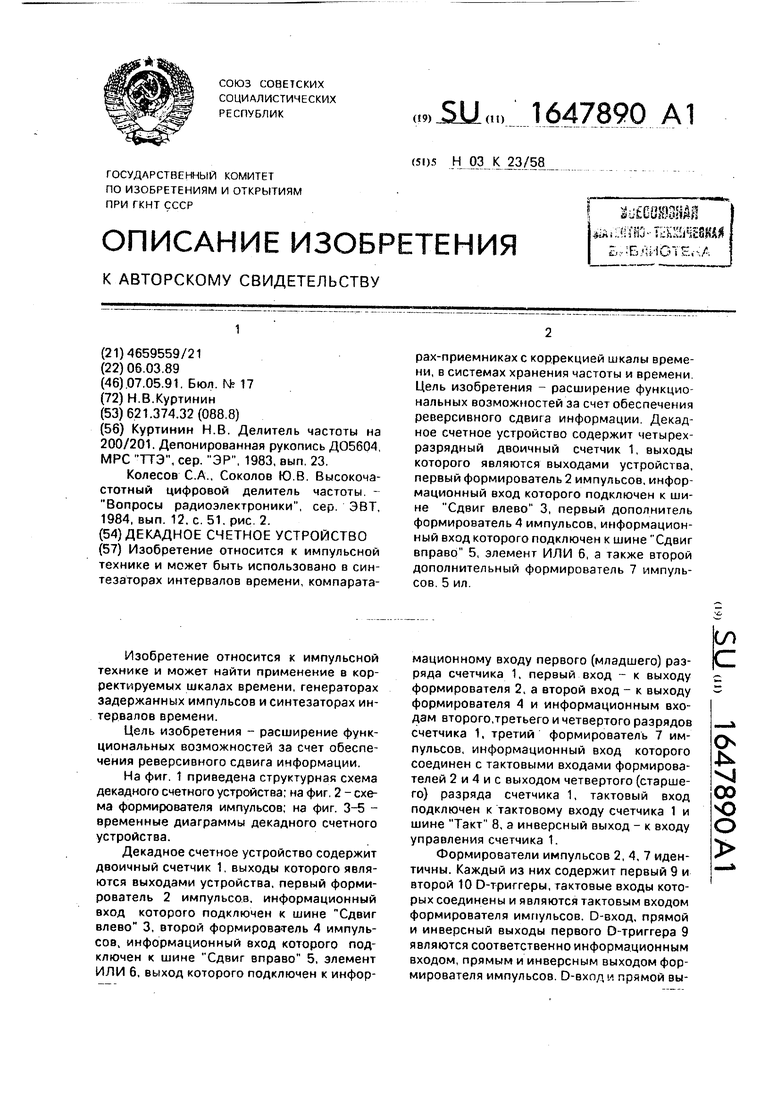

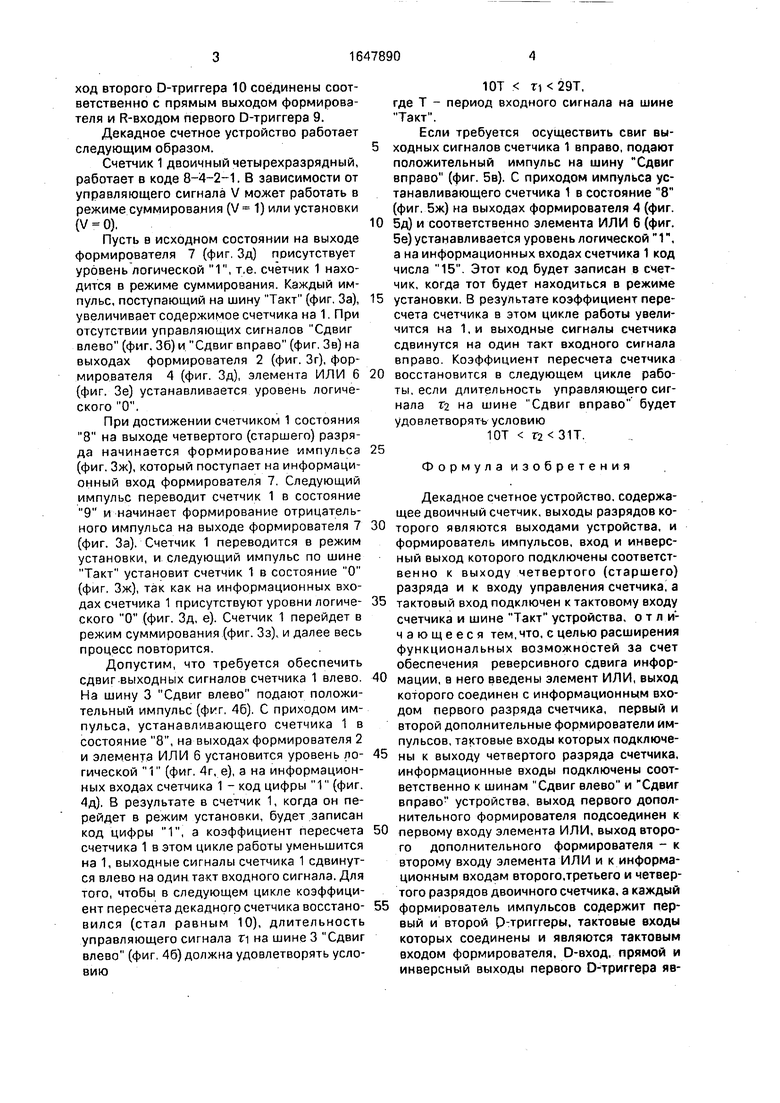

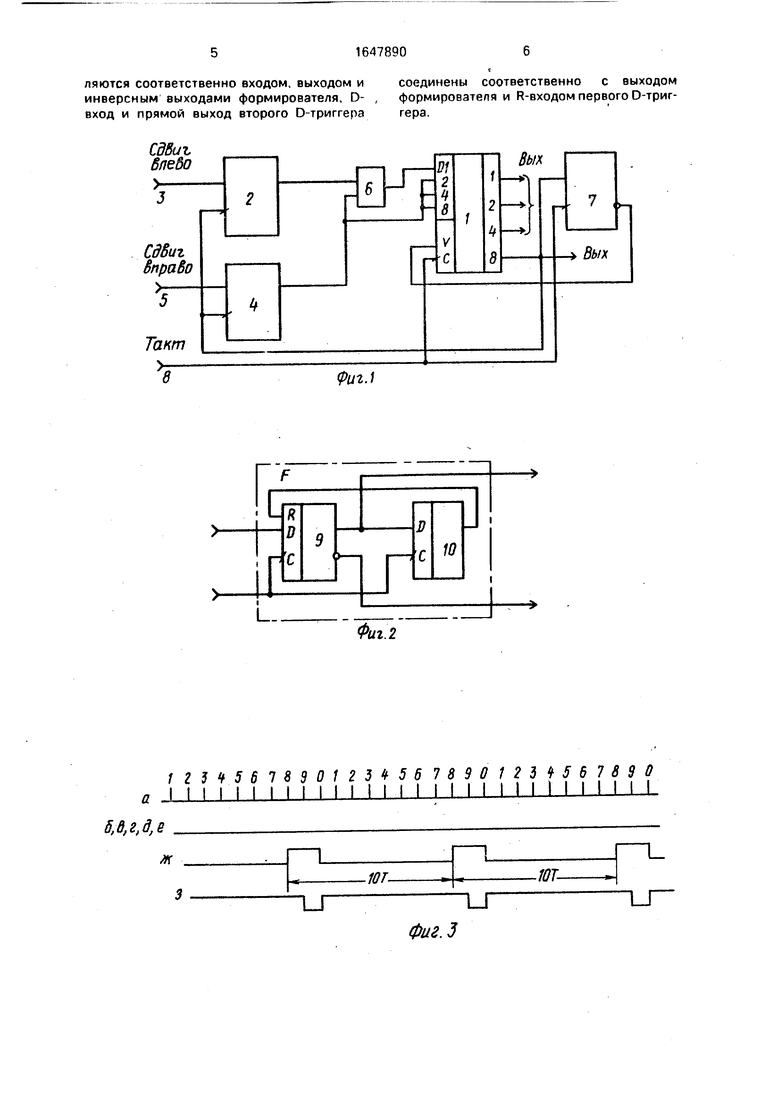

На фиг. 1 приведена структурная схема декадного счетного устройства; на фиг. 2 - схема формирователя импульсов; на фиг. 3-5 - временные диаграммы декадного счетного устройства.

Декадное счетное устройство содержит двоичный счетчик 1, выходы которого являются выходами устройства, первый формирователь 2 импульсов, информационный вход которого подключен к шине Сдвиг влево 3, второй формирователь 4 импульсов, информационный вход которого подключен к шине Сдвиг вправо 5, элемент ИЛИ 6, выход которого подключен к информационному входу первого (младшего) разряда счетчика 1, первый вход - к выходу формирователя 2, а второй вход - к выходу формирователя 4 и информационным входам второго,третьего и четвертого разрядов счетчика 1, третий формирователь 7 импульсов, информационный вход которого соединен с тактовыми входами формирователей 2 и 4 и с выходом четвертого (старшего) разряда счетчика 1, тактовый вход подключен к тактовому входу счетчика 1 и шине Такт 8, а инверсный выход - к входу управления счетчика 1.

Формирователи импульсов 2, 4, 7 идентичны. Каждый из них содержит первый 9 и второй 10 D-триггеры, тактовые входы которых соединены и являются тактовым входом формирователя импульсов. D-вход, прямой и инверсный выходы первого D-триггера 9 являются соответственно информационным входом, прямым и инверсным выходом формирователя импульсов. D-вход и прямой вы(Л

С

о

V4 00 Ю О

ход второго D-триггера 10 соединены соответственно с прямым выходом формирователя и R-входом первого D-триггера 9.

Декадное счетное устройство работает следующим образом.

Счетчик 1 двоичный четырехразрядный, работает в коде 8-4-2-1. В зависимости от управляющего сигнала V может работать в режиме суммирования (V - 1) или установки (V 0).

Пусть в исходном состоянии на выходе формирователя 7 (фиг. Зд) присутствует уровень логической 1, т.е. счётчик 1 находится в режиме суммирования. Каждый импульс, поступающий на шину Такт (фиг. За), увеличивает содержимое счетчика на 1, При отсутствии управляющих сигналов Сдвиг влево (фиг. 36) и Сдвиг вправо (фиг. Зв) на выходах формирователя 2 (фиг. Зг), формирователя 4 (фиг. Зд), элемента ИЛИ 6 (фиг. Зе) устанавливается уровень логического О.

При достижении счетчиком 1 состояния 8 на выходе четвертого (старшего) разряда начинается формирование импульса (фиг. Зж), который поступает на информационный вход формирователя 7. Следующий импульс переводит счетчик 1 в состояние 9 и начинает формирование отрицательного импульса на выходе формирователя 7 (фиг. За). Счетчик 1 переводится в режим установки, и следующий импульс по шине Такт установит счетчик 1 в состояние О (фиг. Зж), так как на информационных входах счетчика 1 присутствуют уровни логического О (фиг. Зд, е). Счетчик 1 перейдет в режим суммирования (фиг. Зз), и далее весь процесс повторится.

Допустим, что требуется обеспечить сдвиг выходных сигналов счетчика 1 влево. На шину 3 Сдвиг влево подают положительный импульс (фиг. 46). С приходом импульса, устанавливающего счетчика 1 в состояние 8, на выходах формирователя 2 и элемента ИЛИ 6 установится уровень логической 1 (фиг. 4г, е), а на информационных входах счетчика 1 - код цифры 1 (фиг. 4д). В результате в счетчик 1, когда он перейдет в режим установки, будет записан код цифры 1, а коэффициент пересчета счетчика 1 в этом цикле работы уменьшится на 1, выходные сигналы счетчика 1 сдвинутся влево на один такт входного сигнала. Для того, чтобы в следующем цикле коэффициент пересчета декадного счетчика восстановился (стал равным 10), длительность управляющего сигнала т на шине 3 Сдвиг влево (фиг. 46) должна удовлетворять условию

ЮТ n 29T,

где Т - период входного сигнала на шине Такт.

Если требуется осуществить свиг выходных сигналов счетчика 1 вправо, подают положительный импульс на шину Сдвиг вправо (фиг. 5в). С приходом импульса устанавливающего счетчика 1 в состояние 8 (фиг. 5ж) на выходах формирователя 4 (фиг.

5д) и соответственно элемента ИЛИ 6 (фиг. 5е) устанавливается уровень логической Г, а на информационных входах счетчика 1 код числа 15. Этот код будет записан в счетчик, когда тот будет находиться в режиме

установки. В результате коэффициент пересчета счетчика в этом цикле работы увеличится на 1,и выходные сигналы счетчика сдвинутся на один такт входного сигнала вправо. Коэффициент пересчета счетчика

восстановится в следующем цикле работы, если длительность управляющего сигнала Г2 на шине Сдвиг вправо будет удовлетворять условию

ЮТ .

Формула изобретения

30

Декадное счетное устройство, содержащее двоичный счетчик, выходы разрядов которого являются выходами устройства, и

формирователь импульсов, вход и инверсный выход которого подключены соответственно к выходу четвертого (старшего) разряда и к входу управления счетчика, а

тактовый вход подключен к тактовому входу счетчика и шине Такт устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения реверсивного сдвига информации, в него введены элемент ИЛИ, выход которого соединен с информационным входом первого разряда счетчика, первый и второй дополнительные формирователи импульсов, тактовые входы которых подключены к выходу четвертого разряда счетчика, информационные входы подключены соответственно к шинам Сдвиг влево и Сдвиг вправо устройства, выход первого дополнительного формирователя подсоединен к

первому входу элемента ИЛИ, выход второго дополнительного формирователя - к второму входу элемента ИЛИ и к информационным входам второго.третьего и четвертого разрядов двоичного счетчика, а каждый

формирователь импульсов содержит первый и второй р-триггеры, тактовые входы которых соединены и являются тактовым входом формирователя, D-вход, прямой и инверсный выходы первого D-триггера являются соответственно входом, выходом и инверсным выходами формирователя, D- вход и прямой выход второго D-триггера

СдВи 1

соединены соответственно с выходом формирователя и R-входом первого D-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты периодических сигналов | 1984 |

|

SU1231595A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Цифровые вторичные часы | 1988 |

|

SU1511733A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Устройство для измерения скорости изменения частоты | 1989 |

|

SU1620952A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Процессор быстрого преобразования уолша-адамара | 1989 |

|

SU1795471A1 |

| Генератор нелинейных двоичных последовательностей максимальной длины | 1986 |

|

SU1322245A1 |

| Устройство для измерения длительности импульсных сигналов | 1986 |

|

SU1383210A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

Изобретение относится к импульсной технике и может быть использовано в синтезаторах интервалов времени, компарэтарах-приемникахс коррекцией шкалы времени, в системах хранения частоты и времени Цель изобретения - расширение функциональных возможностей за счет обеспечения реверсивного сдвига информации Декадное счетное устройство содержит четырехразрядный двоичный счетчик 1, выходы которого являются выходами устройства, первый формирователь 2 импульсов, информационный вход которого подключен к шине Сдвиг влево 3, первый дополнитель формирователь 4 импульсов, информационный вход которого подключен к шине Сдвиг вправо 5, элемент ИЛИ 6, а также второй дополнительный формирователь 7 импульсов 5 ил

123 5618901234567890123 567896 а I 1 1 I I I I I I I I M I I I I I I I M I I I I I I I I

6,в,,д,е

т

-Р

-1QT-ЮТ LJ

Фиг.З

123156 891234-56789012Э4$6 890

I II M II I I I I I I II M I II || I I I I I I

J

1

8,6 0

ж

3

9TLJ

1Z3t56789KOlZ3b56789Q1Z3456789Q a i I I I I I II I I I I I I I II II I II I I I I t II I

1

WT

LJ

Фиг. 4

Фиг. 5

| Куртинин Н.В | |||

| Мяльно-трепальный станок для обработки тресты лубовых растений | 1922 |

|

SU200A1 |

| ПРИСПОСОБЛЕНИЕ ДЛЯ ПРИДАНИЯ ЖЕСТКОСТИ ПАРНОЙ ИЛИ ОРДИНАРНОЙ АВТОМАТИЧЕСКОЙ СЦЕПКЕ ДЛЯ ЖЕЛЕЗНОДОРОЖНЫХ ВАГОНОВ | 1925 |

|

SU5604A1 |

| ЭР, 1983, вып | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Колесов С.А., Соколов Ю.В | |||

| Высокочастотный цифровой делитель частоты - Вопросы радиоэлектроники, сер | |||

| ЭВТ, 1984, вып | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-05-07—Публикация

1989-03-06—Подача