Изобретение относится к вычислительной технике и может быть использовано для самопроверки микропроцессоров в процессе выполнения ос- .новных функций, а также для тестово проверки микропроцессорной системы.

цель изобретения - расширение функциональных возможностей за счет проверки выполнения последовательности команд в режиме обработки прерывания,

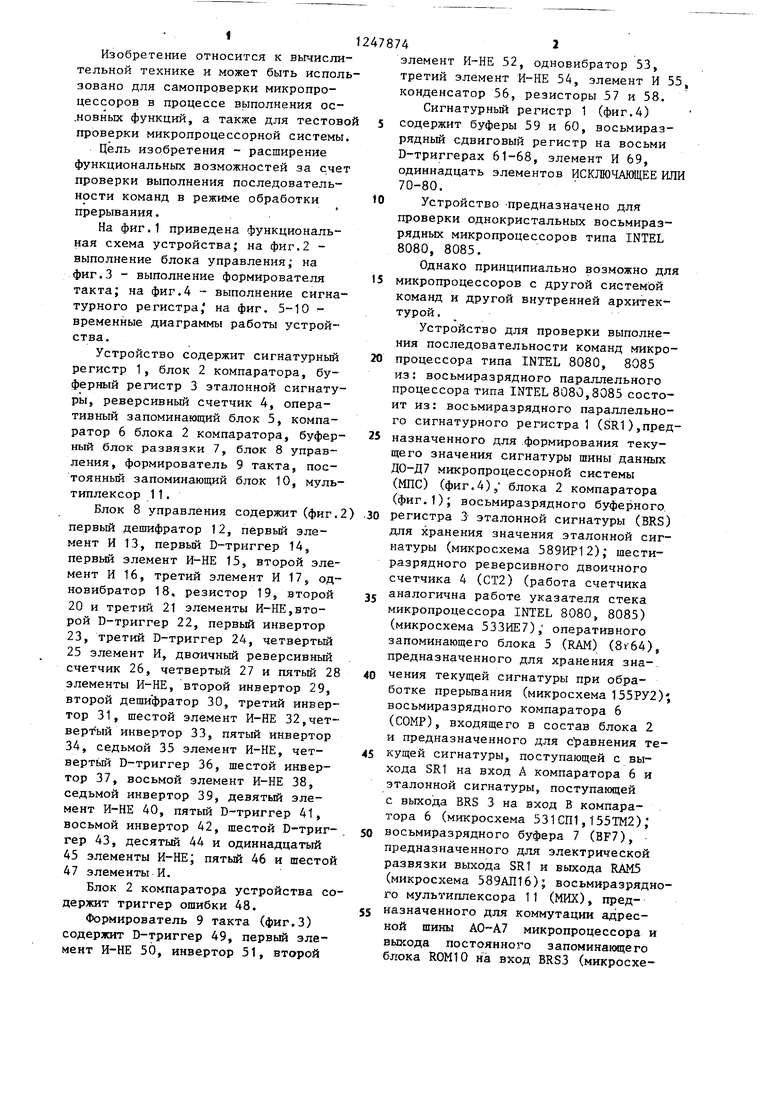

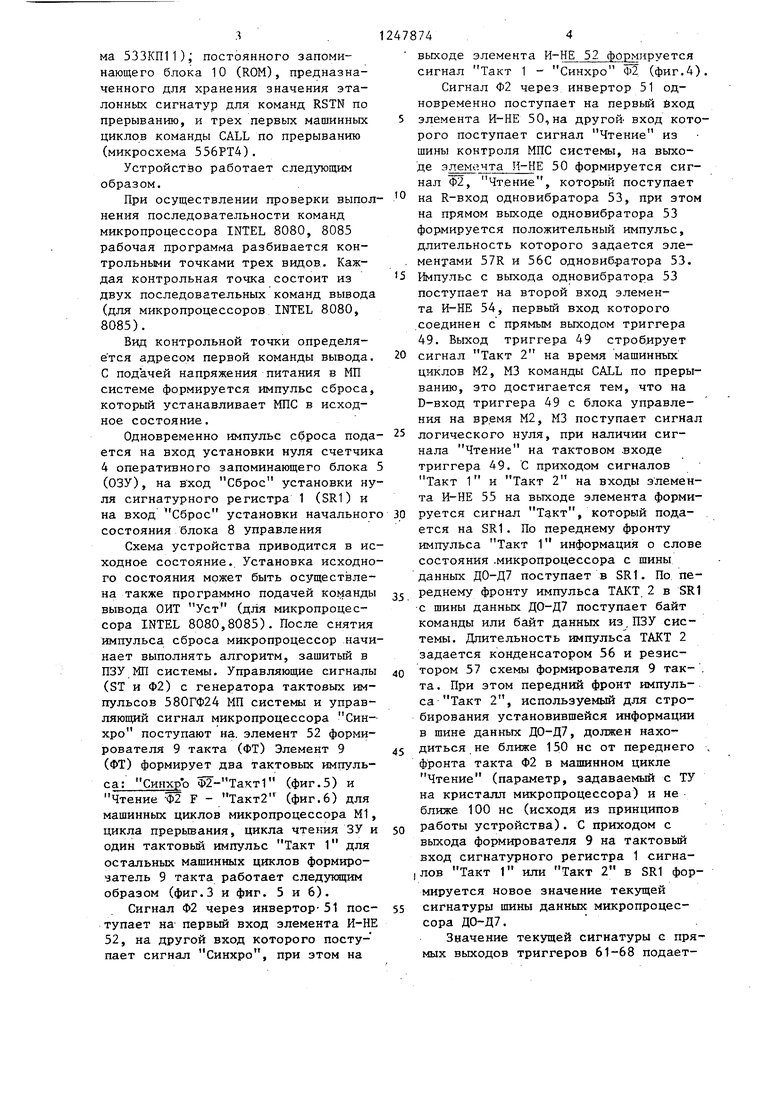

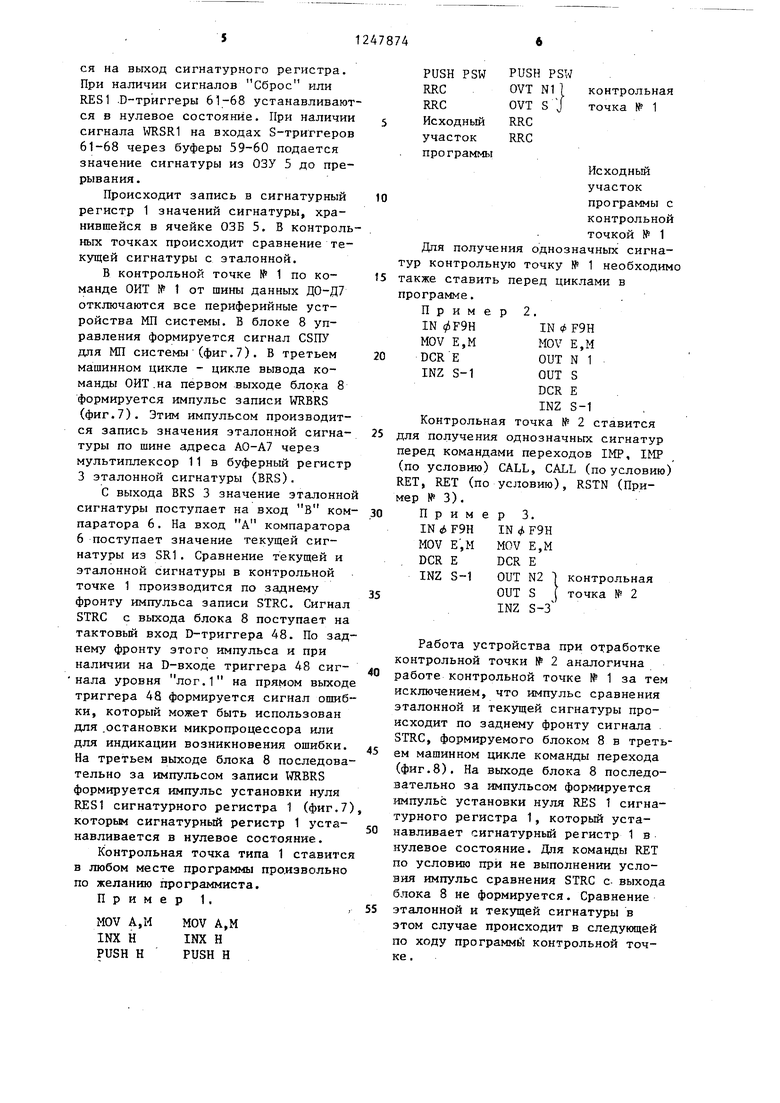

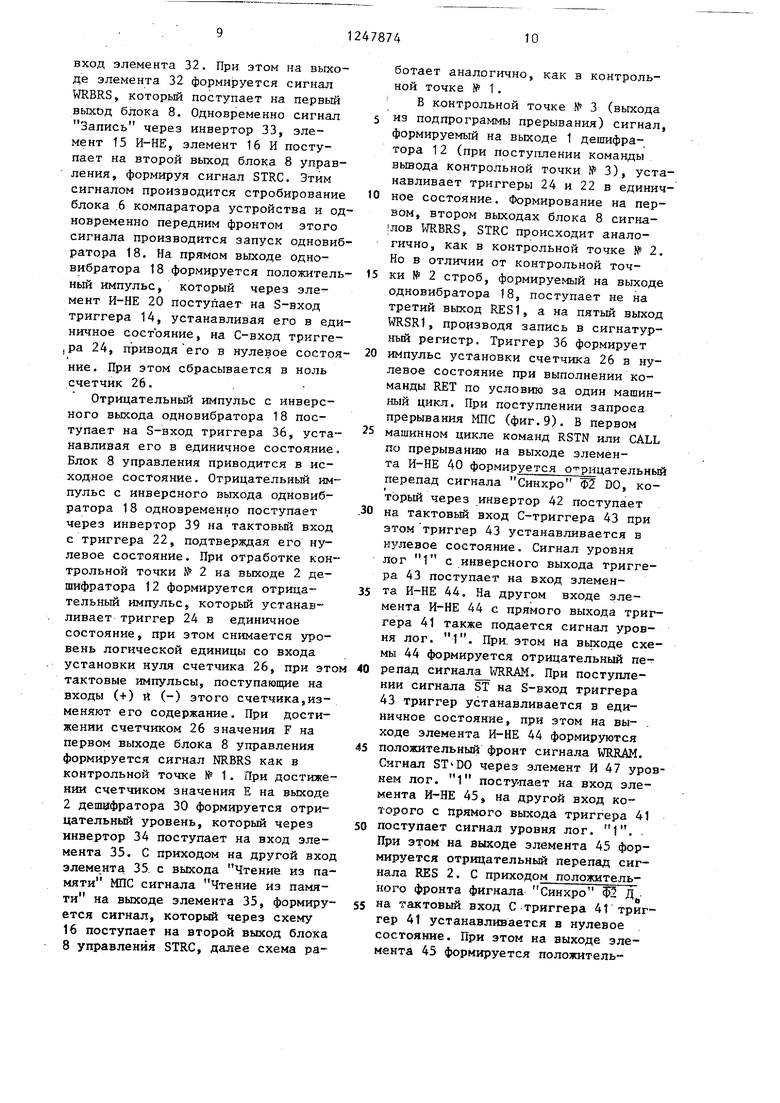

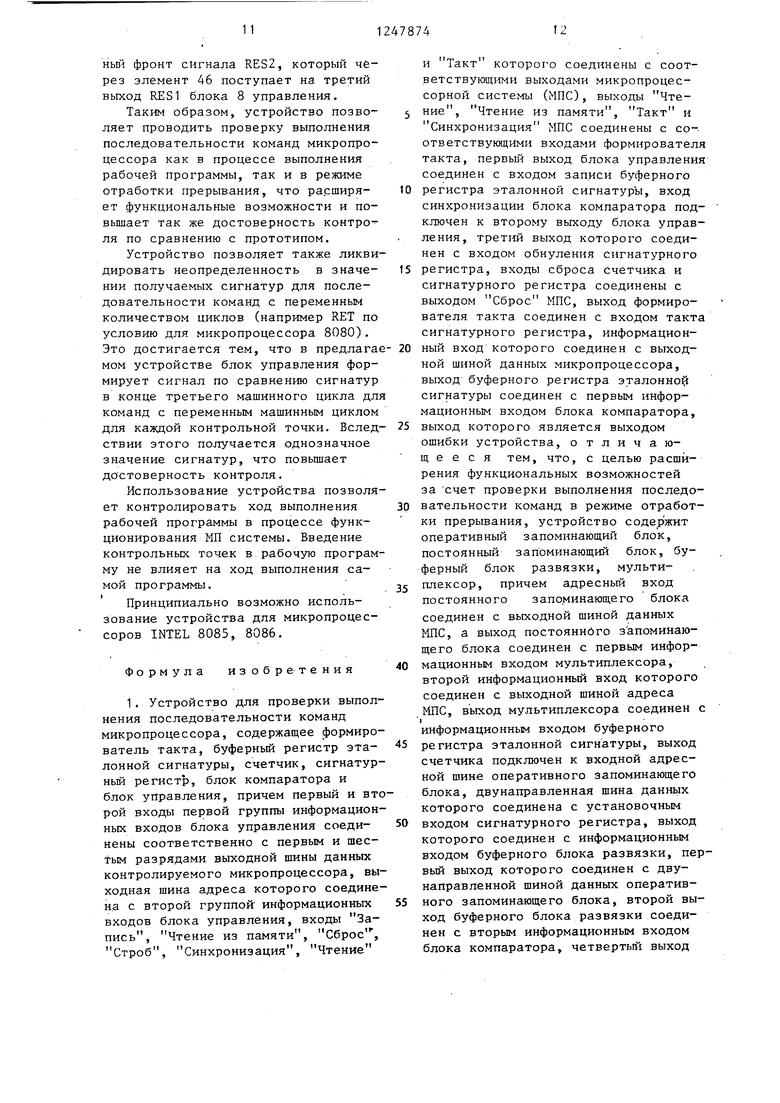

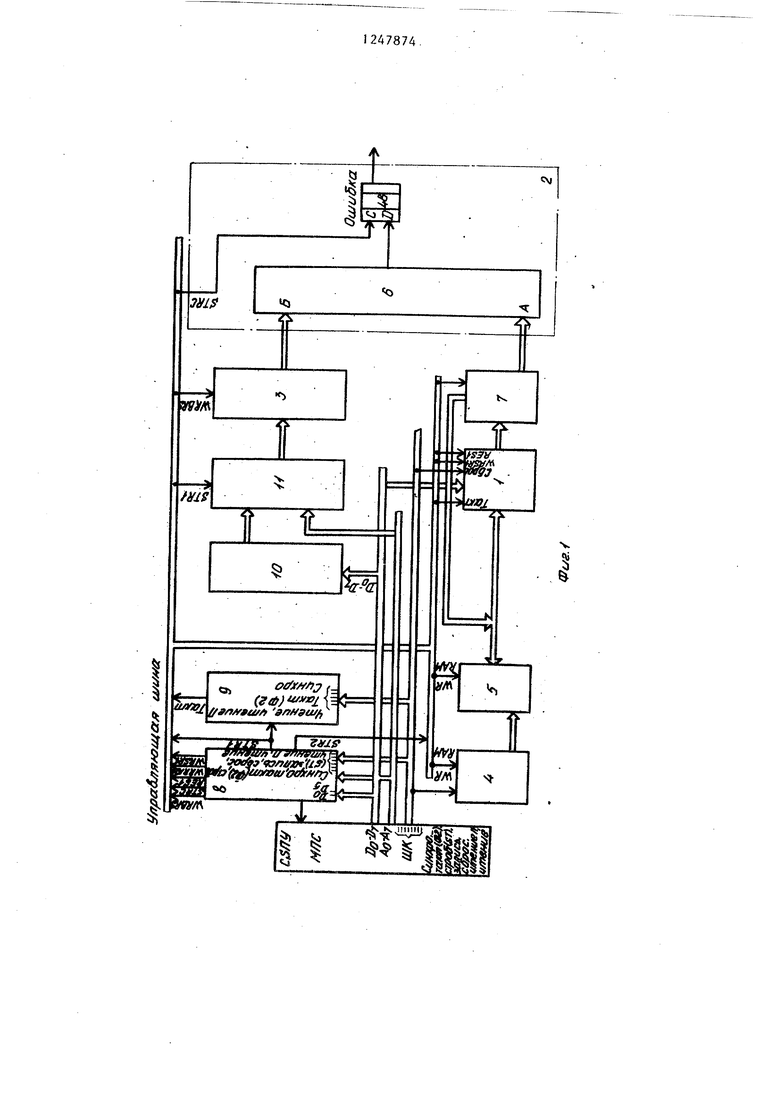

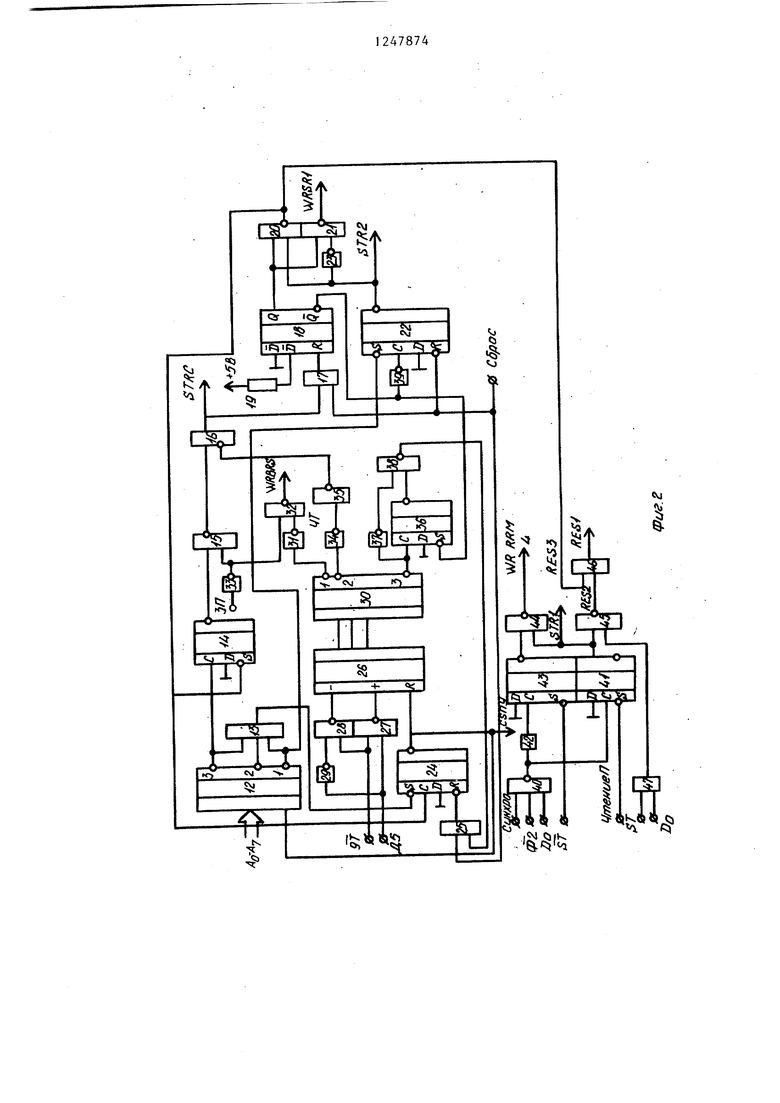

На фиг.1 приведена функциональная схема устройства; на фиг.2 - выполнение блока управленияj на фиг.З - выполнение формирователя такта; на фиг.4 - выполнение сигнатурного регистра, на фиг. 5-10 - временные диаграммы работы устройства .

Устройство содержит сигнатурный регистр 1, блок 2 компаратора, буферный регистр 3 эталонной сигнатуры, реверсивный счетчик 4, оперативный запоминающий блок 5, компаратор 6 блока 2 компаратора, буферный блок развязки 7, блок 8 управления, формирователь 9 такта, постоянный запоминающий блок 10, мультиплексор 11.

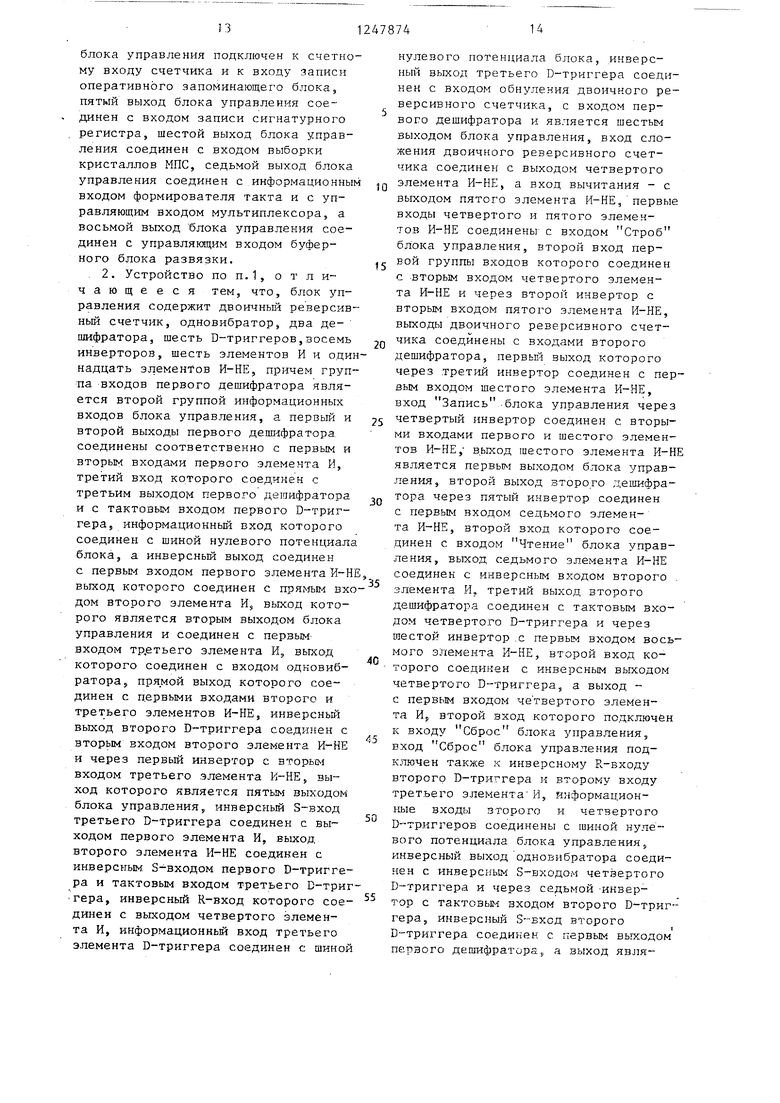

Блок 8 управления содержит (фиг. первый дешифратор 12, первый элемент И 13, первый D-трнггер 14, первый элемент И-НЕ 15, второй элемент И 16, третий элемент И 17, од новибратор 18. резистор 19, второй 20 и третий 21 элементы И-НЕ,второй D-триггер 22, первый инвертор 23, третий D-триггер 24, четвертый 25 элемент И, двоичный реверсивный счетчик 26, четвертый 27 и пятый 28 элементы И-НЕ, второй инвертор 29, второй деши фратор 30, третий инвертор 31, шестой элемент И-НЕ 32,четвертый инвертор 33, пятый инвертор 34, седьмой 35 элемент И-НЕ, четвертый D-триггер 36, шестой инвертор 37, восьмой элемент И-НЕ 38, седьмой инвертор 39, девятый элемент И-НЕ 40, пятый D-триггер 41, восьмой инвертор 42, шестой D-триггер 43, десятый 44 и одиннадцатый 45 элементы И-НЕ; пятый 46 и шестой 47 элементы И.

Блок 2 компаратора устройства содержит триггер ошибки 48.

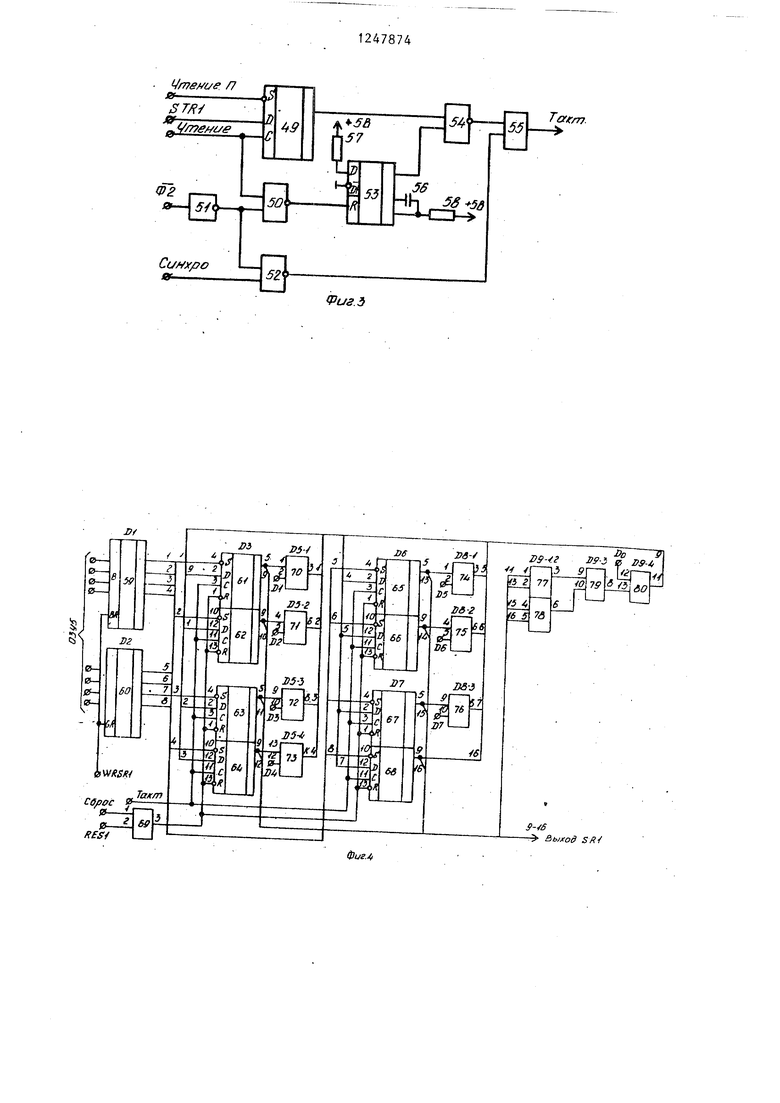

Формирователь 9 такта (фиг.З) содержит D-триггер 49, первый элемент И-НЕ 50, инвертор 51, второй

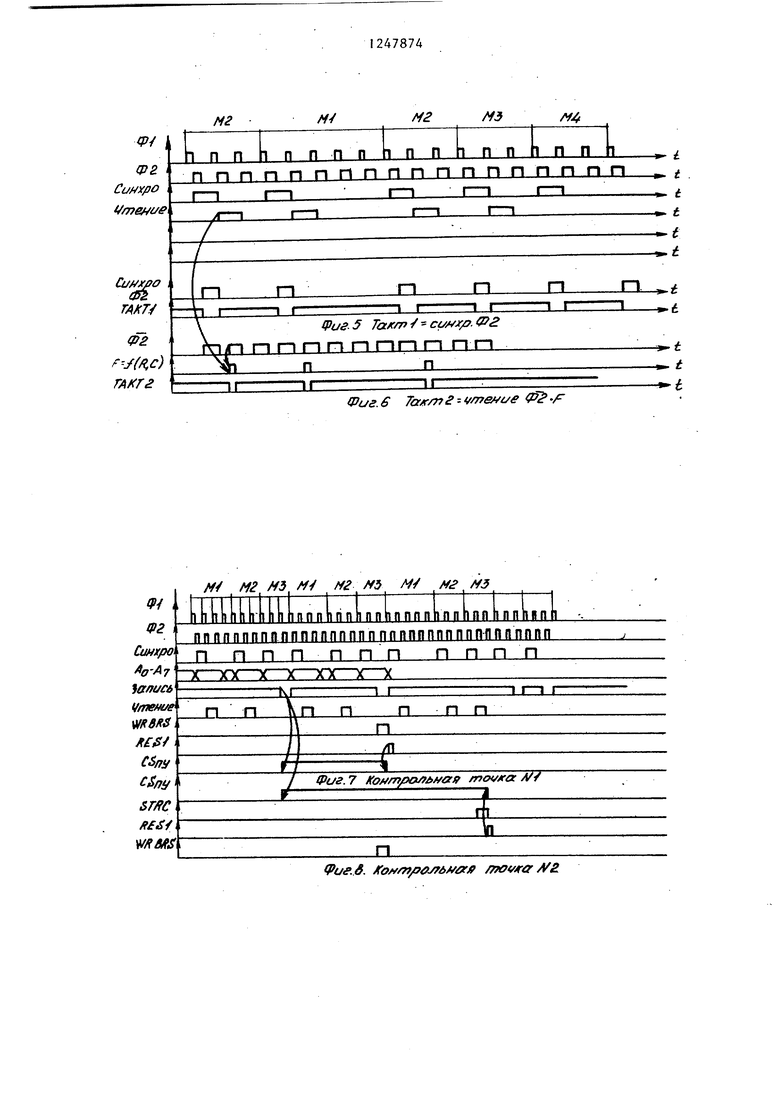

элемент И-НЕ 52, одновибратор 53, третий элемент И-НЕ 54, элемент И 55, конденсатор 56, резисторы 57 и 58. Сигнатурный регистр 1 (фиг.4)

5 содержит буферы 59 и 60, восьмираз- рядньй сдвиговый регистр на восьми D-триггерах 61-68, элемент И 69, одиннадцать элементов ИСКЛОЧАЩЕЕ ИЛИ 70-80.

0 Устройство Предназначено для

проверки однокристальных восьмиразрядных микропроцессоров типа INTEL 8080, 8085.

Однако принципиально возможно для

5 микропроцессоров с другой системой команд и другой внутренней архитектурой .

Устройство для проверки выполнения последовательности команд микро0 процессора типа INTEL 8080, 8085 из: восьмиразрядного параллельного процессора типа INTEL 8080,8085 состоит из: восьмиразрядного параллельного сигнатурного регистра 1 (8К1),пред5 назначенного для .формирования текущего значения сигнатуры шины данных ДО-Д7 микропроцессорной системы (МПС) (фиг.4),, блока 2 компаратора (фиг.1); восьмиразрядного буферного.

0 регистра 3 эталонной сигнатуры (BRS) для хранения значения эталонной сигнатуры (микросхема 589ИР12); шестиразрядного реверсивного двоичного счетчика 4 (СТ2) (работа счетчика

J аналогична работе указателя стека микропроцессора INTEL 8080, 8085) (микросхема 533ИЕ7), оперативного запоминающего блока 5 (RAM) (8v64), предназначенного для хранения зна-.

0 чения текущей сигнатуры при обработке прерьшания (микросхема 155РУ2) ; восьмиразрядного компаратора 6 (СОМР), входящего в состав блока 2 и предназначенного для сравнения теS кущей сигнатуры, поступающей с выхода SR1 на вход А компаратора 6 и эталонной сигнатуры, поступающей с выхода BRS 3 на вход В компаратора 6 (микросхема 531СП1,155ТМ2);

0 восьмиразрядного буфера 7 (BF7), предназначенно.го для электрической развязки выхода SR1 и выхода RAM5 (микросхема 589АЛ16); восьмиразрядного мультиплексора 11 (МИХ), пред5 назначенного для коммутации адресной шины АО-А7 микропроцессора и выхода постоянного запоминающего блока ROM10 на вход BRS3 (микросхема 533Kni1)j постоянного запоминающего блока 10 (ROM), предназначенного для хранения значения эталонных сигнатур для команд RSTN по прерыванию, и трех первых машинных циклов команды CALL по прерыванию (микросхема 556РТ4).

Устройство работает следующим образом.

При осуществлении проверки выполнения последовательности команд микропроцессора INTEL 8080, 8085 рабочая программа разбивается контрольными точками трех видов. Каждая контрольная точка состоит из двух последовательных команд вывода (для микропроцессоров INTEL 8080, 8085).

Вид контрольной точки определяется адресом первой команды вывода. С подачей напряжения питания в МП системе формируется импульс сброса, который устанавливает МПС в исходное состояние.

Одновременно импульс сброса подается на вход установки нуля счетчик 4 оперативного запоминающего блока (ОЗУ) , на в ход Сброс установки нуля сигнатурного регистра 1 (SR1) и на вход Сброс установки начальног состояния блока 8 управления

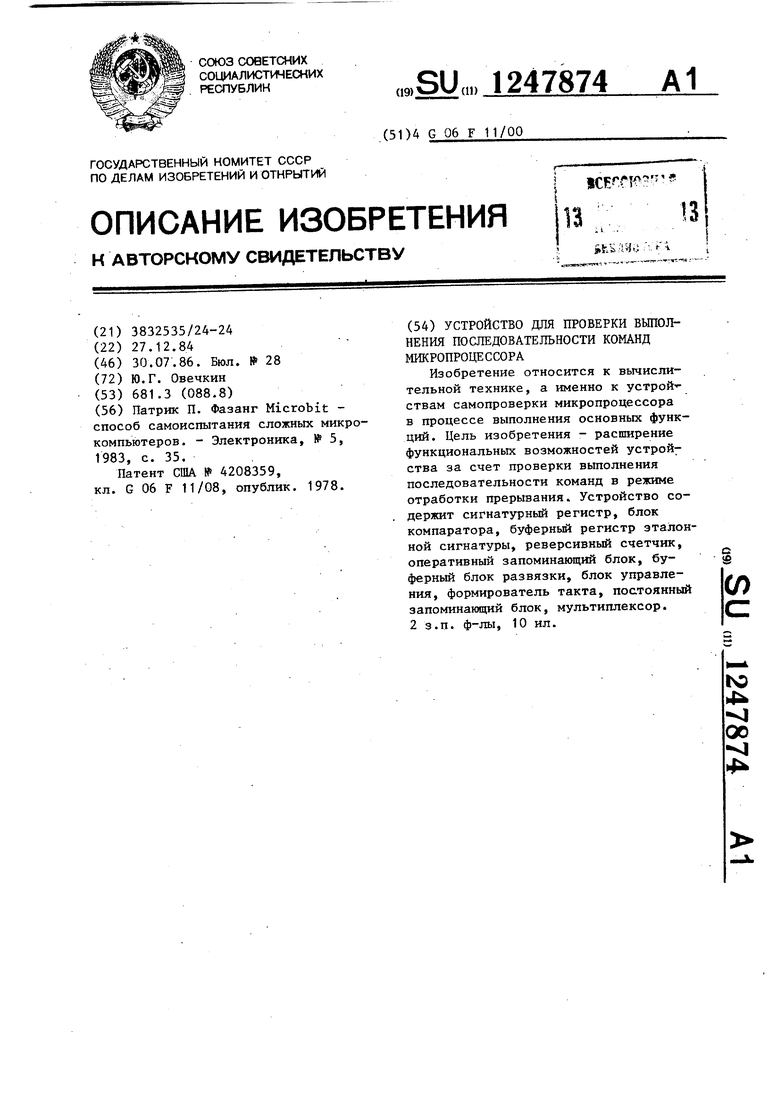

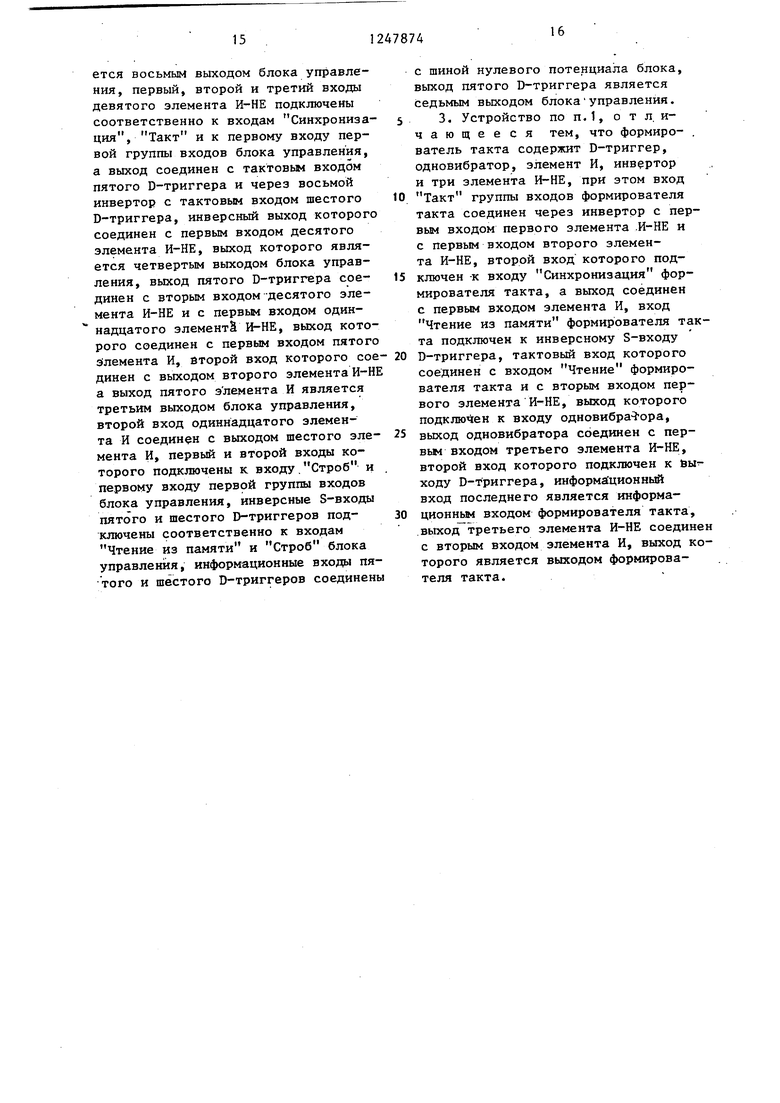

Схема устройства приводится в исходное состояние. Установка исходного состояния может быть осуществлена также программно подачей команды вывода СИТ УСТ (для микропроцессора INTEL 8080,8085). После снятия импульса, сброса микропроцессор начинает выполнять алгоритм, зашитый в ПЗУ МП системы. Управляющие сигналы (ST и Ф2) с генератора тактовых импульсов 580ГФ24 МП системы и управляющий сигнал микропроцессора Син- хро поступают на. элемент 52 формирователя 9 такта (ФТ) Элемент 9 (ФТ) формирует два тактовых импульса: СИН2ФО Ф2- ТактГ (фиг.5) и Чтение Ф2 F - Такт2 (фиг.6) для машинных циклов микропроцессора М1, цикла прерьшания, цикла чтения ЗУ и один тактовый импульс Такт 1 для остальных машинных циклов формирователь 9 такта работает следуклцим образом (фиг.З и фиг. 5 и 6).

Сигнал Ф2 через инвертор-51 поступает на первый вход элемента И-НЕ 52, на другой вход которого посту- пает сигнал Синхро, при этом на

0

5

0

5

0

5.

0

5

0

5

выходе элемента И-НЕ 52 формируется сигнал Такт 1 - Синхро Ф2 (фиг.4).

Сигнал Ф2 через инвертор 51 одновременно поступает на первый йход элемента И-НЕ 50,на другой вход которого поступает сигнал Чтение из шины контроля МПС системы, на выходе элемента И-НЕ 50 формируется сигнал Ф2, Чтение, который поступает на R-вход одновибратора 53, при этом на прямом выходе одновибратора 53 формируется положительный импульс, длительность которого задается элементами 57R и 56С одновиб-ратора 53. импульс с выхода одновибратора 53 поступает на второй вход элемента И-НЕ 54, первый вход которого соединен с прямым выходом триггера 49. Выход триггера 49 строб.ирует сигнал Такт 2 на время машинных циклов М2, МЗ команды CALL по прерыванию, это достигается тем, что на D-вход триггера 49 с блока управления на время М2, МЗ поступает сигнал логического нуля, при наличии сигнала Чтение на тактовом .входе триггера 49. С приходом сигналов Такт Г и Такт 2 на входы элемента И-НЕ 55 на выходе элемента формируется сигнал Такт, который подается на SR1. По переднему фронту импульса Такт 1 информация о слове состояния .микропроцессора с шины данных ДО-Д7 поступает в SR1. По переднему фронту импульса ТАКТ 2 в SR1 с шины данных ДО-Д7 поступает байт команды или байт данных из,ПЗУ системы. Длительность импульса ТАКТ 2 задается конденсатором 56 и резистором 57 схемы формирователя 9 так- . та. При этом передний фронт импуль-. са Такт 2, используемый для стро- бирования установившейся информации в шине данных ДО-Д7, должен находиться не ближе 150 НС от переднего , фронта такта Ф2 в мапшнном цикле Чтение (параметр, задаваемый с ТУ на кристалл микропроцессора) и не ближе 100 НС (исходя из принципов работы устройства). С приходом с выхода формирователя 9 на тактовый вход сигнатурного регистра 1 сигналов Такт 1 или Такт 2 в SR1 формируется новое значение текущей сигнатуры шины данных микропроцессора ДО-Д7.

Значение текущей сигнатуры с прямых выходов триггеров 61-68 подается на выход сигнатурного регистра. При наличии сигналов Сброс или RES1 .D-триггеры 61-68 устанавливаются в нулевое состояние. При наличии сигнала WRSR1 на входах S-триггеров 61-68 через буферы 59-60 подается значение сигнатуры из ОЗУ 5 до прерывания .

Происходит запись в сигнатурный регистр 1 значений сигнатуры, хранившейся в ячейке ОЗБ 5. В контрольных точках происходит сравнение текущей сигнатуры с эталонной.

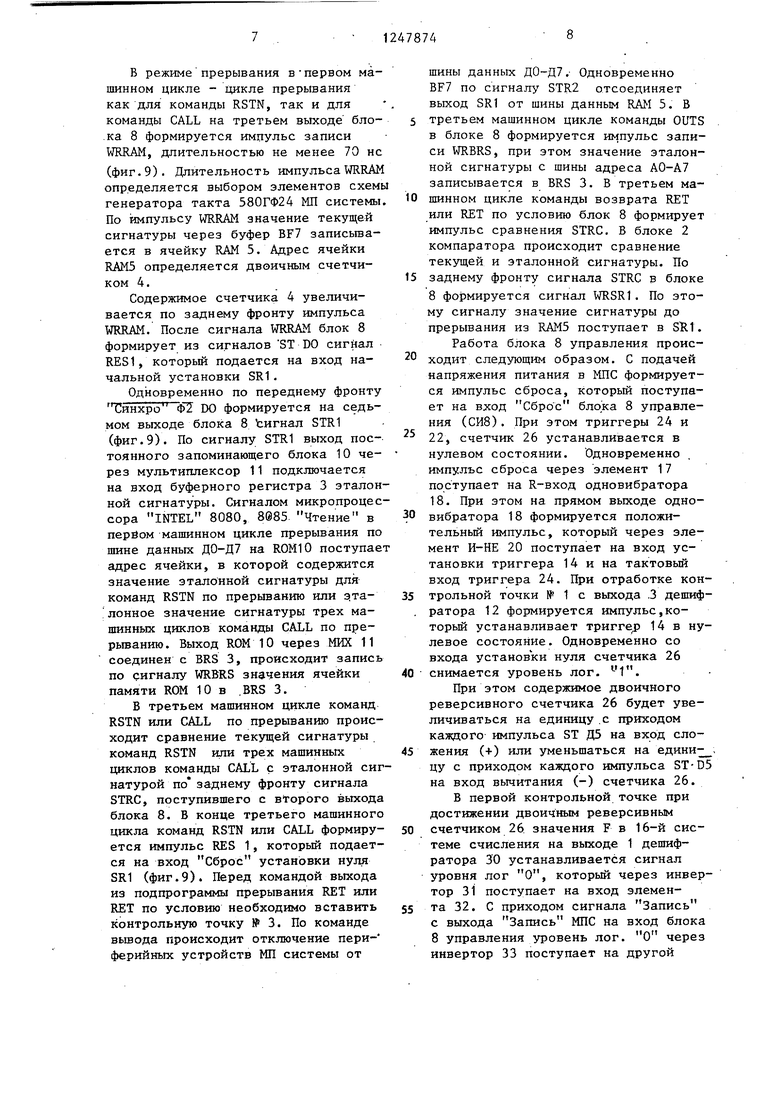

В контрольной точке № 1 по ко- манде ОИТ № 1 от шины данных ДО-Д7 отключаются все периферийные устройства МП системы. В блоке 8 управления формируется сигнал СЗПУ для МП системы (фиг.7). В третьем машинном цикле - цикле вывода команды ОИТ .на первом выходе блока 8 формируется импульс записи WRBRS (фиг.7). Этим импульсом производится запись значения эталонной сигна- туры по шине адреса АО-А7 через мультиплексор 11 в буферный регистр 3 эталонной сигнатуры (BRS).

С выхода BRS 3 значение эталонной сигнатуры поступает на вход В ком- паратора 6. На вход А компаратора 6 поступает значение текущей сигнатуры из SR1. Сравнение текущей и эталонной сигнатуры в контрольной точке t производится по заднему фронту импульса записи STRC. Сигнал STRC с выхода блока 8 поступает на тактовый вход D-триггера 48. По заднему фронту этого импульса и при наличии на D-входе триггера 48 сиг- нала уровня лог.1 на прямом выходе триггера 48 формируется сигнал ошибки, который может быть использован для .остановки микропроцессора или для индикации возникновения ошибки. На третьем выходе блока 8 последовательно за импульсом записи TOBRS формируется импульс установки нуля RES1 сигнатурного регистра 1 (фиг.7) которым сигнатурный регистр 1 уста- навливается в нулевое состояние.

Контрольная точка типа 1 ставится в любом месте программы произвольно по желанию программиста.

Пример 1 ,

MOV А,М MOV А,М INX Н INX Н PUSH Н PUSH Н

j

S 0 5

о , Q

5

PUSH PSW PUSH PSW

RRC OVT N11 контрольная

RRC OVT S J точка № 1

Исходный RRC

участок RRC

программы

Исходньм участок программы с контрольной точкой № 1

Для получения однозначных сигнатур контрольную точку № 1 необходимо также ставить перед циклами в программе.

П р и м е р 2 , IN ф79Е IN MOV Е,М MOV Е,М DCR Е OUT N 1 INZ S-1 OUT S DCR E INZ S-1

Контрольная точка № 2 ставится для получения однозначных сигнатур перед командами переходов IMP, IMP (по условию) CALL, CALL (по условию) RET, RET (по условию), RSTN (Пример № 3).

Пример 3. IN « F9H IN 4 F9H MOV Е,М MOV Е,М DCR Е DCR Е INZ S-1 OUT N2 I контрольная OUT S j точка № 2 INZ S-3

Работа устройства при отработке контрольной точки № 2 аналогична работе контрольной точке № 1 за тем исключением, что импульс сравнения эталонной и текущей сигнатуры происходит по заднему фронту сигнала . STRC, формируемого блоком 8 в третьем машинном цикле команды перехода (фиг.8). На выходе блока 8 последовательно за импульсом формируется импульс установки нуля RES 1 сигнатурного регистра 1, который устанавливает сигнатурньй регистр 1 в нулевое состояние. Для команды RET по условию при не выполнении условия импульс сравнения STRC с. выхода блока 8 не формируется. Сравнение эталонной и текущей сигнатуры в этом случае происходит в следующей по ходу программй контрольной точке ,

В режиме прерывания в первом машинном цикле - цикле прерывания как для команды RSTN, так и для команды CALL на третьем выходе бло- .ка 8 формируется импульс записи WRRAM, длительностью не менее 70 не (фиг.9). Длительность импульса WRRAM определяется выбором элементов схем генератора такта 580ГФ24 МП системы По импульсу WRRAM значение текущей сигнатуры через буфер BF7 записьгаа- ется в ячейку RAM 5. Адрес ячейки RAM5 определяется двоичным счетчиком 4.

Содержимое счетчика 4 увеличивается по заднему фронту импульса WRRAM. После сигнала WRRAM блок 8 формирует из сигналов ST DO сигнал RES1, которьш подается на вход начальной установки SR1.

Одновременно по переднему фронту Т 1инхро Ф DO формируется на седьмом выходе блока 8 Ьигнал STR1 (фиг.9). По сигналу STR1 выход постоянного запоминающего блока 10 через мультиплексор 11 подключается на вход буферного регистра 3 эталонной сигнатуры. Сигналом микропроцессора INTEL 8080, 8685. Чтение в первом машинном цикле прерывания по шине данных ДО-Д7 на ROM10 поступае адрес ячейки, в которой содержится значение эталонной сигнатуры для команд RSTN по прерыванию или э.та- лонное значение сигнатуры трех машинных циклов команды CALL по пре- рьшанию. Выход ROM 10 через МИХ 11 соединен с BRS 3, происходит запись по сигналу WRBRS значения ячейки памяти ROM 10 в .BRS 3.

В третьем машинном цикле команд RSTN или CALL по прерыванию происходит сравнение текущей сигнатуры команд RSTN или трех машинных циклов команды CALL с эталонной сигнатурой по заднему фронту сигнала STRC, поступившего с второго выхода блока 8. В конце третьего машинного цикла команд RSTN или CALL формируется импульс RES 1, который подается на вход Сброс установки нуля SR1 (фиг.9). Перед командой выхода из подпрограммы прерывания RET или RET по условию необходимо вставить контрольную точку № 3. По команде вьшода происходит отключение пери- ферийных устройств МП системы от

шины данных ДО-Д7.- Одновременно BF7 по сигналу STR2 отсоединяет выход SR1 от шины данным RAM 5. В 5 третьем машинном цикле команды OUTS в блоке 8 формируется импульс записи WRBRS, при этом значение эталонной сигнатуры с шины адреса АО-А7 записывается в BRS 3. В третьем ма- 10 шинном цикле команды возврата RET или RET по условию блок 8 формирует импульс сравнения STRC, Б блоке 2 компаратора происходит сравнение текущей и эталонной сигнатуры. По 15 заднему фронту сигнала STRC в блоке 8 формируется сигнал WRSR1. По этому сигналу значение сигнатуры до прерывания из RAM5 поступает в SR1. Работа блока 8 управления проис- 20 ходит следующим образом. С подачей напряжения питания в МПС формируется импульс сброса, который поступает на вход Сброс 8 управления (СИ8). При этом триггеры 24 и

22, счетчик 26 устанавливается в нулевом состоянии. Одновременно импульс сброса через элемент 17 поступает на R-вход одновибратора 18. При этом на прямом выходе одно0 вибратора 18 формируется положительный импульс, который через элемент И-НЕ 20 поступает на вход установки триггера 14 и на тактовый вход триггера 24. При отработке кон5 трольной точки № 1 с выхода .3 дешиф- . ратора 12 формируется импульс,который устанавливает триггер 14 в нулевое состояние. Одновременно со входа установки нуля счетчика 26

0 снимается уровень лог. I.

При этом содержимое двоичного реверсивного счетчика 26 будет увеличиваться на единицу .с приходом каждого импульса ST Д5 на вход сло5 жения (+) или уменьшаться на едини-. цу с приходом каждого импульса ST-D5 на вход вычитания (-) счетчика 26. В первой контрольной точке при достижении двоичным реверсивным

счетчиком 26 значения F в 16-й системе счисления на выходе 1 дешифратора 30 устанавливается сигнал уровня лог О, который через инвертор 31 поступает на вход элемента 32. С приходом сигнала Запись с выхода Запись МПС на вход блока 8 управления уровень лог. О через инвертор 33 поступает на другой

вход элемента 32. При этом на выходе элемента 32 формируется сигнал WRBRS, который поступает на первьй выход блока 8. Одновременно сигнал Запись через инвертор 33, элемент 15 И-НЕ, элемент 16 И поступает на второй выход блока 8 управления, формируя сигнал STRC. Этим сигналом производится стробирование блока .6 компаратора устройства и одновременно передним фронтом этого сигнала производится запуск одновиб ратора 18. На прямом выходе одно- вибратора 18 формируется положительный импульс, который через элемент И-НЕ 20 поступает на S-вход триггера 14, устанавливая его в единичное состояние, на С-вход тригге- |ра 24, приводя его в нулевое состояние. При этом сбрасывается в ноль счетчик 26.

Отрицательный импульс с инверсного выхода одновибратора 18 поступает на S-вход триггера 36, устанавливая его в единичное состояние. Блок 8 управления приводится в исходное состояние. Отрицательньй импульс с инверсного выхода одновибратора 1 8 одновремен1 о поступает через инвертор 39 на тактовый вход с триггера 22, подтверждая его нулевое состояние. При отработке контрольной точки № 2 на выходе 2 дешифратора 12 формируется отрица- тельньй импульс, который устанав ливает триггер 24 в единичное состояние, при этом снимается уровень логической единицы со входа установки нуля счетчика 26, при это тактовые импульсы, поступающие на входы (+) и (-) этого счетчика,изменяют его содержание. При достижении счетчиком 26 значения F на первом выходе блока 8 управления формируется сигнал MBRS как в контрольной точке № 1. При достижении счетчиком значения Е на выходе 2 депцдфратора 30 формируется отрицательный уровень, который через инвертор 34 поступает на вход элемента 35. С приходом на другой вход элемента 35 с выхода Чтение из памяти МПС сигнала Чтение из памяти на выходе элемента 35, формируется сигнал, который через схему 16 поступает на второй выход блока 8 управления STRC, далее схема работает аналогично, как в контрольной точке № 1. В контрольной точке № 3 (выхода

из подпрограммы прерывания) сигнал, формируемый на выходе 1 дешифратора 12 (при поступлении команды вывода контрольной точки № 3), устанавливает триггеры 24 и 22 в единичное состояние. Формирование на первом, втором выходах блока 8 сигна- лов WRBRS, STRC происходит аналогично, как в контрольной точке № 2. Но в отличии от контрольной точки № 2 строб, формируемый на выходе одновибратора 18, поступает не на третий выход RES1, а на пятый выход WRSR1, про 1зводя запись в сигнатурный регистр. Триггер 36 формирует

импульс установки счетчика 26 в нулевое состояние при выполнении команды RET по условию за один машинный цикл. При поступлении запроса прерывания МПС (фиг.9). В первом

машинном цикле команд RSTN или CALL по прерыванию на выходе элемента И-НЕ 40 формируется отрицательный перепад сигнала Синхро Ф2 DO, который через инвертор 42 поступает на тактовый вход С-триггера 43 при этом триггер 43 устанавливается в нулевое состояние. Сигнал уровня лог 1 с инверсного выхода триггера 43 поступает на вход элемента И-НЕ 44, На другом входе элемента И-НЕ 44 с прямого выхода триггера 41 также подается сигнал уровня лог. 1. При. этом на выходе схемы 44 формируется отрицательный перепад сигнала ШКАМ. При поступлении сигнала ST на S-вход триггера 43 триггер устанавливается в единичное состояние, при этом на вы- . ходе элемента И-НЕ 44 формируются

положительный фронт сигнала WRRAM. Сигнал ST DO через элемент И 47 уровнем лог. 1 поступает на вход элемента И-НЕ 45, на другой вход которого с прямого выхода триггера 41

поступает сигнал уровня лог. t. При этом на выходе элемента 45 формируется отрицательный перепад сигнала RES 2. С приходом положитель- ного фронта фигнала Синхро 52 Д

на Гактовый вход С триггера 41 триггер 41 устанавливается в нулевое состояние. При этом на выходе элемента 45 формируется положитель™

Hbu i фронт сигнала RES2, который через элемент 46 лоступает на третий выход RES1 блока 8 управления.

Таким образом, устройство лозво- ляет лроводить проверку выполнения последовательности команд микропроцессора как в процессе выполнения рабочей программы, так и в режиме отработки прерывания, что расширяет функциональные возможности и повышает так же достоверность контроля по сравнению с прототипом.

Устройство позволяет также ликвидировать неопределенность в значении получаемых сигнатур для последовательности команд с переменным количеством циклов (например RET по условию для микропроцессора 8080), Это достигается тем, что в предлагамом устройстве блок управления формирует сигнал по сравнению сигнатур в конце третьего машинного цикла дл команд с переменным машинным циклом для каждой контрольной точки. Вслед ствии этого получается однозначное значение сигнатур, что повышает достоверность контроля.

Использование устройства позволяет контролировать ход выполнения рабочей программы в процессе функционирования МП системы. Введение контрольных точек в рабочую программу не влияет на ход выполнения самой программы.

Принципиально возможно использование устройства для микропроцессоров INTEL 8085, 8086,

Формула изобретения

1 . Устройство для проверки выполнения последовательности команд микропроцессора, содержащее формирователь такта, буферный регистр эталонной сигнатуры, счетчик, сигнатурный регистр, блок компаратора и блок управления, причем первый и втрой входы первой группы информационных входов блока управления соединены соответственно с первым и шестым разрядами выходной шины данных контролируемого микропроцессора, выходная шина адреса которого соединена с второй группой информационных входов блока управления, входы Запись, Чтение из памяти, Сброс, Строб, Синхронизация, Чтение

и Такт которого соединены с соответствующими выходами микропроцессорной системы (МПС), выходы Чте- 5 ние, Чтение из памяти, Такт и Синхронизация МПС соединены с со-. ответствующими входами формирователя такта, первый выход блока управления соединен с входом записи буферного 10 регистра эталонной сигнатуры, вход синхронизации блока компаратора подключен к второму выходу блока управления, третий выход которого соединен с входом обнуления сигнатурного 15 регистра, входы сброса счетчика и сигнатурного регистра соединены с выходом Сброс МПС, выход формирователя такта соединен с входом такта сигнатурного регистра, информацион0 ный вход которого соединен с выходной шиной данных микропроцессора, выход буферного регистра эталонно сигнатуры соединен с первым информационным входом блока компаратора,

5 выход которого является выходом ошибки устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет проверки выполнения последо0 вательности команд в режиме отработки прерывания, устройство содержит оперативный запоминающий блок, постоянный запоминающий блок, буферный блок развязки, мульти5 плексор, причем адресный вход постоянного запоминающего блока соединен с выходной шиной данных МПС, а выход постояннбго з апоминаю- щего блока соединен с первым инфор0 мационным входом мультиплексора,

второй информационный вход которого соединен с выходной шиной адреса

МПС, выход мультиплексора соединен с i информационным входом буферного

5 регистра эталонной сигнатуры, выход счетчика подключен к входной адресной шине оперативного запоминающего блока, двунаправленная шина данных которого соединена с установочным

0 входом сигнатурного регистра, выход которого соединен с информационным входом буферного блока развязки, первый выход которого соединен с двунаправленной шиной данных оператив5 ного запоминающего блока, второй выход буферного блока развязки соединен с вторым информационным входом блока компаратора, четвертьй выход

блока управления подключен к счетному входу счетчика и к входу записи оперативного запоминающего блока, пятый выход блока управления соединен с входом записи сигнатурного регистра, шестой выход блока управления соединен с входом выборки кристаллов МПС, седьмой выход блока управления соединен с информационным входом формирователя такта и с управляющим входом мультиплексора, а восьмой выход блока управления соединен с управлягацим входом буферного блока развязки.

, 2. Устройство по п.1, отличающееся тем, что, блок управления содержит двоичньм реверсивный счетчик, одновибратор, два дешифратора, шесть D-триггеров,восемь инверторов, шесть элементов И и одиннадцать элементов И-НЕ, причем группа входов первого дешифратора является второй группой информационных входов блока управления, а первый и второй выходы первого дешифратора соединены соответственно с первым и вторым входами первого элемента И, третий вход которого соединен с третьим выходом первого дешифратора и с тактовым входом первого D-триг- гера, информационный вход которого соединен с шиной нулевого потенциала блока, а инверсный выход соединен с первым входом первого элемента И-Н вьпсод которого соединен с прямыг-i входом второго элемента И, выход которого является вторым выходом блока управления и соединен с перзыМ входом тр,етьего элемента И, выход которого соединен с входом одновиб- ратора, прямой выход которого соединен с первыми входами второго и третьего элементов И-НЕ, инверсньй выход второго D-триггера соединен с вторым входом второго элемента И-НЕ и через первый инвертор с вторым входом третьего элемента И-НЕ выход которого является пятым выходом блока управления5 инверсный S-вход третьего D-триггера соединен с выходом первого элемента И, выход второго элемента И-НЕ соединен с инверсным S-входом первого D-триггера и тактовым входом третьего D-триг гера, инверсный R-вход которого соединен с выходом четвертого элемента И, информациоиньй вход третьего элемента D-триггера соединен с шиной

нулевого потенциала блока, инверсный выход третьего D-триггера соединен с входом обнуления двоичного реверсивного счетчика, с входом первого дешифратора и является шестым выходом блока управления, вход сложения двоичного реверсивного счетчика соединен с выходом четвертого элемента И-НЕ, а вход вычитания - с выходом пятого элемента И-НЕ, первые входы четвертого и пятого элементов И-НЕ соединены с входом Строб блока управления, второй вход первой группы входов которого соединен с вторым входом четвертого элемента И-НЕ и через второй инвертор с вторым входом пятого элемента И-НЕ, выходы двоичного реверсивного счетчика соединены с входами второго дешифратора, первьм выход которого через третий инвертор соединен с первым входом шестого элемента И-НЕ, вход Запись .блока управления через четвертый инвертор соединен с вторыми входами первого и шестого элементов И-НЕ, вьгход шестого элемента И-НЕ является первым выходом блока управления, второй выход второго дешифратора через пятый инвертор соединен с первым входом седьмого элемента И-НЕ, второй вход которого соединен с входом Чтение блока управления, выход седьмого элемента И-НЕ соединен с инверсным входом второго , элемента И. третий выход второго дешифратора соединен с тактовым входом четвертого D-триггера и через шестой инвертор .с первым входом восьмого элемента И-НЕ, второй вход которого соединен с инверсным выходом четвертого D-триггера, а выход - с первым входом четвертого элемента И; второй вход которого подключен к входу Сброс блока управления, вход Сброс блока управления подключен также к инверсному R-входу второго D-триггера и второму входу третьего элемента И, информационные входы второго и четвертого D-триггеров соединены с шиной нулевого потенциала блока управления, инверсный выход одновибратора соединен с инверсным S-входом чет1зертого D-триггера и через седьмой -инвертор с тактовьЕ-i входом второго D-триг - гера, инверсный З--БХОД второго Б-триггера соединен с первым выходом первого дешифратора,, а выход является восьмым выходом блока управления, первый, второй и третий входы девятого элемента И-НЕ подключены соответственно к входам Синхрониза- ция, Такт и к первому входу первой группы входов блока управления, а выход соединен с тактовым входом пятого D-триггера и через восьмой инвертор с тактовым входом шестого D-триггера, инверсный выход которого соединен с первым входом десятого элемента И-НЕ, выход которого является четвертым выходом блока управления, выход пятого D-триггера сое- динен с вторым входом-десятого элемента И-НЕ и с первьм входом одиннадцатого элемент , выход которого соединен с первым входом пятого Элемента И, второй вход которого сое динен с выходом второго элемента И-НЕ а выход пятого э лемента И является третьим выходом блока управления, второй вход одиннадцатого элемента И соединен с выходом шестого эле- мента И, первый и второй входы которого подключены к входу.Строб и первому входу первой группы входов блока управления, инверсные S-входы пятого и шестого D-триггеров под- ключены соответственно к входам Чтение из памяти и Строб блока управления, информационные входы пятого и шестого D-триггеров соединены

с шиной нулевого потенциала блока, выход пятого В-триггера является седьмым выходом блока управления. 3. Устройство по п. 1, о т л, и- чающееся тем, что формирователь такта содержит D-триггер, одновибратор, элемент И, инвертор и три элемента И-НЕ, при этом вход Такт группы входов формирователя такта соединен через инвертор с первым входом первого элемента .И-НЕ и с первым входом второго элемента И-НЕ, второй вход которого подключен -к входу Синхронизация формирователя такта, а выход соединен с первым входом элемента И, вход Чтение из памяти формирователя такта подключен к инверсному S-входу В-триггера, тактовый вход которого соединен с входом Чтение формирователя такта и с вторым входом первого элемента И-НЕ, выход которого подключен к входу одновибра- ора, выход одновибратора соединен с первьм входом третьего элемента И-НЕ, второй вход которого подключен к йы ходу D-триггера, информа ционный вход последнего является информационным входом формирователя такта, выход третьего элемента И-НЕ соедине с вторым входом элемента И, выход которого является выходом формирователя такта.

KES

DO 2 e S9-Jt

J

1 yir

m

$-iS Выход SR /

М2

///

/// мг нд /У/ нг м5 /V/ мг /yj

(Рие.б. Jfo/f/n/fa jr6f/afff ffrov rar SL

Н2

/УЗ

(Риг. 6 Tafr/nS--v/ne Lfe

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода информации | 1983 |

|

SU1137475A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1365087A2 |

| Цифровой компаратор | 1987 |

|

SU1552136A1 |

| Устройство для контроля логических блоков | 1979 |

|

SU875390A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля и диагностики многоканальной цифровой аппаратуры | 1986 |

|

SU1348758A1 |

| Патрик П | |||

| Фазанг Microbit - способ самоиспытания сложных микрокомпьютеров | |||

| - Электроника, № 5, 1983, с | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Патент США 4208359, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1986-07-30—Публикация

1984-12-27—Подача