Изобретение относится к автоматике и вычислительной технике и может использоваться для построения устройств переработки дискретной информации

Цель изобретения - построение устройства, обеспечивающего преобразование ла- раллельного унитарного кода в дифференциально-разностный семиразрядный код ранга t 1.

На чертеже изображена схема преобразователя 49-разрядного параллельного унитарного кода в семиразрядный дифференциально-разностный код ранга .

Дифференциально-разностные коды представляют собой новый класс кодов, предназначенных для использования в системах классификации и распознавания. Дифференциально-разностные коды в литературе не описаны, процедуры их получения отсутствуют, кодирующие и декодирующие устройства для данного класса кодов в научно-технической и патентной литературе не встречаются.

Преобразователь содержит элементы 1-23 запрета, элементы ИЛИ 24-30, входы 31 и выходы 32.

Работа преобразователя основана на следующем.

Дифференциально-разностным кодом ранга t называется непозиционный двоичный код. обладающий тем свойством, что сумма по модулю два кодов, соответствующих двум числам zi и Z2, имеет г I Z2-Јi I единиц при Iz2-zil t и r t единиц при Iz2-zil t.

Дифференциально-разностный код позволяет значительно повысить быстродействие цифровых систем распознавания образов и других систем классификации, предназначенных для оешения вопроса об эквивалентности двух объектов zi и Z2, представляемых векторами признаков, на основе критериев

2 |z i-z2| J7, i 1

где zi , Z21 - значение 1-го признака, if- порог.

Это достигается тем, что операции вычитания, требующие межразрядных переносов, заменяются операциями поразрядного

(Л

С

о VI

Ю

о

х|

сложения по модулю два. Преобразователи параллельного унитарного кода в дифференциально-разностный используются в аналого-цифровых преобразователях с непосредственным считыванием.

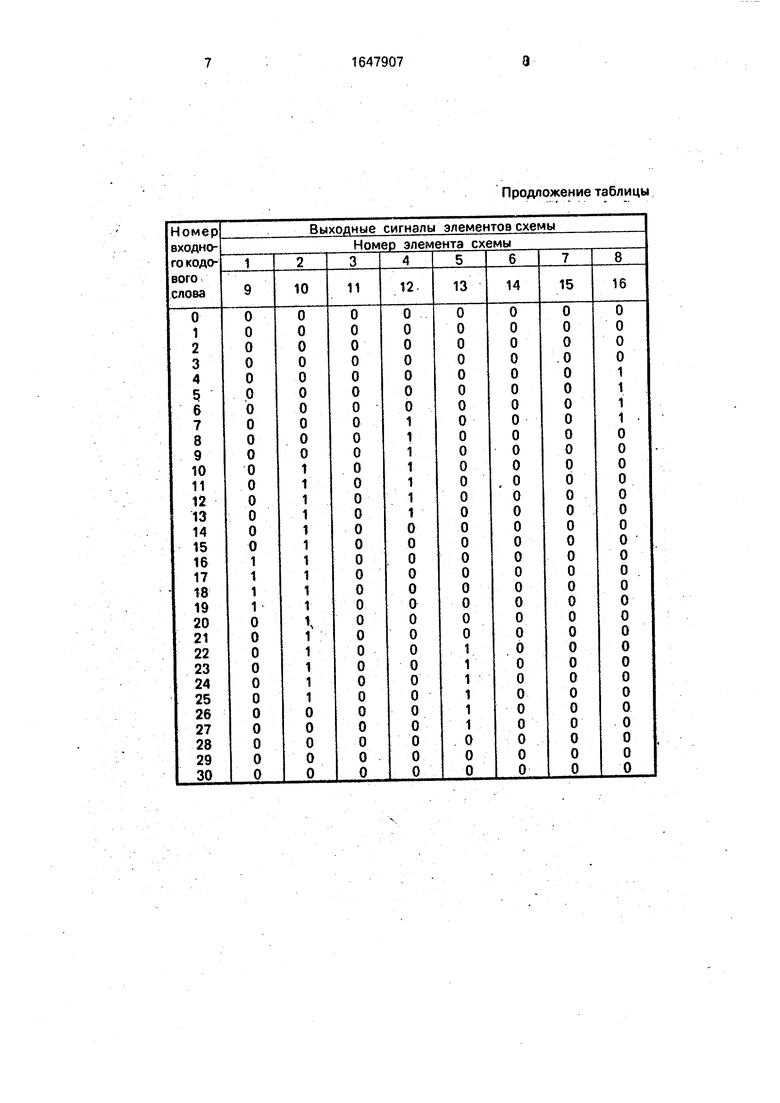

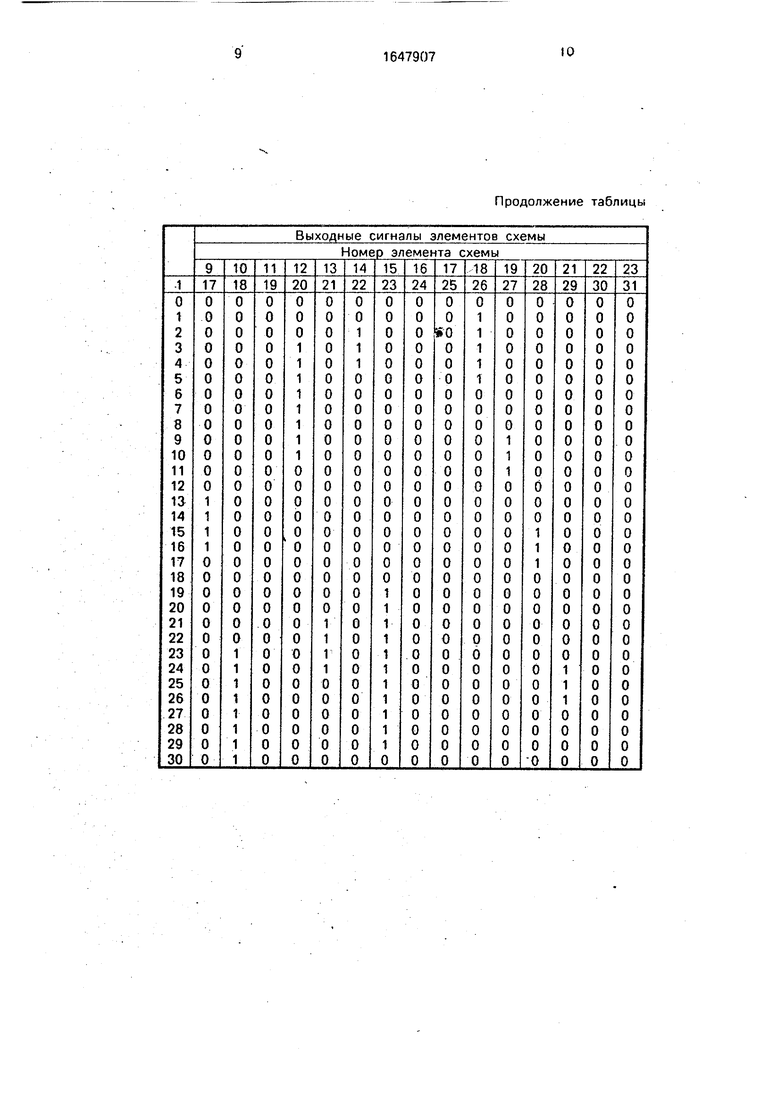

Функционирование преобразователя иллюстрируется таблицей и происходит следующим образом,

На его входы подается параллельный

унитарный код X (, причем для

числа N (N-й кодовой комбинации входного кода)

И при IS N, х, j

фпри l N.

Выходные сигналы преобразователя и его элементов для всех входных кодовых комбинаций представлены в таблице.

Очевидно, что на выходах преобразователя формируется семиразрядный дифференциально-разностный код ранга , обладающий следующим свойством:

Iba-zil при I Z2-Z1I t Sum(znЈ)Z2) /

(г t при t, где Sum - сумма числа единиц двоичного кодового слова, получаемого поразрядным сложением по модулю двух кодовых слов zi и Z2, соответствующих числам zi и и.

Предлагаемый преобразователь может использоваться в быстродействующих ана- логоцифровых преобразователях с непосредственным считыванием в качестве кодирующего логического устройства. При этом f-й вход преобразователя соединяется с выходом 1-го аналогового компаратора напряжений, первый вход которого соединен с информационным входом аналого-цифрового преобразователя, а выход - с 1-м выходом цепочки последовательно соединенных прецизионных резисторов, формирующих напряжение смещения.

Формула изобретения

Преобразователь параллельного унитарного кода в дифференциально-разностный код, отличающийся тем, что он содержит с первого по двадцать третий элементы запрета и с первого по седьмой элементы ИЛИ, выходы которых являются выходами преобразователя, с первого по четвертый входы которого соединены соответственно с информационными входами восемнадцатого, четырнадцатого, двенадцатого и восьмого элементов запрета, выходы которых соответственно соединейы с первыми входами седьмого по четвертый элементов ИЛИ, вторые входы которых соединены с выходами соответственно девятнадцатого, пятнадцатого, тринадцатого и девятого элементов запрета, пятый шестой и восьмой входы преобразователя соединены соответственно с запрещающими входами четырнадцатого, восемнадцатого и восьмого элементов запрета, седьмой, девятый и десятый входы преобразователя соединены с информационными входами

0 соответственно четвертого, девятнадцатого и второго элементов запрета, запрещающие входы которых соответственно соединены с четырнадцатым, двенадцатым и двадцатым входами преобразователя,

5 одиннадцатый, семнадцатый, восемнадцатый и двадцать третий входы которого соединены соответственно с запрещающими входами двенадцатого, девятого, двадцатого и десятого элементов запрета,

0 тринадцатый, пятнадцатый, шестнадцатый и девятнадцатый входы преобразователя соответственно соединены с информационными входами девятого, двадцатого, первого и пятнадцатого элементов запрета,

5 двадцать первый, двадцать второй и двадцать четвертый входы преобразователя сое- динены соответственнос

информационными входами тринадцатого, пятого и двадцать первого элементов запре0 та, запрещающие входы которых соединены соответственно с двадцать пятым, двадцать восьмым и Двадцать седьмым входами преобразователя, входы преобразователя с тридцать первого по тридцать пятый соот5 ветственно соединены с информационными входами шестого, десятого, двадцать второго, шестнадцатого и третьего элементов за- п рета, тридцатый, тридцать седьмой, тридцать де- вятый.сороковойисороктретий входы преобразо0 вателя соответственно соединены с запрещающими входами пятнадцатого, шестого, двадцать второго, шестнадцатого и третьего элементов запрета, тридцать восьмой, сорок первый, сорок второй и сорок четвертый

5 входы преобразователя соответственно соединены с информационными входами одиннадцатого, седьмого, двадцать третьего и семнадцатого элементов запрета, входы преобразователя с сорок пятого по сорок восьмой

0 соединены соответственно с запрещающими входами двадцать третьего, одиннадцатого, седьмого и семнадцатого элементов запрета, выход первого элемента запрета соединен с первым входом первого элемен5 та ИЛИ, второй вход которого соединен с двадцать девятым входом преобразователя, выходы второго третьего элементов запрета соединены соответственно с первым и вторым входами второго элемента ИЛИ, выходы с четвертого по седьмой элементов

запрета соответственно соединены с первого по четвертый входами третьего элемента ИЛИ, выходы десятого и одиннадцатого элементов запрета соответственно соединены с третьим и четвертым входами четвертого элемента ИЛИ, выходы шестнадцатого и семнадцатого элементов запрета соединены соответственно с третьим и четвертым входами шестого элемента ИЛИ, выходы с восемнадцатого по двадцать третий элементов ИЛИ соединены соответственно с первого по шестой входами седьмого элемента ИЛИ, седьмой вход которого соединен с сорок девятым входом преобразователя, тридцать шестой вход которого соединен с третьим входом пятого элемента ИЛИ,

Предложение таблицы

Продолжение таблицы

3J

32

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь дифференциально-разностного кода в двоичный | 1988 |

|

SU1594704A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1987 |

|

SU1439577A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| ЭЛЕКТРОПРИВОД МАНИПУЛЯТОРА | 2014 |

|

RU2551044C1 |

| Устройство для распознавания функциональной полноты систем логических функций | 1979 |

|

SU960795A1 |

| САМОНАСТРАИВАЮЩИЙСЯ ЭЛЕКТРОПРИВОД МАНИПУЛЯТОРА | 2017 |

|

RU2688448C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРИВОДОМ РОБОТА | 2007 |

|

RU2355563C2 |

| Устройство автоматического отключения нагрузки энергосистем при снижении напряжения | 1988 |

|

SU1636923A1 |

| САМОНАСТРАИВАЮЩИЙСЯ ЭЛЕКТРОПРИВОД МАНИПУЛЯЦИОННОГО РОБОТА | 2017 |

|

RU2688449C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 2003 |

|

RU2251141C1 |

Изобретение относится к автоматике и вычислительной технике и может использоваться для построения устройств переработки дискретной информации. Поставленная цель достигается тем, что преобразователь содержит элементы запрета, элементы ИЛИ. На входе преобразователя при этом формируется семиразрядный дифференциально- разностный код числа N. 1 табл., 1 ил.

| Гнатек Ю.Р | |||

| Справочник по цифроана- логовым и аналого-цифровым преобразователям | |||

| - М.: Радио и связь, 1982, с | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-05-07—Публикация

1988-06-27—Подача