е4 &0 СО

сд ч

4j

тельной технике и может быть использовано для суммирования многоразрядных последоззательных дополн гтельных кодо13 с иррациональными основаниями.,

Целью изобретения является расширение функциональных возможностей за счет слолсения дополнительных кодов с иррациональными основаниями

На фиг.1 и 2 представлена фyнкu o напьная схема последовательного сумматора кодов с иррациональными основаниями.

Последовательный сумматор кодов с иррациональными основаниями, содержит элементы ИЛИ 1, И 2-8., ИЛИ 9, 10 И 11, 12., НЕ 13-15, D-трш-геры 16 и 17, элементы Ш1И 18, И 19-22, ИЛИ

вует множество форм представления одного числа,, Из всего этого множества существует одна форма представления, в которой после каждой единицы может быть не менее одного нуля, т.е. минимальная форма представления.

Дополнительным кодом числа A,,, на- зывается код, полученный при вычитании Afjj из DH,, где D,(( - число, заведомо большее любого А,, т.е. f Aj,

Число А f в коде с иррациональными основаниями можно представить в виде NjH

. ,

где ( - основание системы счисления; N - разрядность представления

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1983 |

|

SU1170449A1 |

| Последовательное устройство для умножения | 1987 |

|

SU1444754A1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ДВОИЧНЫХ КОДОВ | 2010 |

|

RU2410746C1 |

Изобретение относится к вычислительной технике и может быть использовано для сложения двух многоразрядных последовательных кодов с иррациональными основаниями. Цель изобретения - расширение функциональньгх возможностей сумматора за счет сложения дополнительных кодов с иррациональными основаниями. Сумматор содержит пять D-триггеров, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, три элемента НЕ, тринадцать элементов ИЛИ, сорок три элемента И, вход начальной установки, так- товый вход, входы последовательных g слагаемых, стробирующий вход дополнительного кода, выход результата. 2 ил., 1 табл. (Л

23-26, И 27-36з ИЛИ 37-39,, И 40-42, ИЛИ 43, В-триггеры 44-46, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 47j элементы И 48-51, элемент ИСКЛЮЧАЮЩЕЕ. ИЛИ 52, элементы И 53-65, ИЛИ 66, выход б7 результатаэ

вход 68 первого слагаемого, вход 69 25 ниями

второго слагаемого, стробирующий вход 70, тактовый вход, 71,- вход 72 начальной установки, связи 73-107 между элементa и устройства.

Элементы ИЛИ t, 9.

, 12,

37-39 и 43, элементы И 2-8,. 11 19-22, 27-36, 40-42, 48-51., 53-fi2, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 47, 52, ИЕ 13-15 предназначены для формирования промежуточных значений алгебраический суммы, D-триггеры 16, 44 предназначены для запоминания младших разрядов промежуточных значений алгебраической

Для перевода положительного числа в дополнительный код в начале прямого кода добавляются три нулевых разряда, старший из которых является

суммы, D-триггеры 17j 45, 46 предназначены для запоминания старших раз- Q зн-аковыМо

рядов промежуточных значений алгебра- Для обнаруженР я переполнения вво- ической cyMivibi, элементы И 63-65, дится еще четвертьй дополнительный ИЛИ 66 предназначены для формирования разряд. Таким образом, дополнитель- вых9дньгх значений алгебраической ный. код числа Ац; будет прёдстаапятьдс С.Я N+4 разрядами, старший из которых является знаковым.

, Рассмотрим пример представления положительных и отрицательных чисел в дополнительном коде с иррациональcym«j,

Сущность и физическая возможность реализации сумматора заключаются в следующем,

Б кодах с иррациональными основаниями, к которым относятся коды Фибоными основаниями.

Положительный код 1 О О 1 1 О 1 О 1 1 1 О 1 О будет представлен следуюшим образом:

О О О 010011010111010

Допол- нитель- ные

разряды

Основные разряды

кода, - значение i-ro разряда, b 0,1 j i - номер разряда кода, ,

1 5 2, .,„, N-1. В кодах с иррациональными основаниями

N 1

, N-I-I

N-1

П+1

. W -- , п -г I г I

21 « °

В качестве D выбирается d , и дополнительньй код отрицательного

числа образуется путем вычитания из единицы веса N+1 разряда модуля отрицательного числа., Дополнительньй код получается (1 Н2)-разрядныЙ5 а в (К+3)-м разряде-записывается знак

прямого Кода числа.

Для перевода положительного числа в дополнительный код в начале прямого кода добавляются три нулевых разряда, старший из которых является

зн-аковыМо

ными основаниями.

31439577

Отрицательньй код - 1 О О 1 101011 I О ГО будет представлен следукщим образом:

.00000101001001

Знаке- Дополвый нитель- Основные разряды

разряд ные

разряды

I

В результате вычислений в старших Ю навливаются также нулевые значения, четырех разрядах положительного кодаПоступление слагаемых на входы 68 и

могут получаться также кодовые комби- 69 для алгебраического сложения кодов нации 101 1, 1 100. Эти кодовыес иррациональными основаниями начикомбинации в дальнейших вычисленияхнается со старших разрядов после сняучаствуют как характеристики положи- 15 тия сигнала начальной установки. При тельных чисел. Таким образом, возмож- сложении прямых кодов с иррациональны четьфе кодовые комбинации в стар-ными основаниями на строб1фующий ших четьфех разрядах дополнительного вход 70 подается постоянньй нулевой кода: 0000; 1010; 101 1; сигнал, а при сложении дополнительных .1 1 00. Появление других комбинаций 20 кодов - в течение первых двух стар- в этих разрядах свидетельствует о пе- . чих разрядов последовательного кода реполнении разрядной сетки прямого единичный сигнал, в остальное время представления числа. также нулевой сигнал. IЕдиничный сигнал на стробирующем

Сложение дополнительных кодов с 25 входе 70 устанавливает на первых вхо иррациональными основаниями произво-Дах элементов И 2, 3 и на вторых

дится, начиная со старших разрядов,входах элементов И 11, 35, 40, 42 нусогласно правилам Фибоначчиевой ариф- левой потенциал, чем запрещается про- метики.хождение сигналов по другим входам

Чтобы исключить выход единицы за 30 указанных элементов. На вторых входах формат дополнительного кода со сторо- элементов И 4, 12, 36 и на первом ны старших разрядов, необходим управ- входе элемента И 41 присутствуют еди- ляющий сигнал, который приходит наничные потенциалы, разрешающие учаспериод знакового и первого дополни-тие в формировании промежуточных знательного разряда. Этот сигнал называ- 35 чений алгебраической элемента ется стробирующим сигналом. Во времяИСКШОЧАМЦЕЕ ИЛИ 47 и элемента И 48,,

его действия запрещается перенос вВ третьем такте на стробирукяций

(1+1)-й разряд, а в (1+2)-й разрядвход 70 приходит нулевой сигнал, при

записывается ноль. . этом на первых входах элементов И 2,

Последовательный сумматор произво-40 3 и на вторых входах элементов И 11, дит сложение как прямых, так и допел- 35, 40, 42 устанавливается единичный нительньгх кодов с иррациональными ос- потенциал, чем разрешается выполнение нованиями.операции сложения с помощью элементов

В дополнитепьных кодах с иррацио- И 2, 3, 5-8, 19-22, 27-34, 48-51, напьными основаниями, так же как и 45 53-64, элементов ИЛИ 1, 9, 10, 23-26, в дополнительных кедах классической . 37, 38, 66, элементов ИСКШОЧАЮИ ЕЕ ИЛИ двоичной системы счисления, знак чис- 47, 52. Одновременно запрещается про- ла представляется перед старшим раз-хождение сигналов с вькодов элемента

рядом кода и участвует в операцииИСКЛЮЧАЮЩЕЕ ИЛИ 47 и элемента И 48

сложения.QQ через элементы И 4, 12, 36, 41.

Последовательный сумматор кодовРассмотрим более подробно процесс

с иррациональными основаниями работа- последовательного сложения дополни- ет следующим образом.тельных кодов с иррациональными осноПри поступлении сигнала на вход 72 ваниями на следующем примере: начальной установки D-триггеры 16, gg х 1010101001010; 17, 44, 45, 46 устанавливаются в ну-у 101010010010 1.

левое состояние, при этом на выходахПеред поступлением кедов на входы

всех элементов И, всех элементов ИЛИ, 68 и 69 слагаемых на вход 72 началь- всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ уста- ной установки его поступает сигнал

начальной установки и устанавливает все D-триггеры в нулевое состояние,

Одновременно с подачей старших значащих разрядов в течение первых двух тактов на стробирующий вход 70 поступает единичный потенциал. По каждому тактовому импульсу поступают следующие разряды кодов слагаемых, начиная со старших разрядов.

Единичные значения старших разр)Я- дов в первый такт поступают на входы 68 и 69 слагаемых, на стробирующи вход 70 поступает также единичньм потенциал. На выходе элемента НЕ 15 устанавливается нулевой потенциал, который, поступая на первые входы - элементов И 2, 3 и вторые входы элементов И 11, 35, 40, 42, подтверждает на их выходах нулевой потенциал. Единичные сигна.пы поступают на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 47 и элемента И 48, при этом на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 47 подтверждается нулевой потенциал, а на выходе элемента И 48 устанавливается единичньш по- тенциал. Этот единичньш потенциал поступает на первьй вход элемента И 36, на втором входе которого присутствует единичный потенциал со стробирующего входа 70, и через элемент ИЛИ 39 поступает на D-ВХОД триггера 44,

С приходом второго тактового импульса на вход 71 в триггер 44 записывается- единица, и на входах 68 и 69 слагаемых устанавливаются значения вторых разрядов слагаем1:11к (в нашем случае нулевые потенциалы). Единичный потенциал прямого выхода триггера 44 поступает на первый вход элемента И 4, на втором входе которого присутствует единичный потенциал со стробирующего входа 70, и через элемент ИЛИ 9 поступает на D-вход триггера 16.

С приходом третьего тактового импульса на вход 71 триггер 16 устанавливается в единичное состояние, а триггер 44 устанавливается в нулевое состояние. На входах 683. 69 слагаемых устанавливаются значения третьих разрядов слагаемых (в нашем случае еди ницьО, на стробирующем входе 70 устанавливается нулевой потенциал, а на выходе элемента НЕ 15 - единичньй

потенциал. На первых входах элементов gc единичный потенциал с прямого выхода И 2, 3 и на вторых входах элементов триггера 44, а на четвертом входе - И 11, 35, 40, 42 устанавливается еди- единичньй потенциал с выхода элемен- .ничный потенциал, а на вторых входах та ИСКЛЮЧАЮЩЕЕ ИЛИ 52. На выходе эле- элементов И 4, 12, 36 и на первом мента И 2 устанавливается единичньй

10

15

395776

входе элемента И 41 устанавливается нулевой потенциал.

На выходах элементов И 48, 49 устанавливаются единичные потенциалы, так как на обоих входах элемента И 48, присутствуют единичные значения разрядов cлaгae ыx, а на входах элемента И 49 присутствуют единичные потенциалы с прямого выхода триггера 16 и инверсных выходов триггеров 17 и 44.

Единичный потенциал с выхода элемента И 48 поступает на первый вход элемента И 21, на другом входе которого присутствует единичный потенциал с прямого выхода триггера 16, и через элемент ИЛИ 26, элемент И 35 и элемент ИЛИ 39 поступает на D-вход триггера 44,.

Единичный потенциал с выхода элемента И 49 через элемент ИЛИ 25 поступает на первьй вход элемента И 30, на втором входе которого присутствует единичный потенциал с выхода элемен- 25 та И 48. С выхода элемента И 30 единичный потенциал через элемент ИЛИ 38 и элемент И 42 поступает на D-вход триггера 46.

С приходом четвертого тактового импульса, триггеры 44 и 46 устанавливаются в единичное состояние, а триггер 16 - в нулевое состояние.

Единичный потенциал с прямого выхода триггера 46, прохода через эле20

30

35

40

45

50

мент ИЛИ 66, устанавливается на выходе 67 и является старшим разрядом результата алгебраического сложения. На входы 68 и 69 слагаемых поступают нулевые значения разрядов слагаемых. На выходах элементов НЕ 13 и 14 устанавливаются единичные потенциалы, которые поступают на входы элемента И 51,

На первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 52 присутствует нулевой потенциал, а на втором входе - единичньй потенциал с прямого выхода триггера 46, который и устанавливается в на выходе элемента ИСКЛЮЧА ОЩЕЕ ИЛИ 52

На первом входе элемента И 2 присутствует единичный потенциал с выхода элемента НЕ 15, на втором входе - единичный потенциал с выхода элемента И 51, на третьем входе потенциал, которьй через элемент ИЛИ 9 поступает на D-вход триггера 16.

С пр11ходом пятого тактового импульса триггер 16 устанавливается в единичное состояние, а триггеры 44 и 46 - в нулевое состояние.

На входах 68 и 69 слагаемых устанавливаются значения пятых разрядов слагаемых (в нашем случае устанавливаются единичные потен;циалы) .

На выходе 67 устанавливается нулевой потенциал, который является вторым разрядом результата алгебраического сложения. На выходах элементов И 48 и 49 устанавливаются единичные потенциалы. Как и во время третьего такта, на D-входах триттеров 44 и 46 устанавливаются единичные потенциалы

С приходом шестого тактового им- пульса происходят переключения, таки же как и во время четвертого тактового, импульса. На выходе 73 устанавливается единичный потенциал.) которы является третьим разрядом результата алгебраического сложения.

С приходом седьмого тактового импульса триггер 16 устанавливается в. единичное состояние, а триггеры 44

35

и 46 - в нулевое состояние. На входах зо хода триггера 45, на третьем входе - 68 и 69 слагаемых устанавливаются значения седьмых разрядов слагаемых (на выходе 68 устанавливается единич- ньй потенциал, на входе 69 устанавливается нулевой потенциал).

На выходе элемента ИСКЛЮЧАЮЩЕЕ РШИ 47 устанавливается единичный потенциал, Которьй поступает на первый вход элемента И 19. На первом входе элемента И 49 присутствует единичный 40 потенциал с инверсного выхода триггера 17, на втором входе - с прямого выхода триггера 16, на третьем входе- с инверсного выхода триггера 44 и единичньй потенциал с выхода элемен- g та И 49 поступает на второй вход эле- мента И 19. Единичный потенциал с выхода элемента И 19 через элемент ИЛИ 26, элемент И 35 и элемент ИЛИ 39 поступает на D-вход триггера 44. gQ

На выходе 67 устанавливается нулевой потенциал, который является

с инверсного выхода триггера 46. Единичный потенциал с выхода элемента И 59 поступает на первьй вход элемента И 63.

На выходе 67 устанавливается единичный потенциал, который является пятым разрядом результата алгебраического сложения.

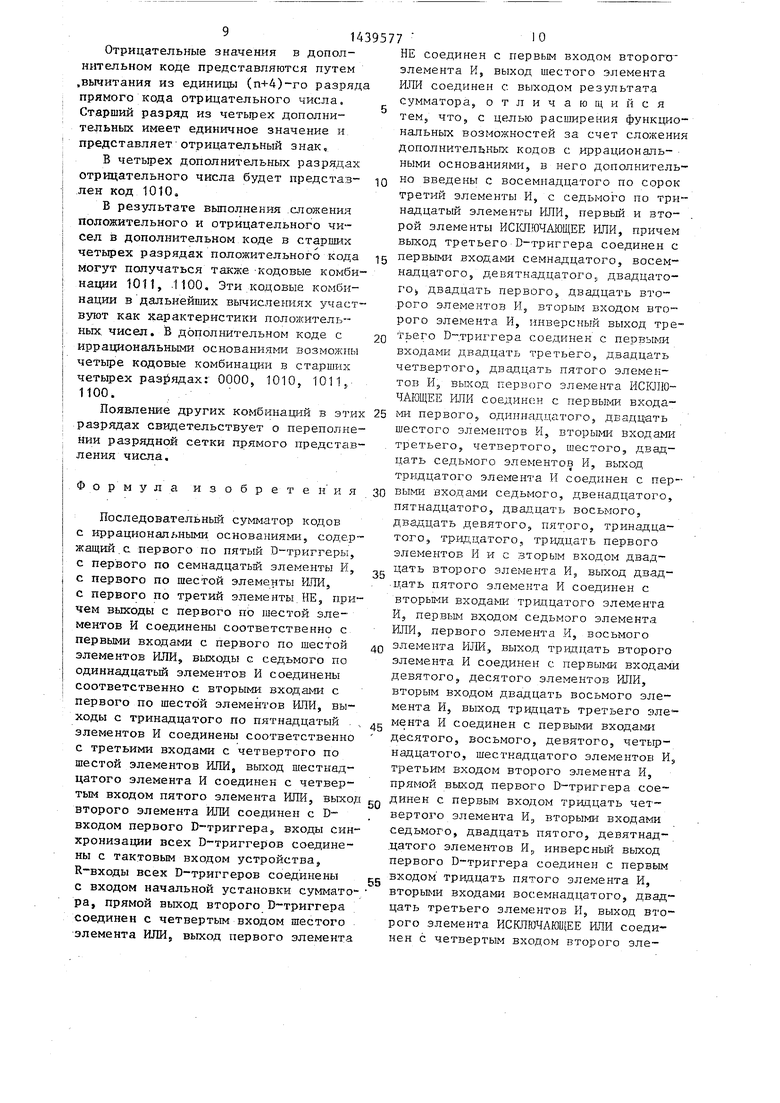

Результаты процесса сложения представлены в таблице,;

Сложение прямых последовательных : кодов с иррациональными основаниями производится при постоянном нулевом потенциале на стробирукщем входе 70 аналогично рассмотренному процессу, начиная с третьего такта.

Положительные значения в дополнительном коде представляются путем прибавления со стороны старших разрядов прямого кода четьфех нулевых разрядов, старший из которых является знаковым.

п+3,,п,п-1,п-2,п-3 ... ,4,3,2,1,0,

Дополнительные разряды

Дополнительный код

четвертым разрядом результата алгёб- раическ ого сложения.

Единичный потенциал с вьпсОда элемента И 49 проходит через элемент ИЛИ 23 и поступает на первый вход элемента 1 27, на второй вход которого поступает единичный потенциал с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 47. Единич- ный потенциал с выхода элемента И 27 через элемент PiЯИ 37, элемент И 40, элемент ИЛИ 43 поступает на D-вход триггера 45,

С приходом восьмого тактового импульса триггеры 44 и 45 устанавливаются в единичное состояние, на входы 68 и 69 слагаемых поступают значения восьмых разрядов слагаемых (на входе

68 устанавливается нулевой потенциал, на входе 69 устанавливается единичный потенциал).

На выходе элемента ИСКЛЮЧАКЩЕЕ ИЛИ 47 поддерживается единичный потенци-

ал, которьш поступает на второй вход элемента И 63. На первом входе элемента И 59 присутствует единичный потенциал с прямого выхода триггера 44, на втором входе - с прямого вы-

хода триггера 45, на третьем входе -

с инверсного выхода триггера 46. Единичный потенциал с выхода элемента И 59 поступает на первьй вход элемента И 63.

На выходе 67 устанавливается единичный потенциал, который является пятым разрядом результата алгебраического сложения.

Результаты процесса сложения представлены в таблице,;

Сложение прямых последовательных : кодов с иррациональными основаниями производится при постоянном нулевом потенциале на стробирукщем входе 70 аналогично рассмотренному процессу, начиная с третьего такта.

Положительные значения в дополнительном коде представляются путем прибавления со стороны старших разрядов прямого кода четьфех нулевых разрядов, старший из которых является знаковым.

Основные разряды прямого кода

Отрицательные значения в дополнительном коде представляются путем .вычитания из единицы (п+4)-го разряд прямого кода отрицательного числа. Старший разряд из четырех дополнительных имеет единичное значение и представляет отрицательный знак,

В четырех дополнительных разрядах отрицательного числа будет представлен код 1010 а

В результате выполнения .сложения положительного и отрицательного чисел в дополнительном коде в старших четьфех разрядах положительного кода могут получаться также -кодовые комбинации 1011, .1100. Эти кодовые комбинации в дальнейших вычислениях участвуют как характеристики пололситель-- ных, чисел. В допол штельном коде с иррациональными основаниями возмол :г1ы четьфе кодовые комбинащ-1и в старших четырех раз| ядах: 0000, 1010, 1011,, 1100.

Появление других комбинаций в этих 25 мя первого, одиннадцатого, двадцать

разрядах свидетельствует о переполнении разрядной сетки прямого представления числа.

Формула изобретен ия

Последовательный сумматор кодов с иррациональными основаниями, содержащий, с первого по пятый D-триггеры, с первого по семнадцатый элементы И, с первого по шестой элементы ИЛИ, с первого по третий элементы.НЕ, причем выходы с первого по шестой элементов И соединены соответственно с первыми входами с первого по шестой элементов ИЛИ, выкоды с седьмого по одиннадцатый элементов И соединены соответственно с вторыми входами с первого по шестой элементов ИЛИ, выходы с тринадцатого по пятнадцатый . элементов И соединены соответственно с третьими входами с четвертого по шестой элементов ИЛИ, выход жестыад- датого элемента И соединен с четвертым входом пятого элемента ИЛИ, выход второго элемента ИЛИ соединен с D- входом первого D-триггера,, входы синхронизации всех D-триггеров соединены с тактовым входом устройства, R-входы всех D-триггеров соед инены с входом начальной установки сумматора, прямой выход второго В триггера соединен с четвертым входом шестого элемента ИЛИ, выход первого элемента

НЕ соединен с первым входом второго- элемента И, выход шестого элемента ИЛИ соединен с выходом результата сумматора, отличающийся тем, что, с целью расширения функциональных возможностей за счет сложения дополнителькьос кодов с иррациональными основаниями, в него дополнительно введены с восемнадцатого по сорок третий элементы И, с седьмого по тринадцатый элементы ИЛИ, первый и вто- . рой элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выход третьего D-триггера соединен с g первыми входами семнадцатого, восемнадцатого, девятнадцатого., двадцато- roj двадцать первого, двадцать второго элементод И, вторым входом второго элемента И, инверсный выход третьего В триггера соединен с первыми входами двадцатгз третьего, двадцать четвертого, двадцать пятого элементов И, выход первс го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первыми вкода0

шестого элементов И, вторыми входами третьего, четвертого, шестого, двадцать седьмого элементов И, выход тридцатого элемента И соединен с пер- входами седьмого, двенадцатого, пятнадцатого, двадцать восьмого, вадцать девятого, пятого, тринадцатого, тридцатого, тридцать первого элементов И и с вторым входом двадцать второго элемента И, выход двадцать пятого элемента И соединен с вторыми входа1 ш тридцатого элемента И, первым входом седьмого элемента ИЛИ, первого элемента И, восьмого элемента ИЖ, выход тридцать второго элемента И соединен с первыми входами девятого, десятого элементов ИЛИ, вторым входом двадцать восьмого элемента Hj выход тридцать третьего эле- мента И соединен с первыми входами десятого, восьмого, девятого, четырнадцатого, шестнадцатого элементов И, третьим входом второго элемента И, прямой выход первого D-триггера соединен с первым входом тридцать четвертого элемента И, вторыми входами седьмого, двадцать пятого, девятнад- .цатого элементов И,, инверсный выход первого D-триггера соединен с первым

входом тридцать пятого элемента И,

вторыми входами восемнадцатого, двадцать третьего элементов И, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с четвертым входом второго эле

мента И, выход восемнадцатого элемента И соединен с вторым входом восьмого элемента ШЖ, вторыми входами восьмого элемента И, одиннадцатого элемента ИЛИ, выход двадцать третьего элемента И соединен с вторыми входами девятого, десятого элементов ИЛИ, выход девятнадцатого элемента И соединен с третьими входами девятого, десятого элементов ИЛИ, выход двадцать четвертого элемента И соединен с первым входом двадцать седьмого элемента И, четвертым входом девятого элемента ИЛИ, прямой выход четверто- го D-триггера соединен с первыми входами тридцать второго, тридцать шестого, тррздцать седьмого элементов И, вторыми входами тридцать четвертого, тридцать пятого элементов И, инверс- ный выход четвертого D-триггера соединен с третьим входом двадцать пятоэлементов И, вторым входом двадцать четвертого элемента И, третьи и вхо- 25 дами двадцать второго, двадцать тре- тьего элементов И, выход тридцать четвертого элемента И соединен с первым входом тридцатого, вторым входом шестнадцатого элементов И, пятым вко- ЗО восьмого элементов И соединены соот- дом девятого элемента ИЛИ, выход ветственно с третьим и четвертым вхотьего элемента И, вход первого операнда сумматора соединен с первыми входами первого элемента ИСКЛЮЧАЮЩЕЕ ГШР, тридцать девятого элемента И, выход третьего элемента НЕ соединен с вторым входом тридцать третьего элемента И, вход второго операнда сумматора соединен с входом третьего элемента НЕ, вторыми входами первого элемента ИСКЛЮЧАОДЕЕ ИЛИ, девятого элемента И, элемента НЕ соединен с первыми входами сорокового, сорок первого, сорок второго, сорок третьего элементов И, тактовьш вход сумматора соединен с входом первого элемента НЕ, первым входом тр1адцать седьмого элемента И, вторыми входами семнадцатого, двадцать шестого, двадцать девятого элементов И, прямой выход второго D- триггера соединен с вторыми входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, двадцать первого элемента И, инверсный выход второго D-триггера соединен с третьими входами девятнадцатого, двадцатого элементов И, четвертым входом восемнадцатого элемента И, выходы двадцать второго и двадцать

трвдцать шестого элемента И соединен с вторым входом тридцатого элемента И, вторым входом одиннадцатого элемента И, выход двадцатого элемента И соединен с вторыми входами шестого, тридцать первого элементов И, выход двадцать первого элемента И соединен с третьими входами восьмого, седьмого элементов ИЛИ, выход тридцать пятого элемента И соединен с вторым входом десятого элемента И, четвертым входом седьмого элемента ИЛИ выход тридцать восьмого элемента И соединен с вто50

рыми входами четырнадцатого и пятнад- g седьмого элемента ИЛИ соединен с вто- цатого элементов И, прямой выход пятого D-триггера соединен с первым входом второго элемента ИСКЛЮЧАЩЕЕ ИЛИ, вторыми входами тридцать второ- го, двадцатого, тридцать восьмого элементов И, третьим входом двадцать четвертого элемента И, инверсный вы- :Ход пятого D-триггера соединен с вторым входом тридцать шестого элемента И, третьими входами восемнадцатого, тридцать пятого элементов И, четвертым входом двадцать третьего элемента И, выход второго элемента НЕ соединен с первым входом тридцать тре55

рым входом пятого элемента И, выход двадцать седьмого элемента И соединен с пятым входом пятого элемента ИЛИ, выходы первого, третьего, четвертого, пятого элементов ИЛИ соединены соответственно с вторыми входами сорок первого, сорокового, сорок второго, сорок третьего элементов И, выходы сорок первого, двадцать девятого элементов И соединены соответственно с первым и вторым входами одиннадцатого элемента ИГШ, выход которого соединен с D-входом третьего D-триггера, выходы сорокового и двадцать шеетридцатьвыход первого

восьмого элементов И соединены соот- ветственно с третьим и четвертым вхотьего элемента И, вход первого операнда сумматора соединен с первыми входами первого элемента ИСКЛЮЧАЮЩЕЕ ГШР, тридцать девятого элемента И, выход третьего элемента НЕ соединен с вторым входом тридцать третьего элемента И, вход второго операнда сумматора соединен с входом третьего элемента НЕ, вторыми входами первого элемента ИСКЛЮЧАОДЕЕ ИЛИ, девятого элемента И, элемента НЕ соединен с первыми входами сорокового, сорок первого, сорок второго, сорок третьего элементов И, тактовьш вход сумматора соединен с входом первого элемента НЕ, первым входом тр1адцать седьмого элемента И, вторыми входами семнадцатого, двадцать шестого, двадцать девятого элементов И, прямой выход второго D- триггера соединен с вторыми входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, двадцать первого элемента И, инверсный выход второго D-триггера соедине с третьими входами девятнадцатого, двадцатого элементов И, четвертым входом восемнадцатого элемента И, выходы двадцать второго и двадцать

5

0

дамп первого элемента ИЛИ, выход семнадцатого элемента И соединен с третьим входом второго элемента {ШИ, выход девятого элемента ИЛИ соединен с вторым, входом третьего элемента И, выходы тридцатого и тридцать первого элементов И соединены соответственно с третьим и четвертым входами третьего элемента ИЛИ, выход восьмого элемента ИЛИ соединен с вторым входом четвертого элемента И, выход десятого элемента ИЛИ соединен с первым входом тринадцатого элемента И, выход

50

g седьмого элемента ИЛИ соединен с вто-

55

рым входом пятого элемента И, выход двадцать седьмого элемента И соединен с пятым входом пятого элемента ИЛИ, выходы первого, третьего, четвертого, пятого элементов ИЛИ соединены соответственно с вторыми входами сорок первого, сорокового, сорок второго, сорок третьего элементов И, выходы сорок первого, двадцать девятого элементов И соединены соответственно с первым и вторым входами одиннадцатого элемента ИГШ, выход которого соединен с D-входом третьего D-триггера, выходы сорокового и двадцать шее131439577lA

того элементов И соединены соответ-динены соответственно с первым и втоственно с первым и вторым входамирым входами тринадцатого элемента

двенадцатого элемента ИЛИ, выход ко-ИЛИ, выход которого соединен с D-HXOторого соединен с D-входом четверто-дом пятого D-триггера, выход сорок

го D-триггера, выходы сорок второготретьего элемента И соединен с D-BXOи тридцать седьмого элементов И сое-дом второго D-триггера.

00 О О- 00 0000 о 00 1 о 000 0000 01 о о 000 001 001 010

010 о 010

101 0001

о о 1

00101000100

01 010100011

00 1 000 о010о

00 о 1 0010011

000 о 00 о000о

10 0000 о000о

000 о 10 о100о

о

о 00 00 100100 о о 000 1 01 о 000 1

о 000 о 00 о 000

000000000000

00 0000 о 000 0000 000 001

10 о 010

01 0001

о о 1

10 о 101 о 000

о

| Последовательный сумматор | 1977 |

|

SU696452A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1983 |

|

SU1170449A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-23—Публикация

1987-05-12—Подача