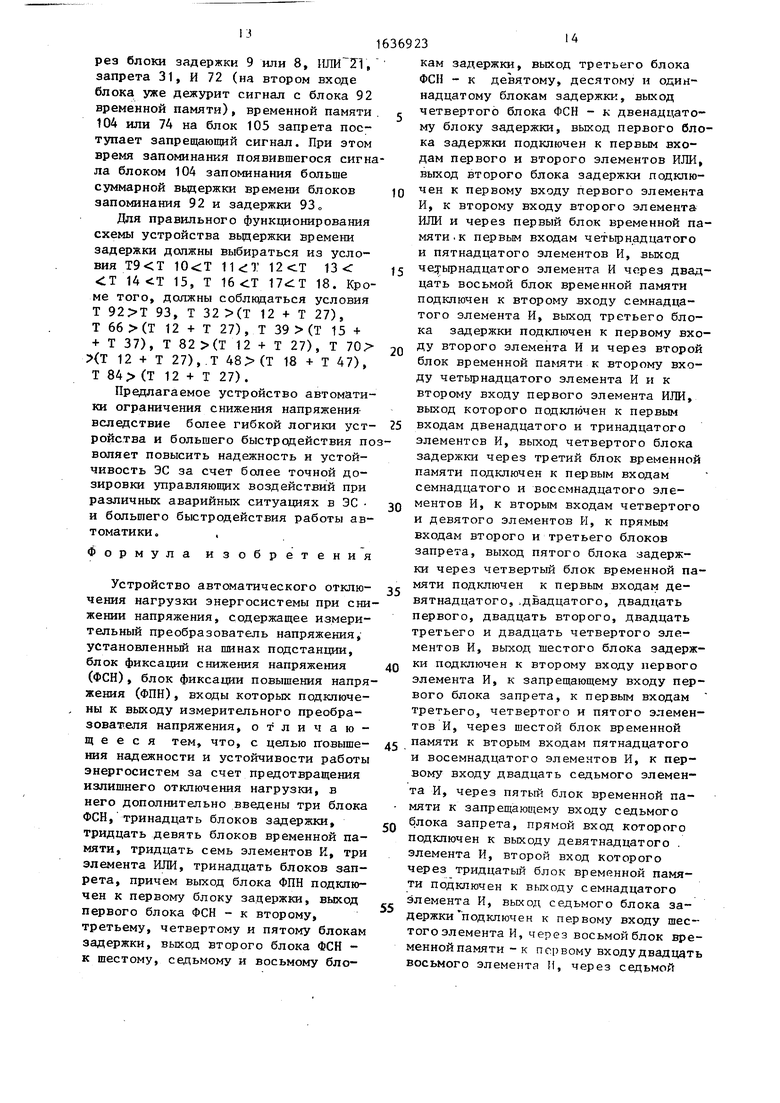

мерительный преобразователь напряжения 2, ступени блока фиксации снижения напряжения 4-7 блок фиксации повышения напряжения 3, блоки задержки 8-19, логические элементы И, блоки временной памяти блоки запрета, логические элементы ИЛИ. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления дозатором | 1990 |

|

SU1791724A1 |

| ЦИФРОВОЕ ПЯТИКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2018 |

|

RU2706198C1 |

| Устройство управления дозатором | 1988 |

|

SU1606874A1 |

| Преобразователь параллельного унитарного кода в дифференциально-разностный код | 1988 |

|

SU1647907A1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Устройство для распознавания функциональной полноты систем логических функций | 1979 |

|

SU960795A1 |

| Система оптимизации управления непосредственно и косвенно управляемыми объектами | 1982 |

|

SU1080117A1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| МОДУЛЬ ДЛЯ ОРГАНИЗАЦИИ ОБМЕНА СООБЩЕНИЯМИ | 2007 |

|

RU2359320C2 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

Изобретение относится к электроэнергетике, в частности к противоаварийной автоматике (ПА) энергосистем, предназначенной для повышения устойчивости и надежности их работы при возникновении аварии. Цель - повышение надежности и устойчивости энергосистем за счет предотвращения излишнего отключения нагрузки. Для этого производится слежение да процессом изменения напряжения в энергосистеме во времени и отключении нуж- ной ступени нагрузки. Устройство содержит сборные шины 1 подстанции, изСО

Изобретение относится к электроэнергетике, в частности к противо- аварийной автоматике (ПА) энергосистем (ЭС), предназначенной для повышения устойчивости и надежности их pa- боты при возникновении аварии.

Цель изобретения - повышение надежности и устойчивости работы энергосистем за счет предотвращения излишнего отключения нагрузки.

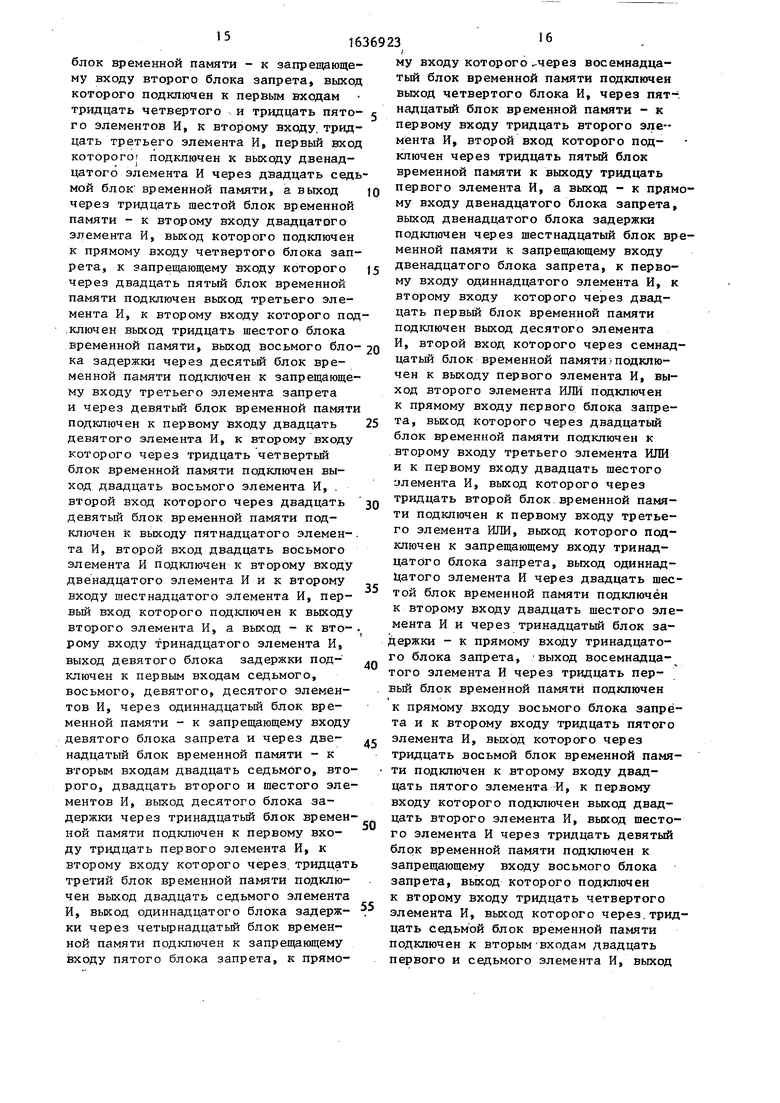

На чертеже представлена блок схема устройства для отключения нагрузки.

Устройство содержит сборные шины 1 подстанции, к которым через измерительный -преобразователь 2 напряжения подключены блок 3 фиксации повышения напряжения ФПН и блоки 4-7 фиксации снижения напряжения ФСН, фиксирующие соответственно четыре ступени снижения напряжения, выход блока 3 ФПН под- ключей к входу первого блока 8 задержки, выход блока 4 ФСН подключен к входам второго, третьего, четвертого и пятого блоков 9-12 задержки, выход блока 5 ФСН - к входам шестого, седьмого и восьмого блоков 13-1-5 задержки, выход блока 6 ФСН - к входам блоков задержки девятого, десятого и одиннадцатого блоков 16- 18 задержки, выход блока 7 ФСН - к входу .двенадцатого блока 19 задержки.

Выходы блоков 8-19 задержки подключены: выход первого блока 8 к педвым входам первого элемента ИЛИ 20 и второго элемента ИЛИ 21 выход второго 9 к второму входу, вторго элемента ИЛИ 21, к первому входу первого элемента И 22 и к входу первого блока 23 временной памяти,выход третьего блока 10 к первому входу второго элемента И 24 и к входу второго блока 25 временной памяти, выход четвертого блока 11 к входу третьего блока -26 временной памяти, выход четвертого блока 11 к входу третьего блока 6 временной памяти, выход пятого блока 12 к четвертому блоку 27 временной памяти, выход шес

0

5

0

того блока 13 к второму входу первого элемента И 22 и к первым входам третьего, четвертого, пятого элементов И 28-30, к запрещающему входу первого блока 31 запрета и к входам пятого и шестого блоков 32 и 33 временной памяти, выход седьмого блока 14 к входам седьмого и восьмого блоков 34, 35 временной памяти, и к первому входу шестого элемента И 36, выход восьмого блока 15 к входам девятого и десятого блоков 37 и 38 временной памяти, выход девятого блока 16 к входам одиннадцатого и двенадцатого блоков 39, 40 временной памяти, к первым входам седьмого, восьмого, девятого и десятого элементов И 41-44, выход десятого блока 17 задержки к входу тринадцатого блока 45 временной памяти, выход одиннадцатого блока 18 к входам четырнадцатого и пятнадцатого блоков 46 и 47 временной памяти, выход двенадцатого блока 19 к входу шестнадцатого блока 48 временной памяти и к первому входу одиннадцатого элемента И 49, выход первого элемента ИЛИ 20 подключен к первым входам двенадцатого и тринадцатого элементов И 50 и 51, выход второго элемента ИЛИ 21 подключен к прямому входу первого блока 31 запрета, выход первого элемента И 22 подключен к входу семнадцатого блока 52 временной памяти, выход первого блока 23 временной памяти подключен к первым входам четырнадцатого и пятнадцатого элементов И 53 и 54, выход второго элемента И 24 подключен к первому входу шестнадцатого элемента И 55, выход второго блока 25 временной памяти подключен к вторым входам первого элемента ИЛИ 20 и четырнадцатого элемента И 53, выход третьего блока 26 временной памяти к входам семнадцатого и восемнадцатого элементов И 56, 57, к первым входам второго и третьего блоков 58,59 запрета и к вторым входам четвертого элемента И 29 я девятого элемента И 43, выход четвертого блока 27 временной памяти к первым входам с девятнадцатого по двадцать четвертый элементов И 60-65, выход двадцать второго элемента И 63 подключен к первому входу двадцать пятого элемента И 66, выход двадцатого элемента И 61 подключен к прямому входу четвертого блока 67 запрета выход четвертого элемента И 21 подключен через восемнадцатый блок 68 временной памяти к прямому входу пятого блока 69 запрета, выход пятого элемента И 30 подключен через девятнадцатый блок 70 временной памяти к зап- 15 69 запрета, выход пятнадцатого блока

20

25

рещающему входу шестого блока 71 запрета, выход первого блока 31 запрета подключен к первому входу двадцать шестого элемента И 72 и через двадцатый блок 73 временной памяти к первому входу третьего элемента ИЛИ 74, выход пятого блока 32 временной памя- ти подключен к запрещающему входу седьмого блока 75 запрета, выход шестого блока 33 временной памяти подключен к вторым входам пятнадцатого и восемнадцатого элементов И 54, 57 и к первому входу двадцать седьмого элемента И 76, выход седьмого блока 34 временной памяти подключен к зап.- рещающему входу второго блока 58 запрета, выход восьмого блока 35 временной памяти подключен к первому входу двадцать восьмого элемента И 77, выход десятого элемента И 44 подключен через двадцать первый блок 78 времен- ной памяти к второму входу одиннадцатого элемента И 49, выход девятого блока 37 временной памяти подключен к первому входу двадцать девятого элемента И 80.

Выход десятого блока 38 временной памяти подключен к запрещающему входу третьего блока 59 запрета, выход одиннадцатого блока 39 временной памяти подключен к запрещающему входу девятого блока 81запрета, выход двенадцатого блока 40 временной памяти подключен к вторым входам второго 24, шестого 36, двадцать второго 63 и двадцать седьмого 76 элементов И, выход седьмого элемента И 41 подключен через двадцать второй блок 82 временной памяти к запрещающему входу десятого блока 83 запрета, выход восьмого элемента И 42 подключен через двадцать третий блок 84 временной памяти к запрещающему, вхо ду одиннадцатого блока 85 запрета,

47 временной памяти подключен к первому входу тридцать второго элемента И 90, выход шестнадцатого блока 48 временной памяти подключен к запрещающему входу двенадцатого блока 91 запрета, выход одиннадцатого элемента И 49 подключен через двадцать шестой блок 92 временной памяти к входу тринадцатого блока 93 задержки и к второму входу двадцать шестого элемента И 72, выход двенадцатого элемента И 50 подключен через двадцать седьмой блок 94 временной памяти к первым входам тридцать третьего 75, 30 тридцать четвертого 96 и тридцать

пятого 9.7 элементов И, выход тринад- цатого элемента И 51 подключен к второму входу тридцатого элемента И 87 и к первым входам тридцать шестого 98 и тридцать седьмого 99 элементов И, выход семнадцатого блока 52 временной памяти подключен к второму . входу десятого элемента И 44, выход четырнадцатого элемента И 53 подключен через двадцать восьмой блок 100 временной памяти к второму входу семнадцатого элемента И 56, выход пят надцатого элемента И 54 подключен через двадцать девятый блок 101 временной памяти к вторым входам двенадцатого 50, шестнадцатого 55 и двадцать восьмого 77 элементов И, выход шестнадцатого элемента И 55 подключен к второму входу тринадцатого элемента И 51, выход семнадцатого элемента И 56 подключен через тридцатый блок 102 временной памяти к второму входу девятнадцатого элемента И 60.

Выход восемнадцатого элемента И 57 подключен через тридцать первый блок 103 временной памяти к прямому входу восьмого блока 79 запрета и второму входу тридцать пятого элемен40

45

50

55

выход девятого элемента И 43 подключен через двадцать четвертый блок 86 временной памяти к первому входу тридцатого элемента И 87, выход третьего элемента И 28 через двадцать пятый блок 88 временной памяти к запрещающему входу четвертого блока 67 запрета, выход тринадцатого блока 45 временной памяти подключен к первому входу тридцать первого элемента И 89, выход четырнадцатого блока 46 временной памяти подключен к запрещающему входу пятого блока

0

5

47 временной памяти подключен к первому входу тридцать второго элемента И 90, выход шестнадцатого блока 48 временной памяти подключен к запрещающему входу двенадцатого блока 91 запрета, выход одиннадцатого элемента И 49 подключен через двадцать шестой блок 92 временной памяти к входу тринадцатого блока 93 задержки и к второму входу двадцать шестого элемента И 72, выход двенадцатого элемента И 50 подключен через двадцать седьмой блок 94 временной памяти к первым входам тридцать третьего 75, 0 тридцать четвертого 96 и тридцать

пятого 9.7 элементов И, выход тринад- цатого элемента И 51 подключен к втоf рому входу тридцатого элемента И 87 и к первым входам тридцать шестого 98 и тридцать седьмого 99 элементов И, выход семнадцатого блока 52 временной памяти подключен к второму . входу десятого элемента И 44, выход четырнадцатого элемента И 53 подключен через двадцать восьмой блок 100 временной памяти к второму входу семнадцатого элемента И 56, выход пятнадцатого элемента И 54 подключен через двадцать девятый блок 101 временной памяти к вторым входам двенадцатого 50, шестнадцатого 55 и двадцать восьмого 77 элементов И, выход шестнадцатого элемента И 55 подключен к второму входу тринадцатого элемента И 51, выход семнадцатого элемента И 56 подключен через тридцатый блок 102 временной памяти к второму входу девятнадцатого элемента И 60.

Выход восемнадцатого элемента И 57 подключен через тридцать первый блок 103 временной памяти к прямому входу восьмого блока 79 запрета и второму входу тридцать пятого элемен0

5

0

5

та И 97, выход второго и третьего блоков 58,59 запрета подключены соответственно к вторым входам тридцать третьего и тридцать шестого элемен- тов И 95, 98, выход девятнадцатого элемента И 60 подключен к прямому входу седьмого блока 75 запрета, выходы д в енад цат or о и двадцать первого элементов И 61 и 62 подключены соот

ветственно к прямым входам четвертого и десятого блоков 67, 83 запрета, выходы двадцать третьего и двадцать четвертого элементов И 64, 65 подключены соответственно к прямым входам шестого и одиннадцатого блоков 71,85 запрета, выход восемнадцатого блока 68 временной памяти подключен к прямому входу пятого блока 69 запрета, выход которого подключен к вто- рому входу тридцать седьмого элемента И 99, выход двадцать шестого элемента И 72 подключен через тридцать второй блок 104 вдеменной памяти к второму входу третьего элемента ИЛИ 74, выход которого подключен к запрещающему входу тринадцатого блока 105 запрета, двадцать седьмого и двадцать восьмого элементов И 76, 77, а также

через тридцать третий и тридцать чет- эд мени, обусловленного уставкой блока

35

40

вертый блоки 106, 107 временной памяти к второму входу соответственно тридцать четвертого и тридцать девятого элементов И 89, выход восьмого блока 79 запрета подключен к второму входу тридцать четвертого И 96, выход двадцать девятого элемента И 80 подключен к прямому входу девятого блока 81 запрета, выход тридцать первого элемента И 80 подключен к прямому входу девятого блока запрета, выход тридцать первого элемента И 89 подключен через тридцать пятый блок 109 временной памяти к второму входу тридцать второго И 90, выход которого подключен к прямому входу двенадцатого блока 91 запрета, тринадцатый блок 95 задержки подключен к прямому входу тринадцатого блока

105 запрета. I

Выход тридцать третьего элемента

И 95 подключен через тридцать шестой блок 109 временной памяти к вторым входам третьего и двадцатого элементов И 28 и 61, выход тридцать четвертого элемента И 96 подключен через тридцать седьмой блок 110 временной памяти к второму входу седьмого и двадцать первого элементов И 41

45

50

10 задержки, напряжение не увеличилось, то по цепи блок ФСН4 - блок 10 задержки - блок 25 временной памяти - элемент И 53 на второй вход последнего также поступает сигнал, В результате этого сигнал с элемента И 53 через блок 100 временной памяти поступает на первый вход элемента И 56. Если увеличения напряжения по-прежнему не происходит, то через блоки задержки 11 и временной памяти 26 поступает сигнал на второй вход элемента И 56 и далее с последнего через блок 102 временной памяти сигнал поступает на первый вход элемента И 60, на второй вход которого поступает сигнал с блока ФСН 4 через блоки задержки 12 и временной памяти 27, если блок ФСН 4 остался в сработанном состоянии. С элемента И 60 сигнал .через блок 75 запрета проходит на отключение нагрузки, если за это время не произошло дальнейшее снижение напряжения. В случае снижения напряжения до уставки сраба тывания второй ступени органа снижения напряжения блока 5 ФСН по цепи блок 5 ФСН - блок 13 задержки - блок 32 временной памяти - блок 75 запре

15

- JQ а 25е6369238

и 62, выход тридцать шестого элемента И 9 7 подключен через тридцать восьмой блок 111 временной

памяти к второму входу двадцать

пятого элемента И 66, выход тридцать шестого элемента И 98 подключен к вторым входам пятого и двадцать третьего элемента И 30 и 64, выход

Ю тридцать седьмого элемента И 99

подключен к вторым входам восьмого и двадцать четвертого элементов И 42 и 65, выход элемента И 36 через тридцать девятый блок 42 временной памяти подключен к запрещающему входу восьмого блока 79 защиты, с выходов блоков 67, 71, 75,81,83,85,91, 105 запрета и элементов И 87,66 посыпаются команды на отключение нагрузки.

Устройство работает следующим образомс

При снижении напряжения на ПС до установки срабатывания органа снижения напряжения первой ступени срабатывает блок ФСН 4 и посылает сигнал через блоки задержки 9 и временной памяти 23 на первый вход элемента И 53. Если по истечении вре5

0

5

0

10 задержки, напряжение не увеличилось, то по цепи блок ФСН4 - блок 10 задержки - блок 25 временной памяти - элемент И 53 на второй вход последнего также поступает сигнал, В результате этого сигнал с элемента И 53 через блок 100 временной памяти поступает на первый вход элемента И 56. Если увеличения напряжения по-прежнему не происходит, то через блоки задержки 11 и временной памяти 26 поступает сигнал на второй вход элемента И 56 и далее с последнего через блок 102 временной памяти сигнал поступает на первый вход элемента И 60, на второй вход которого поступает сигнал с блока ФСН 4 через блоки задержки 12 и временной памяти 27, если блок ФСН 4 остался в сработанном состоянии. С элемента И 60 сигнал .через блок 75 запрета проходит на отключение нагрузки, если за это время не произошло дальнейшее снижение напряжения. В случае снижения напряжения до уставки срабатывания второй ступени органа снижения напряжения блока 5 ФСН по цепи блок 5 ФСН - блок 13 задержки - блок 32 временной памяти - блок 75 запре

та на последний поступает запрещающий сигнал, что препятствует прохождению команды из отключения нагрузки Таким образом, данными цепями фор- . мируется команда на отключение нагрузки при зависании напряжения на уровне уставки срабатывания блока 4 ФСН.

Аналогично схема устройства работает при зависании напряжения на уровне уставки срабатывания органа снижения напряжения второй ступени (при срабатывании ФСК 5) и при зависании напряжения на уровне уставки - срабатывания органа снижения напряжения третьей ступени (при срабатывании ФСН 6). При этом сигнал проходит через блоки ФСН 4, задержки 9, временной памяти 23, ФСК 5, задержки 13, временной памяти 33, И 54, временной памяти 101, задержки 14, временной памяти 35, И 77, временной памяти 107, задержки -15, временной памяти 37, И 80, запрета 81, ФСН 6, задержки 16, временной памяти 39 (при зависании напряжения на уровне уставки срабатывания ФСН 5) и через блоки ФСН 5, задержки 13 временной памяти 33, ФСИ 6, задержки 16, вре-1 менной памяти 40, И 76, временной памяти 106, задержки 17, временной памяти 45, И 89, временной памяти 109, задержки 18, временной памяти 47, И 90, запрета 91, ФСН 7, задержки 1 временной памяти 48 (при зависании напряжения на уровне уставки срабатывания ФСН 6). i

Если при снижении напряжения на ПС до-уставки срабатывания блока 4 ФСН и в последующем до уставки срабатывания блока 5 ФСН, а потом при локализации поврежденного участка сети либо при выполнений каких-либо управляющих воздействий от ПА, напряжение увеличивается до уровня устаки срабатывания блока 4 ФСН или даже до допустимой величины, срабатывает блок ФПН 3, а затем напряжение постепенно сползает и зависает на уровне уставки срабатывания блока 4 ФСН. С блока 4 ЬСН через блоки задержки 9 и временной памяти 23 сигнал поступает на первый вход элемента И 54, на второй вход которого через блоки задержки и временной памяти 33 поступает сигнал с блока 5 ФСН

с элемента И 54, на второй вход которого через блоки задержки 13 и вре

10

15

20

25

- 30 ,

3692310

менной памяти 33 поступает сигнал с блока 5 ФСН,с элемента И 54 сигнал че- ч рез блок 101 задержки поступает на. первый вход элемента И 50, на второй вход которого поступает спустя некоторое время через блоки задержки 10 и временной памяти 25 сигнал с блока 4 ФСН, через блок 8 задержки сигнал с блока 3 ФПН предварительно пройдя через элемент ИЛИ 20 и элемент И 50, поступает через блок 94 временной памяти на первый вход элемента И 95, на второй вход которого черев блоки задержки 11, временной памяти 26 и запрета 58 поступает сигнал с блока 4 ФСН, с элемента И 95 сигнал через блок 100 временной памяти поступает на входы элементов И 28, 61, на второй вход элемента И 28 поступает сигнал с блоков задержки 12 и временной памяти 27, с выхода элемента И 61 сигнал через блок 67 запрета проходит на отключение нагрузки, если при этом на второй вход последнего не поступал через . блок 88 временной памяти запрещающий сигнал с элемента И 28.

Аналогичным образом схема устройства работает и при более глубоких первичных посадках напряжения с более низким нависанием напряжения. При этом схемой устройства предусмотрена фиксация еще пяти ситуаций снижения напряжения.

Ситуация первая о Первичное снижение напряжения до уставки срабатывания блока 5 ФСН с последующим увеличением напряжения и с дальнейшим вторичным снижением напряжения с зависанием на уровне уставки срабатывания блока 5 ФСНо В этом случае сигнал проходит через блоки ФСН 4, задержки 9, временной памяти 23, ФСН 5, задержки 13, временной памяти 33, И 54, временной памяти 101, задержки 10 и временной памяти 25 или ФПН 3, задержки 8, ПЛИ 20, И 50, временной памяти 94, задержки 11, временной памяти 26, И 57, временной памяти 103, запрета 79 (если на него не пвс- тупал запрещающий сигнал от ФСН 5 и ФСН 6 через блоки задержки 14 и 16, временной памяти 40, И 86, временной памяти 112), И 96, временной памяти 110, задержки 12, временной памяти 27, И 62, запрета 83 на отключение нагрузки (если на второй вход блока запрета не поступал запрещающий сиг35

40

15

50

55

15

11

нал с блока ФСН 6 через блоки задержки 16, временной памяти 82).

Ситуация вторая. Первичное снижение напряжения до уставки срабатыва- j ния блока ФСН 5 с последующим увеличением напряжения и с дальнейшим вторичным снижением напряжения до сколь угодно низкой величины. В этом случае сигнал проходит через бло-10 ки ФСН 4, задержки 9, временной памяти 23, ФСН 5, задержки 13, временной памяти 33, И 54, временной памяти 101, задержки 10 и временной памяти 25 или ФПНЗ и задержки 8, ИЛИ 20, И 50, временной памяти 94, задержки 11, временной памяти 26,, И 57, временной памяти 103, И 97, временной памяти 111, задержки 12, временной памяти 27, задержки 16, временной памяти 40, И 63, И 66 на отключение нагрузки.

Ситуация третья о Первичное снижение напряжения до уставки срабатывания блока 6 ФСН с последующим увели- чением напряжения и с дальнейшим вторичным снижением напряжения с зависанием на уровне уставки срабатыва- ния блока 4 ФСН. В этом случае сигнал проходит через блоки ФСН 4, задержки 9, временной памяти 23, ФСН 5, задержки 13, временной памяти 33, И 54, временной памяти 101, задержки 10, ФСН 6, задержки 16, временной памяти 40, И 24, И 55, времен- 35 ной памяти 25 или ФПН 3 и задержки 8, ИЛИ 20, И 51, задержки 11, временной памяти 26, запрета 59 (если на второй вход блока запрета не поступал запрещающий сигнал с блока ФСН 5, через блоки задержки 15 и временной памяти 38), И 98, задержки 12, временной па- мяти 27, И 64, запрета 71 на отключение нагрузки (если на второй вход блока запрета не поступал запрещаю- пщй сигнал с блока ФСН 5 через блоки задержки 13, И 30, временной памяти . 70).

163692312 ки 10, ФСН 6, задержки 16, временной памяти 40, И 24, И 55, временной памяти 25 или ФПН 3, задержки 8, ИЛИ 20, И 51, задержки 11, временной памяти 26, И 29, временной памяти 68, запрета 69 (если на второй вход бло- ка запрета не поступал запрещающий сигнал с блока ФСН 6 через блоки задержки 18 и временной памяти 46), . И 99, задержки 12, временной памяти 27, И 65, запрета 85 на отключение нагрузки (если на второй вход блока запрета не поступал запрещающий сигнал с блока ФСН 6 через блоки задержки 16, И 42 и временной памяти 84) „

Ситуация пятая о Первичное снижение напряжения до уставки срабатывания блока 6 ФСН с последующим увеличением напряжения и с дальнейшим вторичным снижением напряжения до сколь угодно низкой величины. В этом случае сигнал проходит через блоки ФСН 4, задержки 9, временной памяти 23, ФСН 5, задержки 13, временной памяти 33, И 54, временной памяти 101, задержки 10, ФСН 6, задержки 16, временной памяти 40, И 24, И 55, временной памяти 25 или ФПН 3, задержки 8, ИЛИ 20, И 51, задержки 11, временной памяти 26, задержки 16, И 43, временной памяти 86, И 87 на отключение нагрузки.

При снижении напряжения на ПС до уставки срабатывания блока 7 ФСН происходит отключение нагрузки вследствие прохождения сигнала через блоки ФСН 4, задержки 9, ФСН 5, задержки 13, И 22, временной памяти 52, ФСН 6, задержки 16, И 44, временной памяти 8, ФСН 7, задержки 19, И 49, временной памяти 92, задержки 93 и запрета 105 о При этом присутствовавший в нормальном режиме на втором входе блока 105 запрета запрещающий сигнал о т блока 3 ФПН,проходящий к блоку 105 запрета через блоки ИЛИ 21, запрета 31, временной памяти 73, ИЛИ 74, снимае;ся

20

25

30

40

45

Ситуация четвертая. Первичное снижение напряжения до уставки срабатыва-50 в виде поступления на блок 31 запре- та от блока 5 ФСН через блок 13 задержки запрещающего сигнала (время запоминания появившегося сигнала блония блока 6 ФСН с последующим увеличением напряжения и с дальнейшим вто-, ричным снижением напряжения с зависанием на уровне уставки срабатывания блока 5 ФСН, в этом случае сигнал-, проходит через блоки ФСН 4, задержки 9, временной памяти 23, ФСН 5, задержки 13, временной памяти 33, И 54, временной памяти 101, задерж55

ком 73 запоминания меньше выдержки времени блока 93 задержки).. Если-до момента отработки выдержки времени блока 93 задержки напряжение повысится до уставки срабатывания блока ФСН 4 или ФПН 3, то в последних че

ком 73 запоминания меньше выдержки времени блока 93 задержки).. Если-до момента отработки выдержки времени блока 93 задержки напряжение повысится до уставки срабатывания блока ФСН 4 или ФПН 3, то в последних через блоки задержки 9 или 8, ИЛИ 21, запрета 31, И 72 (на втором входе блока уже дежурит сигнал с блока 92 временной памяти), временной памяти 104 или 74 на блок 105 запрета поступает запрещающий сигнал. При этом время запоминания появившегося сигнала блоком 104 запоминания больше суммарной ввдержки времени блоков

запоминания 92 и задержки 93„

Для правильного функционирования схемы устройства вьщержки времени задержки должны выбираться из условия 13 1Т 14 Т 15, Т 16 Т 18. Кроме того, должны соблюдаться условия Т 93, Т 32(Т 12 + Т 27), Т 66 (Т 12 + Т 27), Т 39 (Т 15 + + Т 37), Т 82(Т 12 + Т 27), Т 70; XX 12 + Т 27), Т 48(Т 18 + Т 47), Т 84 (Т 12 + Т 27).

Предлагаемое устройство автоматики ограничения снижения напряжения вследствие более гибкой логики устройства и большего быстродействия поволяет повысить надежность и устойчивость ЭС за счет более точной дозировки управляющих воздействий при различных аварийных ситуациях в ЭС - и большего быстродействия работы автоматики.,

Формула изобретения

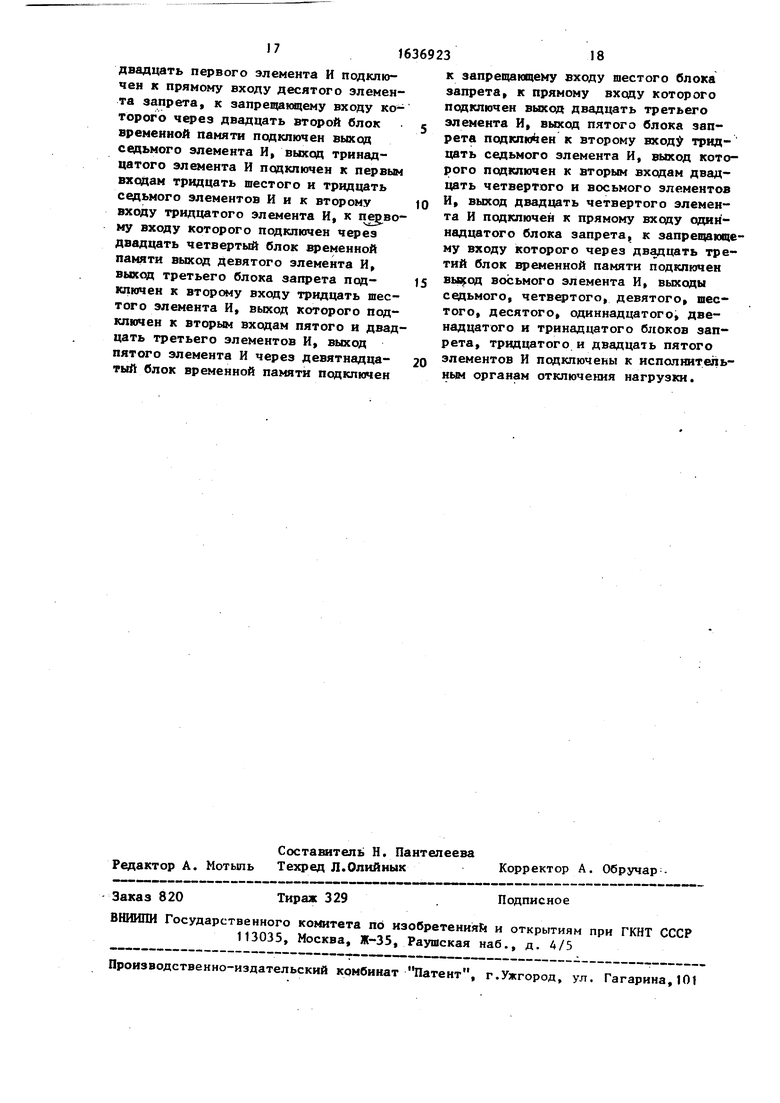

Устройство автоматического отключения нагрузки энергосистемы при снижении напряжения, содержащее измерительный преобразователь напряжения, установленный на шинах подстанции, блок фиксации снижения напряжения (ФСН), блок фиксации повышения напряжения (ФПН), входы которых подключены к выходу измерительного преобразователя напряжения, отличающееся тем, что, с целью повышения надежности и устойчивости работы энергосистем за счет предотвращения излишнего отключения нагрузки, в него дополнительно введены три блока ФСН, тринадцать блоков задержки, тридцать девять блоков временной памяти, тридцать семь элементов К, три элемента ИЛИ, тринадцать блоков запрета, причем выход блока ФПН подключен к первому блоку зацержки, выход первого блока ФСН - к второму, третьему, четвертому и пятому блокам задержки, выход второго блока ФСН - к шестому, седьмому и восьмому бло-

с

s

0

0

5

5

0

5

0

5

кам задержки, выход третьего блока ФСН - к девятому, десятому и одиннадцатому блокам задержки, выход четвертого блока ФСН - к двенадцатому блоку задержки, выход первого блока задержки подключен к первым входам первого и второго элементов ИЛИ, выход второго блока задержки подключен к первому входу первого элемента И, к второму входу второго элемента ИЛИ и через первый блок временной памяти, к первым входам четырнадцатого и пятнадцатого элементов И, выход четырнадцатого элемента И через двадцать восьмой блок временной памяти подключен к второму входу семнадцатого элемента И, выход третьего блока задержки подключен к первому входу второго элемента И и через второй блок временной памяти к второму входу четырнадцатого элемента И и к второму входу первого элемента ИЛИ, выход которого подключен к первым входам двенадцатого и тринадцатого элементов И, выход четвертого блока задержки через третий блок временной памяти подключен к первым входам семнадцатого и восемнадцатого элементов И, к вторым входам четвертого и девятого элементов И, к прямым входам второго и третьего блоков запрета, выход пятого блока задержки через четвертый блок временной памяти подключен к первым входам девятнадцатого, .двадцатого, двадцать первого, двадцать второго, двадцать третьего и двадцать четвертого элементов И, выход шестого блока задержки подключен к второму входу первого элемента И, к запрещающему входу первого блока запрета, к первым входам третьего, четвертого и пятого элементов И, через шестой блок временной памяти к вторым входам пятнадцатого и восемнадцатого элементов И, к первому входу двадцать седьмого элемента И, через пятый блок временной памяти к запрещающему входу седьмого блока запрета, прямой вход которого подключен к выходу девятнадцатого элемента И, второй вход которого через тридцатый блок временной памяти подключен к выходу семнадцатого элемента И, выход седьмого блока задержки подключен к первому входу шестого элемента И, через восьмой блок временной памяти - к первому входу двадцать восьмого элемента И, через седьмой

блок временной памяти - к запрещающему входу второго блока запрета, выход которого подключен к первым входам тридцать четвертого и тридцать пято- го элементов И, к второму входу, тридцать третьего элемента И, первый вход KOToporoj подключен к выходу двенадцатого элемента И через двадцать седьмой блок временной памяти, а выход через тридцать шестой блок временной памяти - к второму входу двадцатого элемента И, выход которого подключен к прямому входу четвертого блока запрета, к запрещающему входу которого через двадцать пятый блок временной памяти подключен выход третьего элемента И, к второму входу которого подключен выход тридцать шестого блока временной памяти, выход восьмого бло- ка задержки через десятый блок временной памяти подключен к запрещающему входу третьего элемента запрета и через девятый блок временной памяти подключен к первому входу двадцать девятого элемента И, к второму входу которого через тридцать четвертый блок временной памяти подключен выход двадцать восьмого элемента И, второй вход которого через двадцать девятый блок временной памяти подключен к выходу пятнадцатого элемен-. та И, второй вход двадцать восьмого элемента И подключен к второму входу двенадцатого элемента И и к второму входу шестнадцатого элемента И, первый вход которого подключен к выходу второго элемента И, а выход - к вто- . рому входу тринадцатого элемента И, выход девятого блока задержки под- ключей к первым входам седьмого, восьмого, девятого, десятого элементов И, через одиннадцатый блок временной памяти - к запрещающему входу девятого блока запрета и через две- надцатый блок временной памяти - к вторым входам двадцать седьмого, второго, двадцать второго и шестого элементов И, выход десятого блока задержки через тринадцатьй блок времен- ной памяти подключен к первому входу тридцать первого элемента И, к второму входу которого через тридцать третий блок временной памяти подключен выход двадцать седьмого элемента И, выход одиннадцатого блока задерж- ки через четырнадцатый блок временной памяти подключен к запрещающему входу пятого блока запрета, к прямому входу которого через восемнадцатый блок временной памяти подключен выход четвертого блока И, через пятнадцатый блок временной памяти - к первому входу тридцать второго элемента И, второй вход которого подключен через тридцать пятый блок временной памяти к выходу тридцать первого элемента И, а выход - к прямму входу двенадцатого блока запрета, выход двенадцатого блока задержки подключен через шестнадцатый блок врменной памяти к запрещающему входу двенадцатого блока запрета, к первому входу одиннадцатого элемента И, к второму входу которого через двадцать первый блок временной памяти подключен выход десятого элемента И, второй вход которого через семнадцатый блок временной памятиподключен к выходу первого элемента И, выход второго элемента ИЛИ подключен к прямому входу первого блока запрета, выход которого через двадцатый блок временной памяти подключен к второму входу третьего элемента ИЛИ и к первому входу двадцать шестого элемента И, выход которого через тридцать второй блок временной памяти подключен к первому входу третьего элемента ИЛИ, выход которого подключен к запрещающему входу тринадцатого блока запрета, выход одиннадцатого элемента И через двадцать шестой блок временной памяти подключён к второму входу двадцать шестого элемента И и через тринадцатый блок задержки - к прямому входу тринадцатого блока запрета, выход восемнадцатого элемента И через тридцать первый блок временной памяти подключен

к прямому входу восьмого блока запрета и к второму входу тридцать пятого элемента И, выход которого через тридцать восьмой блок временной памяти подключен к второму входу двадцать пятого элемента И, к первому входу которого подключен выход двадцать второго элемента И, выход шестого элемента И через тридцать девятый блок временной памяти подключен к запрещающему входу восьмого блока запрета, выход которого подключен к второму входу тридцать четвертого элемента И, выход которого через тридцать седьмой блок временной памяти подключен к вторым входам двадцать первого и седьмого элемента И, выход

17

двадцать первого элемента И подключен к прямому входу десятого элемента запрета, к запрещающему входу которого через двадцать второй блок временной памяти подключен выход седьмого элемента И, выход тринадцатого элемента И подключен к первым входам тридцать шестого и тридцать седьмого элементов И и к второму входу тридцатого элемента И, к первому входу которого подключен через двадцать четвертый блок временной памяти выход девятого элемента И, выход третьего блока запрета подключен к второму входу тридцать шестого элемента И, выход которого подключен к вторым входам пятого и двадцать третьего элементов И, выход пятого элемента И через девятнадцатый блок временной памяти подключен

10

63692318

к запрещающему входу шестого блока запрета к прямому входу которого подключен выход двадцать третьего элемента И, выход пятого блока запрета подключен к второму входу тридцать седьмого элемента И, выход которого подключен к вторым входам двадцать четвертого и восьмого элементов И, выход двадцать четвертого элемента И подключен к прямому входу одиннадцатого блока запрета, к запрещающему входу которого через двадцать третий блок временной памяти подключен выход восьмого элемента И, выходы седьмого, четвертого, девятого, шестого, десятого, одиннадцатого, двенадцатого и тринадцатого блоков запрета, тридцатого и двадцать пятого элементов И подключены к исполнительным органам отключения нагрузки.

15

20

| Устройство для разгрузки района электрической сети | 1976 |

|

SU656152A1 |

| Ручная тележка для реклам | 1923 |

|

SU407A1 |

| Устройство для увязки погруженного на платформу сена | 1927 |

|

SU11264A1 |

| Уральское отделение Энергосетьпроект, 1983. | |||

Авторы

Даты

1991-03-23—Публикация

1988-05-30—Подача