Изобретение относится к электроизмерительной технике и предназначено для допускового контроля сопротивления различных целей в контрольно- измерительной аппаратуре.

Целью изобретения являе ся повышение достоверности Функционирования устройства.

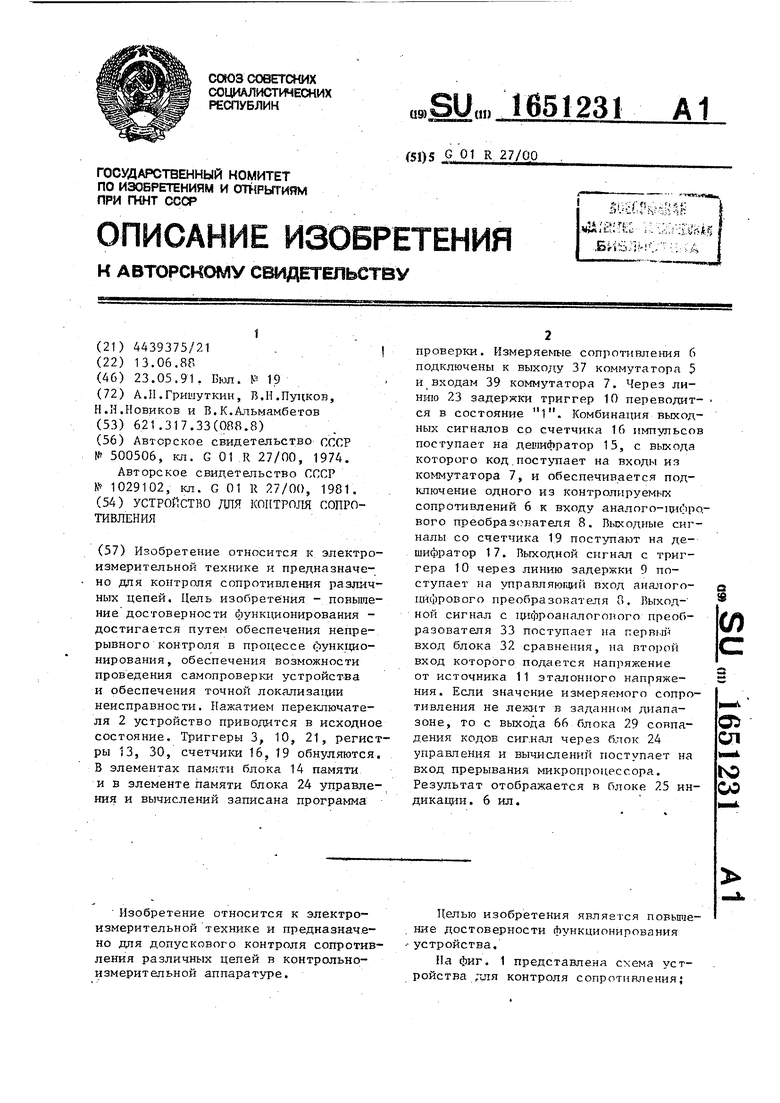

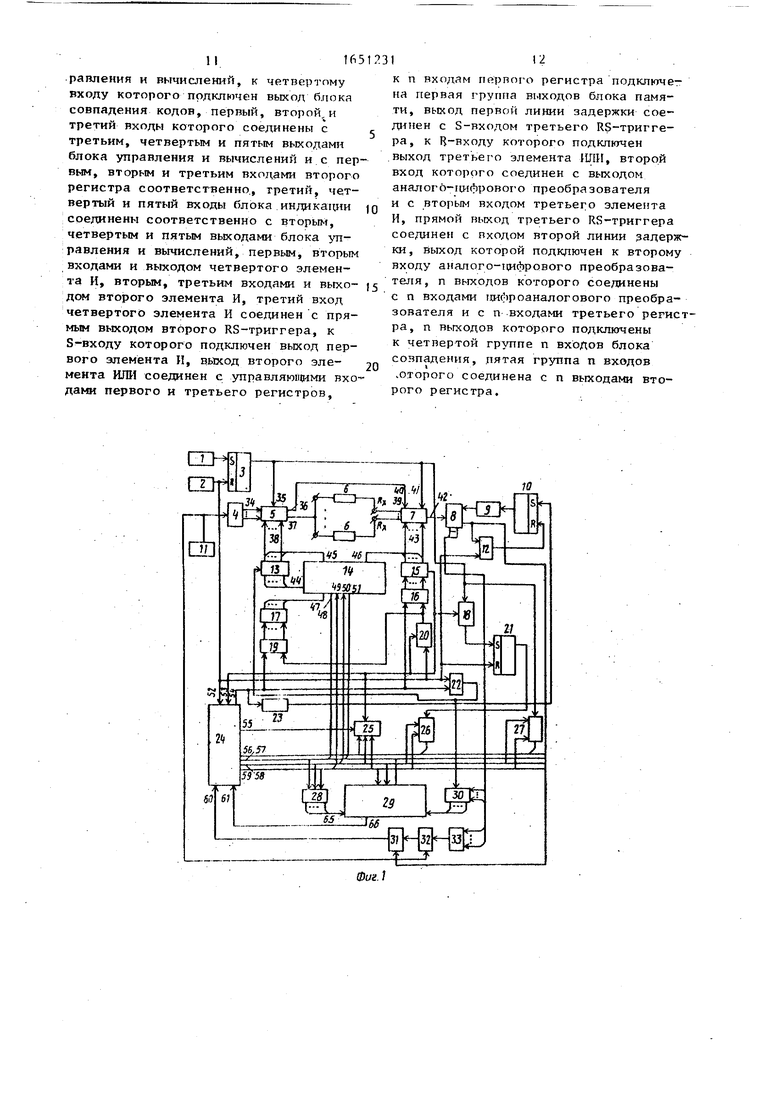

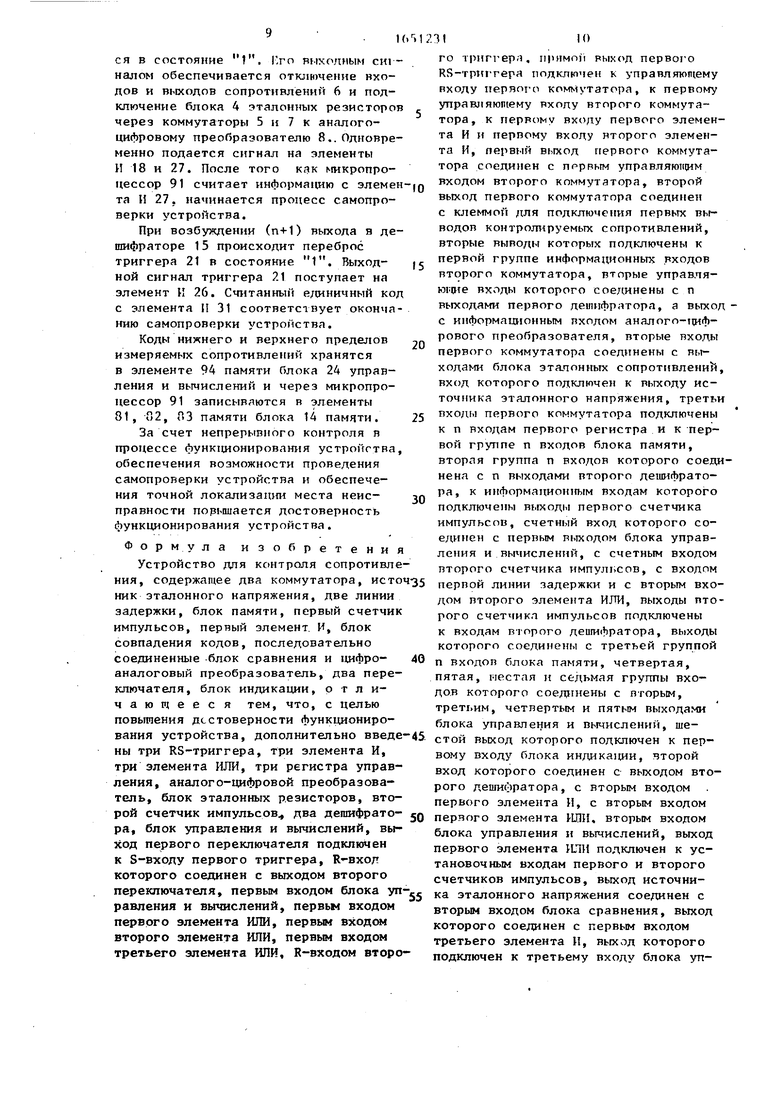

На фиг. 1 представлена схема устройства для контроля сопротивления;

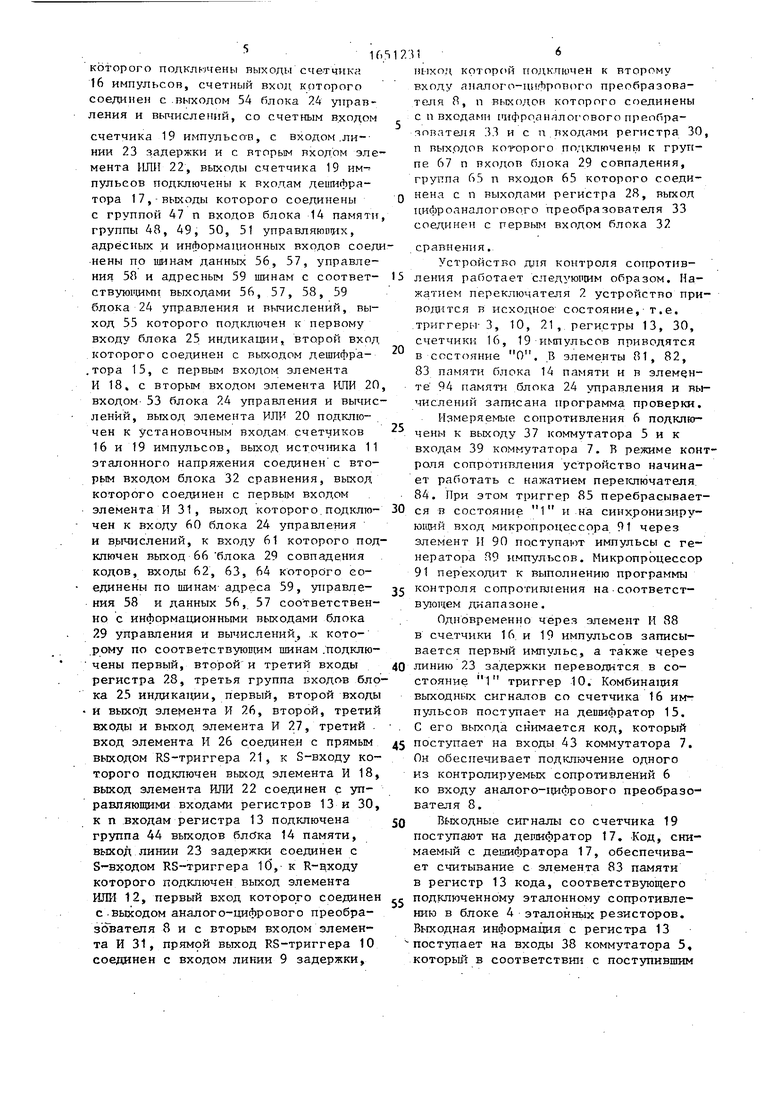

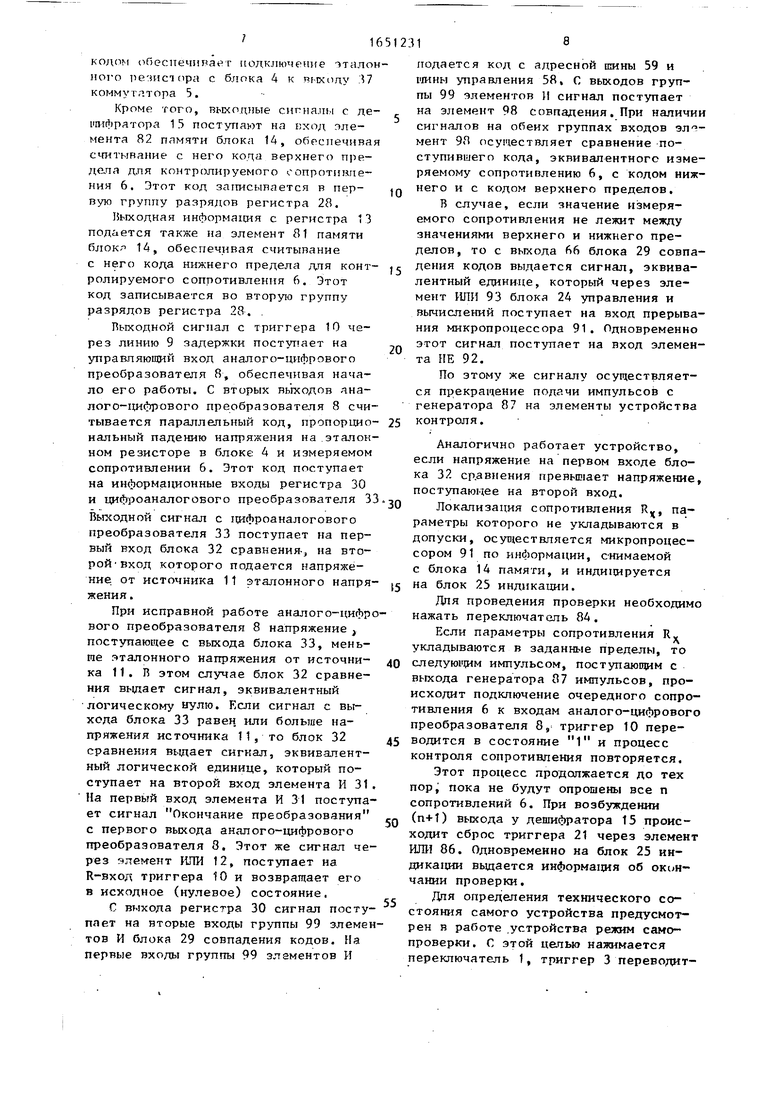

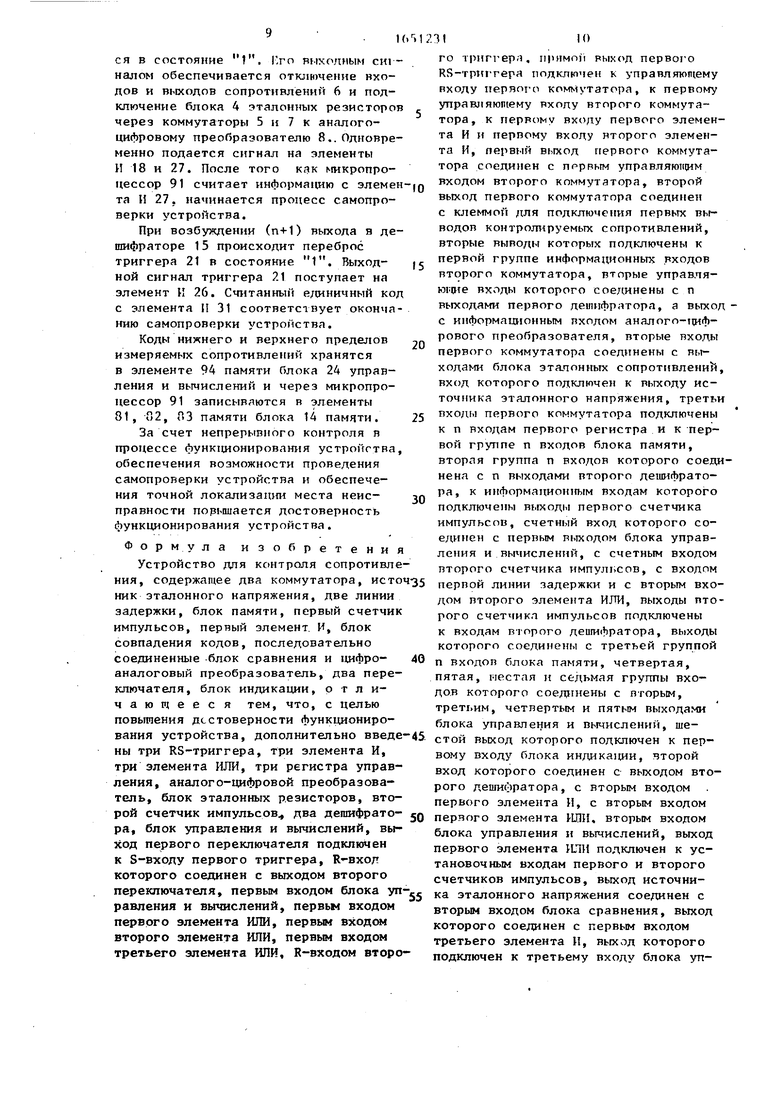

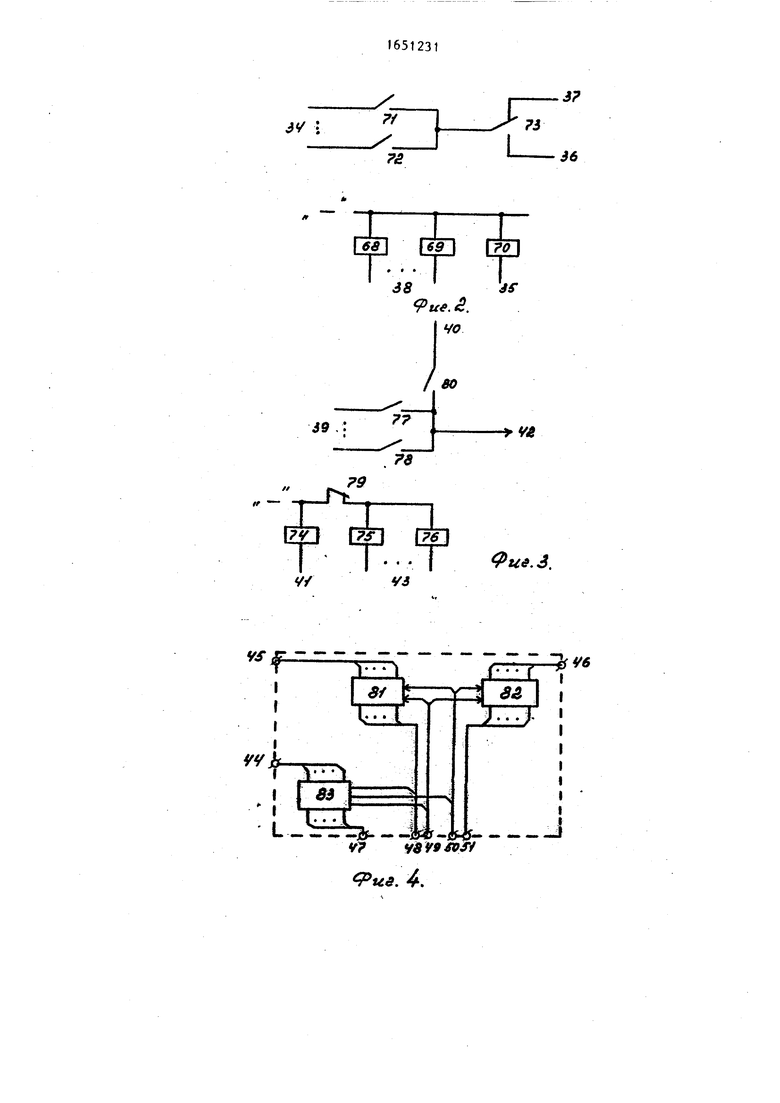

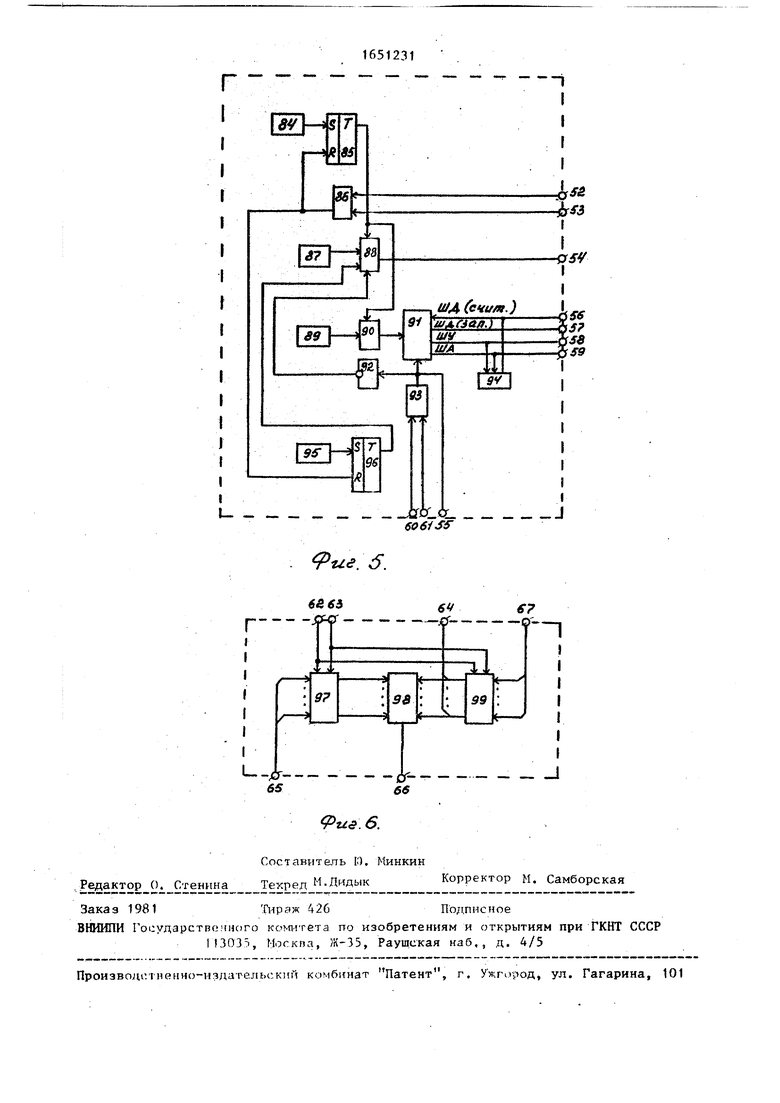

на фиг. 2 - схема первого коммутатора; на фиг. 3 - схема второго коммутатора; на фиг. 4 - схема блока памяти; на фиг. 5 - схема блока уп- 5 равления и вычислений; на фиг. 6 - схема блока совпадения кодов.

Устройство для контроля сопротивления содержит переключатель 1, переключатель 2, RS-триггер З, блок 4 10 эталонных резисторов, первый коммутатор 5, п объектов контроля 6, второй коммутатор 7, аналого-цифровой преобразователь 8, линию 9 задержки, RS-триггер 10, источник 11 эталонного 15 напряжения, элемент ИЛИ 12, регистр 13, блок 14 памяти, дешифратор 15, счетчик 16 импульсов, дешифратор 17, элемент И 18, счетчик 19 импульсов, элемент ИЛИ 20, RS-триггер 21, элементно ИЛИ 22, линию 23 задержки, блок 24 управления и вычислений, блок 25 индикации, элемент И 26, элемент и 27. регистр 28, блок 29 совпадения кодов, регистр 30, элемент И 31, блок 3225

сравнения, цифроаналоговый преобразователь 33, входы 34 коммутатора 5, вход 35 коммутатора 5, выход 36 коммутатора 5, выход 37 коммутатора 5 управляющие входы 38 коммутатора 5,30

входы 39 коммутатора 7, вход 40 коммутатора 7, вход 41 коммутатора 7. выход 42 коммутатора 7, управляющие входы 43 коммутатора 7, группу 44 п выходов блока 14 памяти, группу 45 п входов блока 14 памяти, группу 46 входов блока 14 памяти, группу 47 входов блока 14 памяти, группу 48 информационных входов блока 14 памяти, группу 49 адресных входов блока 14 па-. мяти, группу 50 управляющих входов блока 14 памяти, восьмую группу информационных входов 51 блока памяти 14, вход 52 блока 24 управления и вычислений, вход 53 блока 24 управления, 45 выход 54 блока,24 управления, выход 55 блока 24 управления, шину 56 данных на считывание, шину 57 данных на запись, шину 58 управления, адресную шину 59, вход 60 блока 24 управления, вход 61 блока 24 управления, адресный вход 62 блока 29 совпадения кодов, управляющий вход 63 -блока 29 совпадения, информационный вход 64 блока 29 совпадения, группу 65 входов блока 29 совпадения, выход 66 блока 29 совпадения, группу входов 67 блока 29 совпадения.

Коммутатор 5 (фиг. 2) содержит реле 6П, реле 69, реле 70, замыкающий1651231

ся контакт 71 реле 68, замыкакллийся контакт 72 реле 69, переключаюыийся контакт 73 реле 70.

Коммутатор 7 (фиг. 3) содержит реле 74, реле 75, реле 76, замыкающийся контакт 77 реле 72, замыкаюшийся контакт 78 реле 76, размыкающийся контакт 79 реле 74, замыкающийся контакт 80 реле 74.

Блок 14 памяти (фиг. 4) содержит элемент 81 памяти, элемент 82 памяти, элемент 83 памяти.

Блок 24 управления и вычислений (фиг. 5) содержит переключатель 84, RS-триггер 85, элемент ИДИ 86, генератор 87 импульсов, элемент И 88, генератор 89 импульсов, элемент И 90, микропроцессор 91, элемент НЕ 92, элемент ИЛИ 93, элемент 94 памяти, переключатель 95, RS-триггер 96, мины данных на считывание 56 и на заись 57, шину 58 управления и адресную шину 59.

Блок 29 совпадения кодов (фиг. 6) содержит группу 97 элементов И, элемент 98 совпадения и группу 99 элементов И.

Выход переключателя 1 подключен к S-входу триггера 3, R-вход которого соединен с выходом переключателя 2, входом 52 блока 24 управления и вычислений, первым входом элемента ИЛИ 20, первым входом элемента ИЛИ 22, вторым входом элемента ИЛИ 12, R-вхо- дом триггера 21, прямой выход триггера 3 подключен к управляющему входу 35 коммутатора 5, к управляющему входу 41 коммутатора 7, к второму входу элемента И 18 и к первому входу элемента И 27. выход 36 коммутатора 5 соединен с управляющим входом 40 коммутатора 7, выход 37 через объект контроля (контролируемые сопротивления) 6 подключен к группе 39 информационных входов коммутатора 7, управляющие входы 43 которого соедине- i ны с п выходами дешифратора 15, а выход 42 - с информационным входом аналого-цифрового преобразователя 8, входы 34 коммутатора 5 соединены с выходами блока 4 эталонных сопротивлений, вход которого подключен к выходу источника il эталонного напряжения, входы 38 коммутатора 5 подключены к п выходам регистра 13, которые соединены с группой 45 п входов блока .14 памяти, группа 46 п входов которого соединена с п выходами ле- шифратора 15. к информационным входам

оторого подключены выходы счетчика 16 импульсов, счетный вход которого оединен с выходом 54 блока 24 управения и вычислений, со счетным входом

счетчика 19 импульсов, с входом линии 23 задержки и с вторым входом элемента ИЛИ 22, выходы счетчика 19 импульсов подключены к входам дешифратора 17, выходы которого соединены с группой 47 п входов блока 14 памяти, группы 48, 49, 50, 51 управляющих, адресных и информационных входов соединены по шинам данных 56, 57, управления 58 и адресным 59 шинам с соответствующими выходами 56, 57, 58, 59 блока 24 управления и вычислений, выход 55 которого подключен к первому входу блока 25 индикации, второй вход которого соединен с выходом дешифратора 15, с первым входом элемента И 18, с вторым входом элемента ИЛИ 20, входом 53 блока 24 управления и вычислений, выход элемента ИЛИ 20 подключен к установочным входам счетчиков 16 и 19 импульсов, выход источника 11 эталонного напряжения соединен с вторым входом блока 32 сравнения, выход которого соединен с первым входом элемента И 31, выход которого подключен к входу 60 блока 24 управления и вычислений, к входу 61 которого подключен выход 66 блока 29 совпадения кодов, входы 62, 63, 64 которого соединены по шинам адреса 59, управления 58 и данных 56, 57 соответственно с информационными выходами блока 29 управления и вычислений, к которому по соответствующим шинам .подключены первый, второй и третий входы регистра 28, третья группа входов блока 25 индикации, первый, второй входы

и выход элемента И 26, второй, третий входы и выход элемента И 27, третий вход элемента И 26 соединен с прямым выходом RS-триггера 21, к S-входу которого подключен выход элемента И 18, выход элемента ИЛИ 22 соединен с управляющими входами регистров 13 и 30, к п входам регистра 13 подключена группа 44 выходов 14 памяти, выход линии 23 задержки соединен с S-входом КЗ-триггера 10, к R-входу которого подключен выход элемента ШШ 12, первый вход которого соединен с-выходом аналого-цифрового преобразователя 8 и с вторым входом элемента И 31, прямой выход RS-триггера 10 соединен с входом линии 9 задержки,

15

20

25

30

35

40

45

50

55

П

выход которой подкпючен к второму входу аналого-цифрового преобразователя 8, п выходов которого соединены с п входами 1тфроанллогового преобразователя И и с п пходлми регистра 30, п выходов которого подключены к группе 67 п входов блока 29 совпадения, группа 65 п входов 65 которого соединена с п выходами регистра 28, выхоп цийроаналогового преобразователя 33 соединен с первым входом блока 32

сравнения.

Устройство для контроля сопротивления работает следующим образом. Нажатием переключателя 2 устройство приводится в исходное состояние, т.е. триггеры 3, 10, 21, регистры 13, 30, счетчики 16, 19 импульсов приводятся в состояние О, В элементы 81, 82, 83 памяти блока 14 памяти и в элементе 94 памяти блока 24 управления и вычислений записана программа проверки.

Измеряемые сопротивления 6 подключены к выходу 37 коммутатора 5 и к входам 39 коммутатора 7. В режиме контроля сопротивления устройство начинает работать с нажатием переключателя 84. При этом триггер 85 перебрасывается в состояние 1 и на синхронизирующий вход микропроцессора 91 через элемент И 90 поступают импульсы с генератора 89 импульсов. Микропроцессор 91 переходит к выполнению программы контроля сопротивления на соответствующем диапазоне.

Одновременно через элемент И 88 в счетчики 16 и 19 импульсов записывается первый импульс, а также через линию 23 задержки переводится в состояние 1 триггер 10. Комбинация выходных сигналов со счетчика 16 импульсов поступает на дешифратор 15. С его выхода снимается код, который поступает на входы 43 коммутатора 7. Он обеспечивает подключение одного из контролируемых сопротивлений 6 ко входу аналого-цифрового преобразователя 8.

Вькодные сигналы со счетчика 19 поступают на дешифратор 17. Код, снимаемый с дешифратора 17, обеспечивает считывание с элемента 83 памяти в регистр 13 кода, соответствующего подключенному эталонному сопротивлению в блоке 4 эталонных резисторов. Выходная информация с регистра 13 поступает на входы 38 коммутатора 5, который в соответствии с поступившим

кодом обеспечила г подключение эталонного речист ора с бтгока 4 к гчкоду М коммутатора 5.

Кроме того, выходные сигналы с де- шиФрятора 15 поступают на вход элемента 82 памяти блока 14, обеспечивая считывание с него кода верхнего предела для контролируемого сопротивления 6. Этот код записывается в пер- вую группу разрядов регистра 28.

Выходная информация с регистра 13 подается также на элемент 81 памяти блокя 14, обеспечивая считывание с него кода нижнего предела для конт- ролируемого сопротивления 6. Этот код записывается во вторую группу разрядов регистра 28.

Выходной сигнал с триггера 10 через линию 9 задержки поступает на управляющий вход аналого-цифрового преобразователя 8, обеспечивая начало его работы. С вторых выходов аналого-цифрового преобразователя 8 считывается параллельный код, пропорцио- напьный падению напряжения на эталонном резисторе в блоке 4 и измеряемом сопротивлении 6. Этот код поступает на информационные входы регистра 30 и цифроаналогового преобразователя 33

Выходной сигнал с цифроаналогового преобразователя 33 поступает на первый вход блока 32 сравнения, на второй вход которого подается напряжение от источника 11 эталонного напря- жения.

При исправной работе аналого-цифрового преобразователя 8 напряжение } поступающее с выхода блока 33, меньше эталонного напряжения от источни- ка 11. В этом случае блок 32 сравнения выдает сигнал, эквивалентный логическому нулю. Если сигнал с выхода блока 33 равен или больше напряжения источника 11, то блок 32 сравнения выдает сигнал, эквивалентный логической единице, который поступает на второй вход элемента И 31. На первый вход элемента И 31 поступает сигнал Окончание преобразования с первого выхода аналого-цифрового преобразователя 3. Этот же сигнал через «элемент ИЛИ 12, поступает на R-вход триггера 10 и возвращает его в исходное (нулевое) состояние,

С выхода регистра 30 сигнал поступает на вторые входы группы 99 элементов И блока 29 совпадения кодов. На первые входы группы 99 элементов И

Q

п 5 9

40 д$ ,

5

подается код с адресной шины 59 и шины управления 58, С выходов группы 99 элементов И сигнал поступает на элемент 48 совпадения. При наличии сигналов на обеих группах входов мент 98 осуществляет сравнение поступившего кода, эквивалентного измеряемому сопротивлению 6, с кодом нижнего и с кодом верхнего пределов.

В случае, если значение измеряемого сопротивления не лежит между значениями верхнего и нижнего пределов, то с выхода 66 блока 29 совпадения кодов выдается сигнал, эквивалентный единице, который через элемент ИЛИ 93 блока 24 управления и вычислений поступает на вход прерывания микропроцессора 91. Одновременно этот сигнал поступает на вход элемента НЕ 92.

По этому же сигналу осуществляется прекращение подачи импульсов с генератора 87 на элементы устройства контроля.

Аналогично работает устройство, если напряжение на первом входе блока 32 сравнения превышает напряжение, поступающее на второй вход.

Локализация сопротивления Rx, параметры которого не укладываются в допуски, осуществляется микропроцессором 91 по информации, снимаемой с блока 14 памяти, и индицируется на блок 25 индикации.

Для проведения проверки необходимо нажать переключатель 84.

Если параметры сопротивления R- укладываются в заданные пределы, то следующим импульсом, поступающим с выхода генератора 87 импульсов, происходит подключение очередного сопротивления 6 к входам аналого-цифрового преобразователя 8, триггер 10 переводится в состояние 1 и процесс контроля сопротивления повторяется.

Этот процесс продолжается до тех nopj пока не будут опрошены все п сопротивлений 6. При возбуждении (п+1) выхода у дешифратора 15 происходит сброс триггера 21 через элемент ИЛИ 86. Одновременно на блок 25 индикации выдается информация об окончании проверки.

Для определения технического состояния самого устройства предусмотрен в работе устройства режим самопроверки. С этой целью нажимается переключатель 1, триггер 3 переводится в состояние 1. выходным cm- налом обеспечивается отключение входов и выходов сопротивлений 6 и подключение блока 4 эталонных резисторов через коммутаторы 5 и 7 к аналого- цифровому преобразователю 8.. Одновременно подается сигнал на элементы И 18 и 27. После того как микропроцессор 91 считает информацию с элемен та И 27. начинается процесс самопроверки устройства.

При возбуждении (п+1) выхода в дешифраторе 15 происходит переброс триггера 21 в состояние 1. Выход- ной сигнал триггера 21 поступает на элемент И 26. Считанный единичный код с элемента И 31 соответствует окончанию самопроверки устройства.

Коды нижнего и верхнего пределов измеряемых сопротивлений хранятся в элементе 94 памяти блока 24 управления и вычислений и через микропроцессор 91 записываются в элементы 81, G2, 03 памяти блока 14 памяти.

За счет непрерывного контроля я процессе функционирования устройства, обеспечения возможности проведения самопроверки устройства и обеспечения точной локализации места неис- правности повышается достоверность функционирования устройства.

Формула изобретения

Устройство для контроля сопротивления, содержащее два коммутатора, исто ник эталонного напряжения, две линии задержки, блок памяти, первый счетчик импульсов, первый элемент И, блок совпадения кодов, последовательно соединенные -блок сравнения и цифро- аналоговый преобразователь, два переключателя, блок индикации, отличающееся тем, что, с целью повышения дсстоверности функционирования устройства, дополнительно введе ны три RS-триггера, три элемента И, три элемента ИЛИ, три регистра управления, аналого-цифровой преобразователь, блок эталонных резисторов, второй счетчик импульсов., два дешифрато- ра, блок управления и вычислений, выход первого переключателя подключен к S-входу первого триггера, R-вход которого соединен с выходом второго переключателя, первым входом блока УП равления и вычислений, первым входом первого элемента ИЛИ, первым входом второго элемента ИЛИ, первым входом третьего элемента ИЛИ, R-входом второго триггер-}, примой РЫХОД первого RS-триггера подключен к управляющему входу первого коммутатора, к первому управляющему входу второго коммутатора, к первому входу первого элемента И и первому входу второго элемента И, первый выход первого коммутатора соединен с первым управляющим входом второго коммутатора, второй выход первого коммутатора соединен с клеммой для подключения первых выводов контролируемых сопротивлений, вторые выводы которых подключены к первой группе информационных входов второго коммутатора, вторые управляющие входы которого соединены с п выходами первого дешифратора, а выхо с информационным входом аналого-цифрового преобразователя, вторые входы первого коммутатора соединены с выходами блока эталонных сопротивлений вход которого подключен к выходу источника эталонного напряжения, треть входы первого коммутатора подключены к п входам первого регистра и к первой группе п входов блока памяти, вторая группа п входов которого соеднена с п выходами второго дешифратора, к информационным входам которого подключены выходы первого счетчика импульсов, счетный вход которого соединен с первым выходом блока управления и вычислений, с счетным входом второго счетчика импульсов, с входом первой линии задержки и с вторым входом второго элемента ИЛИ, выходы второго счетчикл импульсов подключены к входам второго дешифратора, выходы которого соединены с третьей группой п входов блока памяти, четвертая, пятая, нестая и седьмая группы входов которого соединены с вторым, третьим, четвертым и пятым выходами блока управления и вычислений, шестой выход которого подключен к первому входу блока индикации, второй вход которого соединен с выходом второго дешифратора, с вторым входом первого элемента И, с вторым входом первого элемента ИЛИ. вторым входом блока управления и вычислений, выход первого элемента ИЛИ подключен к установочным входам первого и второго счетчиков импульсов, выход источника эталонного напряжения соединен с вторым входом блока сравнения, выход которого соединен с первым входом третьего элемента И, выход которого подключен к третьему входу блока уп

равления и вычислений, к четвертому входу которого подключен выход блока совпадения кодов, первый, второй, и третий входы которого соединены с третьим, четвертым и пятым выходами блока управления и вычислений и с первым, вторым и третьим входами второго регистра соответственно, третий, четвертый и пятый входы блока индикации соединены соответственно с вторым, четвертым и пятым выходами блока управления и вычислений, первым, вторым входами и выходом четвертого элемента И, вторым, третьим входами и выхо- дом второго элемента И, третий вход четвертого элемента И соединен с прямым выходом второго RS-триггера, к S-входу которого подключен выход первого элемента И, выход второго элемента ИЛИ соединен с управляющими входами первого и третьего регистров,

к п входам первого регистра подключена первая группа выходов блока памяти, выход первой линии задержки соединен с S-входом третьего RS-триггера, к R-входу которого подключен выход третьего элемента ИЛИ, второй вход которого соединен с выходом аналого-циЛрового преобразователя и с вторым входом третьего элемента И, прямой выход третьего RS-триггера соединен с входом второй линии задержки, выход которой подключен к второму входу аналого-пиАрового преобразователя, п выходов которого соединены с п входами цис роаналогового преобразователя и с п входами третьего регистра, п выходов которого подключены к четвертой группе п входов блока совпадения, пятая группа п входов .оторого соединена с п выходами второго регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Статистический анализатор | 1983 |

|

SU1144120A1 |

| Устройство для контроля параметров | 1988 |

|

SU1665390A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ СИГНАЛОВ АВТОМАТИЧЕСКОЙ ЛОКОМОТИВНОЙ СИГНАЛИЗАЦИИ | 2004 |

|

RU2278795C2 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

| Устройство для считывания графической информации | 1981 |

|

SU983731A1 |

| Устройство для диагностики неисправностей технических объектов | 1988 |

|

SU1536357A1 |

| Устройство для контроля и управления технологическими процессами испытаний и тренировки фотоэлектронных умножителей | 1988 |

|

SU1517041A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

Изобретение относится к электроизмерительной технике и предназначено для контроля сопротивления различных цепей. Цель изобретения - повышение достоверности функционирования - достигается путем обеспечения непрерывного контроля в процессе бункцио- нирования, обеспечения возможности проведения самопроверки устройства и обеспечения точной локализации неисправности. Нажатием переключателя 2 устройство приводится в исходное состояние. Триггеры 3, 10, 21, регистры 13, 30, счетчики 16, 19 обнуляются. В элементах памяти блока 14 памяти и в элементе памяти блока 24 управления и вычислений записана программа проверки. Измеряемые сопротивления 6 подключены к выходу 37 коммутатора 5 и входам 39 коммутатора 7. Через линию 23 задержки триггер 10 переводит- ся в состояние 1. Комбинация выходных сигналов со счетчика 16 импульсов поступает на дешифратор 15, с выхода которого код поступает на входы из коммутатора 7, и обеспечивается подключение одного из контролируемых сопротивлений 6 к входу аналого-циЛро- вого преобразователя 8. Выходные сигналы со счетчика 19 поступают на дешифратор 17. Выходной сигнал с триггера 10 через линию задержки 9 поступает на управляюдай вход аналого- цифрового преобразователя 8. Выходной сигнал с цифроаналогового преобразователя 33 поступает на первый вход блока 32 сравнения, на второй вход которого подается напряжение от источника 11 эталонного напряжения. Если значение измеряемого сопротивления не лежит в заданном диапазоне, то с выхода 66 блока 24 совпадения кодов сигнал через бток 24 управления и вычислении поступает на вход прерывания микропроцессора. Результат отображается в блоке 25 индикации. 6 ил. (Л с сд N) СО

I

I ..I

S061SS

. Фие. б. 6S 6i6tt€

|CtCT-rfQ-

HT-ic-if. 3l

p ; за -. 59

-Э

L. .,

6565

ЈW 6.

Составитель l). Минкин

Радактор 0,.СтенинаТехред М ДиДык 1 1 JLf.-. 1..

Заказ 1981Тираж 426Подписное

ВНИИПИ Государствочиого комитета по изобретениям и открытиям при ГКНТ СССР I 1303т, Могква, Ж-35, Раушская наб,, д. А/5

Производи1 ненно-иэдагельо кий комбинат Патент, г. Ужгород, ул. Гагарина, 101

jfSS

| Цифровой измеритель сопротивления | 1974 |

|

SU500506A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения сопротивления | 1981 |

|

SU1029102A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-05-23—Публикация

1988-06-13—Подача