-элементов И, четвертого RS-триггера, четвертого и пятого элементов ИЛИ, преобразователь кода, состоящий из третьего ичетвертого счетчиков, шестой и седьмой групп элементов И, одиннадцатого элемента И, шестого и седьмого элементов ИЛИ, второго блока формирователей одиночных импульсов, пятого Rb-триггера и второго формирователя одиночных импульсов блок задержки, состоящий из пятого счетчика, третьего дешифратора, вось мой группы элементов И, восьмого, девятого и десятого элементов ИЛИ, третьего формирователя одиночных импульсов, двенадцатого элемента И и шестого RS-триггера,блок сравнения состоящий из группы элементов сравне ния, тринадцатого и четырнадцатого элементов И, первого и второго элементов НЕ и группы развязывающих резисторов, измеритель, состоящий из группы управляемых усилителей, компаратора, блока формирования эталонных напряжений и формирователя . импульсов, управляюпщм входом соединенного с выходом третьей группы элементов ИЛИ, а информационным входом - с выходом компаратора, первый вход которого подключен к выходам группы управляемых усилителей второй вход - к входу блока, формирования эталонных напряжений, управляю щими входами совместно с управляющими входами группы управляемых усилителей соединенного с выходами четвер той группы элементов И и входами второго элемента ИЛИ, первые входы первого и второго элементов И соединены с выходом третьей группы элемен тов ИЛИ, выход.первого элемента И со счетным входом второго счетчика, вторые входы первой группы элементов ИЛИ подключены к Выходу третьего элемента И, первым входом связанного с прямым выходом первого Й5-триггера и вторым входом второго элемента И, инверсный выход первого RS-триггера соединен с вторым входом первого и первым входом четвертого элементов И, третий вход второго, вторые входы третьего и четвертого и первый вход пятого элементов И подключены к Прямому выходу второго RS-триггера выход второго элемента И связан . с вторым входом первого элемента ИЛИ а выход четвертого элемента И с вторыми входами второй группы эле191 ментов ИЛИ, выход переполнения первого счетчика соединен с вторым входом пятого элемента И, подключенного выходом к 5-входу первого RS-триггера, R-вход которого соединен с шиной Установка О и R-входом второго RS-триггера, S-входом подключенного к одному из выходов первого блока формирователей одиночных импульсов, соответствующие выходы которого связаны с первыми входами пятой группы элементов И и третьего элемента ИЛИ, вторые входы пятой группы элементов И соединены с выходами регистра задания вида проверки, а выходы - с информационными входами регистра оперативной памяти вида проверки, подключенного выходами к первым входам четвертой группы элементов И, первые входы которой соединены с выходами первого регистра сдвига, управляющими входами подключенного к выходам шестого и седьмого элементов И, первыми входами связанных с прямым выходом третьего ЯЗ-триггера и управляюпр1м входом первого формирователя одиночных импульсов, информационный вход которого соединен с выходом второго элемента ИЛИ, вход синхронизации и вторые входы шестого и седьмого элементов ИЛИ - с выходами генератора импульсов, а выход - с R-входом третьего RS-триггера, 5-входом подключенного к выходу третьего элемента ИЛИ, BTopbJM входом-связанного с выходом седьмого элемента И, первый вход которого соединен с выходом переполнения второго счетчика, 4 второй вход с выходом последнего разряда второго регистра сдвига, управляющие входы второго регистра сдвига подключены к выходам девятого.и десятого элементов И, а выходы - к третьей группе элементов И, первые входы девятого и десятого элементов И соединены с выходом четвертого Rs-триггера, R-входом подключенного к выходу четвертого, 3-входом - к выходу пятого элементов ИЛИ, вторые входы девятого и десятого элементов И соединены с выходами генератора импульсов, первый вход четвертого элемента ИЛИ и вход сброса второго регистра сдвига связаны с шиной Установка О, остальные входы четвертого элемента ШШ - с вь1ходами третьей группы элементов ШШ, первый вход пятого

элемента ИЛИ соединен с соответствующим выходом блока формирователей одиночных импульсов, второй вход с первым выходом первого формирователя импульсов, а третий - с выходом второго формирователя одиночных импульсов, информационный вход второго формирователя одиночных импульсов подключен к выходу третьего счетчика, информационными входами соединенного с выходами шестой группы элементов И, первые входы которых подключены к выходам группы усилителей, а вторые входы - к первому выходу вто рого блока формирователей одиночных импульсов, первым входом управления соединенного с вторым выходом первого формирователя импульсов, второй вход второго блока формирователей одиночных импульсов связан с первьм входом шестого элементаИЛИ, выход которого подключен к входам сброса третьего и четвертого счетчиков, счетными входами соединенных с выходом одиннадцатого элемента И, первым входом подключенного к выходу пято го R5-триггера и управлякицему входу второго формирователя одиночных импульсов, второй вход одиннадцатого элемента И, входы синхронизации второго блока формирователей одиночных импульсов и второго формирователя одиночных импульсов соединены с выходами генератора импульсов, 5-вход пятого КЗ-триггера подключен к третьему выходу второго блока формирователей одиночных га пульсов, а R-вход к выходу седьмого элемента ИШ, первым входом связанного с выходом второго формирователя одиночных импульсов, первымивходами седьмой группы элементов И и первым входом седьмого элемента ИЛИ, вторые входы шестого и седьмого элементов ИЛИ соединены с шиной Установка О, вторые входы седьмой группы элементов И подключены к выходам четвертого счетчика, а выходы - к первому входу блока индикации, вторым входом соединенного с выходами четвертой группы элементов И,, с вторыми входами восьмой групы элементов И, вторые входы которых соединены с выходами третьего дешифратора,, подключенного к выходам пятого счетчика, счетным входом связанного с выходом двенадцатого элемента И, первый вход которого соединен с выходом шестого RS-триггера и управляющим входом третьего формирователя одиночных импульсов, информационным входом подключенного через восьмой элемент ИЛИ к выходам элементов И восьмой группы, второй вход двенадцатого элемента И и вход синхронизации третьего формирователя одиночных импульсов соединены с . ззыходами генератора импульсов, S-вход шестого RS -триггера и первый вход девятого элемента ИЛИ соединены с выходом элементов ИЛИ третьей группы, а 1 -вход - с выходом десятого элемента ИЛИ, первым входом связанного с выходом третьего формирователя одиночных импульсов и четвертым входом пятого элемента ИЛИ, вторые входы девятого и десятого элементов ИЛИ соединены с шиной Установка О,. , а выход девятого элемента ИЛИ с входом сброса пятого счетчика, пятый вход пятого элемента ИЛИ подключен к выходу тринадцатого элемента И, подсоединенному через первый элемент НЕ к первому входу четырнадцатого элемента И, второй вход которого соединен с первым входом тринадцатого элемента И и соответствующим выходом третьей группы элементов ИЛИ, остальные входы тринадцатого элемента И подключены к выходам элементов сравнения и третьим входом блока индикации, первые входы элементов сравнения соединены с вторьвда выходами контактных групп контролируемого блока и через развязывающие резисторы с выходом второго элемента НЕ, а вторые входы - с выходами дешифратора адреса , вход второго элемента НЕ подключен к соответствуючему выходу четвертой группы элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1390616A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| Устройство для контроля металлизированных переходов печатной платы | 1985 |

|

SU1308955A1 |

| Устройство для контроля межслойных переходов печатной платы | 1980 |

|

SU947793A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРИЧЕСКОГО МОНТАЖА, содержащее блок индикации, узел ввода, выходными шинами соединенный с входами регистра задания адреса, регистра задания вида проверки и управляющиьш входами первогоблока формирователей одиночных импульсов, входы синхронизации которого подключены к выходам генератора импульсов, выход регистра задания адреса подключен к первым входам первой и второй групп элементов И, адресного блока, включающего первый и второй счетчики, информационными входами соединенные с выходами первой и второй групп элементов И соответственно, первый и второй дешифраторы, подключенные входами к выходам одних разрядов первого и второго счетчиков соответственно, подсоединенных выходами других разрядов к входам усилителей группы, первую и вторую группы элементов ИЛИ, первыми входами соединенных с выходами первого и второго дешифраторов, выход переполнения первого счетч ика соединен с первым входом первого элемента ИЛИ, выходом связанного со счетным входом второго счетчика, а входы сброса обоих счетчиков подключены к шине Установка О, вторые входы первой и второй групп элементов И связаны с соответствующими выходами , первого блока формирования одиночных импульсов, выходы первой и второй групп элементов ИЛИ связаны с входом дешифратора адреса и адресным входом контролируемого блока, который первьм выходом контактной группы соединен с информационным входом коммутатора, входом задания, стимулирующих воздействий подключенного к выходу блока стабилизаторов напряжения, формирователь командных импульсов, состоящий из третьей группы элементов ИЛИ и третьей группы элесл ментов И, выходы которой соединены с входами третьей группы элементов ИЛИ, соединенной выходами . с управляющими входами коммутатора, блока стабилизаторов напряжения и контролируемого блока, отлиел чающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены блок группового подключения точек, тоящий из первого и второго й.5-триггеров и пяти элементов И, блок формирования вида проверки, состоящий из четвертой и пятой групп элементов И, первого регистра сдвига, регистра оперативной памяти вида про- , верки, второго и третьего элементов ИЛИ, третьего Р5-триггера, шестого, седьмого и восьмого элементов И и первого формирователя одиночных импульсов, блок формирования шагов управления, состоящий из второго регистра сдвига, девятого и десятого

Изобретение относится к области автоматики и вычислительной техники.

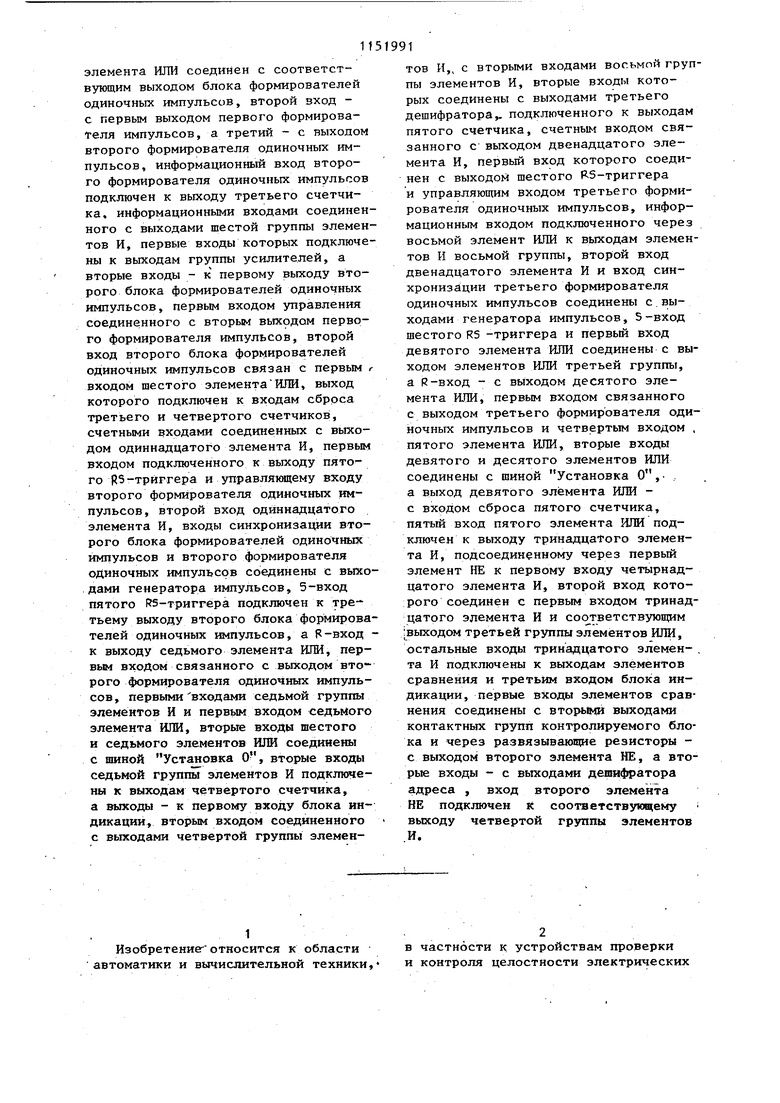

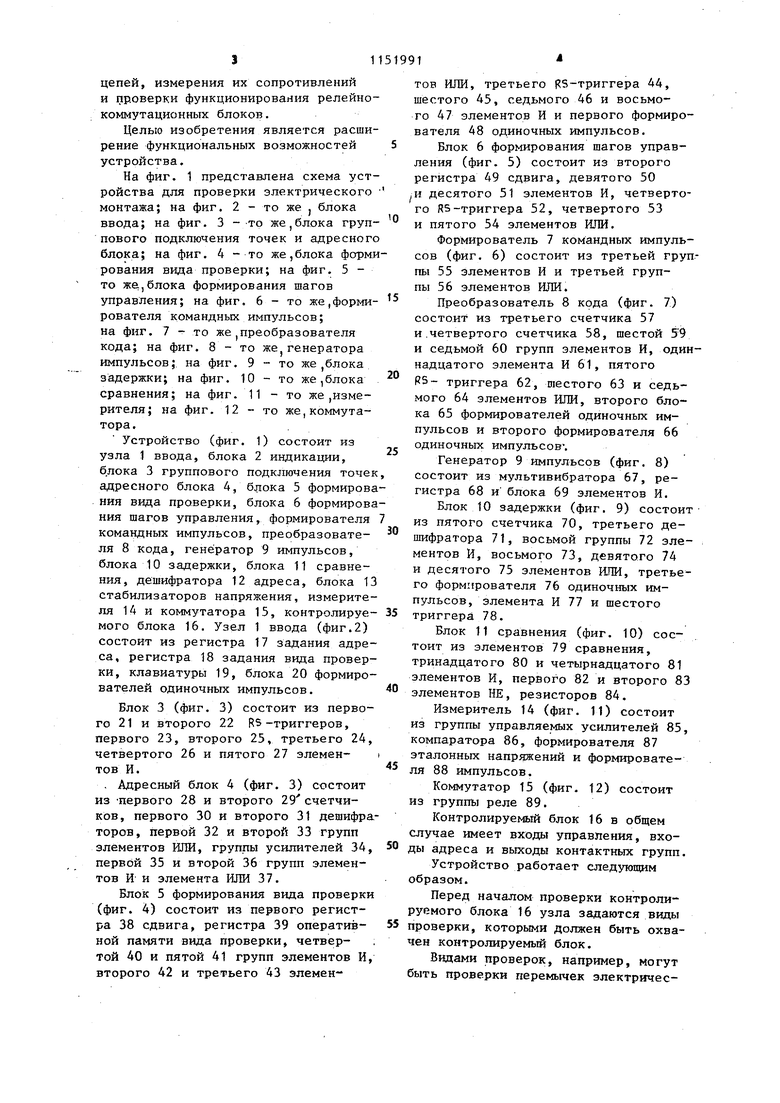

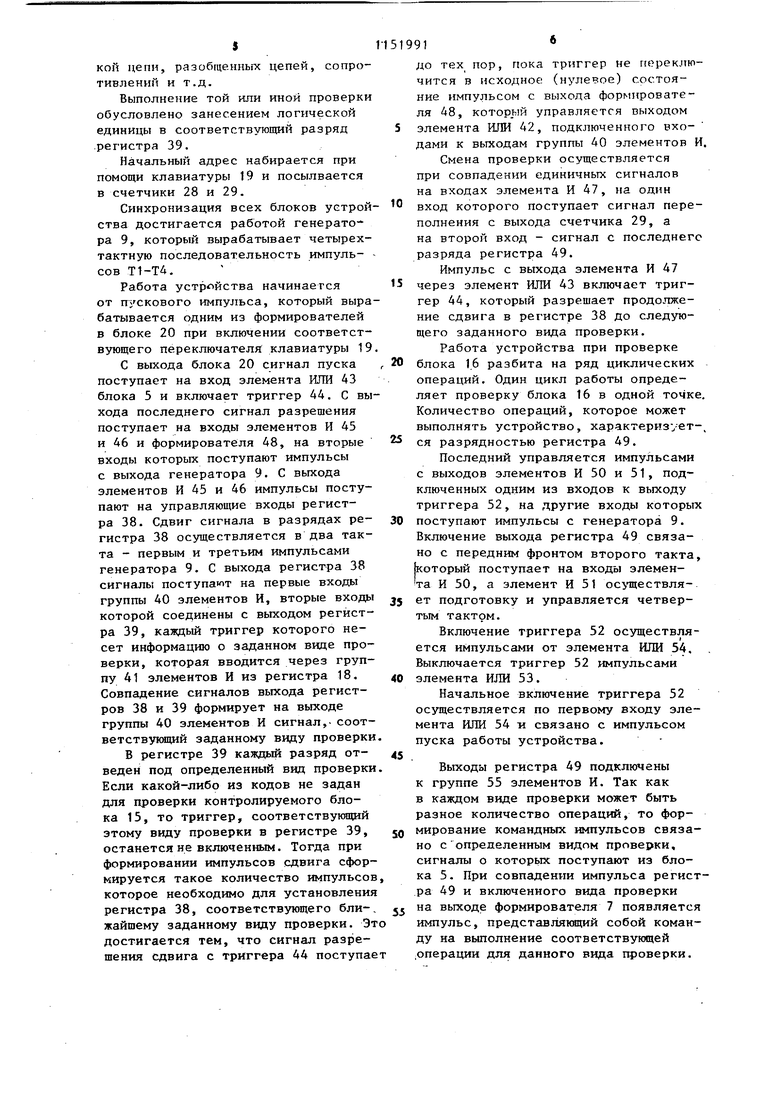

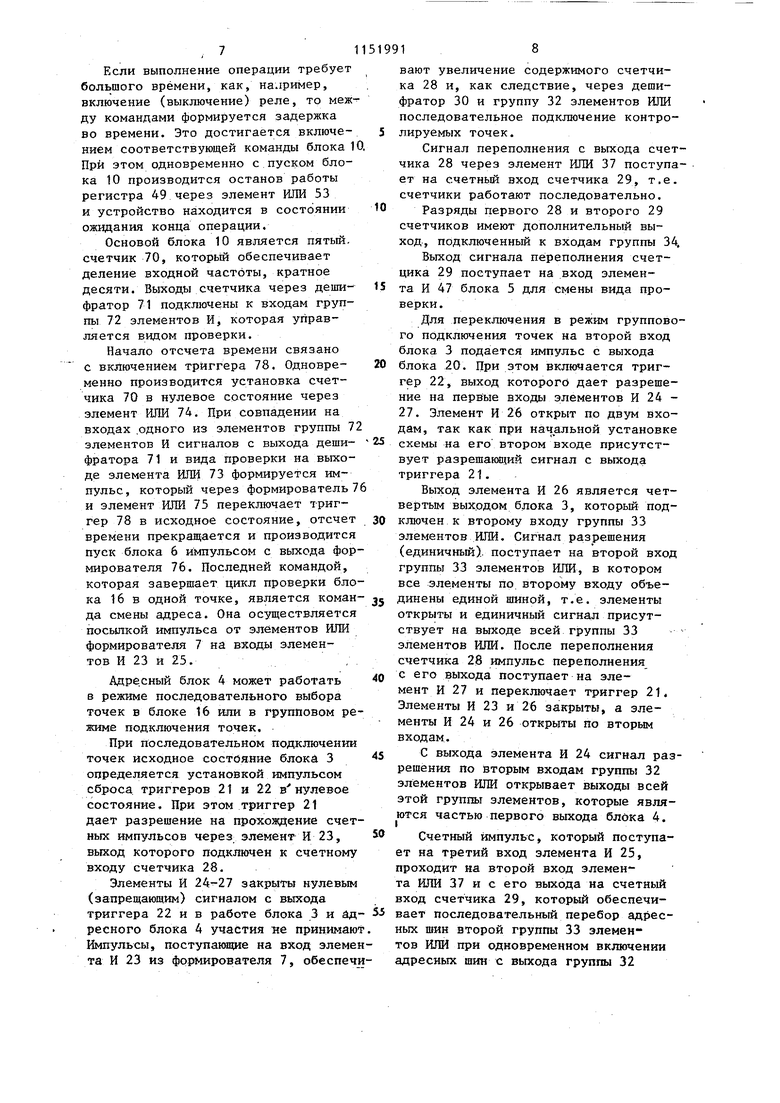

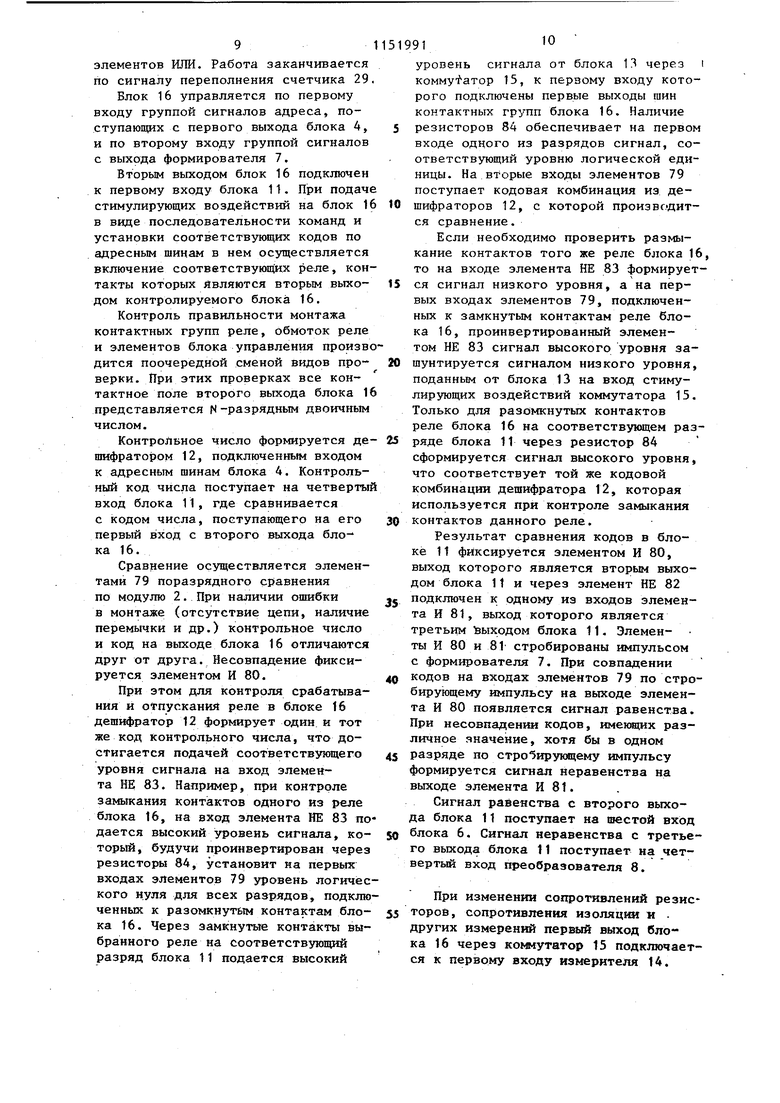

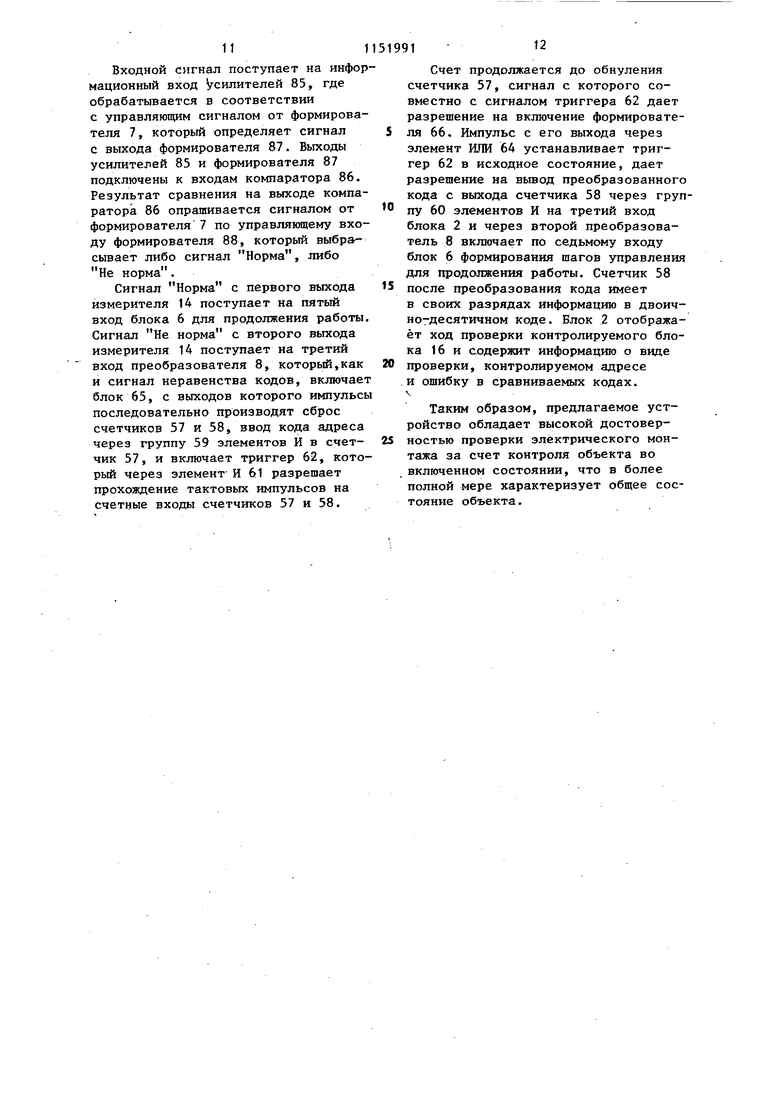

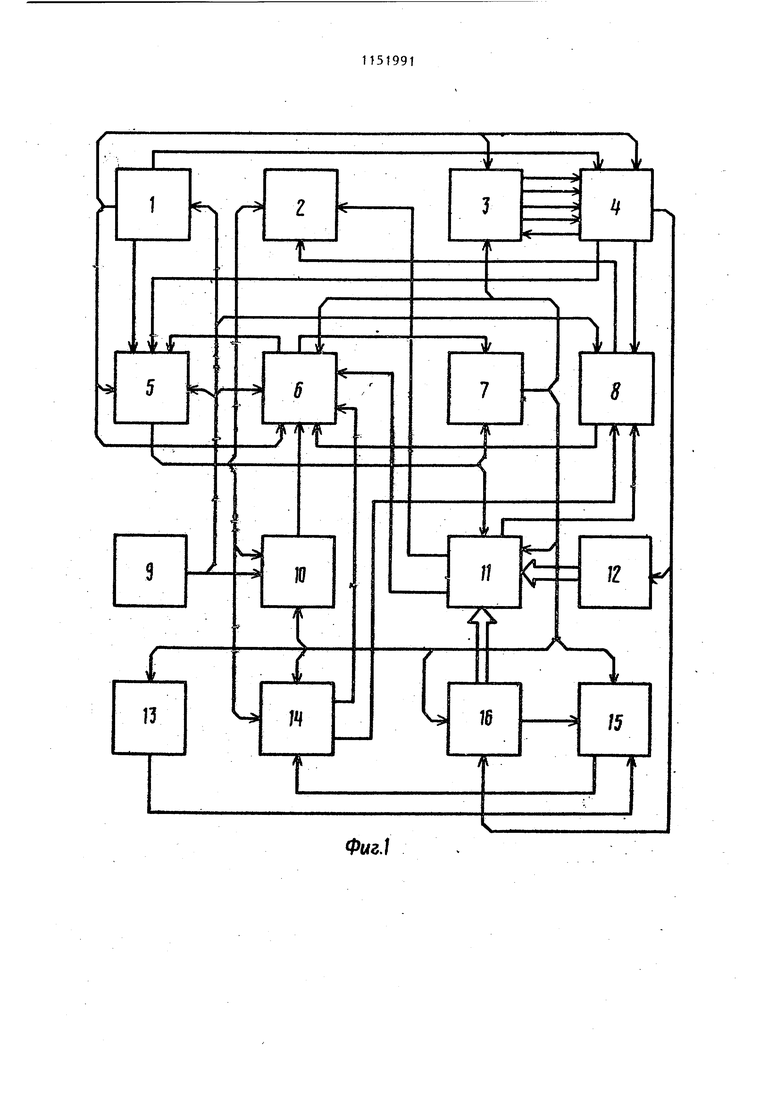

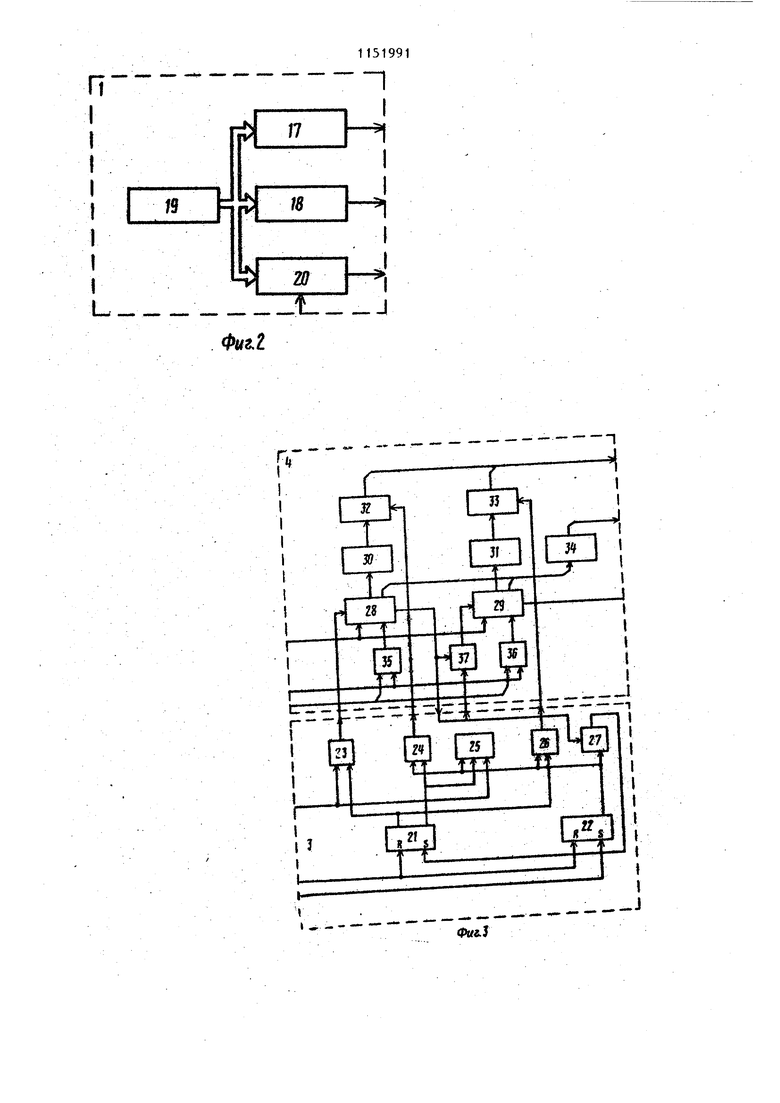

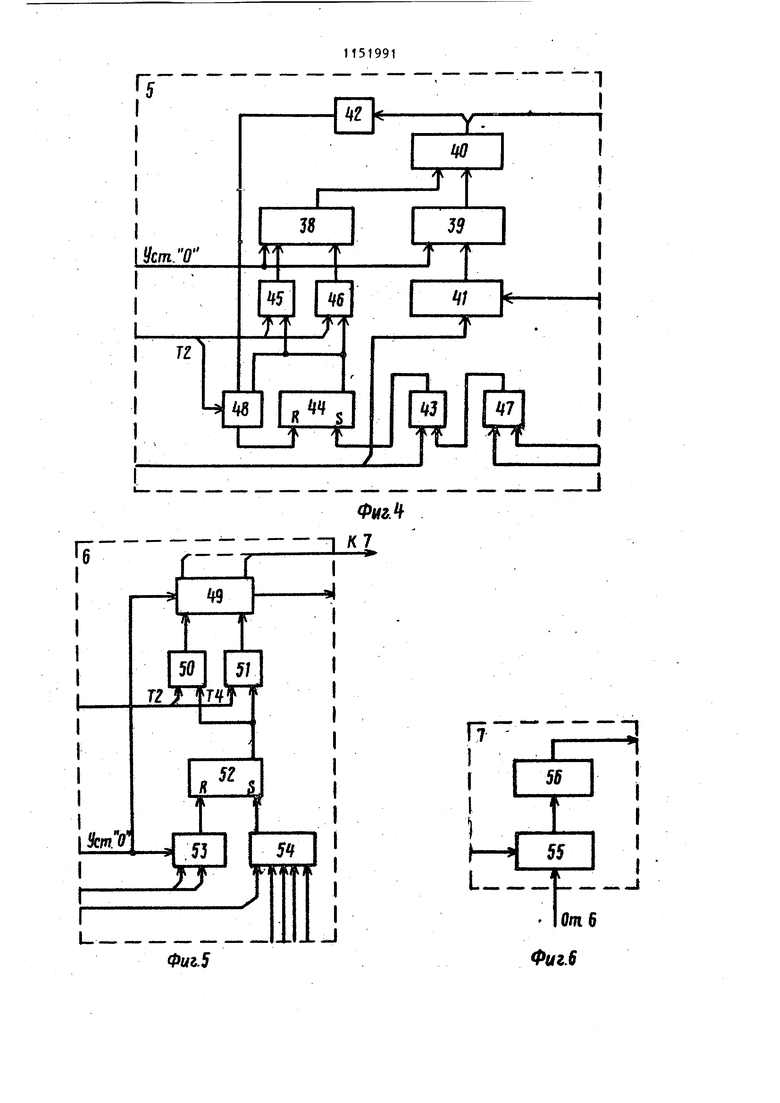

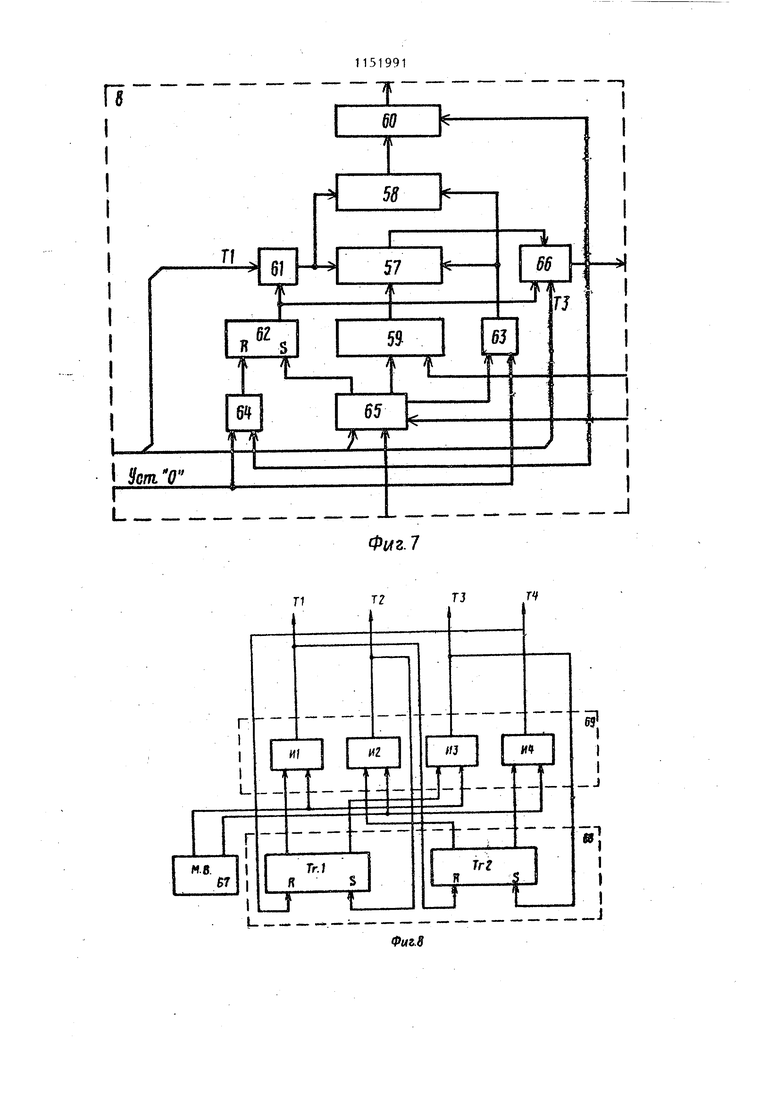

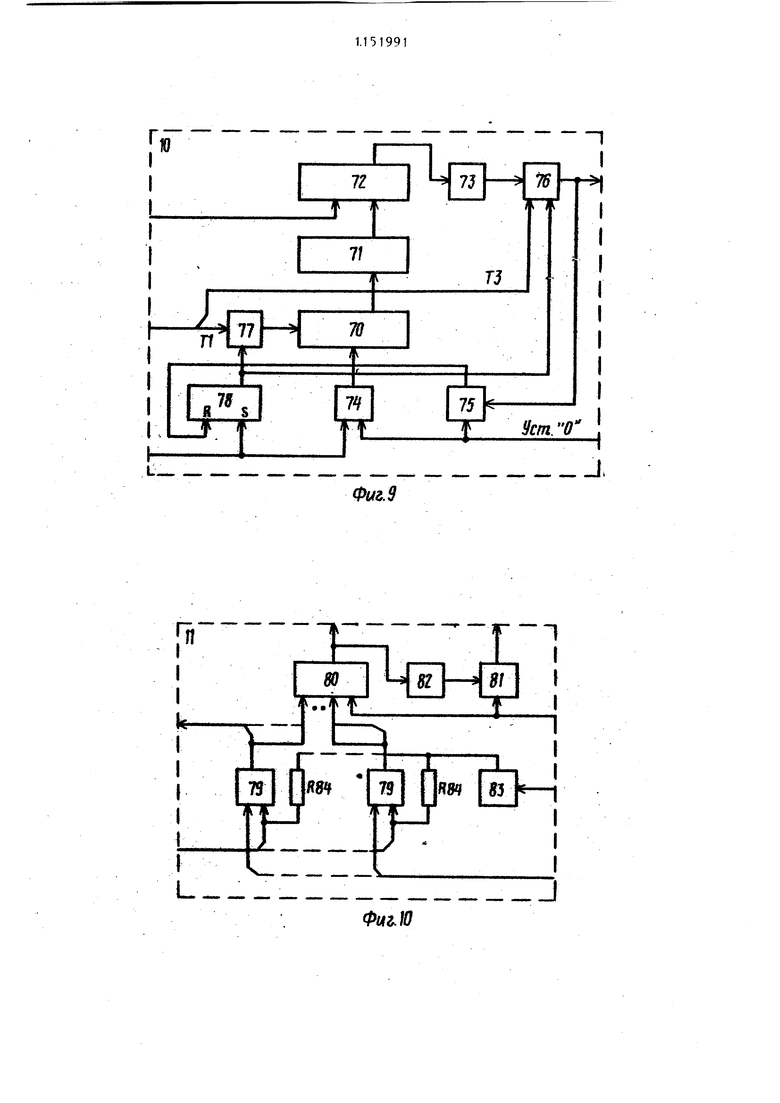

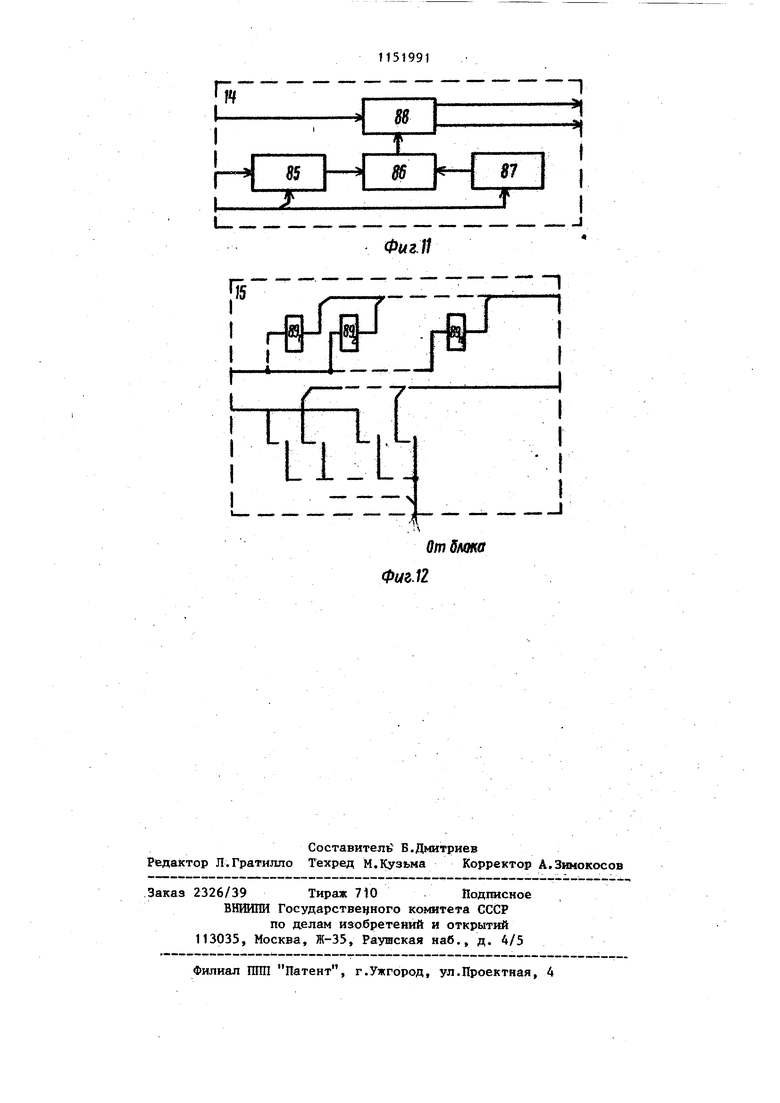

в частности к устройствам проверки и контроля целостности электрических цепей, измерения их сопротивлений и проверки функционирования релейнокоммутационных блоков. Целью изобретения является расширение функциональных возможностей устройства. На фиг. 1 представлена схема устройства для проверки электрического монтажа; на фиг. 2 - то же j блока ввода; на фиг. 3 - то же,блока группового подключения точек и адресного блока; на фиг. 4 - то же,блока форми рования вида проверки; на фиг. 5 то же;,блока формирования шагов управления; на фиг. 6 - то же,формирователя командных импульсов; на фиг. 7 - то же Iпреобразователя кода; на фиг. 8 - то же,генератора импульсов; на фиг. 9 - то же ,блока задержки; на фиг. 10 - то же,блока сравнения; на фиг. 11 - то же ,измерителя; на фиг. 12 - то же,коммутатора. Устройство (фиг. 1) состоит из узла 1 ввода, блока 2 индикации, блока 3 группового подключения точек адресного блока 4, блока 5 формирова ния вида проверки, блока 6 формирова ния шагов управления, формирователя командных импульсов, преобразователя 8 кода, генератор 9 импульсов, блока 10 задержки, блока 11 сравнения, дешифратора 12 адреса, блока 13 стабилизаторов напряжения, измерителя 14 и коммутатора 15, контролируемого блока 16. Узел 1 ввода (фиг.2) состоит из регистра 17 задания адреса, регистра 18 задания вида проверки, клавиатуры 19, блока 20 формирователей одиночных импульсов. Блок 3 (фиг. 3) состоит из первого 2 1 и второго 22 R5 -триггеров, первого 23, второго 25, третьего 24, четвертого 26 и пятого 27 элементов И. , Адресный блок 4 (фиг. 3) состоит из Первого 28 и второго 29 счетчиков, первого 30 и второго 31 дешифра торов, первой 32 и второй 33 групп элементов ШШ, группы усилителей 34, первой 35 и второй 36 групп элементов И и элемента ИЛИ 37. Блок 5 формирования вида проверки (фиг. 4) состоит из первого регистра 38 сдвига, регистра 39 оперативной памяти вида проверки, четвертой 40 и пятой 41 групп элементов И, второго 42 и третьего 43 элемен тов ИЛИ, третьего RS-триггера 44, шестого 45, седьмого 46 и восьмого 47 элементов И и первого формирователя 48 одиночных импульсов. Блок 6 формирования шагов управления (фиг. 5) состоит из второго регистра 49 сдвига, девятого 50 и десятого 51 элементов И, четвертого RS-триггера 52, четвертого 53 и пятого 54 элементов ИЖ. Формирователь 7 командных импульсов (фиг. 6) состоит из третьей группы 55 элементов И и третьей группы 56 элементов ИЛИ. Преобразователь 8 кода (фиг. 7) состоит из третьего счетчика 57 и.четвертого счетчика 58, шестой 59 и седьмой 60 групп элементов И, одиннадцатого элемента И 61, пятого R5 триггера 62, шестого 63 и седьмого 64 элементов ИЛИ, второго блока 65 формирователей одиночных импульсов и второго формирователя 66 одиночных импульсов-. Генератор 9 импульсов (фиг. 8) состоит из мультивибратора 67, регистра 68 и блока 69 элементов И. Блок 10 задержки (фиг. 9) состоитиз пятого счетчика 70, третьего дешифратора 71, восьмой группы 72 элементов И, восьмого 73, девятого 74 и десятого 75 элементов ИПИ, третьего формирователя 76 одиночных импульсов, элемента И 77 и шестого триггера 78. Блок 11 сравнения (фиг. 10) состоит из элементов 79 сравнения, тринадцатого 80 и четырнадцатого 81 элементов И, первого 82 и второго 83 элементов НЕ, резисторов 84. Измеритель 14 (фиг. 11) состоит из группы управляемых усилителей 85, компаратора 86, формирователя 87 эталонных напр5рсений и формирователя 88 импульсов. Коммутатор 15 (фиг. 12) состоит из группы реле 89. Контролируемь1й блок 16 в общем случае имеет входы управления, вхоы адреса и выходы контактных групп. Устройство работает следующим образом. Перед началом проверки контролиуемого блока 16 узла задаются виды проверки, которьми должен быть охваен контролируемый блок. Врздами проверок, например, могут ыть проверки перемычек электричесS

кой цепи, разоб це.ннь1Х цепей, сопротивлений и т.д.

Выполнение той или иной проверки обусловлено занесением логической е/диницы в соответствующий разряд .регистра 39.

Начальный адрес набирается при помощи клавиатуры 19 и посылвается в счетчики 28 и 29.

Синхронизация всех блоков устрой ства достигается работой генератора 9, который вырабатывает четырехтактную последовательность импульсов Т1-Т4.

Работа устройства начинается от пускового импульса, который вырабатывается одним из формирователей в блоке 20 при включении соответствующего переключателя клавиатуры 19

С выхода блока 20 сигнал пуска поступает на вход элемента ИЛИ 43 блока 5 и включает триггер 44. С выхода последнего сигнал разрешения поступает на входы элементов И 45 и 46 и формировате ля 48, на вторые входы которых поступают импульсы с выхода генератора 9. С выхода элементов И 45 и 46 импульсы поступают на управляющие входы регистра 38. Сдвиг сигнала в разрядах регистра 38 осуществляется в два такта - первым и третьим импульсами генератора 9, С выхода регистра 38 сигналы поступают на первые входы группы 40 элементов И, вторые входы которой соединены с выходом регистра 39, каждый триггер которого несет информацию о заданном виде проверки, которая вводится через группу 41 элементов И из регистра 18. Совпадение сигналов выхода регистров 38 и 39 формирует на выходе группы 40 элементов И сигнал,- соответствующий заданному виду проверки

В регистре 39 каждый разряд отведен под определенный вид проверки Если какой-либо из кодов не задан для проверки контролируемого блока 15, то триггер, соответствукшщй этому виду проверки в регистре 39, останется не включенным. Тогда при формировании импульсов сдвига сформируется такое количество импульсов которое необходимо для установления регистра 38, соответствзпощего бли-, жайщему заданному виду проверки. Эт достигается тем, что сигнал разрешения сдвига с триггера 44 поступае

991

до тех пор, пока триггер не переключится в исходное (нулевое) состояние импульсом с выхода формирователя 48, который управляется выходом элемента ИЛИ 42, подключенного входами к выходам группы 40 элементов

Смена проверки осуществляется при совпадении единичных сигналов на входах элемента И 47, на один вход которого поступает сигнал переполнения с выхода счетчика 29, а на второй вход - сигнал с последнег разряда регистра 49.

Импульс с выхода элемента И 47 через элемент ИЛИ 43 включает триггер 44, который разрешает продолжение сдвига в регистре 38 до следующего заданного вида проверки.

Работа устройства при проверке блока 16 разбита на ряд циклических операций. Один цикл работы определяет проверку блока 16 в одной точк Количество операций, которое может выполнять устройство, характеризует ся разрядностью регистра 49.

Последний управляется импульсами с выходов элементов И 50 и 51, подключенных одним из входов к выходу триггера 52, на другие входы которы поступают импульсы с генератора 9. Включение выхода регистра 49 связано с передним фронтом второго такта который поступает на входы элемента И 50, а элемент И 51 ос тцествляет подготовку и управляется четвертым тактом.

Включение триггера 52 осуществляется импульсами от элемента ИЛИ 54. Выключается триггер 52 импульсами элемента ИЛИ 53.

Начальное включение триггера 52 осуществляется по первому входу элемента ИДИ 54 и связано с импульсом пуска работы устройства.

Выходы регистра 49 подключены к группе 55 элементов И. Так как в каждом виде проверки может быть разное количество операций, то формирование командных импульсов связано сопределенным видом проверки, сигналы о которьпс поступают из блока 5. При совпадении импульса регистра 49 и включенного вида проверки на выходе формирователя 7 появляется импульс, представлякнций собой команду на выполнение соответствующей .операции для данного вида проверки.

,71

Если выполнение операции требует большого времени, как, налример, включение (выключение) реле, то между командами формируется задержка во времени. Это достигается включением соответствующей команды блока 10 При этом одновременно с пуском блока 10 производится останов работы регистра 49 через элемент ИЛИ 53 и устройство находится в состоянии ожидания конца операции.

Основой блока 10 является пятый, счетчик 70, который обеспечивает деление входной частоты, кратное десяти. Выходы счетчика через дешифратор 71 подключены к входам группы 72 элементов И, которая управляется видом проверки.

Начало отсчета времени связано с включением триггера 78. Одновременно производится установка счетчика 70 в нулевое состояние через элемент ИЛИ 74. При совпадении на входах .одного из элементов группы 72 элементов И сигналов с выхода дешифратора 71 и вида проверки на выходе элемента ЕЛИ 73 формируется импульс, который через формирователь 7 и элемент ИЛИ 75 переключает триггер 78 в исходное состояние, отсчет времени прекращается и производится пуск блока 6 импульсом с выхода формирователя 76. Последней командой, которая завершает цикл проверки блока 16 в одной точке, является команда смены адреса. Она осз ществляется посьшкой импульса от элементов ИЛИ формирователя 7 на входы элементов И 23 и 25.,

Адре.сный блок 4 может работать в режиме последовательного выбора точек в блоке 16 или в групповом режиме подключения точек.

При последовательном подключении точек исходное состбяние блоки 3 определяется установкой импульсом сброса триггеров 21 и 22 внулевое состояние. При этом триггер 21 дает разрешение на прохождение счетных импульсов через элемент И 23, выход которого подключен к счетному входу счетчика 28.

Элементы И 24-27 закрыты нулевым (запрещающим) сигналом с выхода триггера 22 и в работе блока 3 и адресного блока 4 участия ие принимают Импульсы, поступающие на вход элемен та И 23 из формирователя 7, обеспечн8

вают увеличение содержимого счетчика 28 и, как следствие, через дешифратор 30 и группу 32 элементов ИЛИ последовательное подключение контролируемых точек.

Сигнал переполнения с выхода счетчика 28 через элемент ИЛИ 37 поступает на счетньй вход счетчика 29, т.е. счетчики работают последовательно.

0 Разряды первого 28 и второго 29 счетчиков имеют дополнительный выход, подключенный к входам группы 34,

Выход сигнала переполнения счетцика 29 поступает на вход элемента И 47 блока 5 для смены вида проверки.

Для переключения в режим группового подключения точек на второй вход блока 3 подается импульс с выхода

0 блока 20. Цри этом включается триггер 22, выход которого дает разрешение на первые входы элементов И 24 27. Элемент И 26 открыт по двум входам, так как при начальной установке схемы на его втором входе присутствует разрешакяций сигнал с выхода триггера 21.

Выход элемента И 26 является четвертым выходом блока 3, который подключен к второму входу группы 33 элементов ИЛИ. Сигнал разрешения (единичный), поступает на второй вход группы 33 элементов ШШ, в котором все элементы по второму входу объединены единой шиной, т.е. элементы открыты и единичный сигнал присутствует на выходе всей группы 33 элементов ИЖ. После переполнения счетчика 28 импульс переполнения

0 с его выхода поступает на элемент И 27 и переключает триггер 21. Элементы И 23 и 26 закрыты, а элементы И 24 и 26 открыты по вторым входам.

5 С выхода элемента И 24 сигнал разрешения по вторым входам группы 32 элементов ШШ открывает выходы всей этой группы злементов, которые являются частью первого выхода блока 4.

Счетный импульс, который поступает на третий вход элемента И 25, проходит на второй вход элемента ИЛИ 37 и с его выхода на счетный вход счетчика 29, который обеспечивает последовательньй перебор адресных шин второй группы 33 элементов ИЛИ при одновременном включении адресных шин с выхода группы 32 9 элементов ИЛИ. Работа заканчивается по сигналу переполнения счетчика 29 Блок 16 управляется по первому входу группой сигналов адреса, поступающих с первого выхода блока 4, и по второму входу группой сигналов с выхода формирователя 7, Вторым выходом блок 16 подключен к первому входу блока 11. При подаче стимулирующих воздействий на блок 16 в виде последовательности команд и установки соответствующих кодов по адресным шинам в нем осуществляется включение соответствующих реле, контакты которых Являются вторым выходом контролируемого блока 16. Контроль правильности монтажа контактных групп реле, обмоток реле и элементов блока управления произво дится поочередной сменой видов проверки. При этих проверках все контактное поле второго выхода блока 16 представляется N-разрядным двоичным числом. Контрольное число формируется дешифратором 12, подключенным входом к адресным шинам блока 4. Контрольный код числа поступает на четвертый вход блока 11, где сравнивается с кодом числа, поступающего на его первый вход с второго выхода блока 1 6 . Сравнение осуществляется элементами 79 поразрядного сравнения по модулю 2. При наличии ошибки в монтаже (отсутствие цепи, наличие перемычки и др.) контрольное число и код на выходе блока 16 отличаются друг от друга. Несовпадение фиксируется элементом И 80. При этом для контроля срабатывания и отпускания реле в блоке 16 дешифратор 12 формирует один, и тот же код контрольного числа, что достигается подачей соответствующего уровня сигнала на вход элемента НЕ 83. Например, при контроле замыкания контактов одного из реле блока 16, на вход элемента НЕ 83 по дается высокий уровень сигнала, который, будучи проинвертирован через резисторы 84, установит на первых входах элементов 79 уровень логичес кого нуля для всех разрядов, подклю ченных к разомкнутым контактам блока 16. Через замкнутые контакты выбранного реле на соответствующий разряд блока 11 подается высокий 91 уровень сигнала от блока 13 через i коммутатор 15, к первому входу которого подключены первые выходы шин контактных групп блока 16. Наличие резисторов 84 обеспечивает на первом входе одного из разрядов сигнал, соответствующий уровню логической единицы. На вторые входы элементов 79 поступает кодовая комбинация из дешифраторов 12, с которой производится сравнение. Если необходимо проверить размыкание контактов того же реле блока 16, то на входе элемента НЕ 83 формируется сигнал низкого уровня, а на первых входах элементов 79, подключенных к замкнутым контактам реле блока 16, проинвертированный элементом НЕ 83 сигнал высокого уровня зашунтируется сигналом низкого уровня, поданным от блока 13 на вход стимулирующих воздействий коммутатора 15. Только для разомкнутых контактов реле блока 16 на соответствующем разряде блока 11 через резистор 84 сформируется сигнал высокого уровня, что соответствует той же кодовой комбинации дешифратора 12, которая используется при контроле замыкания контактов данного реле. Результат сравнения кодов в блоке 11 фиксируется элементом И 80, выход которого является вторым выходом блока 11 и через элемент НЕ 82 подключен к одному из входов элемента И 81, выход которого является третьим 1зыхрдом блока 11. Элемен- ты И 80 и 81 стробированы импульсом с формирователя 7. При совпадении кодов на входах элементов 79 по стробирующему импульсу на выходе элемента И 80 появляется сигнал равенства. При несовпадении кодов, имеющих различное значение, хотя бы в одном разряде по стро ирующему импульсу формируется сигнал неравенства на выходе элемента И 81. Сигнал райеяства с второго выхода блока 11 поступает на шестой вход блока 6. Сигнал неравенства с третьего выхода блока 11 поступает на четвертьй вход преобразователя 8. При изменении сопротивлений резисторов, сопротивления изоляц{ш н . других измерений первый выход блока 16 через коютутатор 15 подключается к первому входу измерителя 14.

11 1

Входной сигнал поступает на информационный вход Усилителей 85, где обрабатывается в соответствии с управляющим сигналом от формирователя 7, который определяет сигнал с выхода формирователя 87. Выходы усилителей 85 и формирователя 87 подключены к входам компаратора 86. Результат сравнения на выходе компаратора 86 опрашивается сигналом от формирователя 7 по управляющему входу формирователя 88, который выбрасывает либо сигнал Норма, либо Не норма.

Сигнал Норма с первого выхода измерителя 14 поступает на пятый вход блока 6 для продолжения работы. Сигнал Не норма с второго выхода измерителя 14 поступает на третий вход преобразователя 8, который,KaiK и сигнал неравенства кодов, включает блок 65, с выходов которого импульсы последовательно производят сброс счетчиков 57 и 58, ввод кода адреса через группу 59 элементов И в счетчик 57, и включает триггер 62, который через элемент И 61 разрешает прохождение тактовых импульсов на счетные входы счетчиков 57 и 58.

12

51991

Счет продолжается до обнуления счетчика 57, сигнал с которого совместно с сигналом триггера 62 дает разрешение на включение формирователя 66. Импульс с его выхода через элемент ИЛИ 64 устанавливает триггер 62 в исходное состояние, дает разрешение на вывод преобразованного кода с выхода счетчика 58 через группу 60 элементов И на третий вход блока 2 и через второй преобразователь 8 включает по седьмому входу блок 6 формирования шагов управления для продолжения работы. Счетчик 58

после преобразования кода имеет

в своих разрядах информацию в двоично-десятичном коде. Блок 2 отображает ход проверки контролируемого блока 16 и содержит информацию о виде

проверки, контролируемом адресе

и ошибку в сравниваемых кодах.

Таким образом, предлагаемое устройство обладает высокой достоверностью проверки электрического монтажа за счет контроля объекта во включенном состоянии, что в более полной мере характеризует общее состояние объекта.

ФмгЛ

Фнг:2

Г5

I - -1 Kl

ii

Фиь.5

.I

ФигЛ

It

- -I

I0m6 Ф«г.6

Гв

П

61

в « S

ю

Зет О

Г

п

i 60

-

66

57

f

rj

5

ej

I

. 7

гч

rj

Hi

I.:.

1

Фи1.Ю

Ф«гЛ

втбмко Фие.12

| Устройство для контроля цифровыхблОКОВ | 1979 |

|

SU796860A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 758174, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-23—Публикация

1983-05-18—Подача