Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известен двоичный вычитатель [1], который содержит логические элементы и формирует двоичный код разности двух трехразрядных двоичных чисел, задаваемых двоичными сигналами, и бит, определяющий ее знак.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного двоичного вычитателя, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка четырехразрядных двоичных чисел.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип двоичный вычитатель [2], который содержит одиннадцать элементов исключающее ИЛИ, шесть элементов И и формирует двоичный код разности двух четырехразрядных двоичных чисел, задаваемых двоичными сигналами, и бит, определяющий ее знак. При этом схемная глубина прототипа равна 9.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится схемная сложность, обусловленная тем, что цена по Квайну схемы прототипа равна 46.

Техническим результатом изобретения является упрощение схемы двоичного вычитателя за счет уменьшения ее цены по Квайну при сохранении функциональных возможностей прототипа и не большая чем у прототипа схемная глубина.

Указанный технический результат при осуществлении изобретения достигается тем, что в двоичном вычитателе, содержащем одиннадцать элементов исключающее ИЛИ и шесть элементов И, k-й ( ), (

), ( )-й входы и первый выход двоичного вычитателя, первый и второй входы m-го (

)-й входы и первый выход двоичного вычитателя, первый и второй входы m-го ( ) элемента и соединены соответственно с первым, вторым входами k-го элемента исключающее ИЛИ и первым входом первого элемента И, выходом и первым входом m-го элемента исключающее ИЛИ, особенность заключается в том, что в него дополнительно введены два элемента ИЛИ, первый, второй входы пятого элемента исключающее ИЛИ, первый, второй входы и выход i-го (

) элемента и соединены соответственно с первым, вторым входами k-го элемента исключающее ИЛИ и первым входом первого элемента И, выходом и первым входом m-го элемента исключающее ИЛИ, особенность заключается в том, что в него дополнительно введены два элемента ИЛИ, первый, второй входы пятого элемента исключающее ИЛИ, первый, второй входы и выход i-го ( ) элемента ИЛИ соединены соответственно с выходами девятого, третьего, первым, вторым входами (

) элемента ИЛИ соединены соответственно с выходами девятого, третьего, первым, вторым входами ( )-го и первым входом (

)-го и первым входом ( )-го элементов исключающее ИЛИ, первый вход (

)-го элементов исключающее ИЛИ, первый вход ( )-го и выход (

)-го и выход ( )-го элементов исключающее ИЛИ, второй вход шестого и выход (

)-го элементов исключающее ИЛИ, второй вход шестого и выход ( )-го элементов И соединены соответственно с выходом (

)-го элементов И соединены соответственно с выходом ( )-го элемента И и вторым входом i-го элемента ИЛИ, выходом пятого элемента И и вторым входом (

)-го элемента И и вторым входом i-го элемента ИЛИ, выходом пятого элемента И и вторым входом ( )-го элемента исключающее ИЛИ, первый вход одиннадцатого элемента исключающее ИЛИ соединен с выходом шестого элемента И, а вторые входы шестого, одиннадцатого и выход седьмого элементов исключающее ИЛИ соединены соответственно с выходами восьмого, десятого элементов исключающее ИЛИ и вторым выходом двоичного вычитателя, третий, четвертый и пятый выходы которого соединены соответственно с выходами пятого, шестого и одиннадцатого элементов исключающее ИЛИ.

)-го элемента исключающее ИЛИ, первый вход одиннадцатого элемента исключающее ИЛИ соединен с выходом шестого элемента И, а вторые входы шестого, одиннадцатого и выход седьмого элементов исключающее ИЛИ соединены соответственно с выходами восьмого, десятого элементов исключающее ИЛИ и вторым выходом двоичного вычитателя, третий, четвертый и пятый выходы которого соединены соответственно с выходами пятого, шестого и одиннадцатого элементов исключающее ИЛИ.

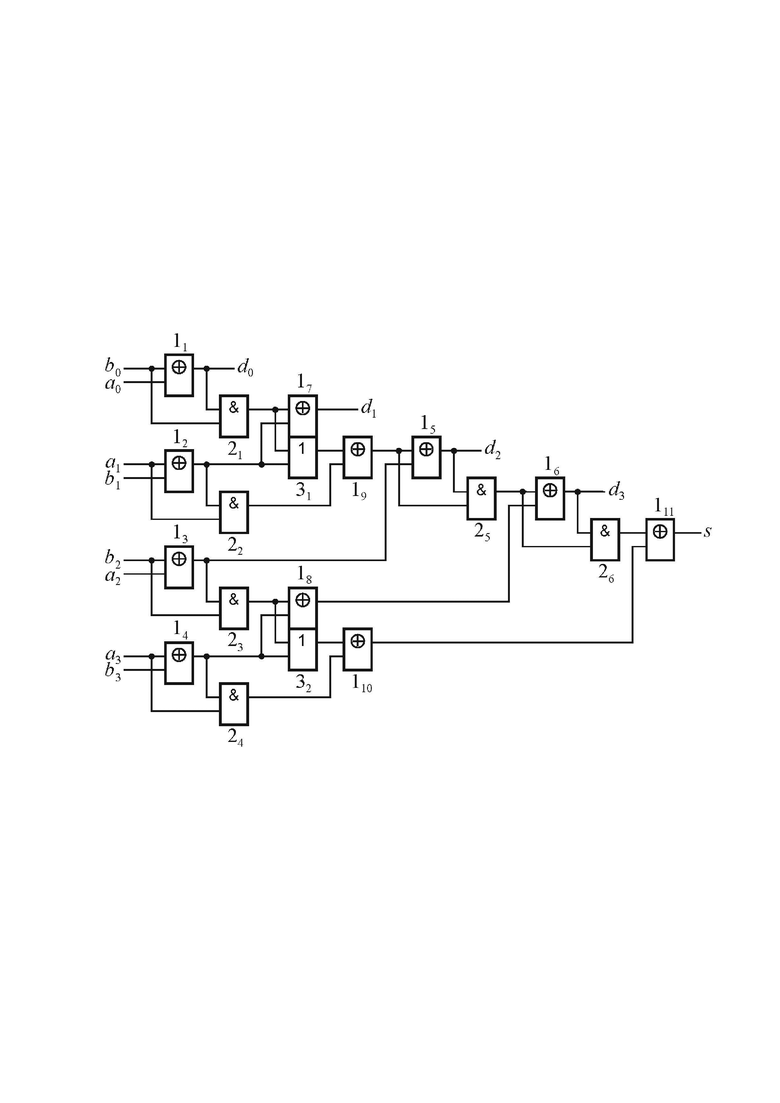

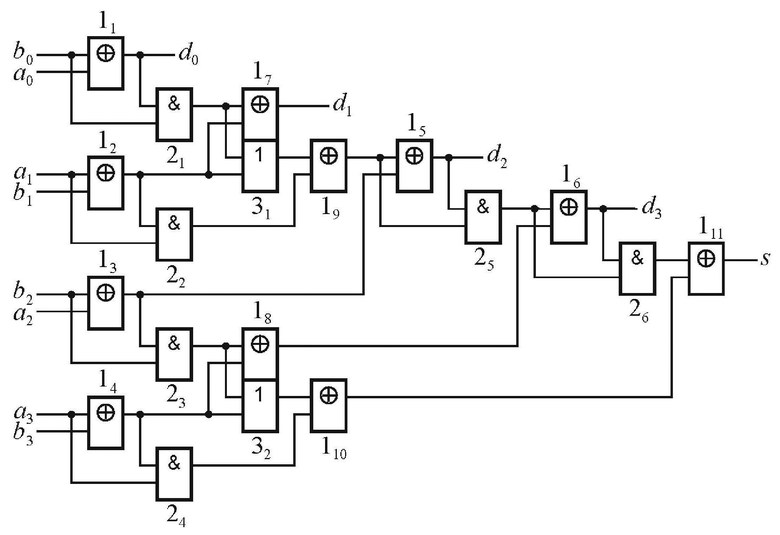

На чертеже представлена схема предлагаемого двоичного вычитателя.

Двоичный вычитатель содержит элементы исключающее ИЛИ 11,…,111, элементы И 21,…,26 и элементы ИЛИ 31, 32, причем первый вход элемента 111, первый вход и выход элемента 1m ( ) соединены соответственно с выходом элемента 26, вторым и первым входами элемента 2m, первый, второй входы элемента 15, первый, второй входы и выход элемента 3i (

) соединены соответственно с выходом элемента 26, вторым и первым входами элемента 2m, первый, второй входы элемента 15, первый, второй входы и выход элемента 3i ( ) подключены соответственно к выходам элементов 19, 13, первому, второму входам элемента 1i+6 и первому входу элемента 1i+8, первый вход элемента 1i+6 и выход элемента 12×i, второй вход элемента 26 и выход элементов 22×i соединены соответственно с выходом элемента 22×i-1 и вторым входом элемента 3i, выходом элемента 25 и вторым входом элемента 1i+8, а вторые входы элементов 16, 111 и выходы элементов 11, 17, 15, 16, 111 подключены соответственно к выходам элементов 18, 110 и первому, второму, третьему, четвертому, пятому выходам двоичного вычитателя, k-й (

) подключены соответственно к выходам элементов 19, 13, первому, второму входам элемента 1i+6 и первому входу элемента 1i+8, первый вход элемента 1i+6 и выход элемента 12×i, второй вход элемента 26 и выход элементов 22×i соединены соответственно с выходом элемента 22×i-1 и вторым входом элемента 3i, выходом элемента 25 и вторым входом элемента 1i+8, а вторые входы элементов 16, 111 и выходы элементов 11, 17, 15, 16, 111 подключены соответственно к выходам элементов 18, 110 и первому, второму, третьему, четвертому, пятому выходам двоичного вычитателя, k-й ( ) и (

) и ( )-й входы которого соединены соответственно с первым и вторым входами элемента 1k.

)-й входы которого соединены соответственно с первым и вторым входами элемента 1k.

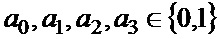

Работа предлагаемого двоичного вычитателя осуществляется следующим образом. На его первый, шестой, третий, восьмой и пятый, второй, седьмой, четвертый входы подаются соответственно двоичные сигналы  и

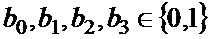

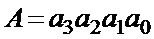

и  , которые задают подлежащие обработке четырехразрядные двоичные числа

, которые задают подлежащие обработке четырехразрядные двоичные числа  ,

,  , причем

, причем  и

и  определяют значения старших и младших разрядов соответственно. Поскольку наборы 00 и 11 значений сигналов

определяют значения старших и младших разрядов соответственно. Поскольку наборы 00 и 11 значений сигналов  (

( ),

),  являются равноценными для элементов 1k, 2k, достаточно рассмотреть функционирование предлагаемого вычитателя для следующих наборов значений этих сигналов: 00, 01, 10. В представленной ниже таблице приведены значения выходных сигналов

являются равноценными для элементов 1k, 2k, достаточно рассмотреть функционирование предлагаемого вычитателя для следующих наборов значений этих сигналов: 00, 01, 10. В представленной ниже таблице приведены значения выходных сигналов  предлагаемого вычитателя, полученные с учетом работы его элементов для всех возможных комбинаций указанных наборов.

предлагаемого вычитателя, полученные с учетом работы его элементов для всех возможных комбинаций указанных наборов.

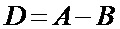

Согласно представленной таблице имеем  , где

, где  – четырехразрядное двоичное число, задаваемое двоичными сигналами

– четырехразрядное двоичное число, задаваемое двоичными сигналами  (

( и

и  определяют значения старшего и младшего разрядов соответственно), причем если число D является положительным либо

определяют значения старшего и младшего разрядов соответственно), причем если число D является положительным либо  , то

, то  , если отрицательным, то

, если отрицательным, то  и оно представлено в дополнительном коде.

и оно представлено в дополнительном коде.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый двоичный вычитатель имеет схемную глубину, равную 9, и формирует двоичный код разности двух четырехразрядных двоичных чисел, задаваемых двоичными сигналами, и бит, определяющий ее знак. При этом схема предлагаемого двоичного вычитателя проще, чем у прототипа, поскольку ее цена по Квайну равна 38.

Источники информации:

1. Патент РФ 2629453, кл. G06F7/50, 2017 г.

2. Патент РФ 2789722, кл. G06F7/50, 2023 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2022 |

|

RU2789722C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2024 |

|

RU2829014C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2023 |

|

RU2809213C1 |

| Умножитель | 1984 |

|

SU1171784A1 |

| Устройство для умножения числа на постоянный коэффициент | 1984 |

|

SU1168928A1 |

| УСТРОЙСТВА И СПОСОБЫ ПОВЫШЕНИЯ ЕМКОСТИ ДЛЯ БЕСПРОВОДНОЙ СВЯЗИ | 2008 |

|

RU2452119C2 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАННОГО ОБУЧЕНИЯ | 1968 |

|

SU222044A1 |

| УСОВЕРШЕНСТВОВАННЫЙ КАНАЛ УПРАВЛЕНИЯ В СИСТЕМЕ ВЫСОКОСКОРОСТНОГО ПАКЕТНОГО ДОСТУПА | 2012 |

|

RU2607466C2 |

| Способ адаптивного мажоритарногодЕКОдиРОВАНия КОдОВыХ КОМбиНАций | 1978 |

|

SU809567A1 |

| СПОСОБ КВАДРАТУРНОЙ АМПЛИТУДНО-ФАЗОВОЙ МОДУЛЯЦИИ | 2020 |

|

RU2738091C1 |

Изобретение относится к области цифровой вычислительной техники. Технический результат заключается в уменьшении схемной сложности устройства при сохранении возможности формирования двоичного кода разности двух четырехразрядных двоичных чисел. Технический результата достигается за счет того, что двоичный вычитатель содержит одиннадцать элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, шесть элементов И и два элемента ИЛИ, соединенных между собой с реализацией вычитания четырехразрядных двоичных чисел, задаваемых двоичными сигналами. 1 ил., 1 табл.

Двоичный вычитатель, содержащий одиннадцать элементов исключающее ИЛИ и шесть элементов И, причем k-й ( ), (

), ( )-й входы и первый выход двоичного вычитателя, первый и второй входы m-го (

)-й входы и первый выход двоичного вычитателя, первый и второй входы m-го ( ) элемента и соединены соответственно с первым, вторым входами k-го элемента исключающее ИЛИ и первым входом первого элемента И, выходом и первым входом m-го элемента исключающее ИЛИ, отличающийся тем, что в него дополнительно введены два элемента ИЛИ, первый, второй входы пятого элемента исключающее ИЛИ, первый, второй входы и выход i-го (

) элемента и соединены соответственно с первым, вторым входами k-го элемента исключающее ИЛИ и первым входом первого элемента И, выходом и первым входом m-го элемента исключающее ИЛИ, отличающийся тем, что в него дополнительно введены два элемента ИЛИ, первый, второй входы пятого элемента исключающее ИЛИ, первый, второй входы и выход i-го ( ) элемента ИЛИ соединены соответственно с выходами девятого, третьего, первым, вторым входами (

) элемента ИЛИ соединены соответственно с выходами девятого, третьего, первым, вторым входами ( )-го и первым входом (

)-го и первым входом ( )-го элементов исключающее ИЛИ, первый вход (

)-го элементов исключающее ИЛИ, первый вход ( )-го и выход (

)-го и выход ( )-го элементов исключающее ИЛИ, второй вход шестого и выход (

)-го элементов исключающее ИЛИ, второй вход шестого и выход ( )-го элементов И соединены соответственно с выходом (

)-го элементов И соединены соответственно с выходом ( )-го элемента И и вторым входом i-го элемента ИЛИ, выходом пятого элемента И и вторым входом (

)-го элемента И и вторым входом i-го элемента ИЛИ, выходом пятого элемента И и вторым входом ( )-го элемента исключающее ИЛИ, первый вход одиннадцатого элемента исключающее ИЛИ соединен с выходом шестого элемента И, а вторые входы шестого, одиннадцатого и выход седьмого элементов исключающее ИЛИ соединены соответственно с выходами восьмого, десятого элементов исключающее ИЛИ и вторым выходом двоичного вычитателя, третий, четвертый и пятый выходы которого соединены соответственно с выходами пятого, шестого и одиннадцатого элементов исключающее ИЛИ.

)-го элемента исключающее ИЛИ, первый вход одиннадцатого элемента исключающее ИЛИ соединен с выходом шестого элемента И, а вторые входы шестого, одиннадцатого и выход седьмого элементов исключающее ИЛИ соединены соответственно с выходами восьмого, десятого элементов исключающее ИЛИ и вторым выходом двоичного вычитателя, третий, четвертый и пятый выходы которого соединены соответственно с выходами пятого, шестого и одиннадцатого элементов исключающее ИЛИ.

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2024 |

|

RU2829014C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2022 |

|

RU2789731C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2022 |

|

RU2789722C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2019 |

|

RU2709653C1 |

| Станок для придания концам круглых радиаторных трубок шестигранного сечения | 1924 |

|

SU2019A1 |

Авторы

Даты

2025-05-22—Публикация

2024-11-26—Подача