Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны двоичные вычитатели (см., например, патент РФ 2629453, кл. G06F 7/50, 2017г.), которые содержат логические элементы и формируют двоичный код разности двух трёхразрядных двоичных чисел, задаваемых двоичными сигналами, и бит, определяющий её знак.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных двоичных вычитателей, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка четырёхразрядных двоичных чисел.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип двоичный вычитатель (патент РФ 2789722, кл. G06F 7/50, 2023г.), который содержит элементы исключающее ИЛИ, элементы И и формирует двоичный код разности двух четырёхразрядных двоичных чисел, задаваемых двоичными сигналами, и бит, определяющий её знак.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся большие аппаратурные затраты, обусловленные тем, что прототип содержит тринадцать элементов исключающее ИЛИ и десять элементов И.

Техническим результатом изобретения является уменьшение аппаратурных затрат при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в двоичном вычитателе, содержащем десять элементов исключающее ИЛИ и семь элементов И, первый вход и выход i-го  элемента исключающее ИЛИ и выход пятого элемента исключающее ИЛИ соединены соответственно с вторым и первым входами i-го элемента И и вторым выходом двоичного вычитателя, первые входы восьмого и девятого элементов исключающее ИЛИ подключены соответственно к выходам пятого и шестого элементов И, особенность заключается в том, что первый вход и выход r-го

элемента исключающее ИЛИ и выход пятого элемента исключающее ИЛИ соединены соответственно с вторым и первым входами i-го элемента И и вторым выходом двоичного вычитателя, первые входы восьмого и девятого элементов исключающее ИЛИ подключены соответственно к выходам пятого и шестого элементов И, особенность заключается в том, что первый вход и выход r-го  элемента И и выход четвёртого элемента И соединены соответственно с вторыми входами (r+4)-го и (r+7)-го элементов исключающее ИЛИ и первым входом пятого элемента исключающее ИЛИ, первые входы шестого, седьмого и десятого элементов исключающее ИЛИ подключены соответственно к выходам восьмого, девятого элементов исключающее ИЛИ и седьмого элемента И, а первый, второй входы r-го элемента исключающее ИЛИ и первый, второй входы четвёртого элемента исключающее ИЛИ соединены соответственно с (r+1)-м, (r+5)-м и первым, пятым входами двоичного вычитателя, первый, третий четвёртый и пятый выходы которого подключены соответственно к выходам четвёртого, шестого, седьмого и десятого элементов исключающее ИЛИ.

элемента И и выход четвёртого элемента И соединены соответственно с вторыми входами (r+4)-го и (r+7)-го элементов исключающее ИЛИ и первым входом пятого элемента исключающее ИЛИ, первые входы шестого, седьмого и десятого элементов исключающее ИЛИ подключены соответственно к выходам восьмого, девятого элементов исключающее ИЛИ и седьмого элемента И, а первый, второй входы r-го элемента исключающее ИЛИ и первый, второй входы четвёртого элемента исключающее ИЛИ соединены соответственно с (r+1)-м, (r+5)-м и первым, пятым входами двоичного вычитателя, первый, третий четвёртый и пятый выходы которого подключены соответственно к выходам четвёртого, шестого, седьмого и десятого элементов исключающее ИЛИ.

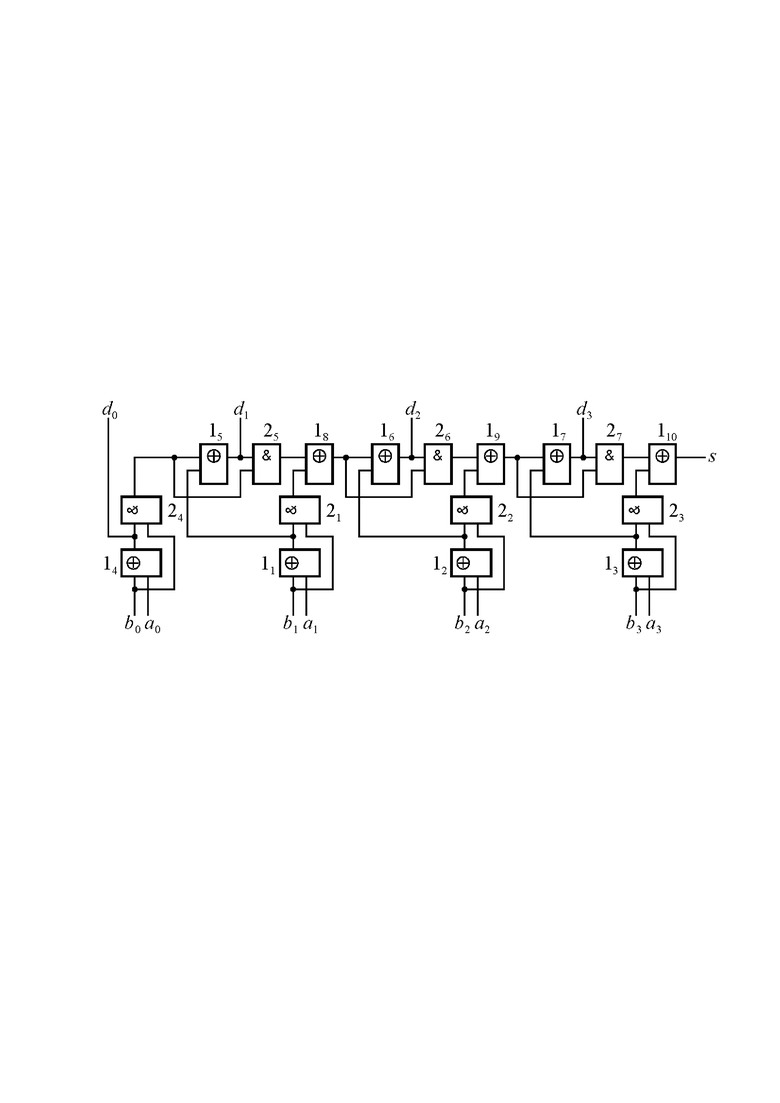

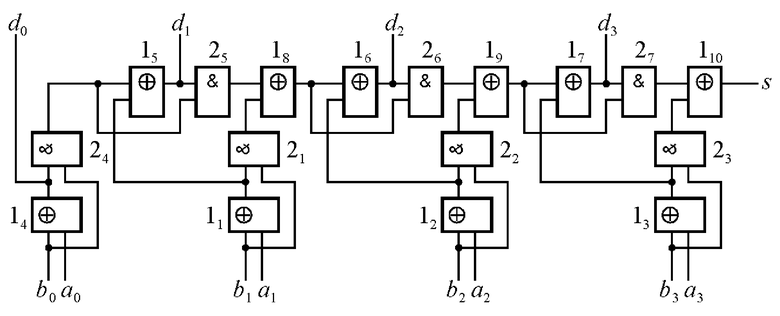

На чертеже представлена схема предлагаемого двоичного вычитателя.

Двоичный вычитатель содержит элементы исключающее ИЛИ 11, …, 110 и элементы И 21, …, 27, причём первый вход и выход элемента 1i  и выход элемента 24 соединены соответственно с вторым и первым входами элемента 2i и первым входом элемента 15, первый, второй входы элемента 1r+7

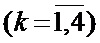

и выход элемента 24 соединены соответственно с вторым и первым входами элемента 2i и первым входом элемента 15, первый, второй входы элемента 1r+7  и второй вход элемента 1r+4 подключены соответственно к выходам элементов 2r+4, 2r и выходу элемента 1r, первые входы элементов 16 и 17 соединены соответственно с выходами элементов 18 и 19, а первый, второй входы элемента 1r и первый, второй входы элемента 14 подключены соответственно к (r+1)-му, (r+5)-му и первому, пятому входам двоичного вычитателя, k-й

и второй вход элемента 1r+4 подключены соответственно к выходам элементов 2r+4, 2r и выходу элемента 1r, первые входы элементов 16 и 17 соединены соответственно с выходами элементов 18 и 19, а первый, второй входы элемента 1r и первый, второй входы элемента 14 подключены соответственно к (r+1)-му, (r+5)-му и первому, пятому входам двоичного вычитателя, k-й  и пятый выходы которого соединены соответственно с выходами элементов 1k+3 и 110.

и пятый выходы которого соединены соответственно с выходами элементов 1k+3 и 110.

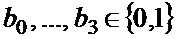

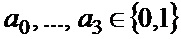

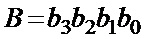

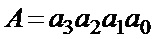

Работа предлагаемого двоичного вычитателя осуществляется следующим образом. На его первый, …, четвертый и пятый, … , восьмой входы подаются соответственно двоичные сигналы  и

и  , которые задают подлежащие обработке четырехразрядные двоичные числа

, которые задают подлежащие обработке четырехразрядные двоичные числа  ,

,  , причём

, причём  и

и  определяют значения старших и младших разрядов соответственно. Поскольку наборы 00 и 11 значений сигналов

определяют значения старших и младших разрядов соответственно. Поскольку наборы 00 и 11 значений сигналов  ,

,

являются равноценными для элементов

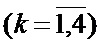

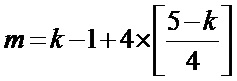

являются равноценными для элементов  (

( , [] - оператор выделения целой части),

, [] - оператор выделения целой части),  , достаточно рассмотреть функционирование предлагаемого вычитателя для следующих наборов значений этих сигналов: 00, 01, 10. В представленной ниже таблице приведены значения выходных сигналов

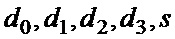

, достаточно рассмотреть функционирование предлагаемого вычитателя для следующих наборов значений этих сигналов: 00, 01, 10. В представленной ниже таблице приведены значения выходных сигналов  предлагаемого вычитателя, полученные с учетом работы его элементов для всех возможных комбинаций указанных наборов.

предлагаемого вычитателя, полученные с учетом работы его элементов для всех возможных комбинаций указанных наборов.

Согласно представленной таблице имеем  , где

, где  - четырёхразрядное двоичное число, задаваемое двоичными сигналами

- четырёхразрядное двоичное число, задаваемое двоичными сигналами  (

( и

и  определяют значения старшего и младшего разрядов соответственно), причем если число D является положительным либо

определяют значения старшего и младшего разрядов соответственно), причем если число D является положительным либо  , то

, то  , если отрицательным, то

, если отрицательным, то  и оно представлено в дополнительном коде.

и оно представлено в дополнительном коде.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый двоичный вычитатель формирует двоичный код разности двух четырехразрядных двоичных чисел, задаваемых двоичными сигналами, и бит, определяющий её знак, и обладает меньшими по сравнению с прототипом аппаратурными затратами, поскольку содержит на три элемента исключающее ИЛИ и на три элемента И меньше, чем в аппаратурном составе прототипа.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2022 |

|

RU2789722C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2024 |

|

RU2840388C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2023 |

|

RU2809213C1 |

| УСТРОЙСТВА И СПОСОБЫ ПОВЫШЕНИЯ ЕМКОСТИ ДЛЯ БЕСПРОВОДНОЙ СВЯЗИ | 2008 |

|

RU2452119C2 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАННОГО ОБУЧЕНИЯ | 1968 |

|

SU222044A1 |

| УСОВЕРШЕНСТВОВАННЫЙ КАНАЛ УПРАВЛЕНИЯ В СИСТЕМЕ ВЫСОКОСКОРОСТНОГО ПАКЕТНОГО ДОСТУПА | 2012 |

|

RU2607466C2 |

| Умножитель | 1984 |

|

SU1171784A1 |

| СПОСОБ КВАДРАТУРНОЙ АМПЛИТУДНО-ФАЗОВОЙ МОДУЛЯЦИИ | 2020 |

|

RU2738091C1 |

| Устройство для умножения числа на постоянный коэффициент | 1984 |

|

SU1168928A1 |

| Устройство для исправления одиночных ошибок | 1982 |

|

SU1053108A2 |

Изобретение относится к области вычислительной технике. Технический результат заключается в уменьшении аппаратных затрат при реализации устройства. Технический результат достигается за счет того, что двоичный вычитатель содержит десять элементов исключающее ИЛИ (11, …, 110) и семь элементов И (21, …, 27), соединенных между собой специальным образом для обеспечения формирования двоичного кода разности двух четырёхразрядных двоичных чисел, задаваемых двоичными сигналами, а также формирования бита, определяющего её знак. 1 ил.

Двоичный вычитатель, содержащий десять элементов исключающее ИЛИ и семь элементов И, причём первый вход и выход i-го  элемента исключающее ИЛИ и выход пятого элемента исключающее ИЛИ соединены соответственно с вторым и первым входами i-го элемента И и вторым выходом двоичного вычитателя, первые входы восьмого и девятого элементов исключающее ИЛИ подключены соответственно к выходам пятого и шестого элементов И, отличающийся тем, что первый вход и выход r-го

элемента исключающее ИЛИ и выход пятого элемента исключающее ИЛИ соединены соответственно с вторым и первым входами i-го элемента И и вторым выходом двоичного вычитателя, первые входы восьмого и девятого элементов исключающее ИЛИ подключены соответственно к выходам пятого и шестого элементов И, отличающийся тем, что первый вход и выход r-го  элемента И и выход четвёртого элемента И соединены соответственно с вторыми входами (r+4)-го и (r+7)-го элементов исключающее ИЛИ и первым входом пятого элемента исключающее ИЛИ, первые входы шестого, седьмого и десятого элементов исключающее ИЛИ подключены соответственно к выходам восьмого, девятого элементов исключающее ИЛИ и седьмого элемента И, а первый, второй входы r-го элемента исключающее ИЛИ и первый, второй входы четвёртого элемента исключающее ИЛИ соединены соответственно с (r+1)-м, (r+5)-м и первым, пятым входами двоичного вычитателя, первый, третий четвёртый и пятый выходы которого подключены соответственно к выходам четвёртого, шестого, седьмого и десятого элементов исключающее ИЛИ.

элемента И и выход четвёртого элемента И соединены соответственно с вторыми входами (r+4)-го и (r+7)-го элементов исключающее ИЛИ и первым входом пятого элемента исключающее ИЛИ, первые входы шестого, седьмого и десятого элементов исключающее ИЛИ подключены соответственно к выходам восьмого, девятого элементов исключающее ИЛИ и седьмого элемента И, а первый, второй входы r-го элемента исключающее ИЛИ и первый, второй входы четвёртого элемента исключающее ИЛИ соединены соответственно с (r+1)-м, (r+5)-м и первым, пятым входами двоичного вычитателя, первый, третий четвёртый и пятый выходы которого подключены соответственно к выходам четвёртого, шестого, седьмого и десятого элементов исключающее ИЛИ.

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2019 |

|

RU2709653C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2017 |

|

RU2689185C2 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2770302C1 |

| US 20050198094 A1, 08.09.2005 | |||

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2016 |

|

RU2629453C1 |

Авторы

Даты

2024-10-22—Публикация

2024-05-17—Подача