о ел

оо

00

оо

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ | 2000 |

|

RU2197061C2 |

| Устройство для сопряжения каналов ЭВМ с периферийными устройствами | 1990 |

|

SU1732348A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1594551A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ | 2002 |

|

RU2254673C2 |

| Система передачи цифровой информации | 1990 |

|

SU1786679A1 |

| Устройство циклового фазирования для волоконно-оптических систем передачи информации | 1988 |

|

SU1540021A1 |

| СПОСОБ ИСПРАВЛЕНИЯ ОШИБОК ПРИ ПЕРЕДАЧЕ ИНФОРМАЦИИ БИИМПУЛЬСНЫМ КОДОМ Манчестер-II И УСТРОЙСТВО ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2566336C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИИМПУЛЬСНОГО КОДА В БИНАРНЫЙ КОД | 2004 |

|

RU2258305C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2258304C1 |

| Устройство для приема информации | 1988 |

|

SU1672571A1 |

Изобретение относится к импульсной технике и. может использоваться в системах передачи цифровой информации для преобразования биимпульсного кода Манчестер 2 в бинарный код без возврата к Преобразователь содержит универсальный регистр 1, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 2, 3 и имеет информационный и тактовый входы 4, 5, тактовый и информационный выходы 6 и 7 о 2 ил.

Фиг.1

.Изобретение относится к импульсной технике и может использоваться к системах передачи цифровой информации ,

Целью изобретения является упрощение преобразователя

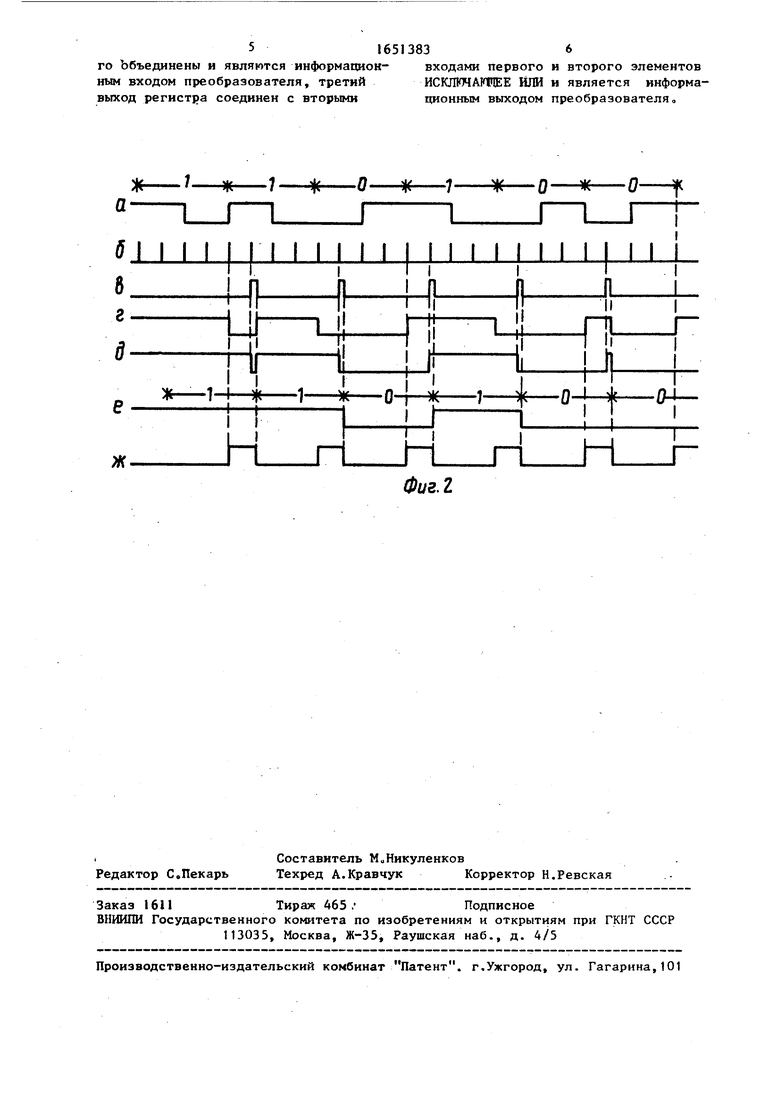

На фиг и 2 показаны функциональная схема преобразователя и временные диаграммы, поясняющие его работу.

Преобразователь содержит (фиг.1) универсальный регистр 4, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и 3, информационный и тактовый входы 4 и 5, тактовый и информационный выходы 6 и 7 о

Преобразователь работает следующим образом

На вход 4 преобразователя поступают данные в коде Манчестер 2 (фиг„2а)е На вход 5 поступает последовательность тактовых импульсов, период следования которых равен 4/16 длительности битовой посылки кода Манчестер 2 (на фиг„26 для простоты изображен каждый четвертый импульс этой последовательности).

При отсутствии связи выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 с входом управления режимом работы регистра 1 в режиме синхронного сдвига задержка входного сигнала по первому выходу составляет J/2 длительности битовой посылки, по второму выходу - 3/4 длительности, по третьему выходу - длительность битовой посылки. При одинаковых логических уровнях сигналов на первом и втором входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 с выхода этого элемента на вход управления режимом работы регистра J поступает логический О, обеспечивающий последовательный синхронный сдвиг входного сигнала в регистре 1„ При разны логических уровнях сигналов на входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 с выхода этого элемента на управляющий вход регистра 1 поступает сигнал, обеспечивающий параллельную синхронную запись (фиг02в). По фронту тактового импульса в регистр I заносится входной сигнал (фиг.2а)0Вид сигнала на втором выходе регистра 1 представлен на фиг.2д.

На третьем выходе регистра 1, являющемся информационным выходом 7 преобразователя, появляются данные в коде без возврата к нулю (фиг„2е).

0

5

0

5

0

5

0

5

0

5

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2 суммирует по модулю два сигналм с первого и третьего выходов регистра 1, и на выходе 6 преобразователя формируются тактовые импульсы (фиг.2ж).

Рассмотрим преобразование первых бит последовательности 110100 (фиг„2а).

В исходном состоянии все разряды регистра 1 установлены в единичное состояние. Через восемь тактов входных тактовых импульсов после поступления на вход 4 преобразователя второй половины первого бита (фиг«2а) на первом выходе регистра 1 появится сигнал логического О (фиг.2г) и на выходе 6 преобразователя сформируется сигнал логической 1 (фиг.2ж). Еще через четыре тактовых интервала сигнал логического О появится на втором выходе регистра 1 (фиг.2д). При этом на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 сформируется сигнал логической 1 (фиг„2в), переводящий регистр 1 в режим параллельной записи. Очередной тактовый импульс записывает во все разряды регистра 1 единичное состояние первой половины второго бита (фиг.2а, в, г, д, е). На третьем выходе регистра 1 формируется преобразованное значение прижимаемого бита (фиго2е). На выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и 3 устанавливается нулевой логический уровень (фиг.2в,ж), и регистр 4 переводится в режим последовательного сдвига информации,, Далее работа преобразователя повторяется.

Формула изобретения

I

Преобразователь биимпульсного кода в бинарный, содержащий первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является тактовым выходом преобразователя, отличающийся тем, что, с целью упрощения преобразователя, в него введен регистр, тактовый вход которого является тактовым входом преобразователя, первый и второй выходы регистра соединены с первыми входами соответственно первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом регистра, параллельные и последовательный информационные входы которо516513836

го Ъбъединены и являются информацией- входами первого и второго элементов ным входом преобразователя, третий ИСКЛМАЩЕЕ ИЛИ и является информа- выход регистра соединен с вторыми ционным выходом преобразователя.

Фиг.2

| Преобразователь кода | 1986 |

|

SU1325707A1 |

| БЕСКОНТАКТНАЯ ИНДУКЦИОННАЯ МУФТА | 0 |

|

SU372624A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-23—Публикация

1989-04-11—Подача