Изобретение относится к вычислительной технике, предназначено для . вычисления дискретного преобразования Фурье и процедуры цифровой фильтращлг и может быть использовано в системах цифровой обработки сигналов.

Целью изобретения является -упрощение устройства за счет снижения аппаратурных затрат на формирование весовых коэффициентов.

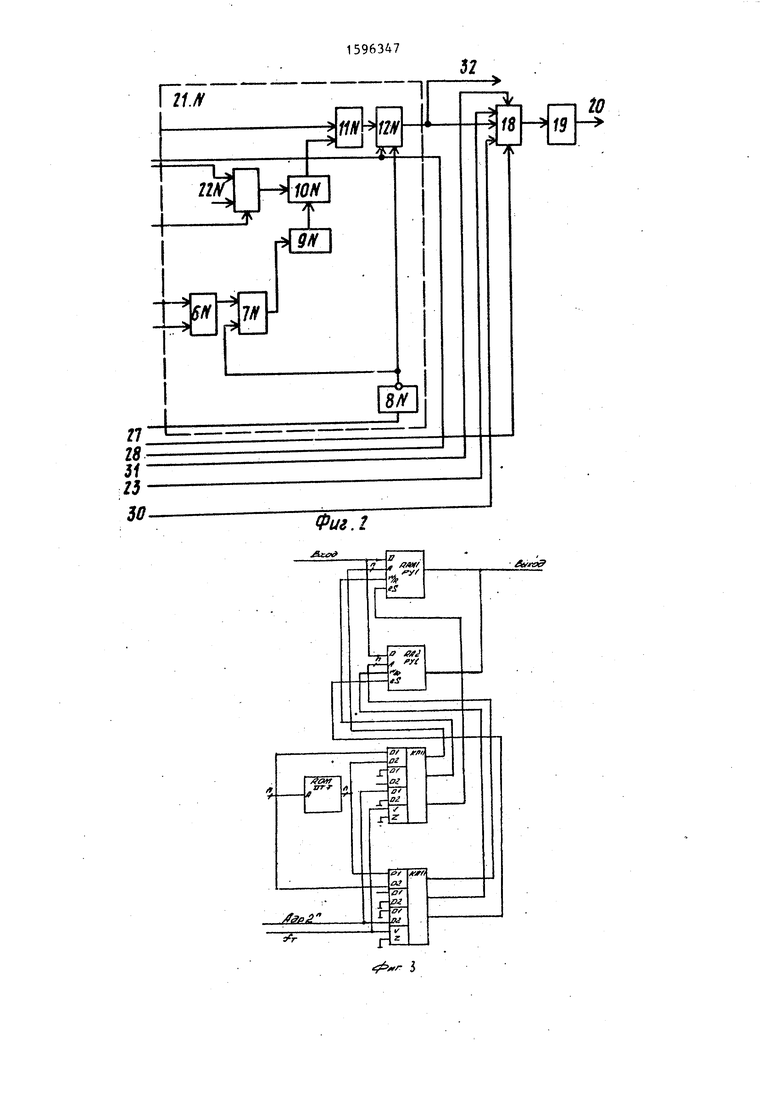

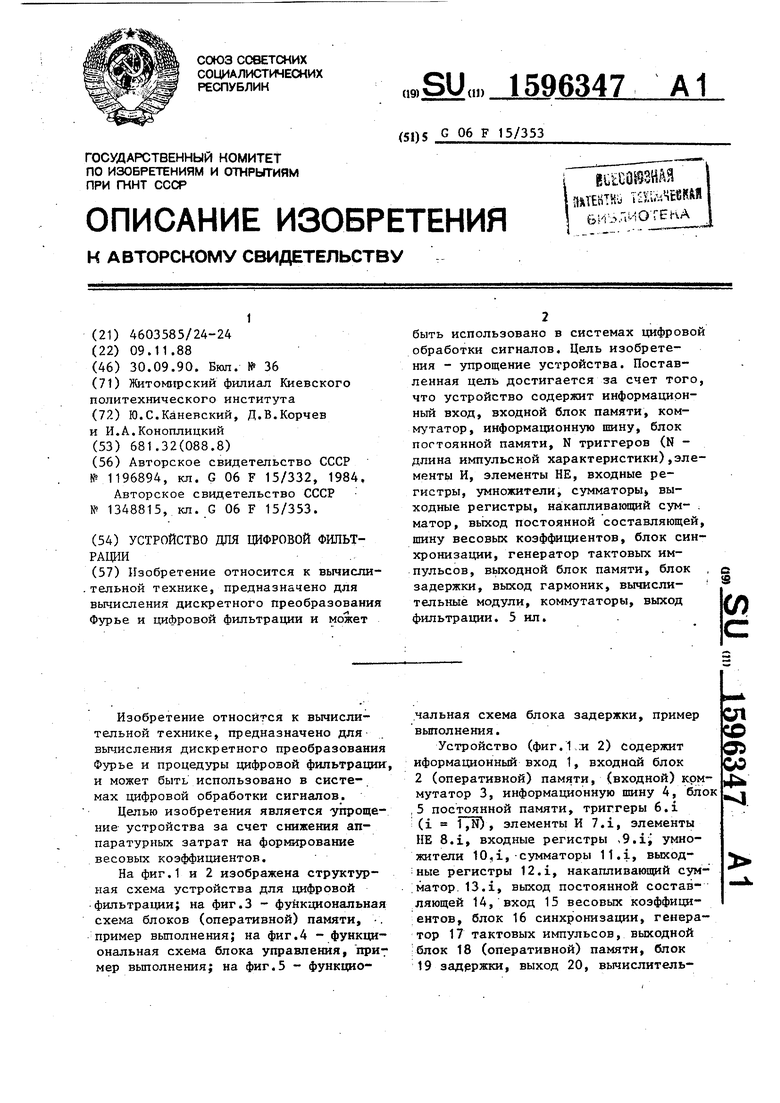

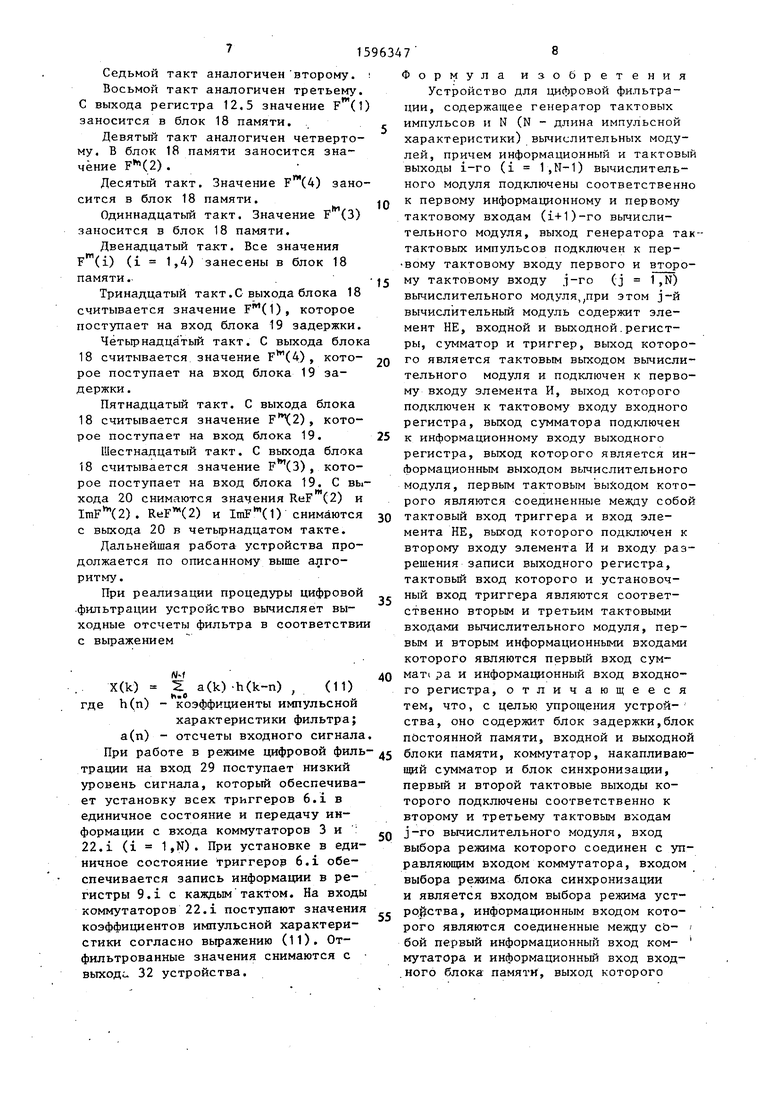

На фиг.1 и 2 изображена структурная схема устройства для цифровой фильтрации; на фиг.З - функциональная схема блоков (оперативной) памяти, -. пример вьшолнения; на фиг.4 - функциональная схема блока управления, при мер выполнения; на фиг.5 - функциочальная схема блока задержки, пример выполнения.

Устройство (фиг.1 ;и 2) содержит иформационный вход 1, входной блок 2 (оперативной) памяти, (входной) коммутатор 3, информационную шину 4, бло ,5 постоянной памяти, триггеры 6.1 :(i 1,N), элементы И 7.1, элементы НЕ 8.1, входные регистры ,9.1 умножители 10,1, сумматоры 11.1, выход;ные регистры 12.1, накапливающий сум;матор. 13.1, выход постоянной составляющей 14, вход 15 весовых коэффициентов, блок 16 синхронизации, генератор 17 тактовых импульсов, выходной :блок 18 (оперативной) памяти, блок 19 задэржки, выход 20, вычислитель315963ные модули 21,i, коммутаторы 22.i, входы 23 и 24 блока 16, выходы 25 - 28 блока 16, вход 29 выбора режима | устройства, выход 30 блока 16, вы ход 31 блока 16, выход 32 фильтрации. Устройство при вычислений ДПФ работает следующим образом. Устройство вычисляет следующее выражение:

N-f

,W;

F (k) (n) -W, k 0,N-1 , (1)

ii«0 где a(n) - элементы исходного вектора Са„ 7 размерности N; F(k) - элементы выходного вектора коэффициентов Фурье f размерности N; W ., - весовые коэффициенты; .5Г(Г W, е ., 2S m - номер входной последователь- ности; п - размерность преобразования, заданная простым числом. Запишем выражение (1) в следующем

N-1

.«k.

- ) ReW {

(2)

t:0 ImF(k) ) IH,W где Re - действительная часть комплексного числа; Im - мнимая часть комплексного числа. Найдем результат суммарного Fp(k вычисления действительных и мнимых составляющих спектра действительной последовательности, т.е. сумЬдму (2) и (3) ) - 1 з. Vl , где Wc ImW Ч .

Выражение (4) можно вычислять еле дующим образом:

F7(k) - а-(о) + ), k - f7iPl;(5)

F(k) еГ(гО (6) 5 2Q

k 1, (N-1)/2 (9) ImF(k) 0,5 FlJCk) - F(N-k) , 7 ) . Основные вычислительные затраты приходятся на выражение (6). Записав его в матричном виде и вьтолнив соответствующие перестановки, получим при N 5: В выражении (8) выполнено приведение индексов Весовых коэффициентов по модулю 5. Циклическая структура . матрицы позволяет значительно снизить затраты на формирование весовых козф::фициентов и вычисление. После вычисления выражений (5), (6) и (7) .... .ч. можно произвести разделение действительных и мнимых частей спектра действительного массива по формулам: ) «05 F(k) + ) k 1,(N-1)/2 (10) Рассмотрим на примере вычисления спектра действительного массива для N 5. Вудем полагать, что информаци; во все регистры и триггеры записывается положительным перепадом синхросигнала. На вход 22 подается верхний логический уровень, которьй разрешает прохождение информации с входа входного коммутатора 3 и с входов коммутатора 22.1 (i 1,N). Для данного случая порядок следования весовых коэффициентов на входах умножителей согласно (8) следующий:Будем описывать работу устройств относительно инверсной синхронизации Входные отсчеты поступают непрерывным потоком на вход 1 устройства с частотой тактового генератора 17. Блок 2 оперативной памяти производит переупорядочение последовательности входных отсчетов. Триггеры 6. синхронизируются положительным пере падом прямого синхросигнала, все остальные узлы - положительным пере падом инверсного синхросигнала. С в хода генератора 17 тактовых импульсов поступает последовательность прямоугольных импульсов типа меандра . При описании работы информация блоках устройства соответствует вре мени до прихода положительного фро.н синхросигнала. Первьш такт.- На входе 1 устройст ва значение ) . На шине 4 - а (О Триггеры 6.1 (i 1,5) обнулены. На информационном входе триггера 6.1 единичное значение, которое через половину такта -записывается в триггер 6.1, на входе триг гера 6.1 устанавливается нулевое значение с выхода 26 блока 16. На ши не 15 весовых коэффициентов значение W, которое поступает с выхода блока 5 постоянной памяти. С выхода триггера 6.1 единичное значение разрешает поступление инверсного синхро сигнала для записи а (0) в регистр м / хч 9.1. С выхода 28 блока 16 поступает сигнал запрета на регистры 12.1. Второй такт. На входе 1 значение (1); на шине 4 - (1). В середине такта единичное значение переписывается из триггера 6.1 в триггер 6.2. На входе триггера 6.1 нулевое значение. На входе 15 значение w. В регистре 9.1 записано значение ); на выходах сумматора 11.1 и умножителя 10.1 - значение ), В накапливающем сумматоре 13 значение d(0). Третий такт. На входе 1 - (2)j на шине А - (2). В середине такта -единичное значение из триггера 6.2 записывается в триггер 6.3, что разрешает запись информации в регистр 9.3,на входе триггера 6.1 нулевое значение. В регистрах 9.1 и 9.2 находятся а (О) и (1) соответственно. На выходах умножителей 10.1 и 10; 2 значения (0) и ) + (1) W соответственно. На выходе регистра 12.1 значение а (0). В сумматоре 13 значение (0) + . , етвертый такт. На входе 1 ). На шине 4 - а (4). В середине такта единичное значение из триггера 6.3 записывается в триггер 6.4,что разрешают запись информации в регистр 9.4, на входе триггера 6.1 нулевое значение. На шине 15 значение W. В регистрах 9.1, (0), а (1), 9.2 и 9.3 значения а соответственно. На выходах умножителей 10.1, 10.2, 10.3 значения а (0),(1) W и a(2)w соответственно. На выходах сумматоров 11.1, 11.2 и 11.3 значения ), ) + а (1) W% ) + W + + (2) W соответственно. На выходе регистров 12. 1 и 12.2 значения ), а (0) + а (1) W соответственно. В накапливающем сумматоре 13 значение а (0) -i- ) + а (2). Пятый такт. На входе 1 - -а (4); на шине 4 - ). В середине такта единичное значение из триггера 6.4 записывается в триггер 6.5. На входе триггера 6.1 появляется единичное значение. На шине 15 значение W. В регистрах 9.1 (1 1.4) значения ), ), а (2) и (4) соответственно. На выходах умножителей 10.1, 10.2, 10.3 и 10.4 значения ), (1) W,(2) W и (4) W соответственно. На выходах сумматоров 11.1 (1 1,4) значения а (0) , а (О) + ) V7, ) + а (1) W + ( + (2) WS ) + + а + (4) W соответственно. В сумматоре 13 значение (0) + а (1) + + а (2) + а (4). - Шестой такт аналогичен первому. Обработка (т+1)-го массива производится по описанному вьш1е алгоритму. В накапливающем сумматоре 13 значение (0) а-СО) + ) + а (2),+ а (4) + ) , которое считывается во внешнее устройство. 15 Седьмой такт аналогиченвторому, Восьмой такт аналогичен третьему. С выхода регистра 12.5 значение F(t заносится в блок 18 памяти. Девятый такт аналогичен четвертому. В блок 18 памяти заносится значение (2) . Десятый такт. Значение Р (4) заносится в блок 18 памяти. Одиннадцатый такт. Значение ) заносится в блок 18 памяти. Двенадцатый такт. Все значения F (i) (i 1,4) занесены в блок 18 памяти. Тринадцатый такт.С выхода блока 18 считывается значение F(1), которое поступает на вход блока 19 задержки. Четырнадцатый такт. С выхода блока 18 считывается значение (4) , которое поступает на вход блока 19 задержки . Пятнадцатый такт. С выхода блока 18 считывается значение ) , которое поступает на вход блока 19. Шестнадцатый такт. С вькода блока 18 считывается значение (3) , которое поступает на вход блока 19. С выхода 20 снимаются значения ReF (2) и (2) . ReF(2) и ) снимаются с выхода 20 в четырнадцатом такте. Дальнейшая работа устройства продолжается по описанному выше алгоритму. При реализации процедуры цифровой .фильтрации устройство вычисляет выходные отсчеты фильтра в соответствии с выражением X(k) i a(k)-hCk-n) , (11) где h(n) - коэффициенты импульсной характеристики фильтра; а(п) - отсчеты входного сигнала При работе в режиме цифровой филь трации на вход 29 поступает низкий

уровень сигнала, который обеспечивает установку всех триггеров 6.1 в единичное состояние и передачу информации с входа коммутаторов 3 и : 22.1 (1 1,N). При установке в единичное состояние триггероэ 6.1 обеспечивается запись информации в регистры 9.1 с каждым тактом. На входы коммутаторов 22.1 поступают значения коэффициентов импульсной характеристики согласно вьфажению (11). Отфильтрованные значения снимаются с выхода 32 устройства.

первый и второй тактовые выходы которого подключены соответственно к второму и третьему тактовым входам

j-ro Бьиислительного модуля, вход

выбора режима которого соединен с управляющим входом коммутатора, входом выбора режима блока синхронизации и является входом выбора режима устррйства, информационным входом которого являются соединенные между сЬ- / бой первый информационный вход коммутатора и информационный вход вход.ного блока памяти, выход которого 7 Формула изобретения Устройство для цифровой фильтрации, содержащее генератор тактовых импульсов и N (N - длина импульсной характеристики) вычислительных модулей, причем информационный и тактовый выходы i-ro (i 1,N-1) вычислительного модуля подключены соответственно к первому информационному и первому тактовому входам (i+1)-ro вычислительного модуля, выход генератора так-тактовых импульсов подключен к первому тактовому входу первого и второму тактовому входу J-ro t,j 1 ,N) вычислительного модуля,,при этом j-й вычислительный модуль содержит элемент НЕ, входной и выходной.регистры, сумматор и триггер, выход которого является тактовым выходом вычислительного модуля и подключен к первому входу элемента И, выход которого подключен к тактовому входу входного регистра, выход сумматора подключен к информационному входу выходного регистра, выход которого является информационным выходом вычислительного модуля, первым тактовым выходом которого являются соединенные между собой тактовый вход триггера и вход элемента НЕ, выход которого подключен к второму входу элемента И и входу разрешения записи выходного регистра, тактовый вход которого и установочный вход триггера являются соответственно вторым и третьим тактовыми входами вычислительного модуля, первым и вторым информационными входами которого являются первый вход суммате ра и информационный вход входного регистра, отличающееся тем, что, с целью упрощения устройства, оно содержит блок задержки,блок постоянной памяти, входной и выходной блоки памяти, коммутатор, накапливающий сумматор и блок синхронизации.

подключен к второму информационному входу коммутатора, выход которого подключен к второму информационному входу j-ro вычислительного модуля и . информационному входу накапливающего сумматора, тактовый вход которого соединен с входами управления записью считыванием входного и выходного блоков памяти, тактовым входом блока синхронизации и подключен к выходу генератора тактовых импульсов, третий тактовый выход блока синхронизации подключен к установочному входу накапливающего сумматора, выход которого является выходом постоянной составляющей устройства, выходом гармоник которого является выход блока задержки, вход которого подключен к выходу выходного блока памяти, первый и второй адресные входы которого соединены соответственно с первым и вторым адресными входами входного блока памяти и подключены соответственно к первому и второму информационным вьпсодам блока синхронизации.

третий информационный выход которого подключен к третьим адресным входам входного и выходного блоков памяти и адресному входу блока постоянной памяти, выход которого подключен к третьему информационному входу j-ro вычислительного модуля, информационный выход N-ro вычислительного модуля подключен к информационному входу выходного блока памяти и является выходом фильтрации устройства, при этом j-й вычислительный модуль содержит умножитель и коммутатор, выход,, которого подключен к первому входу умножителя, выход которого подключен к второму входу сумматора, выход входного регистра подключён к второму входу умножителя, первый информационный вход умножителя является третьим информационным входом вычислительного модуля, входом выбор режима которого является управляющий вход коммутатора, второй информационный .вход которого является входом задания константы устройства.

Фиг.1

Леа

4w«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой фильтрации | 1988 |

|

SU1545230A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1988 |

|

SU1575202A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1721610A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1348815A1 |

| Устройство для цифровой обработки сигналов | 1989 |

|

SU1652981A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1989 |

|

SU1781684A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1577072A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1989 |

|

SU1645967A1 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1989 |

|

SU1619299A1 |

Изобретение относится к вычислительной технике, предназначено для вычисления дискретного преобразования Фурье и цифровой фильтрации и может быть использовано в системах цифровой обработки сигналов. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет того, что устройство содержит информационный вход, входной блок памяти, коммутатор, информационную шину, блок постоянной памяти, N триггеров (N - длина импульсной характеристики), элементы И, элементы НЕ, входные регистры, умножители, сумматоры, выходные регистры, накапливающий сумматор, выход постоянной составляющей, шину весовых коэффициентов, блок синхронизации, генератор тактовых импульсов, выходной блок памяти, блок задержки, выход гармоник, вычислительные модули, коммутаторы, выход фильтрации. 5 ил.

--f.

SL. pf

гв

26

Фиг. 5

| Устройство для цифровой фильтрации | 1984 |

|

SU1196894A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-30—Публикация

1988-11-09—Подача