Изобретение относится к вычислительной технике, предназн 1чено для вычисления дискретною преобразования Лурье и процедуры ииФровсй фильтрации и может быть использовано в системах цифровой обработки сигналов. Мелью изобретения является упрощение устройства за счет снижения аппаратурных затрат на формирование весовых коэффициентов.

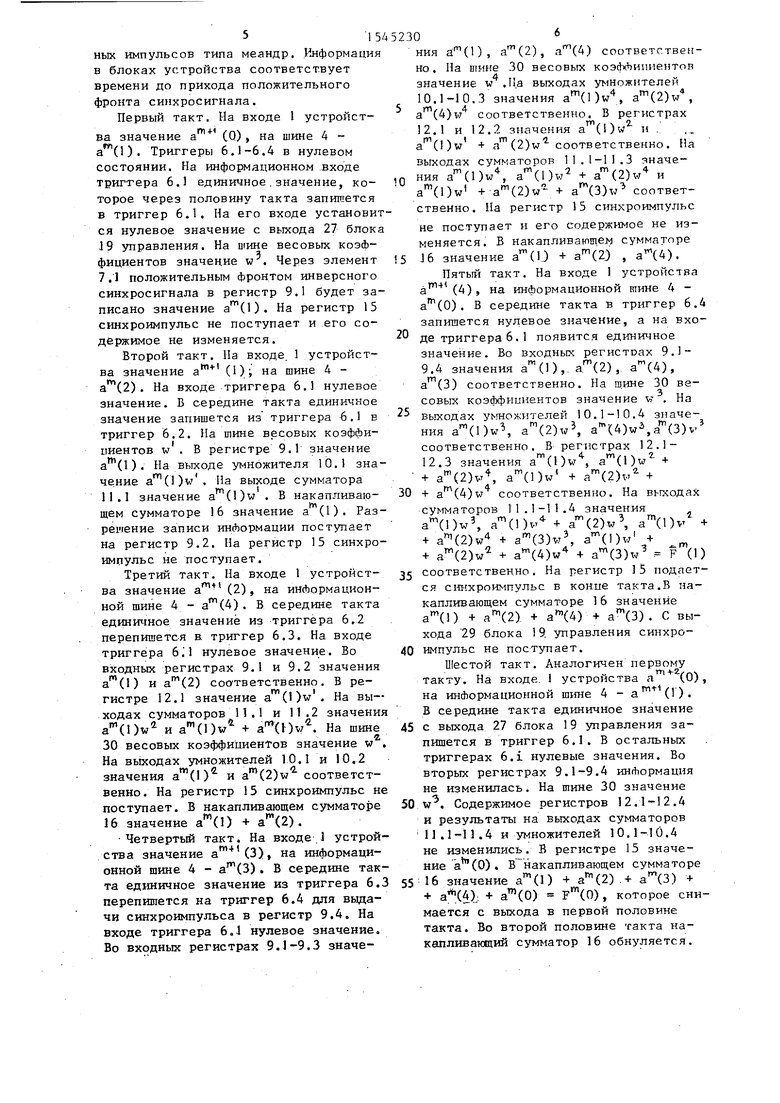

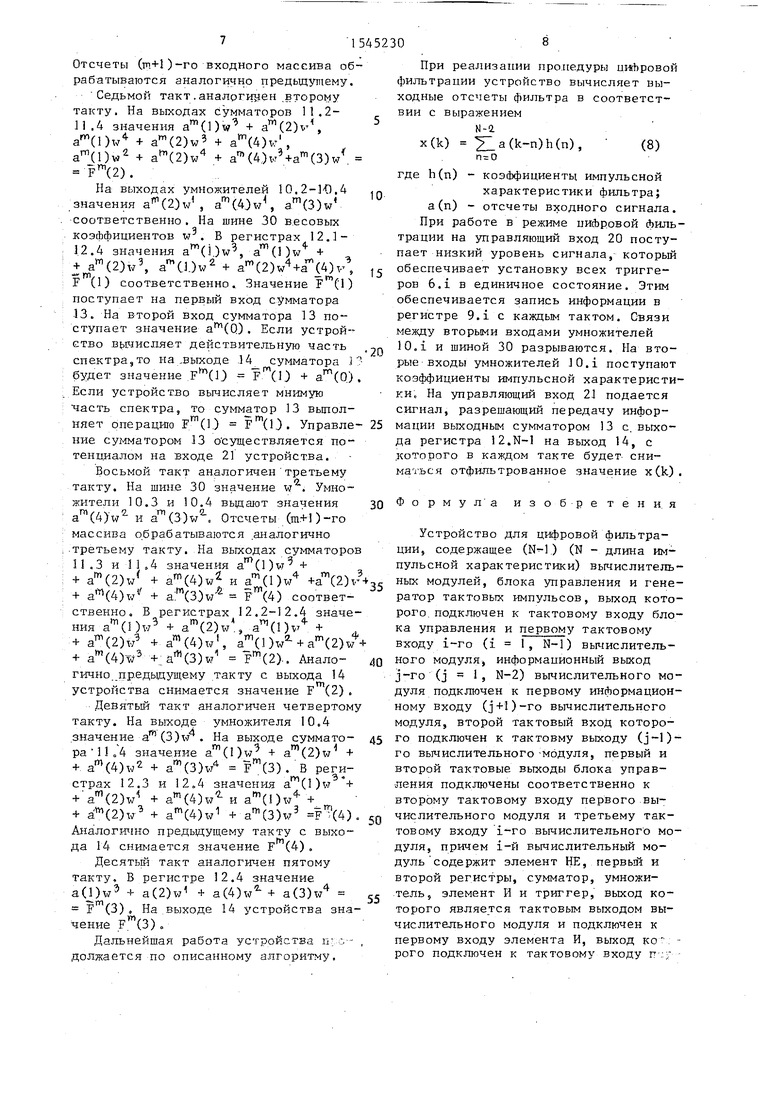

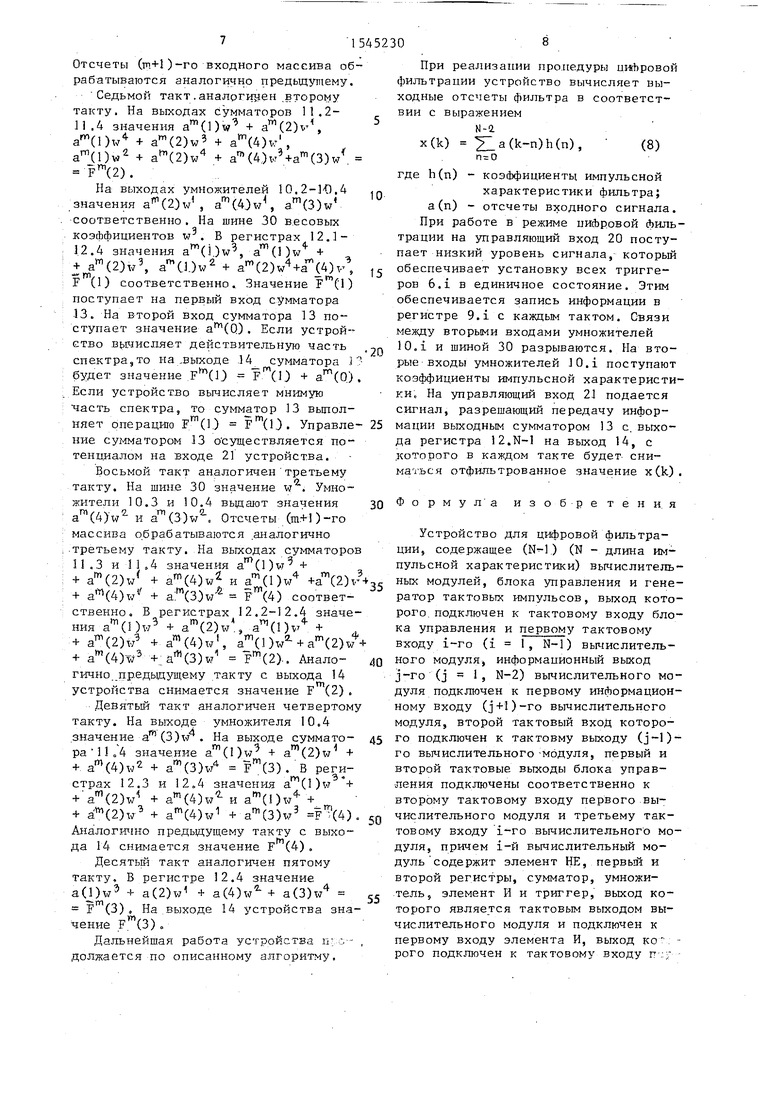

На Фиг.1 и 2 изображена структурная схема устройства для цифровой фильтрации; на фиг.3 - Функциональная схема блока оперативной памяти; на фиг.4 - функциональная схема блока управления.

Устройство (фиг.1 и 2) содержит информационный вход 1, блок 2 оперативной памяти, коммутатор 3, информационную шину 4, блок 5 постоянной памяти (весовых коэффициентов), триггеры 6.i d I, N-1), элементы 2 И

7.1, элементы НГ 8.1, входные регистры 9.1, умножители ЮЛ, сумматоры ll.i, выходные регистры 12.i, выходной сумматор 13, информационный выход 14, регистр 15 первого отсчетэ, накапливающий сумматор 16, выход 17 постоянной составляющей, генератор 18 тактовых импульсов, блок 19 управления, первый вход 20 задания режима устройства, второй вход 21 задания режима устройства, тактовый вход 22 блока J9 управления, такто ьи выход 33 блока 19 управления, обнуляющий выход 24 блока 19 управления, вход 25 управления режимом блока 19 упртзле- ния, адресный выход 26 блока 19 управления, тактовый выход Г7 блок т 19 управления, вычислительные МОДУпи 28.1, тактовый выход 29 блока 19 yi - равления, шина 30 весовых ктгМч-чщрн- тов, второй адресный выход 31 о-ч 1 9 управления.

(Л

С

Работу устройства при вычислении дискретного преобразования Лурье.

Устройство вычисляет следующее выражение :

N-I

П 0

го / л a (n)wN

k - О, N-l,(1)

FW(k)

w,

nk

де а (п) - элементы исходного действительного вектора jg размерности N; элементы выходного вектора коэффициентов Фурье размерности N;

весовые коэффициенты;15

27 )ТГ .ГТ1

е , j лН;

номер входной последовательности;

N - размерность преобразова- 20 ния, заданная простым числом.

Представим выражение (1) в следуюем виде:

1М25

Хат(п),(2)

«N

m

Ло)

FW(k)

-.m

где )

Fm(k)

(3)

am(0) + Fm(k),k-ltN-l,

i

определяется выражением N-1k

,k-l,N-l. (4).

Запишем выражение (4) в матричном виде и, выполнив соответствующие перестановки з , получим для N 5

В выражении (5) выполнено приведение индексов весовых коэффициентов по Модулю 5.

Циклическая структура матрицы весовых коэффициентов в выражении (5) позволяет значительно сократить аппаратурные затраты на их формирование.

Для действительных входных данных выражение (1) можно свести к виду (3

(6) (7)

ReFm(k)

m

(k)

am(0) + ReFro(k), (k) .

Слагаемые ReFm(k) и IJ (k) в выражениях (6) и (7) можно привести к

виду (5) с циклическими матрицами j и соответственно.

Очевидно, что разница между вычис)

jg

15

20

25

.

30

35

40

45

50

55

Т-, hrt,лением значений ReF (k)

и

(И)

Т Р rtl состоит в том, что при вычислении

действительной части на вторые входы умножителей- 10.1 будут подаваться действительные части весовых коэФЛн- циентов, а при вычислении мнимой части - мнимые. Порядок следования входных, выходных данных и весовых коэффициентов идентичен. Поэтому в дальнейшем будет считать ), Fm(n), wn действительными числами. Рассмотрим на примере вычисление одной из частей спектра для N 5. Информация во все регистры и триггеры записывается положительным перепадом синхро сигнала. На вход 20 подается верхний логический уровень, который разрешает прохождение информации с первого входа коммутатора 3 на информационную шину 4. Этот режим соответствует вычислению ДПФ. При вычислении свертки на вход 20 поступает нижний логический уровень. При этом в режиме вычисления ДПФ верхний логический уровень нп входе 21 соответствует вычислению косинусных составляющих, а нижний логический уровень - мнимых. Для косинусных составляющих сумматор 13 вычисляет сумму операндов на его входах, а с блока 5 на шину 30 поступают действительные значения весовых коэффициентов. При вычислении мнимых составляющих сумматор 13 осуществляет передачу на выход операнда с выхода регистра 12.N-1, а с блока 5 поступают мнимые составляющие весовых коэффициентов. Переключение составляющих коэффициентов производится старшим адресом выхода 31, который формируется вторым управляющим входом 21.

Будем описывать работу устройства относительно инверсной синхронизации. Входные отсчеты поступают непрерывным потоком на вход I устройства с частотой тактового генератора 18. Блок 2 оперативной памяти производит переупорядочивание последовательности входных отсчетов. Триггеры 6.1 синхронизируются положительным гЬронтом прямого синхросигнала, все остальные регистры - положительным фронтом инверсного синхросигнала. С выхода генератора 18 тактовых импульсов поступает последовательность прямоугопь51 5

ных импульсов типа меандр. Илформааия в блоках устройства соответствует времени до прихода положительного фронта синхросигнала.

Первый такт. На входе I устройства значение ат+ (0) , на шине 4 - 3(1). Триггеры 6.1-6.4 в нулевом состоянии. На информационном входе триггера 6.1 единичное значение, которое через половину такта запишется в триггер 6.1. На его входе установится нулевое значение с выхода 27 блока 19 управления. На шине весовых коэффициентов значение w . Через элемент 7.1 положительным Фронтом инверсного синхросигнала в регистр 9.1 будет записано значение ат(1). На регистр 15 синхроимпульс не поступает и его содержимое не изменяется.

Второй такт. Па входе 1 устройства значение (1); на шине 4 - а (2). На входе триггера 6.1 нулевое значение. В середине такта единичное значение запишется из триггера 6.1 Е

триггер 6.2. На шине весовых коэффициентов w . В регистре 9.1 значение а (1). Па выходе умножителя 10.1 значение 3(1)w . На выходе сумматора 11.1 значение a (l)w . В накапливающем сумматоре 16 значение а (1). Раз- речение записи информации поступает на регистр 9.2. На регистр 15 синхроимпульс не поступает.

Третий такт. На входе 1 устройства значение (2), на инЛормацион- ной шине 4 - aw(4). В середине такта единичное значение из триггера 6.2 перепишется в триггер 6.3. На входе триггера 6.1 нулевое значение. Во входных регистрах 9.1 и 9.2 значения ) и ат(2) соответственно. В регистре 12.1 значение )w . На выходах сумматоров 11.1 и 11.2 значения am(l)wu и am(l)w + 3(1 )w. На шине 30 весовых коэффициентов значение w . На выходах умножителей 10.1 и 10.2 значения ат(1)4 и am(2)wi соответственно. На регистр 15 синхроимпульс не поступает. В накапливающем сумматоре 16 значение ат(1) + ат(2).

Четвертый такт. На входе 1 устройства значение (3), на информационной шине 4 - ). В середине такта единичное значение из триггера 6.3 перепишется на триггер 6.4 для выдачи синхроимпульса в регистр 9.4. На входе триггера 6.J нулевое значение. Во входных регистрах 9.1-9.3 значе2 Ю6

ния ат(1), ат(2), лгп(4) COPTIUM г гнен- но. На шине 30 весовых коэ(«Ъипнентмп значение w .Па выходах умножителей 10.1-10.3 значения am(l)w4, am(2)w4, a (4)w соответственно. В регистрах 12.1 и 12.2 значения и a (I)w + arn(2)w соответственно. На выходах сумматоров 11.1-11.3 тначе0 ния , 3(1 )w2 + am(2)w4 и

am(l)w + a T1(2)w 2 + ам(3)иэ соответственно. На регистр 15 синхроимпульс не поступает и его содержимое не изменяется. В накапливающем сумматоре

5 16 значение am(l) + am(2) , a(4).

Пятый такт. На входе 1 устройства а|Т14(4), на информационной тине 4 - 3(0). В середине такта в триггер 6.4 запишется нулевое значение, а на вхо де триггера 6.1 появится единичное значение. Во входных регистрах 4.1- 9.4 значения а (1), а (2), ат(4), а (3) соответственно. На шине 30 весовых коэффициентов значение v . На

выходах умноэмпелей 10.1-10.4 знлчеР 1/1Ч Ч /0 fn Y / / 1

ния a (l)w5, a (2)w% a (4)wi,a (3)v соответственно. В регистрах 12.1- 12.3 значения am(l)w4, am(l)w7 + + aw(2)v, 3(1 )w + am(2)w2 +

0 + arri(4)w соответственно. На выходах сумматоров М.1-11.4 значения am(l)w3, + am(2)w3, am(l)v + + ani(2)w4 + ) 3, am(l)wp + + aM(2)wa + aw(4)w4 + aw(3)w3 F (1)

5 соответственно. На регистр 15 подастся синхроимпульс в конце так та.R накапливающем сумматоре 16 значение ат(1) + ат(2) + а|1 (4) + ат(3) . С вы- хода 29 блока 19 управления синхро0 импульс не поступает.

Шестой такт. Аналогичен первому такту. На входе 1 устройства а (О), на информационной шине 4 - агт11 1(1). В середине такта единичное значение

5 с выхода 27 блока 19 управления запишется в триггер 6.1. В остальных триггерах 6.1 нулевые значения. Во вторых регистрах 9.1-9.4 информация не изменилась. На шине 30 значение

1

0 w . Содержимое регистров 12.1-12.4 и результаты на выходах сумматоров 11.1-11.4 и умножителей 10.1-10.4 не изменились. В регистре 15 значение а (0). В накапливающем сумматоре

5 16 значение ат(1) + ат(2) + aw(3) + + 3(4) + ато(0) Fm(0), которое снимается с выхода в первой половине такта. Во второй половине такта на- капливаютий сумматор 16 обнуляется.

10

15

Отсчеты (тп + 1)-го входного массива обрабатываются аналогично предыдущему.

Седьмой такт.аналогичен второму такту. На выходах сумматоров 11.2- 11.4 значения am(l)w3 + am(2)v + am(2)w3 + , + a(2)w4 + a™ (4)(3)w F™(2) .

На выходах умножителей 10.2-Ш.4 значения arn(2)w( , am(4)w, am(3)w соответственно. На шине 30 весовых

a

коэффициентов w . В регистрах 12.1- 12.4 значения )w , am(l)w + + nam(2)w3, am(l)w2 + arn(2)w4+arn(4)v F (1) соответственно. Значение F (1) поступает на первый вход сумматора 13. На второй вход сумматора 13 поступает значение ). Если устройство вычисляет действительную час гь спектра,то на выходе 14 сумматора i будет значение Frn(l) Fm(l) + am(0 , Если устройство вычисляет мнимую часть спектра, то сумматор 13 выполняет операцию F (1) F (О. Управле- 25 мацин выходным сумматором ние сумматором 13 осуществляется потенциалом на входе 21 устройства.

Восьмой такт аналогичен третьему такту. На шине 30 значение w4. Умножители 10.3 и 10.4 выдают значения a™(4)w2 и am(3)wa. Отсчеты (га+1)-го массива обрабатываются аналогично третьему такту. На выходах сумматоров 11.3 и 11.4 значения am(l)w +

При реализации процедуры цифровой фильтрации устройство вычисляет выходные отсчеты фильтра в соответствии с выражением

N-u

x(k) XLa(k-n)h(n), (8)

где h(n) - коэффициенты импульсной характеристики Фильтра; а(п) - отсчеты входного сигнала. При работе в режиме цифровой Фильтрации на управляющий вход 20 поступает низкий уровень сигнала, который обеспечивает установку всех триггеров 6.1 в единичное состояние. Этим обеспечивается запись информации в регистре 9.1 с каждым тактом. Связи между вторыми входами умножителей 10.1 и шиной 30 разрываются. Па вторые входы умножителей 10.1 поступают коэффициенты импульсной характеристики. На управляющий вход 21 подается сигнал, разрешающий передачу инфор3 с выхода регистра 12.N-1 на выход 14, с которого в каждом тпкте будет сни- ма)Ь(ч отфильтрованное значение х(k).

30 Формула изобретения

20

+ am(2)wr+ am(4)w2 и )х/ +ат(2)Л35 + )1/ + am(3)w U Fm(4) соответственно. В регистрах 12.2-12.4 значе- ния am(l)w3 + am(2)w 3(1 )v + + a(2)v3 + am(4)w , am(l )wz + am(2)w4+ + am(4)w3 + )1 Fm(2) . Анало- 40 гично предыдущему такту с выхода 14 устройства снимается значение F (2).

Девятый такт аналогичен четвертому такту. На выходе умножителя 10.4

Устройство для цифровой Фильтрации, содержащее (N-l) (N - длина импульсной характеристики) вьгчислитель- ных модулей, блока управления и генератор тактовых импульсов, выход которого подключен к тактовому входу блока управления и первому тактовому входу 1-го (, N-1) вычислительного модуля, информационный выход j-го (j - 1, N-2) вычислительного модуля подключен к первому информационному входу (j+l)-ro вычислительного модуля, второй тактовый вход которо50

значение am(3)w4. На выходе суммато- 45 го подключен к тактовму выходу (j-1)- ра 11.4 значение + a (2)w + + am(4)w2 + am(3)w4 Fm(3) . В регистрах 12.3 и 12.4 значения + + am(2)v/ + am(4)w 2- и am(l)w4 + + am(2)w3 + am(4)w1 + am(3)w3 Fm(4) . Аналоптчно предыдущему такту с выхода 14 снимается значение F (4).

Десятый такт аналогичен пятому такту. В регистре 12.4 значение a(l)w3 + a(2)w + a(4) + a(3)w4 Fm(3). На выходе 14 устройства значение Fm(3) .

Дальнейшая работа устройств,, i должается по описанному алгоритму.

55

го вычислительного модуля, первый и второй тактовые выходы блока управления подключены соответственно к второму тактовому входу первого вычислительного модуля и третьему тактовому входу 1-го вычислительного модуля, причем 1-й вычислительный модуль содержит элемент НЕ, первый и второй регистры, сумматор, умножитель, элемент И и триггер, выход которого является тактовым выходом вычислительного модуля и подключен к первому входу элемента И, выход ко рого подключен к тактовому входу г

0

5

5 мацин выходным сумматором

При реализации процедуры цифровой фильтрации устройство вычисляет выходные отсчеты фильтра в соответствии с выражением

N-u

x(k) XLa(k-n)h(n), (8)

где h(n) - коэффициенты импульсной характеристики Фильтра; а(п) - отсчеты входного сигнала. При работе в режиме цифровой Фильтрации на управляющий вход 20 поступает низкий уровень сигнала, который обеспечивает установку всех триггеров 6.1 в единичное состояние. Этим обеспечивается запись информации в регистре 9.1 с каждым тактом. Связи между вторыми входами умножителей 10.1 и шиной 30 разрываются. Па вторые входы умножителей 10.1 поступают коэффициенты импульсной характеристики. На управляющий вход 21 подается сигнал, разрешающий передачу инфор3 с выхода регистра 12.N-1 на выход 14, с которого в каждом тпкте будет сни- ма)Ь(ч отфильтрованное значение х(k).

0

30 Формула изобретения

Устройство для цифровой Фильтрации, содержащее (N-l) (N - длина импульсной характеристики) вьгчислитель- ных модулей, блока управления и генератор тактовых импульсов, выход которого подключен к тактовому входу блока управления и первому тактовому входу 1-го (, N-1) вычислительного модуля, информационный выход j-го (j - 1, N-2) вычислительного модуля подключен к первому информационному входу (j+l)-ro вычислительного модуля, второй тактовый вход которо го подключен к тактовму выходу (j-1)-

го подключен к тактовму выходу (j-1)-

го вычислительного модуля, первый и второй тактовые выходы блока управления подключены соответственно к второму тактовому входу первого вычислительного модуля и третьему тактовому входу 1-го вычислительного модуля, причем 1-й вычислительный модуль содержит элемент НЕ, первый и второй регистры, сумматор, умножитель, элемент И и триггер, выход которого является тактовым выходом вычислительного модуля и подключен к первому входу элемента И, выход ко рого подключен к тактовому входу г

вого регистра, выход которого подключен к первому входу умножителя, выход которого подключен к первому входу сумматора, выход которого подключен к информационному входу второго регистра, выход которого является информационным выходом вычислительного модуля, первым информационным входом которого является второй вход сумматора, первый установочный вход триггера является первым тактовым входом вычислительного модуля, вторым тактовым входом которого является второй установочный вход триггера, информационный вход первого регистра является вторым информационным входом вычислительного модуля, третьим тактовым входом которого является вход элемента НЕ, выход которого подключен к второму входу элемента И и тактовому входу второго регистра, а второй вход умножителя является входом задания коэффициента вычислительного модуля, отличаю щеес я тем, что, с целью упрощения устройства, оно содержит блок памяти, блок постоянной памяти, коммутатор, сумматор, регистр и накапливающий сумматор, выход которого является выходом постоянной составляющей устройства, информационным входом которого являются соединенные между собой- первый информационный вход коммутатора и информационный вход блока памяти, выход которого подключен к второму ин0

5

0

5

0

5

формашюнному входу коммутатора, ны- ход которого подключен к второму информационному входу 1-го вычислительного модуля, вход задания козсМшциен- та которого подключен к выходу блока постоянной памяти, адресный вход которого подключен к первому адресному выходу блока управления, второй адресный выход которого подключен к адресному входу блока памяти, управляющий вход коммутатора соединен с пер- i вьм входом задания режима блока управления и является первым входом задания режима устройства, вторым входом задания режима которого являются соединенные между собой второй вход задания режима блока управления и - вход синхронизации сумматора, выход которого является информационным выходом устройства, третий тактовый выход блока управления подключен к тактовому входу регистра, выход которого подключен к первому информационному входу сумматора, второй инбормапион- ный вход которого подключен к информационному выходу (N-l)-ro вычислительного модуля, выход обнуления блока управления подключен к входу обнуления накапливающего сумматора, информационный вход которого соединен с информационным входом регистра и подключен к выходу коммутатора, а выход генератора тактовых импульсов подключен к тактовому входу накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой фильтрации | 1988 |

|

SU1577072A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1988 |

|

SU1575202A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1596347A1 |

| Устройство для цифровой обработки сигналов | 1989 |

|

SU1652981A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1388891A1 |

| Устройство для выполнения дискретного преобразования Фурье | 1987 |

|

SU1474673A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1348815A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1721610A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1989 |

|

SU1781684A1 |

| Устройство для вычисления дискретного преобразования Фурье и свертки | 1988 |

|

SU1573459A1 |

Изобретение относится к вычислительной технике, предназначено для вычисления дискретного преобразования и выполнения цифровой фильтрации и может быть использовано в сиситемах цифровой обработки сигналов. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет того, что в состав устройства входят N-1 (N - длина импульсной характеристики или размерность преобразования) вычислительных модулей, блок памяти, блок постоянной памяти, коммутатор, блок управления, генератор тактовых импульсов, накапливающий сумматор, сумматор, регистр и соответствующие связи между узлами устройства. 4 ил.

Выход

I

и;

С5

«mi

J. i

-EL

Ji

Mp

Г2

{

cmi

/г

ft/e

flw26

flw.J/

W г

ЧА

А А АА ( t

). 2J|l f l

«Ј.

(/Г2

УЗ

ffllF

1t 01 -

№

J

2

27

2S

h

| Устройство для цифровой фильтрации | 1984 |

|

SU1196894A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1348815A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1990-02-23—Публикация

1988-05-30—Подача