Изобретение относится к вычислительной технике, предназначено для вычисли ния одно и двумерного дискретного преобразования Фурье и процедуры цифровой фильтрации. Изобретение может быть использовано в системах цифровой обработки сигналов.

Целью изобретения является расширение функциональных возможностей устройства.

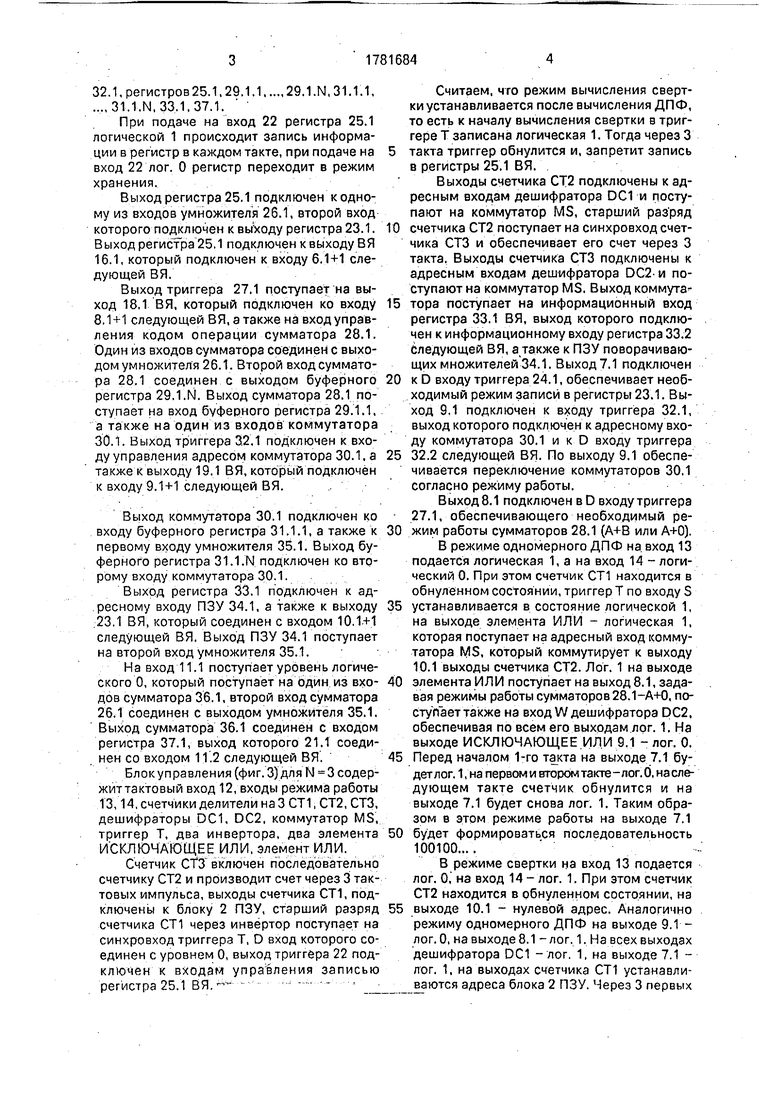

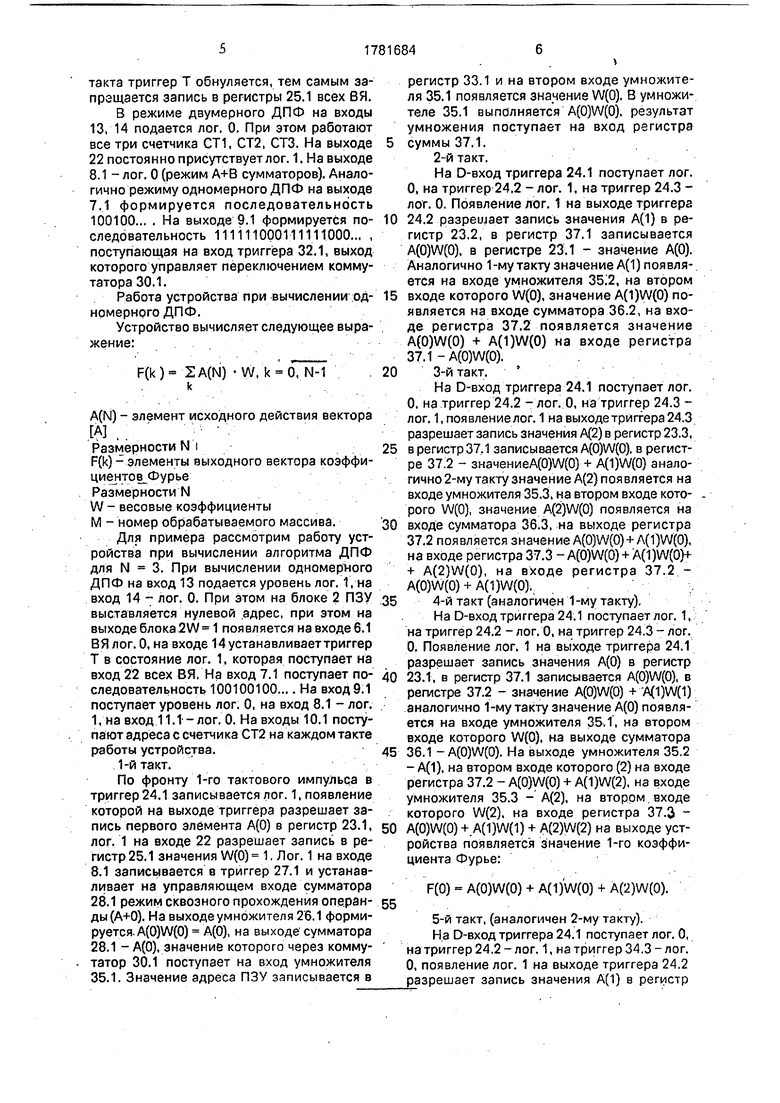

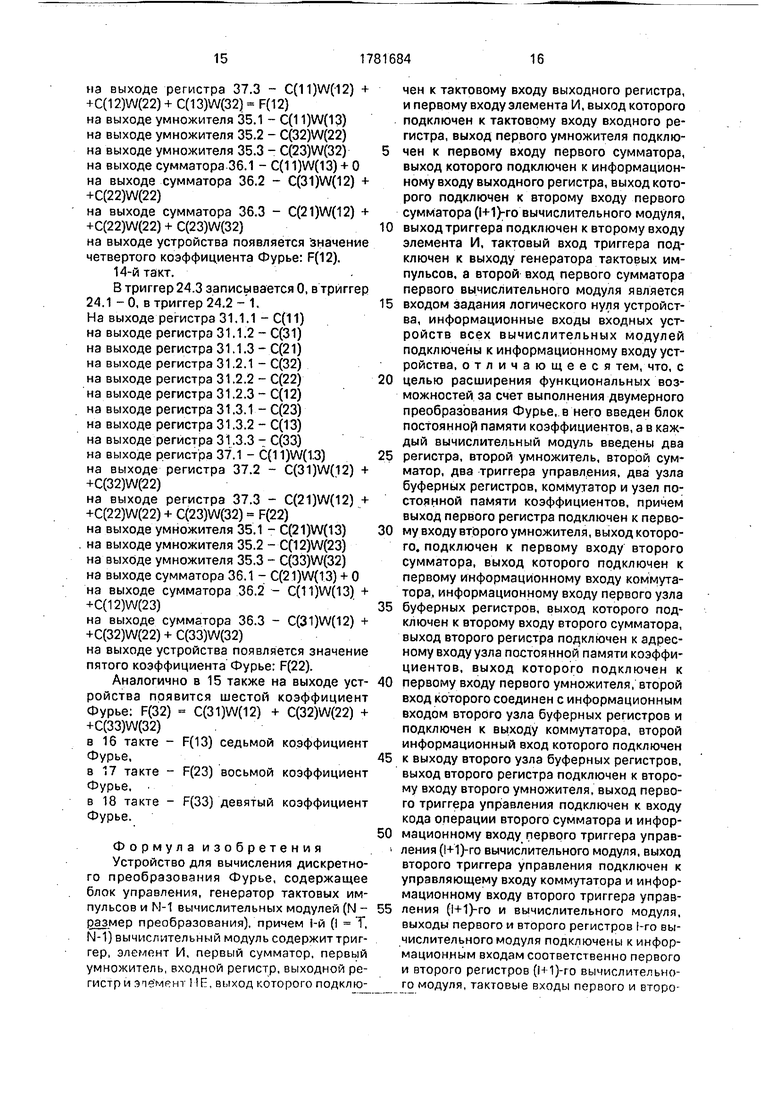

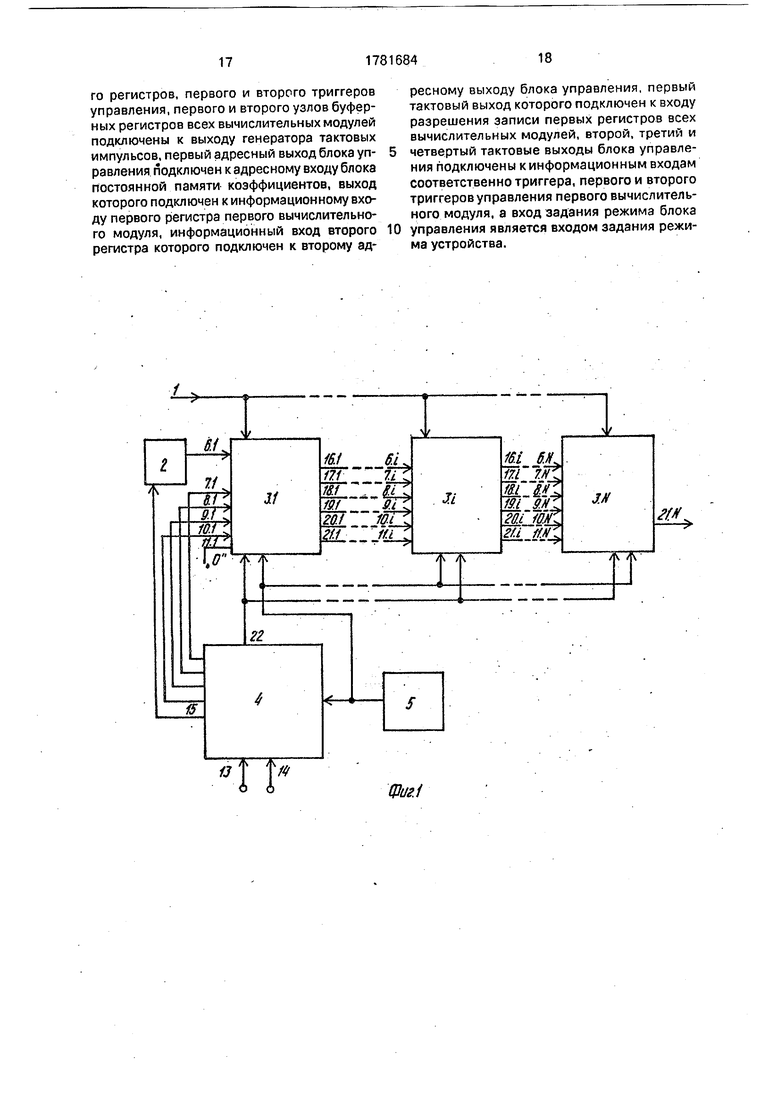

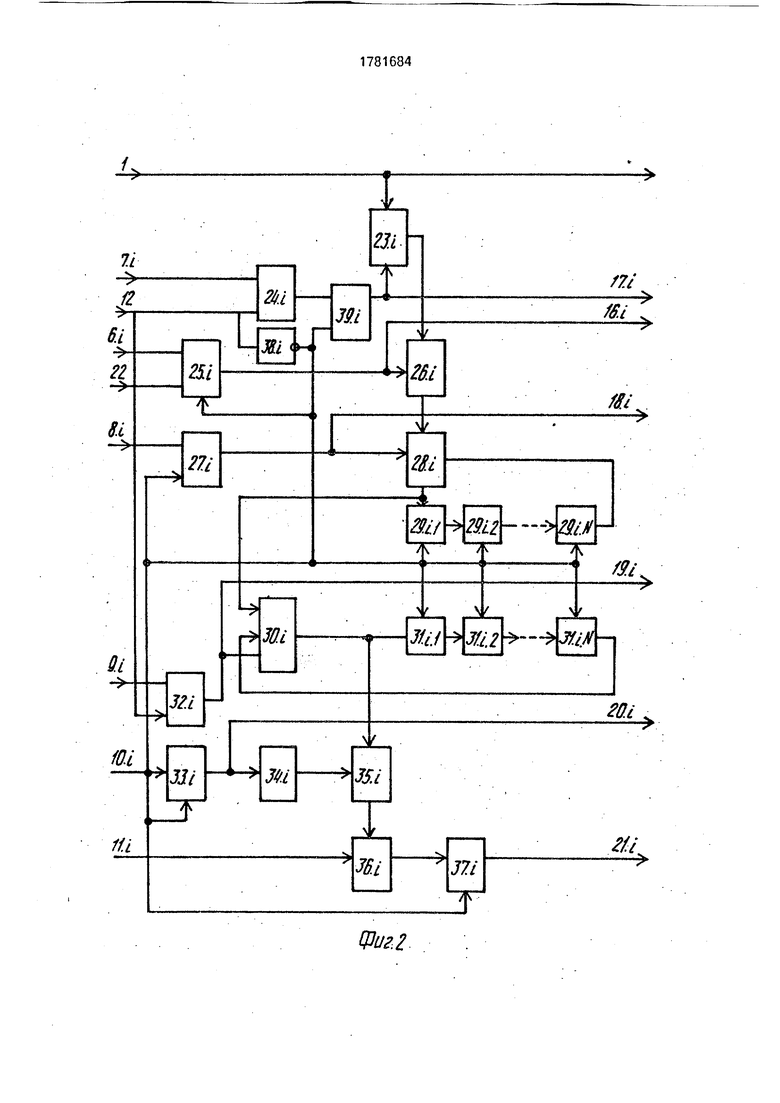

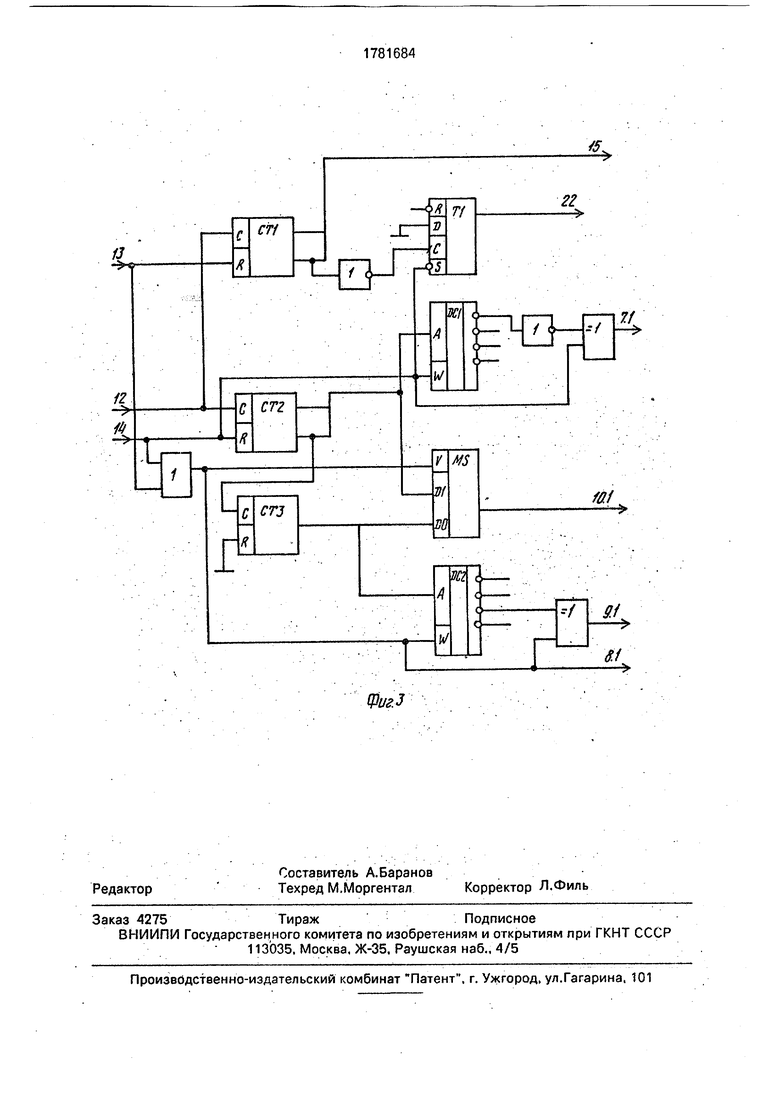

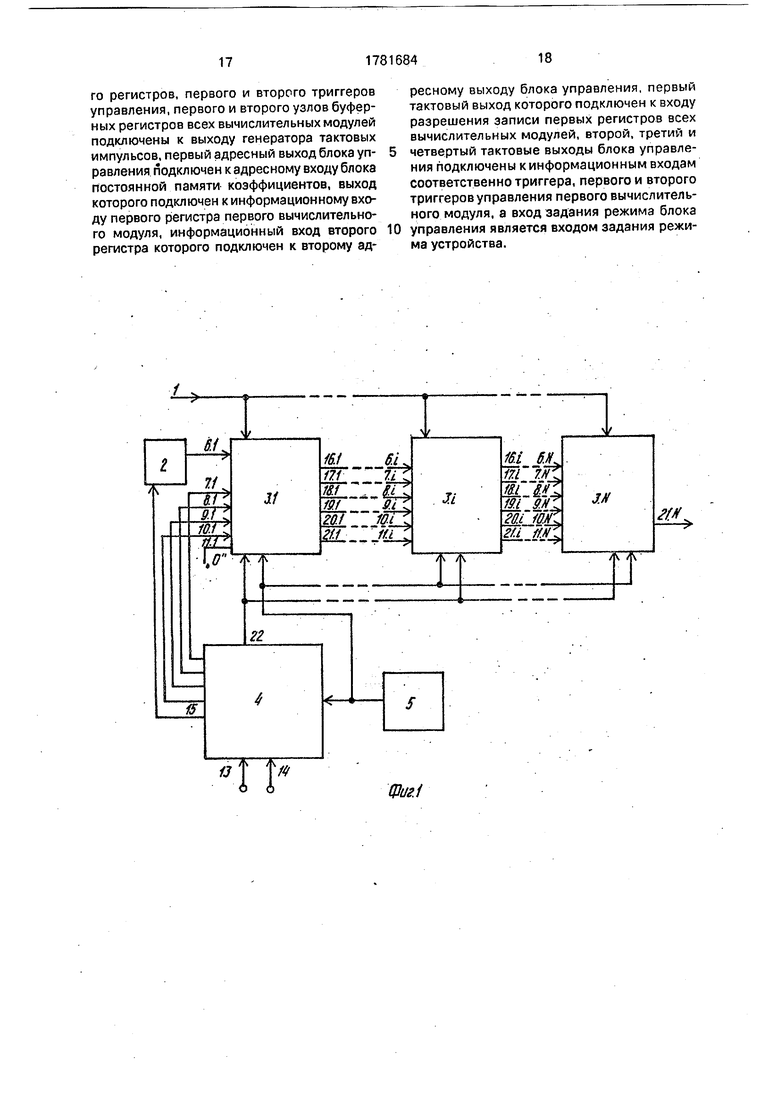

На фиг. 1, 2 изображены структурные схемы устройства и вычислительной ячейки; на фиг. 3 приведен пример выполнения функциональной схемы блока управления.

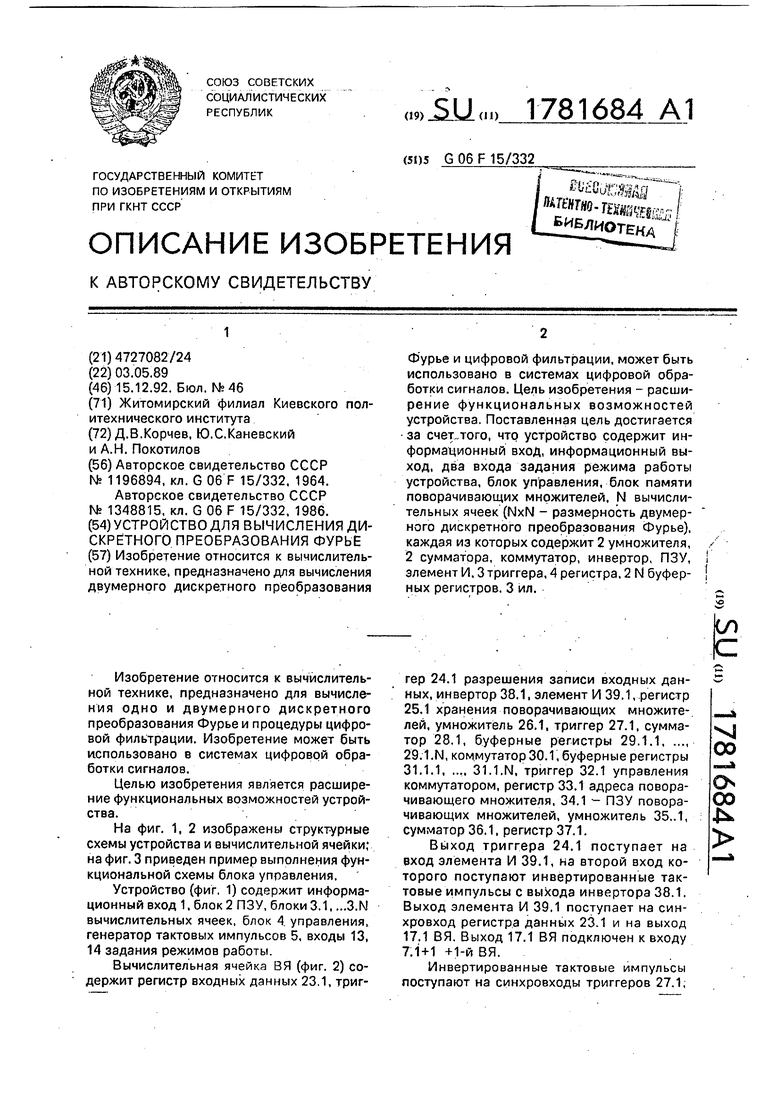

Устройство (фиг, 1) содержит информационный вход 1, блок 2 ПЗУ, блоки 3.1. ...3.N вычислительных ячеек, блок 4 управления, генератор тактовых импульсов 5, входы 13, 14 задания режимов работы.

Вычислительная ячейка ВЯ (фиг. 2) содержит регистр входных данных 23.1, триггер 24.1 разрешения записи входных данных, инвертор 38.1, элемент И 39.1, регистр 25.1 хранения поворачивающих множителей, умножитель 26.1, триггер 27.1, сумматор 28.1, буферные регистры 29.1.1

29.1.N, коммутатор 30.1, буферные регистры

31.1.1 31.1.N, триггер 32.1 управления

коммутатором, регистр 33.1 адреса поворачивающего множителя, 34.1 - ПЗУ поворачивающих множителей, умножитель 35..1, сумматор 36.1, регистр 37.1.

Выход триггера 24.1 поступает на вход элемента И 39.1, на второй вход которого поступают инвертированные тактовые импульсы с выхода инвертора 38.1. Выход элемента И 39.1 поступает на син- хровход регистра данных 23.1 и на выход 17.1 ВЯ. Выход 17.1 ВЯ подключен к входу 7.1 + 1 +1-й ВЯ.

Инвертированные тактовые импульсы поступают на синхровходы триггеров 27.1,

Ч 00

о

00

32.1, регистров25.1,29.1.129.1.N, 31.1.1,

..., 31.1.N, 33.1. 37.1.

При подаче на вход 22 регистра 25.1 логической 1 происходит запись информации в регистр в каждом такте, при подаче на вход 22 лог. О регистр переходит в режим хранения.

Выход регистра 25.1 подключен к одному из входов умножителя 26.1, второй вход которого подключен к выходу регистра 23.1. Выход регистра 25,1 подключен «выходу ВЯ 16.1, который подключен к входу 6.1+1 следующей ВЯ.

Выход триггера 27.1 поступает на выход 18,1 В Я, который подключен ко входу 8.1+1 следующей ВЯ, а также на вход управления кодом операции сумматора 28.1. Один из входов сумматора соединен с выходом умножителя 26.1. Второй вход сумматора 28.1 соединен с выходом буферного регистра 29.1.N. Выход сумматора 28.1 поступает на вход буферного регистра 29.1.1, а также на один из входов коммутатора 30Л. Выход триггера 32.1 подключен к входу управления адресом коммутатора 30.1, а также к выходу 19.1 ВЯ, который подключен к входу 9.1+1 следующей ВЯ.

Выход коммутатора 30.1 подключен ко входу буферного регистра 31.1.1, а также к первому входу умножителя 35.1. Выход буферного регистра 31.1.N подключен ко второму входу коммутатора 30.1.

Выход регистра 33.1 подключен к адресному входу ПЗУ 34.1, а также к выходу 23.1 ВЯ, который соединен с входом 10.1+1 следующей ВЯ. Выход ПЗУ 34.1 поступает на второй вход умножителя 35.1.

На вход 11.1 поступает уровень логического 0, который поступает на один из входов сумматора 36.1, второй вход сумматора 26.1 соединен с выходом умножителя 35.1. Выход сумматора 36.1 соединен с входом регистра 37.1, выход которого 21.1 соединен со входом 11.2 следующей ВЯ.

Блок у правления (фиг. 3) для N 3 содер- життактовый вход 12, входы режима работы 13,14, счетчики делители на 3 СТ1, СТ2, СТЗ, дешифраторы DC1, DC2, коммутатор MS, триггер Т, два инвертора, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ.

Счетчик СТЗ включен последовательно счетчику СТ2 и производит счет через 3 тактовых импульса, выходы счетчика СТ1, подключены к блоку 2 ПЗУ, старший разряд счетчика СТ1 через инвертор поступает на синхровход триггера Т, D вход которого соединен с уровнем 0, выход триггера 22 подключен к входам управления записью регистра 25.1 ВЯ.- -

Считаем, ч го режим вычисления свертки устанавливается после вычисления ДПФ, то есть к началу вычисления свертки в триггере Т записана логическая 1. Тогда через 3

такта триггер обнулится и, запретит запись в регистры 25.1 ВЯ.

Выходы счетчика СТ2 подключены к адресным входам дешифратора DC1 и поступают на коммутатор MS, старший раз ряд

0 счетчика СТ2 поступает на синхровход счетчика СТЗ и обеспечивает его счет через 3 такта. Выходы счетчика СТЗ подключены к адресным входам дешифратора DC2- и поступают на коммутатор MS. Выход коммута5 тора поступает на информационный вход регистра 33.1 ВЯ, выход которого подключен к информационному входу регистра 33.2 следующей ВЯ, а также к ПЗУ поворачивающих множителей 34.1. Выход 7.1 подключен

0 к D входу триггера 24.1, обеспечивает необходимый режим записи в регистры 23.1. Выход 9.1 подключен к входу триггера 32.1, выход которого подключен к адресному входу коммутатора 30.1 и к D входу триггера

5 32.2 следующей ВЯ. По выходу 9.1 обеспечивается переключение коммутаторов 30,1 согласно режиму работы.

Выход 8.1 подключен в D входу триггера 27.1, обеспечивающего необходимый ре0 жим работы сумматоров 28.1 (А+В или А+0). В режиме одномерного ДПФ на вход 13 подается логическая 1, а на вход 14 - логический 0. При этом счетчик СТ1 находится в обнуленном состоянии, триггер Т по входу S

5 устанавливается в состояние логической 1, на выходе элемента ИЛИ - логическая 1, которая поступает на адресный вход коммутатора MS, который коммутирует к выходу 10.1 выходы счетчика СТ2. Лог. 1 на выходе

0 элемента ИЛИ поступает на выход 8. задавая режимы работы сумматоров 28.1-А+О, поступает также на вход W дешифратора DC2, обеспечивая по всем его выходам лог. 1. На выходе ИСКЛЮЧАЮЩЕЕ ИЛИ 9.1 - лог. 0.

5 Перед началом 1-го такта на выходе 7.1 будет лог. 1, на первом и втором такте-лог. О, наследующем такте счетчик обнулится и на выходе 7.1 будет снова лог. 1. Таким образом в этом режиме работы на выходе 7.1

0 будет формироваться последовательность 100100....

В режиме свертки на вход 13 подается лог. О, на вход 14 - лог. 1. При этом счетчик СТ2 находится в обнуленном состоянии, на

5 выходе 10.1 - нулевой адрес. Аналогично режиму одномерного ДПФ на выходе 9.1 - лог. О, на выходе 8.1 -лог. 1. На всех выходах дешифратора DC1 - лог. 1, на выходе 7.1 - лог. 1, на выходах счетчика СТ1 устанавливаются адреса блока 2 ПЗУ. Через 3 первых

такта триггер Т обнуляется, тем самым за- пращается запись в регистры 25.1 всех ВЯ.

В режиме двумерного ДПФ на входы 13, 14 подается лог. 0. При этом работают все три счетчика СТ1, СТ2, СТЗ. На выходе 22 постоянно присутствует лог. 1. На выходе 8.1 - лог. О (режим А+В сумматоров). Аналогично режиму одномерного ДПФ на выходе 7.1 формируется последовательность 100100... . На выходе 9.1 формируется последовательность 111111000111111000... , поступающая на вход триггера 32.1, выход которого управляет переключением коммутатора 30.1.

Работа устройства при вычислении одномерного ДПФ.

Устройство вычисляет следующее выражение:

FOO

2A(N)

k

W, k 0, N-1

A(N) - элемент исходного действия вектора

А . . Размерности N i

F(k) - элементы выходного вектора коэффициенте в Фурье Размерности N W - весовые коэффициенты М - номер обрабатываемого массива.

Для примера рассмотрим работу устройства при вычислении алгоритма ДПФ для N 3. При вычислении одномерного ДПФ на вход 13 подается уровень лог. 1, на вход 14 - лог. 0. При этом на блоке 2 ПЗУ выставляется нулевой адрес, при этом на выходе блока 2W 1 появляется на входе 6.1 ВЯ лог. О, на входе 14 уста на вливает триггер Т в состояние лог. 1, которая поступает на вход 22 всех ВЯ. На вход 7.1 поступает последовательность 100100100.... На вход 9.1 поступает уровень лог. О, на вход 8.1 - лог. 1, на вход 11.1-лог. 0. На входы 10.1 поступают адреса с счетчика СТ2 на каждом такте работы устройства.

1-й такт.

По фронту 1-го тактового импульса в триггер 24,1 записывается лог. 1, появление которой на выходе триггера разрешает запись первого элемента А(0) в регистр 23.1, лог. 1 на входе 22 разрешает запись в регистр 25.1 значения W(0) 1, Лог. 1 на входе 8.1 записывается в триггер 27.1 и устанавливает на управляющем входе сумматора 28.1 режим сквозного прохождения операнды (А+0). На выходе умножителя 26.1 формируется. A(0)W(0) А(0), на выходе сумматора 28.1 - А(0), значение которого через коммутатор 30.1 поступает на вход умножителя 35.1. Значение адреса ПЗУ записывается в

регистр 33.1 и на втором входе умножителя 35.1 появляется значение W(0). В умножителе 35.1 выполняется A(0)W(0), результат умножения поступает на вход регистра

5 суммы 37.1. 2-й такт.

На D-вход триггера 24.1 поступает лог. О, на триггер 24.2 - лог. 1, на триггер 24.3 - лог. 0. Появление лог. 1 на выходе триггера

0 24.2 разрешает запись значения А(1) в регистр 23.2, в регистр 37.1 записывается A(0)W(0), в регистре 23.1 - значение А(0). Аналогично 1-му такту значение А(1) появляется на входе умножителя 35I2, на втором

5 входе которого W(0), значение A(1)W(0) появляется на входе сумматора 36.2, на входе регистра 37.2 появляется значение A(0)W(0) + A(1)W(0) на входе регистра

37.1-A(0)W(0). 0 3-й такт.

На D-вход триггера 24,1 поступает лог. О, на триггер 24.2 - лог. О, на триггер 24.3 - лог. 1, появлениелог. 1 на выходе триггера 24.3 разрешает запись значения А(2) в регистр 23.3,

5 в регистр 37.1 записывается A(0)W(0), в регистре 37.2 - значениеА(0)Л/(0) + A(1)W(0) аналогично 2-му такту значение А(2) появляется на входе умножителя 35.3, на втором входе которого W(0), значение A(2)W(0) появляется на

0 входе сумматора 36.3, на выходе регистра

37.2появляется значение A(0)W(0) + A(1)W(0), на входе регистра 37.3 - A(0)W(0) + A(1)W(0)+ + A(2)W(0), на входе регистра 37.2 - A(0)W(0) + A(1)W(0).

5 4-й такт (аналогичен 1-му такту).

На D-вход триггера 24.1 поступает лог. 1, на триггер 24.2 - лог. О, на триггер 24.3 - лог. 0. Появление лог. 1 на выходе триггера 24.1 разрешает запись значения А(0) в регистр

0 23.1, в регистр 37.1 записывается A(0)W(0), в регистре 37.2 - значение A(0)W(0) + A(1)W(1) аналогично 1-му такту значение А(0) появляется на входе умножителя 35.1, на втором входе которого W(0), на выходе сумматора

5 36.1 - A(0)W(0). На выходе умножителя 35.2 - А(1), на втором входе которого (2) на входе регистра 37.2 - A(0)W(0) + A(1)W(2), на входе умножителя 35.3 - А(2), на втором входе которого W(2), на входе регистра 37.3 0 A(0)W(0) +.A(1)W(1) + A(2)W(2) на выходе устройства появляется значение 1-го коэффициента Фурье:

F(0) - A(0)W(0) + A(1)W(0) + A(2)W(0).

5-й такт, (аналогичен 2-му такту).

На D-вход триггера 24.1 поступает лог. О, на триггер 24,2 - лог. 1, на триггер 34.3 - лог. О, появление лог. 1 на выходе триггера 24.2 разрешает запись значения А(1) в регистр

23.2, в регистр 37.1 записывается A(0)W(0), в

регистре 37.2 - значение A(0)W(0) + A(1)W(2)

на входе умножителя 35.2 - А(1), на втором

входе которого (0),

на входе регистра 37.2 - A(0)W(0) + A(1)W(0) 5

на входе умножителя 35 3 - А(2), на втором

-входе которого (41,

на входе регистра 37.1 - A(0)W(0)

на входе регистра 37,3 - A(0)W(0) + A(1)W(2)+

+ A(2)W(4)10

на выходе устройства появляется значение

2-го коэффициента Фурье:

F(1) A(0)W(0) + A(1)W(1) + A(2)W(2)

6-й такт (аналогичен 3-му такту)

На D-вход триггера 24.1 поступает лог.

О, на триггер 24.2 - лог. О,

на триггер 24.3 - лог. 1, появление лог. 1 на

выходе триггера 24.3.20

Разрешает запись значения А(2) в регистр

23,3,

на входе умножителя 35.3 - А(2). на втором

входе которого W(0),

на выходе умножителя 35.3 - A(2)W(0)25

на выходе устройства появляется значение

3-го коэффициента Фурье:

F(2) - A(0)W(0) + A(1)W(2) + A(2)W(4)

Дальнейшая работа устройства аналогична описанному выше алгоритму.

При реализации дискретной свертки устройство вычисляет выходные отсчеты в соответствии с выражением:

X(k) SA(k-N)H(N)

k

A(k-N) - элементы входного массива,

H(N) - коэффициенты импульсной характеристики.

На вход 13 блока управления подается лог, 0, на вход 14-лог. 1. На выходе счетчика СТ2 постоянно установлен нулевой адрес, который поступает на вход 10.1 ВЯ, обеспечивая установку одного из сомножителей на умножителях 35.1 равного единице.

Блок управления рассмотрен для случая импульсной характеристики длины равной 3.

Вычисление дискретной свертки после вычисления ДПФ, то есть считаем, что на выходе 22 блока управления уровень лог. 1. На выходе 7.1 - постоянный уровень лог. 1, который обеспечивает запись входных дан- ных в регистры 23.1 на каждом такте, на выходе 9.1 - лог. О, на выходе 8.1 - лог. 1.

В течение первых трех тактов идет загрузка коэффициентов в регистры 25.1,25.2, 25.3, На 4-м такте триггер Т обнуляется и на

входы 22 всех ВЯ поступает лог. О, который запрещает запись информации в регистры 25.1,25.2,25.3.

Работа устройства при вычислении двумерного ДПФ.

В режиме двумерного ДПФ устройство вычисляет следующее выражение:

F(N) - x (X х ),

где X - матрица входных отсчетов размерности

, - матрицы весовых коэффициентов размерности.

Рассмотрим работу устройства на примере N 3

ГХ(11) Х(12) Х(13)

Х(21) Х(22) Х(23)

Х(31) Х(32) Х(33)

(11)(12)(13)

(21)(22)(23)

(31)(32)(33)

(11)(12)(13)

(21)(22)(23)

(31)(32)(33)

0

5

0

5

0

5

На входы 13. 14 блока управления подаются уровни лог.О, на 14 входе устанавливает триггер Т в состояние лог. 1, которая присутствует на входах 22 ВЯ разрешая запись в регистры, 25.1 значений W, Счетчик ст. 1 обеспечивает смену адресов блока 2 ПЗУ на каждом такте работы. В блоке 2 хранятся значения W.

Счетчики ст 2, ст 3 обеспечивает смену адресов ПЗУ ВЯ, где хранятся значения W через каждые 3 такта.

На вход 7.1 с блока управления поступает последовательность 1001001... (как и в режиме одномерного ДПФ). управляющая записью данных в регистры 23.1.

На вход 9.1 поступает последовательность 111111000111111000... , которая управляет переключением коммутаторов 30.1.

На вход 8.1 поступает уровень лог. 0. который переводит сумматоры 38.1 в режим вычисления суммы двух операндов (А+В).

На вход 10.1 поступают адреса значе; ний W через каждые 3 такта. Считаем, что в регистрах 29.1, 31.1 до начала вычислений записаны нули.

1-й такт.

По фронту первого тактового импульса в триггер 24.1 записывается лог. 1 со входа 7.1, которая разрешает прохождение инвертированного тактового импульса через эле- мент 39.1. Значение Х(11) записывается в

регистр 23.1, а значение (11) записывается в регистр 25.1,

на выходе умножителя 26.1- Х(11)W(11)

на выходе сумматора 28.1 - Х(11)W(11)

2-й такт.

В триггер 24.2 записывается лог. 1, а в триггеры 24.1 записывается лог. 1, а в триггеры 24.1. 24.3 - лог. 0.

Значение Х(12) записывается в регистр 23.2,

в регистр 25.1 записывается значение W(21)

в регистр 25.2 - значение W(11) на выходе умножителя 26.1 - X(11)W(21) на выходе умножителя 26.2 - X(12)W(11) в регистре 29.1.1 - значение Х(11)W(11) на выходе сумматора 28.1 - значение X(11)W(21)

на выходе сумматора 28.2 - значение X(12)W(11)

3-й такт.

В триггере 24.3 записывается 1, а в триггеры 24.1, 24.2 - 0.

Значение Х(13)записывается в регистр 23.3, в регистр 25.1 записывается значение W(31) в регистр 25.2 записывается значение W(21) в регистр 25.3 записывается значение W(11) на выходе умножителя 26.1 - Х(11)W(31) на выходе умножителя 26.2 - X(12)W(21) на выходе умножителя 26.3 - X(13)W(11) на выходе сумматора 28.1 - Х(11)W(31) на выходе сумматора 28.2 - X(12)W(21) на выходе сумматора 28.3 - X(13)) на выходе регистра 29.1.1 -X(11)W(21) на выходе регистра 29.1.2 - Х(11)W(1)

на выходе регистра 29.2.1 - X(12)W(11)

4-й такт.

В триггере 24.3 записывается 0, в триггер 24.1 - 1, в триггер 24.2 - 0. Значение Х(21) записывается в регистр 23.1, в регистр 25.1 записывается значение W(12) в регистр 25.2 записывается значение W(31) в регистр 25.3 записывается значение W(21) на выходе умножителя 26.1 - X(21)W(12) на выходе умножителя 26.2 - X(12)W(31) на выходе умножителя 26 3 - X(13)W(21) на выходе сумматора 28.1 - X(21)W(12) + +Х(11)W(11)

на выходе сумматора 28.2 - X(12)W(31) на выходе сумматора 28.3 - X(13)W(21)

на выходе регистра 29.1.1 - X(11)W(31) на выходе регистра 29.1.2 - X(11)W(21) на выходе регистра 29.1.3- Х(11)W(11) на выходе регистра 29.2.1 - X(12)W(2l) на выходе регистра 29.2 2 - X(12)W(11)

на выходе регистра 29.3.1 - X(13)W(11)

5-й такт.

В триггер 24.3 записывается 0, в триггер 24.1-0, в триггер 24.2-1. значение Х(22) записывается в регистр 23.2,

в регистр 25.1 записывается значение W(22)

в регистр 25.2 записывается значение W(12)

в регистр 25.3 записывается значение W(31)

на выходе умножителя 26.1 - X(21)W(22)

на выходе умножителя 26.2 - X(22)W(12)

на выходе умножителя 26.3 - X(13)W(31)

на выходе сумматора 28.1 - X(21)W(22) +

+X(11)W(21)

на выходе сумматора 28.2 - X(22)W(12) +

+X(12)W(11)

на выходе сумматора 28.3 - X(13)W(31)

на выходе регистра 29.1.1 - X(21)W(12) +

+X(11)W(11)

на выходе регистра 29.1.2 - Х(11)W(31)

на выходе регистра 29.1.3 - Х(11)W(21)

на выходе регистра 29.2.1 - X(12)W(31)

на выходе регистра 29.2.2 - X(12)W(21)

на выходе регистра 29.2.3 - X(12}W(11)

на выходе регистра 29.3.1 - X(13)W(21)

на выходе регистра 29.3.2 - X(13)W(11)

б-й такт.

В триггере 24.3 записывается 1, в триггер 24.1 - 0, в триггер 24.2 - 0. Значение Х(23) записывается в регистр 23.3, в регистр 25.1 записывается значение W(32) в регистр 25.2 записывается значение W(22) в регистр 25.3 записывается значение W(12) на выходе умножителя 26.1 - X(21)W(32) на выходе умножителя 26.2 - X(22)W(12) на выходе умножителя 26,3 - X(23)W(12) на выходе сумматора 28.1 - X(11)W(31) « +X(21)W(32)

на выходе сумматора 28.2 - X(12)W(11) + +X(22)W(22)

на выходе сумматора 28.3 - X(13)W(11) + +X(23)W(12)

на выходе регистра 29.1.1 - X(11)W(21) + +X(21)W(22)

на выходе регистра 29.1.2 - X(11)W(11) + +X(21)W(12)

на выходе регистра 29.1.3 -X(11)W(31) на выходе регистра 29.2.1 - X(12)W(11) + +X(22)W(12)

на выходе регистра 29.2.2 -X(12)W(31) на выходе регистра 29.2.3 -X(12)W(21) на выходе регистра 29.3.1 - X(13)W(31) на выходе регистра 29.3.2 -X(13)W(21) на выходе регистра 29.3.3 - X(13)W(11)

7-й такт.

В триггер 24.3 записывается 0, в триггер 24.1 - 1, в триггер 24.2 - 0. Значение Х(31) записывается в регистр 23.1, на входе 9.1 триггера 32.1 появляется лог. 0. Инвертированным тактовым импульсом триггер устанавливается в 0 и коммутатор 30.1 коммутирует выход сумматора 28.1 на вход умножителя 35.1 и на выход буферного регистра 31.1.1.

В регистр 25.1 записывается значение W(13)

в регистр 25.2 записывается значение W(32)

в регистр 25.3 записывается значение W(22)

на выходе умножителя 26.1 - X(31)W(13)

на выходе умножителя 26.2 - X(22)W(32)

на выходе умножителя 26.3 - X(23)W(22)

на выходе сумматора 28.1 - X(11)W(11) +

+X(21)W(12) + X(31)W(13) - С(11)

на выходе сумматора 28.2 - X(12)W(3T) +

+X(22)W(32)

на выходе сумматора 28.3 - X(13)W(21) +

+X(23)W(22)

на выходе регистра 29.1.1 - X(11)W(31) +

+X(21)W(32)

на выходе регистра 29.1.2 - X(11)W(21) +

+X(21)W(22)

на выходе регистра 29.1.3 - X(11)W(11) +

+X(21)W(12)

на выходе регистра 29.2.1 - X(12)W(21) +

+X(22)W(22)

на выходе регистра 29.2.2 - X(12)W(11) +

+X(22)W(12)

на выходе регистра 29.2.3 - X(12)W(31)

на выходе регистра 29.3.1 - X(13)W(11) +

+X(23)W(12)

на выходе регистра 29.3.2 - X(13)W(31)

на выходе регистра 29.3.3 - X(13)W(21}

на выходе ПЗУ 34.1 -W(11)

на выходе умножителя 35.1 - С(11)W(11)

на выходе сумматора 36.1 - С(11)W(11)

8-й такт.

В триггер 24.3 записывается 0, в триггер 24.1 - 0, в триггер 24.2 - 1. значение Х(32) записывается в регистр 23.2, в регистр 25.1 записывается значение W(23) в регистр 25.2 записывается значение W(13) в регистр 25.3 записывается значение W(32) на выходе умножителя 26.1 - X(31)W(23) на выходе умножителя 26.2 - X(32)W(13) на выходе умножителя 26.3 - X(23)W(32) на выходе сумматора 28.1 - X(11)W(21) + +X(21)W(22) + X(31)W(23) С(21) на выходе сумматора 28.2 - X(12)W(11) + +X(22)W(12) + X(32)W(13) С(12) на выходе сумматора 28.3 - X(13)W(31) + +X(23)W(32)

на выходе регистра 29.1.1 - W(11) на выходе регистра 29.1.2 - X(11)W(31) + +X(21)W(32)

на выходе регистра 29.1.3 - X(11)W(21) + +X(21)W(22)

на выходе регистра 29.2.1 - X(12)W(31) + +X(22)W(32)

на выходе регистра 29,2.2 - X(12)W(21) + +X(22)W(22)

на выходе регистра 29.2.3 - X(12)W(11) + +X(22)W(12)

на выходе регистра 29.3.1 - X(13)W(21) + +X(23)W(22)

на выходе регистра 293.2 - X(13)W(11) ь HX(23)W(12)

на выходе регистра 29.3.3 - X(13)W(31) на выходе регистра 31.1.1 - С(11) на выходе регистра 37.1 - С(11)W(11) на выходе ПЗУ 34.2 - W(21)

на выходе умножителя 35.1 - C(21)W(11) на выходе умножителя 35.2 - C(12)W(11) на выходе сумматора 36.1 - C(21)W(11) на выходе сумматора 36.2 - C(11)W(11) + +C(12)W(21)

0 9-й такт.

В триггере 24.3 записывается 1, в триггер 24.1 - 0, в триггер 24.2 - 0. значение Х(33) записывается в регистр 23.3, в регистр 25.1 записывается значение W(33)

5 в регистр 25.2 записывается значение W(23) в регистр 25.3 записывается значение W(13) на выходе умножителя 26.1 - X(31)W(33) на выходе умножителя 26.2 - X(32)W(23) на выходе умножителя 26.3 - X(33)W(13)

0 на выходе сумматора 28.1 - X(11)W(31) + +X(21)W(32) + X(31)W(33) С(31) на выходе сумматора 28.2 - X(12)W(21) + +X(22)W(22) + X(32)W(23) - С(22) на выходе сумматора 28.3 - X(13)W(11) +

5 +X(23)W(12) + X(33)W(13) С(13) на выходе регистра 29.1.1 - С(21) на выходе регистра 29.1.2 - 0(11) на выходе регистра 29.1.3 - X(11)W(31) + +X(21)W(32)

0 на выходе регистра 29.2.1 - С(12)

на выходе регистра 29.2.2 - X(12)W(31) +

+X(22)W(32)

на выходе регистра 29.2.3 - X(12)W(21) +

+X(22)W(22)

5 на выходе регистра 29.3.1 - X(13)W(31) + +X(23)W(32)

на выходе регистра 29.3.2 - X(13)W(21) + +Х(23)Л/(22)на выходе регистра 29.3.3 - -X(13)W(11) + X(23)W(12)

0 на выходе регистра 31.1.1-С(21) на выходе регистра 31.1.2-0(11) на выходе регистра 31.2.1 - 0(12) на выходе регистра 37.1 - C(21)W(11) на выходе регистра 37.2 - C(11)W(11) +

5 +C(12)W(21)

на выходе умножителя 35.1 - C(21)W(11) на выходе умножителя 25.2 - C(22)W(21) на выходе умножителя 35.3 - C(13)W(31) на выходе сумматора 36.1 - C(31)W(11) + О

0 на выходе сумматора 36.2 - C(22)W(21) + +C(21)W(11)

на выходе сумматора 36.3 - C(13)W(31) + +C(11)W(11) + C(12)W(21) 10-й такт

5 В триггер 24.3 записывается 0, в триггер 24.1 - 1, в триггер 24,2 - 0. На входе триггера 9.1 появляется уровень 1, триггер устанавливает в 1, тем самым коммутируется выход регистра 31.1.3 на вход коммутатора 30.1.

На выходе умножителя 26.2 - X(32)W(33)

на выходе умножителя 26.2 - X(33)W(23)

на выходе сумматора 28.2 - X(12)W(31)

+X(22)W(32) + X(32)W(33) - С(32)

на выходе сумматора 28.3 - X(13)W(21)

+X(23)W(22) + X(33)W(23) С(23)

на выходе регистра 29.1.1 - С(31)

на выходе регистра 29.1.2 - С(21)

на выходе регистра 29.1.3 - С(11)

на выходе регистра 29.2.1 - С(22)

на выходе регистра 29.2.2 - С(12)

на выходе регистра 29.2.3 - X(12)W(31)

-i-X(22)W(32)

на выходе регистра 29.3.1 - С(13)

на выходе регистра 29.3.2 - X(13)W(31)

+X(23)W(32)

на выходе регистра 29.3.3 - X(13)W(21)

+X(23)W(22)

на выходе регистра 31.1.1 - С(31)

на выходе регистра 31.1.2 - С(21)

на выходе регистра 31.1,.3 - С(11)

на выходе регистра 31.2.1 - С(22)

на выходе регистра 31.2.2 - С(12)

на выходе регистра 31.3..1 - С(13)

на выходе регистра 37.1 - C(31)W(11)

на выходе регистра 37.2 - C(22)W(2d)

C(21)W(11)

на выходе регистра 37.3 - C(13)W(31)

С(11)W(11) + C(12)W(21) - F(11)

на выходе умножителя 35.1 - C(11)W{22)

на выходе умножителя 35.2 - C(32)W(21)

на выходе умножителя 35.3 - C(23)W(31)

на выходе сумматора 36.1 - С(11)W(12) + О

на выходе сумматора 36.2 - C(31)W(11)

+C(32)W(21)

на выходе сумматора Зб.З - C(22)W(21)

+C(21)W(11) + C(23)W(31)

на выходе устройства появляется значен

первого коэффициента Фурье: F(11)

11-и такт.

В триггер 24.3 записывается 0. в тригг 24.1 -0, в триггер 24.2 - 1. На выходе умножителя 26.3 - X(33)W(33) на выходе сумматора 28.3 - X(13)W(31) + X(23)W(32) + X(33)W(33) - С(33) на выходе регистра 29.2.1 - С(32) на выходе регистра 29,2.2 - С(22) на выходе регистра 29.2.3 - С(12) на выходе регистра 29.3.1 - С(23) на выходе регистра 29.3.2 - С(13) на выходе регистра 29.3.3 - X(13)W(31) +X(23)W(32)

на выходе регистра 31.1.1 - С(11) на выходе регистра 31.1.2 - С(31) на выходе регистра 31.1.3-0(21) на выходе регистра 31.2.1 - С(32) на выходе регистра 31.2.2 - С(22) на выходе регистра 31.2.3 - С(12) на выходе регистра 31.3.1 -- С(23) на выходе регистра 31.3.2 - С(13)

на выходе регистра 37.1 - С(11}W(12) на выходе регистра 37.2 - C(31)W(11) + +C(32)W(21)

на выходе регистра 37.3 - C(21)W(11) + 5 +C(22)W(21) + C(23)W(31) - F(21)

на выходе умножителя 35.1 - C(21)W(12) на выходе умножителя 35.2 - C(12)W(22) на выходе умнои&теля 35.3 - C(33)W(31) на выходе сумматора 36.1 - C(21)W(12) + О

0 на выходе сумматора 36.2 - C(11)W(12) + +C(12)W(22)

на выходе сумматора 36.3 - C(31)W(11) + +C(32)W(21) + C(3;3)W(31) на выходе устройства появляется значение

5 второго коэффициента Фурье: F(21). 12-й такт.

В триггер 24,3 записывается 1, в триггер 24.1 -.0, в триггер 24.2 - 0. На выходе регистра 29.3.1 - С(33)

0 на выходе регистра 29.3.2 - С(23) на выходе регистра 29.3.3 - С(13) на выходе регистра 31.1.1 - С(21) на выходе регистра 31.1.2 - С(11) на выходе регистра 31.1.3 - С(31)

5 на выходе регистра 31.2.1 - С(12) на выходе регистра 31.2.2 - С(32) на выходе регистра 31.2.3 - С(22) на выходе регистра 31.3.1 - С(33) на выходе регистра 31.3.2 - С{23)

0 на выходе регистра 31..3.3 - С(13) на выходе регистра 37.1 - C(21)W(12) на выходе регистра 37.2 - C(11)W(12) + +C(12)W(22) на выходе регистра 37.3 - C(31)W(11) +

5 +C(32)W(21) + C(33)W(31) F(31)

на выходе умножителя 35.1 - C(31)W(12) на выходе умножителя 35.2 - C(22)W(22) на выходе умножителя 35.3 - C(13)W(32) на выходе сумматора 36.1 - C(31)W(12) + О

0 на выходе сумматора 36.2 - C(22)W(22) + +C(21)W(12)

на выходе сумматора 36.3 - C(13)W(32) + +C(11)W(12) + C(12)W(22) на выходе устройства появляется значение

5 третьего коэффициента Фурье: F(31) 13-й такт.

В триггер 24.3 записывается 0, в триггер 24.1 - 1, в триггер 24.2 - 0. На выходе регистра 31.1.1 - С(31)

0 на выходе регистра 31.1.2 - С(21) на выходе регистра 31.1.3 - С(11) на выходе регистра 31.2.1 - С(22) на выходе регистра 31.2.2 - С(12) на выходе регистра 31.2.3 - С(32)

5 на выходе регистра 31.3.1 - С(13) на выходе регистра 31.3.2 - С(33) на выходе регистра 31.3.3 - С(23) на выходе регистра 37.1 - C(31)W(12) , на выходе регистра 37.2 - C(21)W(12) + +C(22)W(22)

на выходе регистра 37.3 - C(11)W(12) +

+C(12)W(22) + C(13)W(32) F(12)

на выходе умножителя 35.1 - С(11)W(13)

на выходе умножителя 35.2 - C(32)W(22)

на выходе умножителя 35.3 - C(23)W(32)

на выходе сумматора 36.1 - С(11)W(13) + О

на выходе сумматора 36.2 - C(31)W(12) +

+C(22)W(22)

на выходе сумматора 36.3 - C(21)W(12) +

+C(22)W(22) + C(23)W(32)

на выходе устройства появляется значение

четвертого коэффициента Фурье: F(12).

14-й такт.

В триггер 24.3 записывается 0, в триггер 24.1 - 0, в триггер 24.2 - 1. На выходе регистра 31.1.1 - С(11) на выходе регистра 31.1.2 - С(31) на выходе регистра 31.1.3 - С(21) на выходе регистра 31.2.1 - С(32) на выходе регистра 31.2.2 - С(22) на выходе регистра 31.2.3 - С(12) на выходе регистра 31.3.1 - С(23) на выходе регистра 31.3.2 - С(13) на выходе регистра 31.3.3 - С(33) на выходе регистра 37.1 - C(11)W(1.3) на выходе регистра 37.2 - C(31)W(12) + +C(32)W(22)

на выходе регистра 37.3 - C(21)W(12) + +C(22)W(22) + C(23)W(32) F(22) на выходе умножителя 35.1 - C(21)W(13) на выходе умножителя 35.2 - Cf12)W(23) на выходе умножителя 35.3 - C(33)W(32) на выходе сумматора 36.1 - C(21)W{13) + О на выходе сумматора 36.2 - C(11)W(13) + +C(12)W(23)

на выходе сумматора 36.3 - C(31)W(12) + +C(32)W(22) + C(33)W(32) на выходе устройства появляется значение пятого коэффициента Фурье: F(22).

Аналогично в 15 также на выходе устройства появится шестой коэффициент Фурье: F(32) - C(31)W(12) + C(32)W(22) + +C(33)W(32)

в 16 такте - F(13) седьмой коэффициент Фурье,

в 17 такте - F(23) восьмой коэффициент Фурье.

в 18 такте - F(33) девятый коэффициент Фурье.

Формула изобретения Устройство для вычисления дискретного преобразования Фурье, содержащее блок управления, генератор тактовых импульсов и N-1 вычислительных модулей (N - дазмер преобразования), причем i-й (I Г, N-1) вычислительный модуль содержит триггер, элемент И, первый сумматор, первый умножитель, входной регистр, выходной ре- гистри эпе мрт 1 IE, выход которого подключен к тактовому входу выходного регистра, и первому входу элемента И, выход которого подключен к тактовому входу входного регистра, выход первого умножителя подключен к первому входу первого сумматора, выход которого подключен к информационному входу выходного регистра, выход которого подключен к второму входу первого сумматора (i+1)-ro вычислительного модуля,

0 выход триггера подключен к второму входу элемента И, тактовый вход триггера подключен к выходу генератора тактовых импульсов, а второй вход первого сумматора первого вычислительного модуля является

5 входом задания логического нуля устройства, информационные входы входных устройств всех вычислительных модулей подключены к информационному входу устройства, отличающееся тем, что, с

0 целью расширения функциональных возможностей за счет выполнения двумерного преобразования Фурье, в него введен блок постоянной памяти коэффициентов, а в каждый вычислительный модуль введены два

5 регистра, второй умножитель, второй сумматор, два триггера управления, два узла буферных регистров, коммутатор и узел постоянной памяти коэффициентов, причем выход первого регистра подключен к перво0 му входу второго умножителя, выход которого, подключен к первому входу второго сумматора, выход которого подключен к первому информационному входу коммутатора, информационному входу первого узла

5 буферных регистров, выход которого подключен к второму входу второго сумматора, выход второго регистра подключен к адресному входу узла постоянной памяти коэффициентов, выход которого подключен к

0 первому входу первого умножителя, второй вход которого соединен с информационным входом второго узла буферных регистров и подключен к выходу коммутатора, второй информационный вход которого подключен

5 к выходу второго узла буферных регистров, выход второго регистра подключен к второму входу второго умножителя, выход первого триггера управления подключен к входу кода операции второго сумматора и инфор0 мационному входу первого триггера управ- ления (1+1)-го вычислительного модуля, выход второго триггера управления подключен к управляющему входу коммутатора и информационному входу второго триггера управ5 ления (1+1}-го и вычислительного модуля, выходы первого и второго регистров 1-го вычислительного модуля подключены к информационным входам соответственно первого и второго регистров (И 1)-го вычислительного модуля, тактовые входы первого и второго регистров, первого и второго триггеров управления, первого и второго узлов буферных регистров всех вычислительных модулей подключены к выходу генератора тактовых импульсов, первый адресный выход блока управления подключен к адресному входу блока постоянной памяти коэффициентов, выход которого подключен к информационному входу первого регистра первого вычислительного модуля, информационный вход второго регистра которого подключен к второму ад0

ресному выходу блока управления, первый тактовый выход которого подключен к входу разрешения записи первых регистров всех вычислительных модулей, второй, третий и четвертый тактовые выходы блока управления подключены к информационным входам соответственно триггера, первого и второго триггеров управления первого вычислительного модуля, а вход задания режима блока управления является входом задания режима устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для операций над матрицами | 1990 |

|

SU1735868A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1721610A1 |

| Устройство для умножения матриц | 1991 |

|

SU1801224A3 |

| ЭЛЕКТРОПРИВОД УДАРНОГО ДЕЙСТВИЯ | 1992 |

|

RU2017319C1 |

| Устройство для операций над матрицами | 1990 |

|

SU1784997A1 |

| Многоканальный коммутатор | 1989 |

|

SU1661986A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки (ЭЛТ) | 1988 |

|

SU1509862A1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| Линейный интерполятор | 1987 |

|

SU1439534A1 |

| Устройство для цифровой обработки сигналов | 1989 |

|

SU1652981A1 |

Изобретение относится к вычислительной технике, предназначено для вычисления двумерного дискретного преобразования Фурье и цифровой фильтрации, может быть использовано в системах цифровой обработки сигналов. Цель изобретения - расширение функциональных возможностей устройства. Поставленная цель достигается за счет„того, что устройство содержит информационный вход, информационный выход, два входа задания режима работы устройства, блок управления, блок памяти поворачивающих множителей, N вычислительных ячеек (NxN - размерность двумерного дискретного преобразования Фурье), каждая из которых содержит 2 умножителя, 2 сумматора, коммутатор, инвертор, ПЗУ, элемент И, 3 триггера, 4 регистра, 2 N буферных регистров. 3 ил.

I Г

Щиг.1

I

Фиг.2

| Устройство для цифровой фильтрации | 1984 |

|

SU1196894A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Прибор для заливки свинцом стыковых рельсовых зазоров | 1925 |

|

SU1964A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1348815A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-15—Публикация

1989-05-03—Подача