05

ел

GO

О CD

Изобретение относится к технике связи и может быть использовано в системах цифровой коммутации.

Целью изобретения является повышение помехозащищенности путем преобразования двоичных сигналов в биим- пульсные.

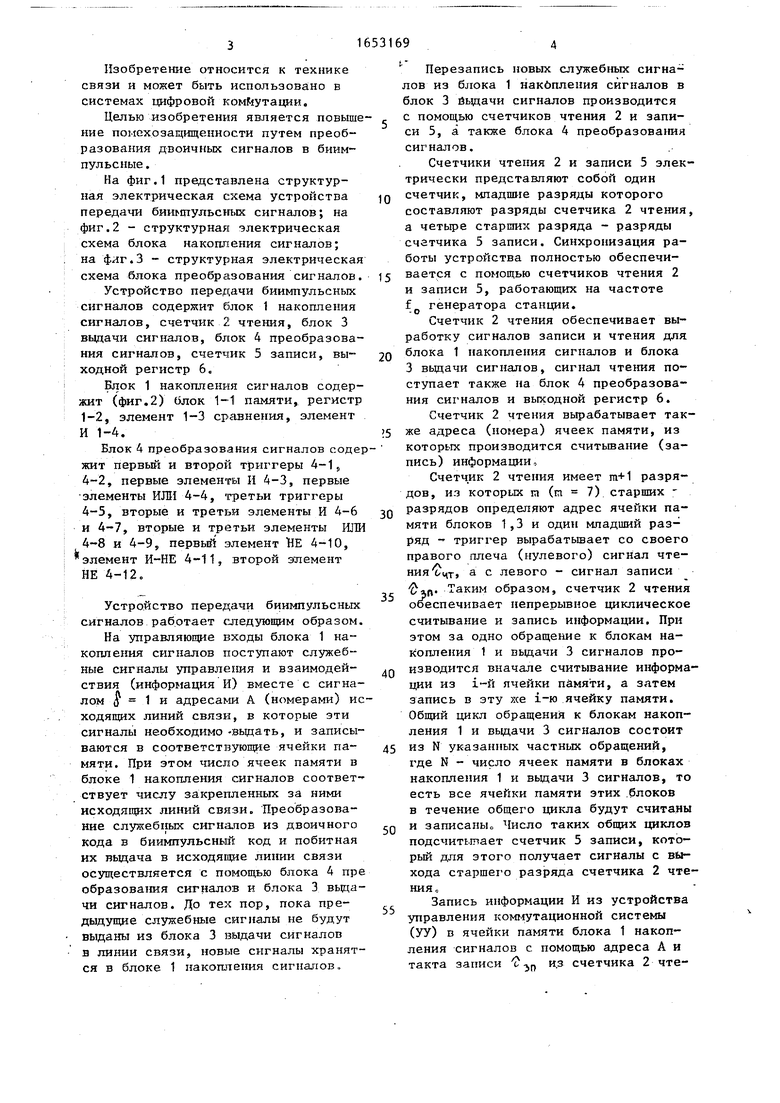

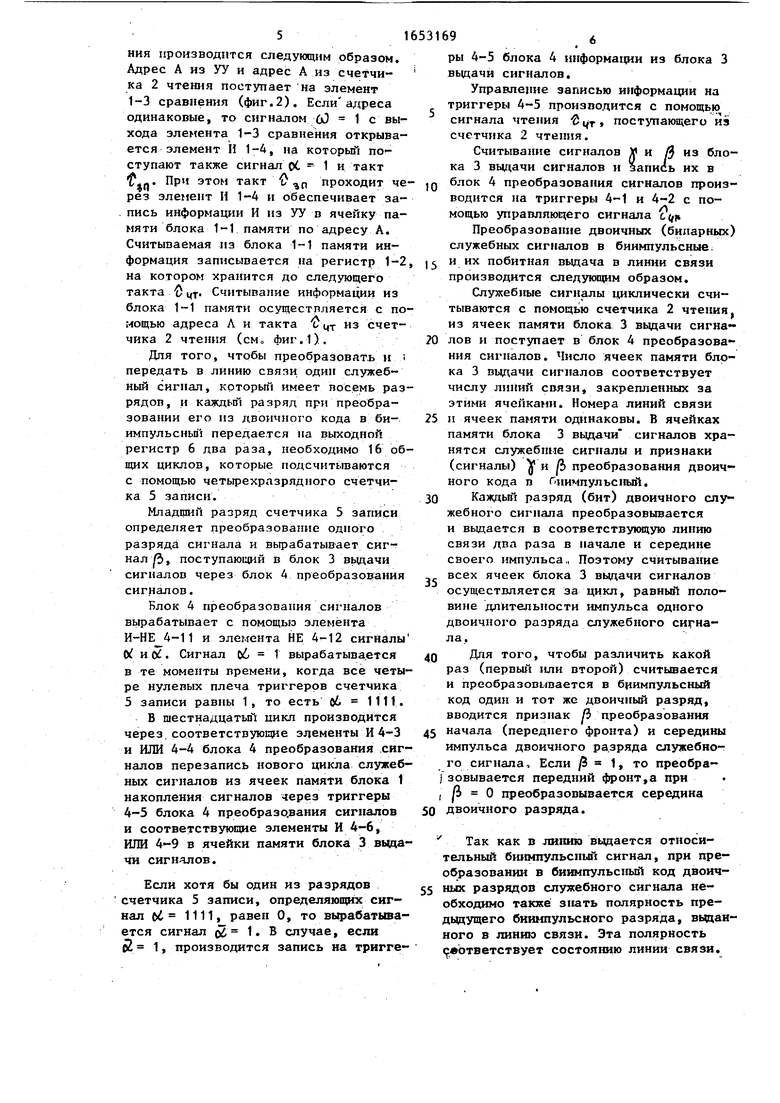

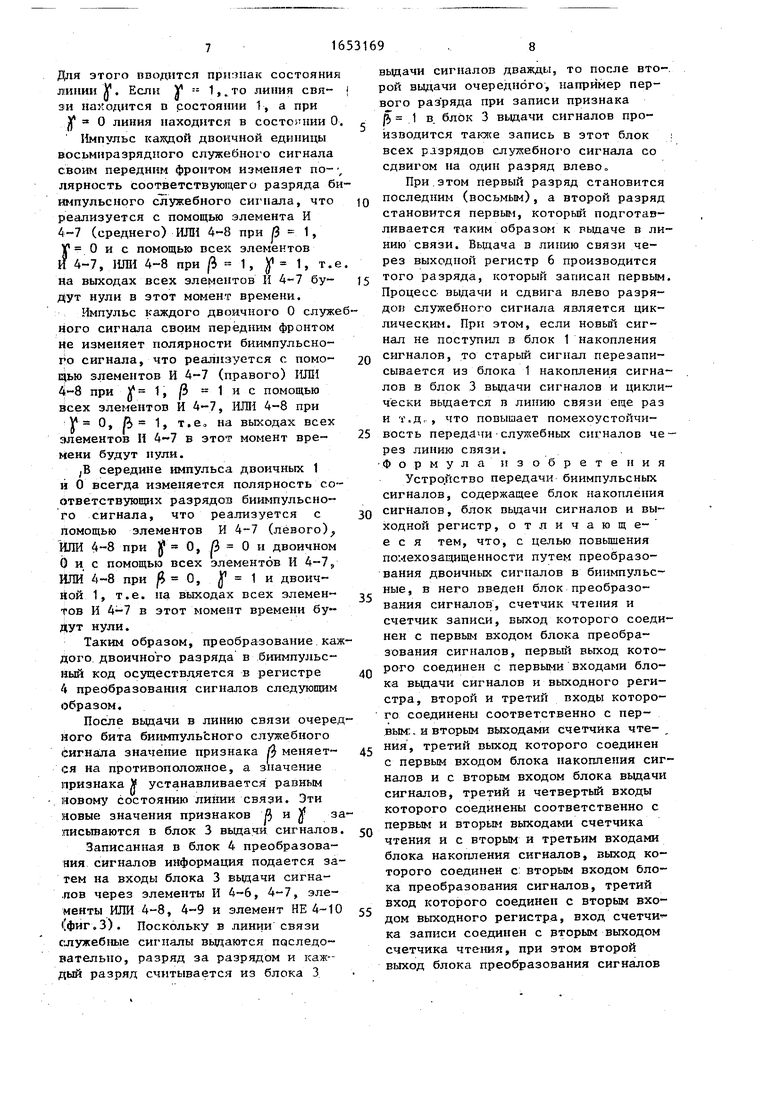

На фиг.1 представлена структурная электрическая схема устройства передачи биимпульсных сигналов; на фиг. 2 - структурная электрическая схема блока накопления сигналов; на флг.З - структурная электрическая схема блока преобразования сигналов.

Устройство передачи биимпульсных сигналов содержит блок 1 накопления сигналов, счетчик 2 чтения, блок 3 выдачи сигналов, блок 4 преобразования сигналов, счетчик 5 записи, выходной регистр 6.

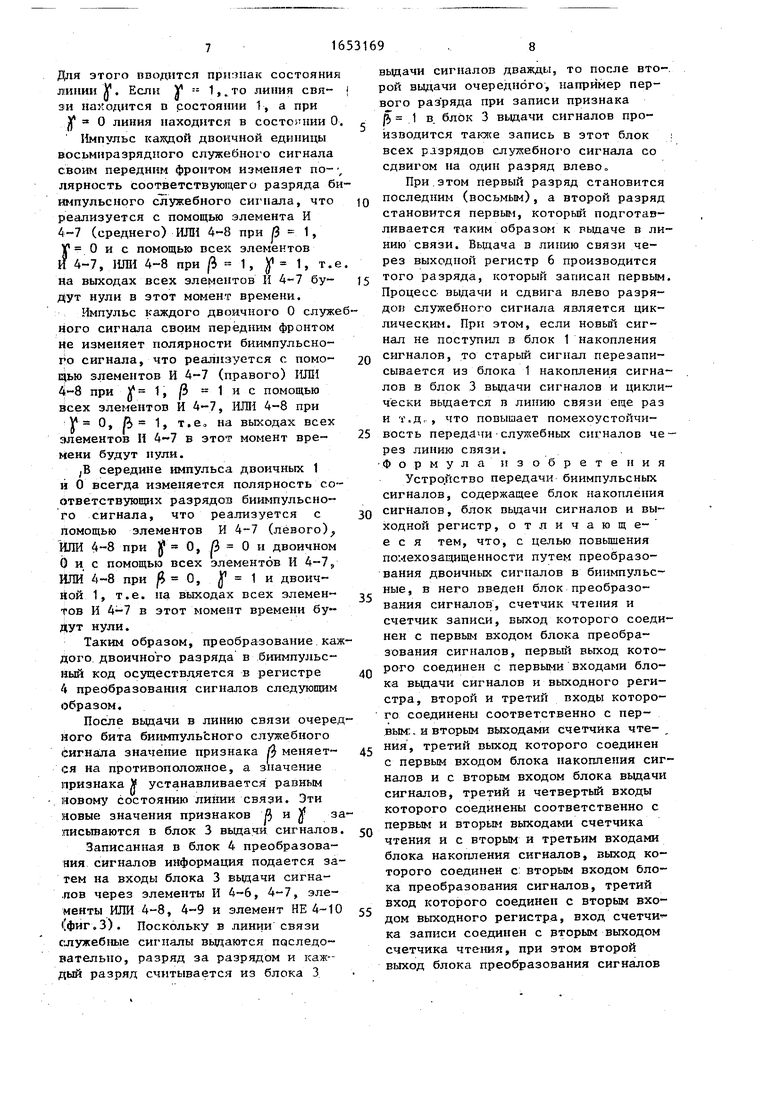

Блок 1 накопления сигналов содержит (фиг.2) блок 1-1 памяти, регистр 1-2, элемент 1-3 сравнения, элемент И 1-4.

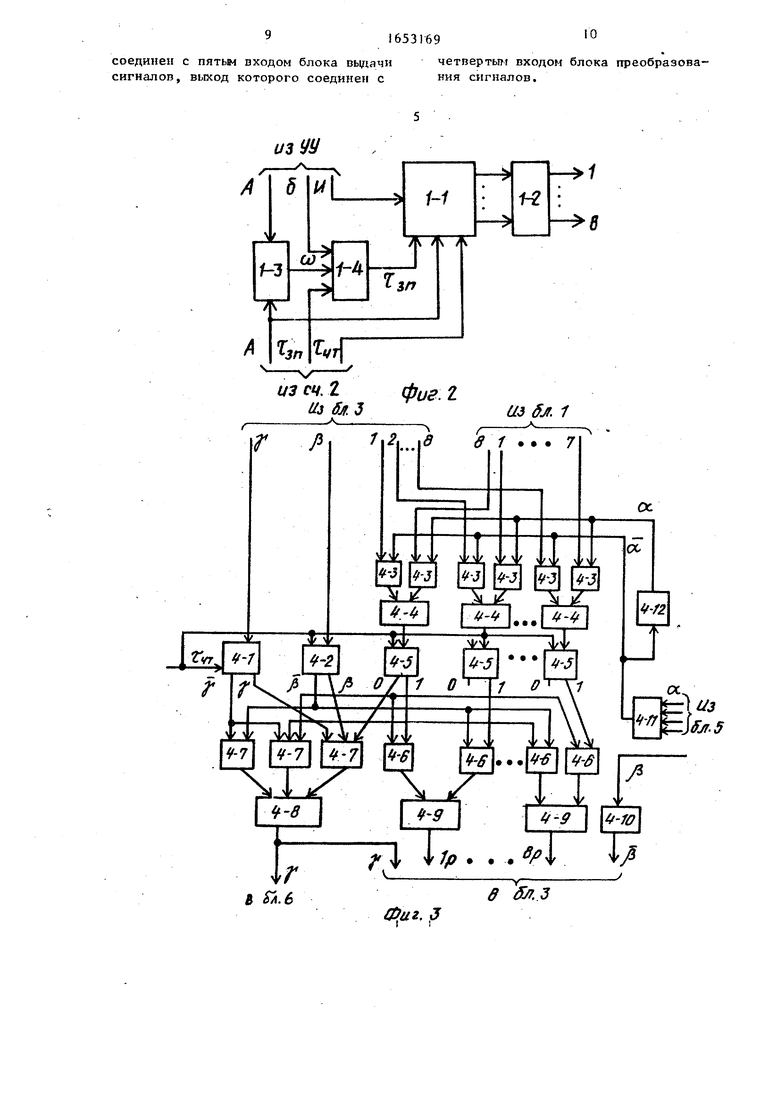

Блок 4 преобразования сигналов содержит первый и второй триггеры 4-1, 4-2, первые элементы И 4-3, первые элементы ИЛИ 4-4, третьи триггеры 4-5, вторые и третьи элементы И 4-6 и 4-7, вторые и третьи элементы ИЛИ 4-8 и 4-9, первый элемент НЕ 4-10, элемент И-НЕ 4-11, второй элемент НЕ 4-12.

Устройство передачи биимпульсных сигналов работает следующим образом.

На управляющие входы блока 1 накопления сигналов поступают служебные сигналы управления и взаимодействия (информация И) вместе с сигналом (у 1 и адресами А (номерами) исходящих линий связи, в которые эти сигналы необходимо -выдать, и записываются в соответствующие ячейки памяти. При этом число ячеек памяти в блоке 1 накопления сигналов соответствует числу закрепленных за ними исходящих линий связи. Преобразование служебных сигналов из двоичного кода в биимпульсный код и побитная их выдача в исходящие линии связи осуществляется с помощью блока 4 пре образования сигналов и блока 3 выдачи сигналов. До тех пор, пока предыдущие служебные сигналы не будут выданы из блока 3 выдачи сигналов в линии связи, новые сигналы хранятся в блоке 1 накопления сигналов.

5

0

0

5

0

5

0

5

Перезапись новых служебных сигналов из блока 1 накопления сигналов в блок 3 выдачи сигналов производится с помощью счетчиков чтения 2 и записи 5, а также блока 4 преобразования сигналов.

Счетчики чтения 2 и записи 5 электрически представляют собой один счетчик, младшие разряды которого составляют разряды счетчика 2 чтения, а четыре старпих разряда - разряды счатчика 5 записи. Синхронизация работы устройства полностью обеспечивается с помощью счетчиков чтения 2 и записи 5, работающих на частоте f генератора станции.

Счетчик 2 чтения обеспечивает выработку сигналов записи и чтения для блока 1 накопления сигналов и блока 3 выдачи сигналов, сигнал чтения поступает также на блок 4 преобразования сигналов и выходной регистр 6.

Счетчик 2 чтения вырабатывает также адреса (номера) ячеек памяти, из которых производится считывание (запись) информации.

Счетчик 2 чтения имеет т+1 разрядов, из которых п (п 7) старших - разрядов определяют адрес ячейки памяти блоков 1,3 н один младший разряд - триггер вырабатывает со своего

правого плеча (нулевого) сигнал чтелния 6ц-р, а с левого - сигнал записи

Ј,„. Таким образом, счетчик 2 чтения обеспечивает непрерывное циклическое считывание и запись информации. При этом за одно обращение к блокам накопления 1 и выдачи 3 сигналов производится вначале считывание информации из i-й ячейки памяти, а затем запись в эту же i-ю ячейку памяти. Общий цикл обращения к блокам накопления 1 и выдачи 3 сигналов состоит из N указанных частных обращений, где N - число ячеек памяти в блоках накопления 1 и выдачи 3 сигналов, то есть все ячейки памяти этих блоков в течение общего цикла будут считаны и записаны Число таких общих циклов подсчитияает счетчик 5 записи, который для этого получает сигналы с выхода старшего разряда счетчика 2 чтения о

Запись информации И из устройства управления коммутационной системы (УУ) в ячейки памяти блока 1 накопления сигналов с помощью адреса А и

такта записи с.

}П

из счетчика 2 чтения производится следующим образом. Адрес А из УУ и адрес А из счетчика 2 чтения поступает на элемент 1-3 сравнения (фиг.2). Если адреса одинаковые, то сигналом oJ - 1 с выхода элемента 1-3 сравнения открывается элемент И 1-4, на который поступают также сигнал 0. 1 и такт

0 Р этом такт Ј %п проходит через элемент И 1-4 и обеспечивает запись информации И из УУ в ячейку памяти блока 1-1 памяти по адресу А. Считываемая из блока 1-1 памяти информация записывается на регистр 1-2, на котором хранится до следующего такта О чт. Считывание информации из блока 1-1 памяти осущестпляется с поосущестпляется

мощью адреса А и такта Јчт из счетчика 2 чтения (смо фиг.1).

Для того, чтобы преобразовать и передать в линию святи один служебный сигнал, который имеет восемь разрядов, и каждый разряд при преобразовании его из двоичного кода в бн- импульсныи передается на выходной регистр 6 два раза, необходимо 16 общих циклов, которые подсчитываются с помощью четырехразрядного счетчика 5 записи.

Младший разряд счетчика 5 записи определяет преобразование одного разряда сигнала и вырабатывает сш- нал (Ь, поступающий в блок 3 выдачи сигналов через блок 4 преобразования сигналов.

Блок 4 преобразования сигналов вырабатывает с помощыэ элемента И-НЕ 4-11 и элемента НЕ 4-12 сигналы di и оЈ. Сигнал Об 1 вырабатывается в те моменты времени, когда все четыре нулевых плеча триггеров счетчика 5 записи равны 1, то есть & 1111.

В шестнадцатый цикл производится через соответствующие элементы И 4-3 и ИЛИ 4-4 блока 4 преобразования сигналов перезапись нового цикла служебных сигналов из ячеек памяти блока 1 накопления сигналов через триггеры 4-5 блока 4 преобразования сигналов и соответствующие элементы И 4-6, ИЛИ 4-9 в ячейки памяти блока 3 выдачи сигналов.

Если хотя бы один из разрядов счетчика 5 записи, определяющих сигнал ftd 1111, равен 0, то вырабатывается сигнал оЈ 1. В случае, если (2 1 производится запись на тригге10

15

20

6531696

ры 4-5 блока 4 информации из блока 3 выдачи сигналов.

Управление записью информации на триггеры 4-5 производится с помощью сигнала чтения Јчт, поступающего из счетчика 2 чтения.

Считывание сигналов и А из блока 3 выдачи сигналов и запись их в блок 4 преобразования сигналов производится па триггеры 4-1 и 4-2 с помощью управляющего сигнала

Преобразование двоичных (бинарных) служебных сигналов в биимпульсные и их побитная выдача в линии связи производится следующим образом.

Служебные сигналы циклически считываются с помощью счетчика 2 чтения р из ячеек памяти блока 3 выдачи сигналов и поступает в блок 4 преобразования сигналов. Число ячеек памяти блока 3 выдачи сигналов соответствует числу линий связи, закрепленных за этими ячейками. Номера линий связи и ячеек памяти одинаковы. В ячейках памяти блока 3 выдачи сигналов хранятся служебние сигналы и признаки (сигналы) у и { преобразования двоичного кода п г.нимпульсный.

Каждый разряд (бит) двоичного служебного сигнала преобразовывается и выдается в соответствующую линию связи два раза в начале и середине своего импульса,, Поэтому считывание всех ячеек блока 3 выдачи сигналов осуществляется за цикл, равный половине длительности импульса одного двоичного разряда служебного сигнала.

Для того, чтобы различить какой раз (первый или второй) считывается и преобразовывается в биимпульсный код один и тот же двоичный разряд, вводится признак /3 преобразования

25

30

35

40

45 начала (переднего фронта) и середины импульса двоичного разряда служебного сигнала, Если /3 1, то преобразовывается передний фронт,а при ( 0 преобразовывается середина 50 двоичного разряда.

Так как в линию выдается относительный биимпульсный сигнал, при преобразовании в биимпульсный код двоич- 55 ных разрядов служебного сигнала необходимо также знать полярность предыдущего биимпульсного разряда, выданного в линию связи. Эта полярность соответствует состоянию линии связи.

Для этого пводнтсл пршпак состояния линии V. Если У - 1,.то линия свп- зн наз:одится D состоянии 1, а при У 0 линия находится в состоянии 0

Импульс каждой двоичной единицы восьмиразрядного служебного сигнала своим передним фронтом изменяет по- лярность соответствукяцего разряда би импульсного служебного сигнала, что реализуется с помощью элемента И 4-7 (среднего) ИЛИ 4-8 при |3 1 , Г 0 и с помощью всех элементов И 4-7, ИЛИ 4-8 при ft 1, 1, т.е на выходах всех элементов И 4-7 бу- дут нули в этот момент времени.

Импульс каждого двоичного 0 служеного сигнала своим передним фронтом не изменяет полярности биимпульсно- го сигнала, что реализуется г. помо- цыо элементов И 4-7 (правого) ИЛИ 4-8 при )f 1 Р 1 и с помощью всех элементов И 4-7, ИЛИ 4-8 при

У О h 1 т.во на выходах всех элементов И в этот момент вре- мени будут нули.

,В середине импульса двоичных 1 и 0 всегда изменяется полярность соответствующих разрядов биимпульсно- го сигнала, что реализуется с помощью элементов И 4-7 (левого), ИЛИ 4-8 при у О, и двоичном О и с помощью всех элементов И 4-7, ИЛИ 4-8 при О, У 1 и двоичной 1, т.е. на выходах всех элемен- тов И 4-7 в этот момент времени будут нули.

Таким образом, преобразование каждого двоичного разряда в биимпульс- ный код осуществляется в регистре 4 преобразования сигналов следующим образом.

После выдачи в линию связи очередного бита бинмпульсного служебного сигнала значение признака rt меняет- ся на противоположное, а значение признака И устанавливается равным новому состоянию линии связи. Эти новые значения признаков А и записываются в блок 3 выдачи сигналов.

Записанная в блок 4 преобразования сигналов информация подается затем на входы блока 3 выдачи сигналов через элементы И 4-6, 4-7, элементы ИЛИ 4-8, 4-9 и элемент НЕ 4-10 (фиг.З). Поскольку в линии связи служебные сигналы выдаются последовательно, разряд за разрядом и каж-- дый разряд считывается из блока 3

выдачи сигналов дважды, то после второй выдачи очередного, например первого разряда при записи признака $ 1 в блок 3 выдачи сигналов производится также запись в этот блок всех разрядов служебного сигнала со сдвигом на один разряд влево„

При этом первый разряд становится последним (восьмым), а второй разряд становится первым, который подготавливается таким образом к рыдаче в линию связи. Выдача в линию связи через выходной регистр 6 производится того разряда, который записан первым Процесс выдачи и сдвига влево разрядов служебного сигнала является циклическим. При этом, если новый сигнал не поступил в блок 1 накопления сигналов, то старый сигнал перезаписывается из блока 1 накопления сигналов в блок 3 выдачи сигналов и циклически выдается п линию связи еще раз и ч .д , что повышает помехоустойчивость передачи служебных сигналов через линию спязи. Формула изобретения

Устройство передачи биимпульсных сигналов, содержащее блок накопления сигналов, блок выдачи сигналов и выходной регистр, отличающееся тем, что, с целью повышения помехозащищенности путем преобразования двоичных сигналов в бинмпульс- ные, в него введен блок преобразования сигналов, счетчик чтения и счетчик записи, выход которого соединен с первым входом блока преобразования сигналов, первый выход которого соединен с первыми входами блока выдачи сигналов и выходного регистра, второй и третий пходы которого соединены соответственно с первым, и вторым выходами счетчика чтения , третий выход которого соединен с первым входом блока накопления сигналов и с вторым входом блока выдачи сигналов, третий и четвертый входы которого соединены соответственно с первым и вторым выходами счетчика чтения и с вторым и третьим входами блока накопления сигналов, выход которого соединен с вторым входом блока преобразования сигналов, третий вход которого соединен с вторым входом выходного регистра, вход счетчи - ка записи соединен с вторым выходом счетчика чтения, при этом второй выход блока преобразования сигналов

соединен с пятым входом блока выдлчи сигналов, выход которого соедшген с

четвертым входом блока преобразования сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования и коммутации сигналов | 1988 |

|

SU1566505A1 |

| Устройство временной коммутации биимпульсных сигналов | 1989 |

|

SU1711344A1 |

| Многомодульная коммутационная система для асинхронных цифровых сигналов | 1986 |

|

SU1394459A1 |

| Устройство преобразования биимпульсных уплотненных сигналов | 1985 |

|

SU1319308A1 |

| Устройство пространсктвенно-временной коммутации | 1978 |

|

SU684772A1 |

| Устройство временной коммутации асинхронных цифровых сигналов | 1979 |

|

SU773955A1 |

| Устройство для приема цифровых сигналов | 1989 |

|

SU1646065A1 |

| Устройство для контроля коммутационной системы | 1986 |

|

SU1401639A1 |

| Устройство временной коммутации асинхронных цифровых сигналов | 1989 |

|

SU1700762A1 |

| Устройство для приема цифровых сигналов | 1986 |

|

SU1394444A1 |

Изобретение относится к технике цифровой коммутации сигналов. Цель изобретения - повышение помехозащищенности путем преобразования двоичных сигналов в биимпульсные. Устройство содержит блок 1 накопления сигналов, счетчик 2 чтения,блок 3 выдачи сигналов, блок 4 преобразования сигналов, счетчик 5 записи, выходной регистр 6. Поступающие на 2 вход устройстпа вместе с адресом исходящей линии информационные сигналы записываются в блоке 1 накопления сигналов в ячейку, соответствующую номеру исходящей линии, откуда затем через блок 4 преобразования сигналов переписываются в блок 3 выдачи сиг- налое. Блоки 3 и 4 преобразуют информацию на все исходящие линии в относительный бнинпульсный сигнал, причем это преобразование производится ь одно и то же время по всем каналам. При длине информации, равной N бит, формирование бинмпульсного сигнала занимает 2N тактов. Полное преобразование сигналов во всех каналах занимает 2N циклов счетчика 2 чтения, причем за каждые два цикла производится преобразование одного бите во всех каналах, 3 ил. (Я

изУУ

| Устройство временной коммутации асинхронных цифровых сигналов | 1979 |

|

SU773955A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-05-30—Публикация

1989-12-21—Подача