ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема цифровых сигналов | 1986 |

|

SU1394444A1 |

| Устройство для асинхронной коммутации цифровых сигналов | 1987 |

|

SU1506584A1 |

| Устройство коммутации с эластичной памятью | 1988 |

|

SU1647921A1 |

| Электронный коммутатор | 1988 |

|

SU1626444A1 |

| Устройство преобразования и коммутации сигналов | 1988 |

|

SU1566505A1 |

| Устройство для контроля коммутационной системы | 1986 |

|

SU1401639A1 |

| Устройство пространсктвенно-временной коммутации | 1978 |

|

SU684772A1 |

| Устройство сопряжения асинхронных разноскоростных цифровых сигналов | 1990 |

|

SU1755386A1 |

| Устройство передачи биимпульсных сигналов | 1989 |

|

SU1653169A1 |

| Коммутационное устройство | 1987 |

|

SU1478371A1 |

Изобретение относится к технике цифровой коммутации. Цель - повышение устойчивости приема информации. Устройство содержит блок 1 входящих регистров, блок 2 входящей памяти, блок 3 определения каналов, блок 4 сравнения, счетчик 5 адреса, блок 6 исходящей памяти, регистр 7, счетчик 8 перезаписи. Сущность изобретения заключается в закреплении в процессе установления соединений за каждым временным каналом соответствующего момента времени считывания цифровых сигналов из ячеек входящей памяти, которые обслуживают все эти каналы, и перезаписи сигналов в ячейки исходящей памяти. При этом моменты поступления сигналов из временных каналов в ячейки входящей памяти и моменты считывания сигналов из этих ячеек разнесены во времени на заранее выбранный промежуток, что обеспечивает устранение проскальзываний. 6 ил.

Изобретение относится к технике связи и может быть использовано в системах цифровой коммутации.

Цель изобретения - повышение устойчивости приема информации.

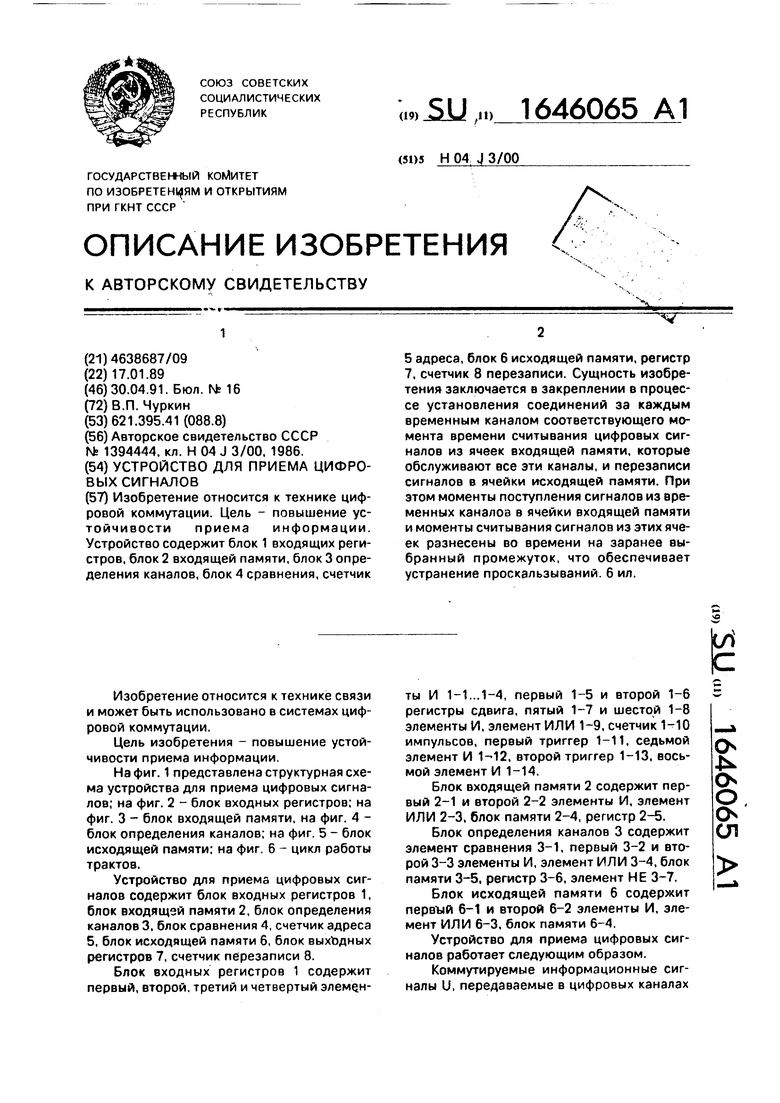

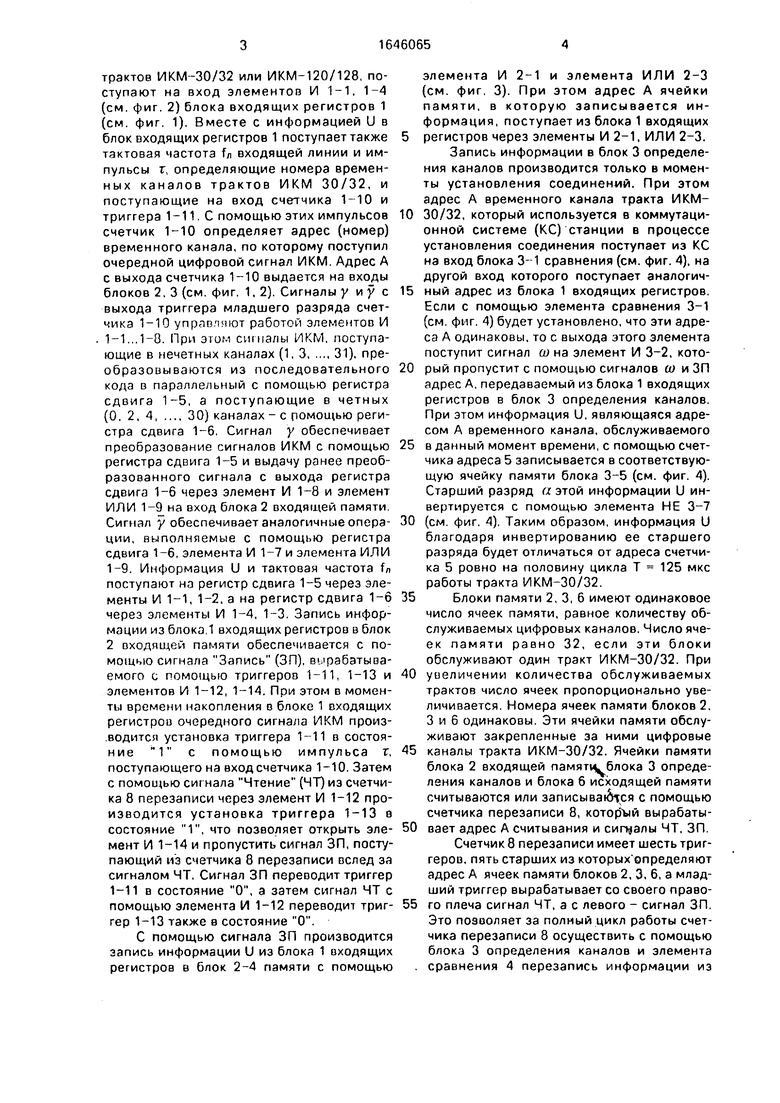

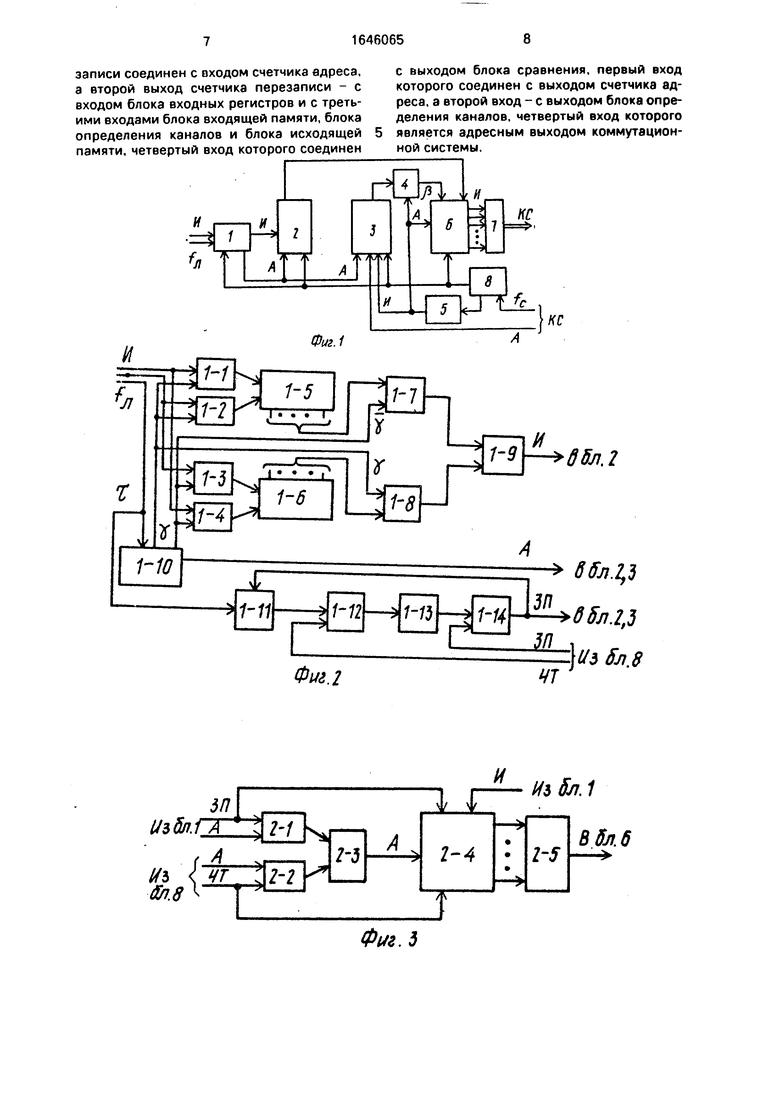

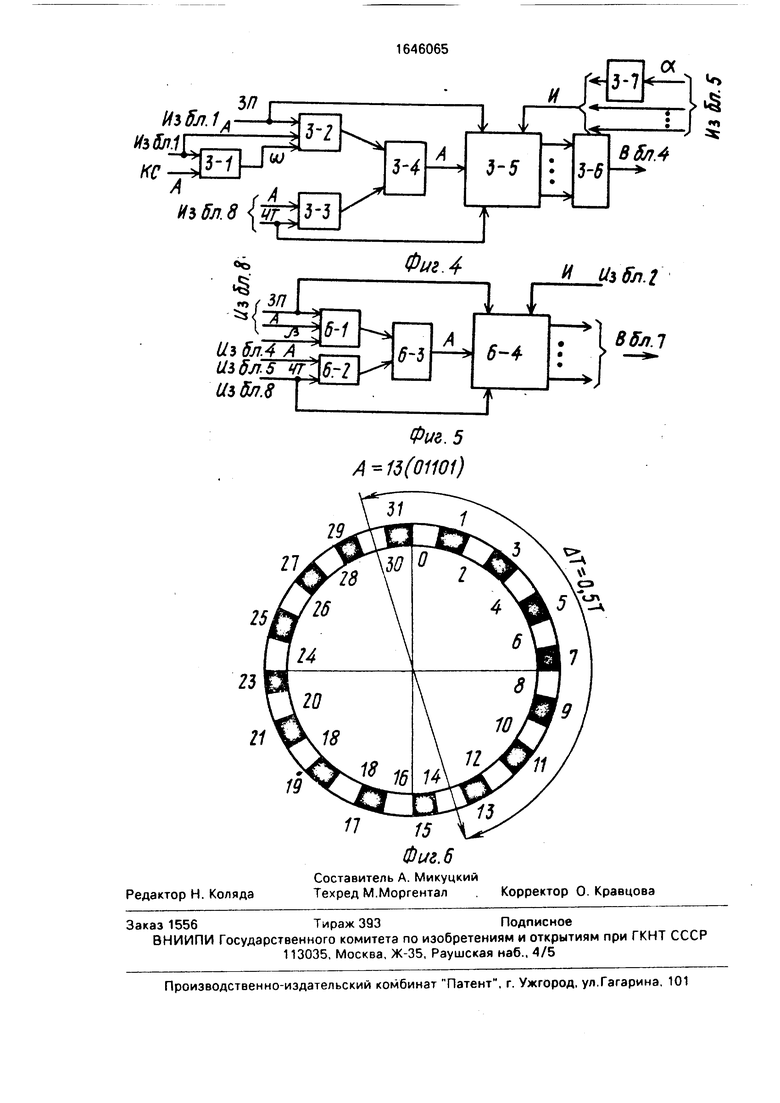

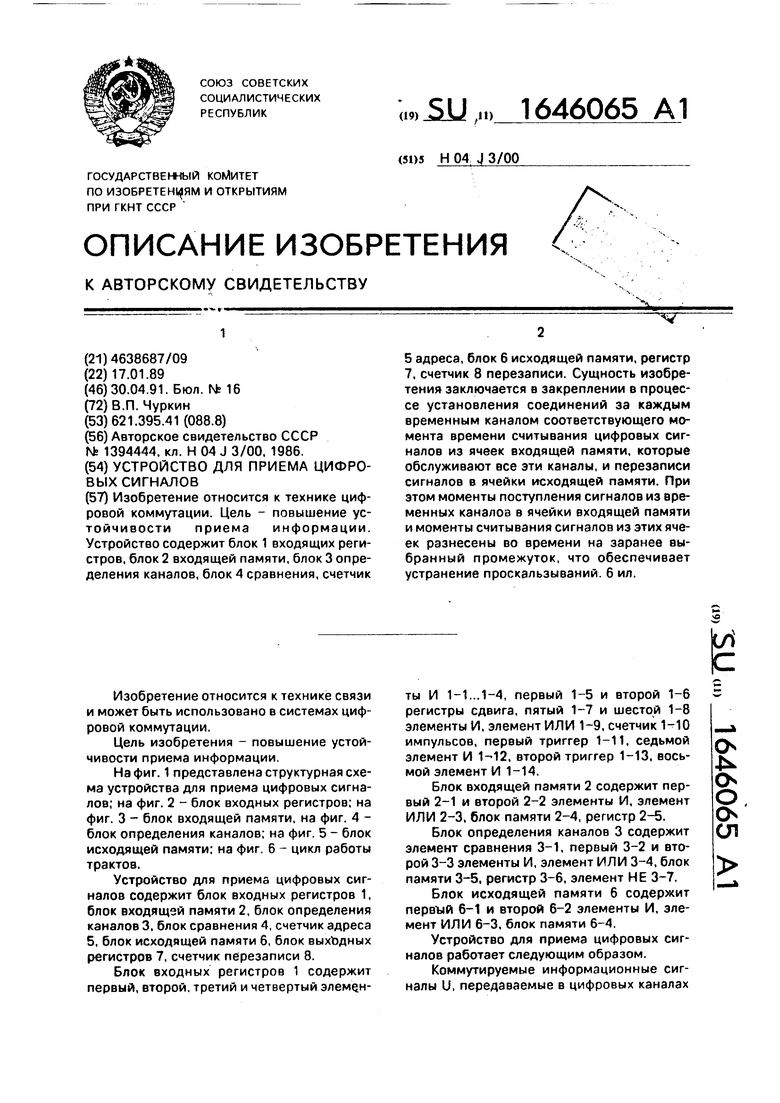

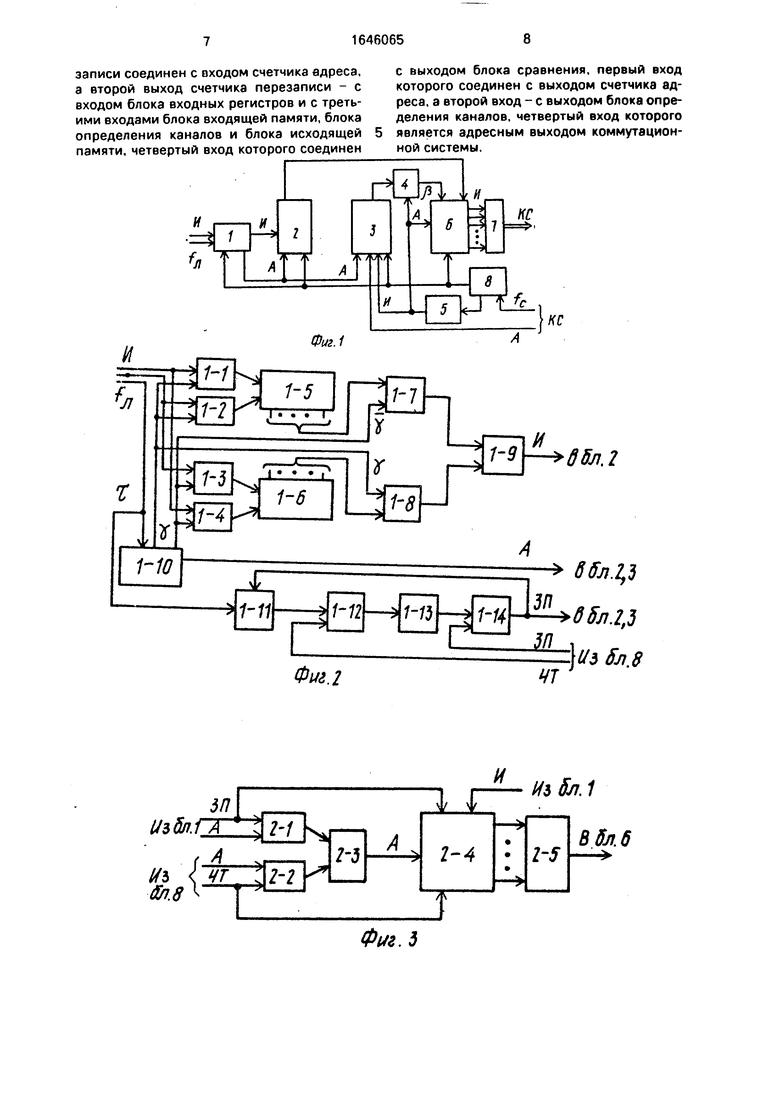

На фиг. 1 представлена структурная схема устройства для приема цифровых сигналов; на фиг. 2 - блок входных регистров: на фиг. 3 - блок входящей памяти, на фиг. 4 - блок определения каналов; на фиг. 5 - блок исходящей памяти: на фиг, 6 - цикл работы трактов.

Устройство для приема цифровых сигналов содержит блок входных регистров 1, блок входящей памяти 2, блок определения каналов 3. блок сравнения 4, счетчик адреса 5, блок исходящей памяти 6, блок выходных регистров 7, счетчик перезаписи 8.

Блок входных регистров 1 содержит первый, второй, третий и четвертый элеме нты И 1-1...1-4, первый 1-5 и второй 1-6 регистры сдвига, пятый 1-7 и шестой 1-8 элементы И, элемент ИЛИ 1-9, счетчик 1-10 импульсов, первый триггер 1-11, седьмой элемент И 1-12, второй триггер 1-13, восьмой элемент И 1-14.

Блок входящей памяти 2 содержит первый 2-1 и второй 2-2 элементы И, элемент ИЛИ 2-3, блок памяти 2-4, регистр 2-5.

Блок определения каналов 3 содержит элемент сравнения 3-1, первый 3-2 и второй 3-3 элементы И, элемент ИЛИ 3-4, блок памяти 3-5, регистр 3-6, элемент НЕ 3-7.

Блок исходящей памяти 6 содержит первой 6-1 и второй 6-2 элементы И, элемент ИЛИ 6-3. блок памяти 6-4.

Устройство для приема цифровых сигналов работает следующим образом.

Коммутируемые информационные сигналы U, передаваемые в цифровых каналах

О 4 О О

сл

рактов ИКМ-30/32 или ИКМ-120/128, потупают на вход элементов И 1-1, 1-4 см. фиг. 2) блока входящих регистров 1 см. фиг. 1). Вместе с информацией U в лок входящих регистров 1 поступает также актовая частота входящей линии и импульсы г, определяющие номера временных каналов трактов ИКМ 30/32, и поступающие на вход счетчика 1-10 и триггера 1-11. С помощью этих импульсов счетчик 1-10 определяет адрес (номер) временного канала, по которому поступил очередной цифровой сигнал ИКМ. Адрес А с выхода счетчика 1-10 выдается на входы блоков 2, 3 (см. фиг. 1, 2). Сигналы у и у с выхода триггера младшего разряда счетчика 1-10 управпчют работой элементов И 1-1...1-8. При эюм сшналы ИКМ, поступающие в нечетных каналах (1, 331), преобразовываются из последовательного кода в параллельный с помощью регистра сдвига 1-5, а поступающие в четных (О, 2, 430) каналах - с помощью регистра сдвига 1-6. Сигнал у обеспечивает преобразование сигналов ИКМ с помощью регистра сдвига 1-5 и выдачу ранее преобразованного сигнала с выхода регистра сдвига 1-6 через элемент И 1-8 и элемент ИЛИ 1-9 на вход блока 2 входящей памяти. Сигнал у обеспечивает аналогичные операции, выполняемые с помощью регистра сдвига 1-6, элемента И 1-7 и элемента ИЛИ 1-9. Информация U и тактовая частота in поступают на регистр сдвига 1-5 через элементы И 1-1, 1-2, а на регистр сдвига 1-6 через элементы И 1-4, 1-3. Запись информации из блока 1 входящих регистров в блок 2 входящей памяти обеспечивается с помощью сигнала Запись (ЗП), вырабатываемого с помощью триггеров 1-11, 1-13 и элементов И 1-12, 1-14. При этом в моменты времени накопления в блоке 1 входящих регистров очередного сигнала ИКМ производится установка триггера 1-11 в состояние 1 с помощью импульса т, поступающего на вход счетчика 1-10. Затем с помощью сиг нала Чтение (ЧТ) из счетчика 8 перезаписи через элемент И 1-12 производится установка триггера 1-13 в состояние 1, что позволяет открыть элемент И 1-14 и пропустить сигнал ЗП, поступающий из счетчика 8 перезаписи вслед за сигналом ЧТ, Сигнал ЗП переводит триггер 1-11 в состояние О, а затем сигнал ЧТ с помощью элемента И 1-12 переводит триггер 1-13 также в состояние О.

С помощью сигнала ЗП производится запись информации U из блока 1 входящих регистров в блок 2-4 памяти с помощью

элемента И 2-1 и элемента ИЛИ 2-3 (см. фиг. 3). При этом адрес А ячейки памяти, в которую записывается информация, поступает из блока 1 входящих

регистров через элементы И 2-1, ИЛИ 2-3. Запись информации в блок 3 определения каналов производится только в моменты установления соединений. При этом адрес А временного канала тракта ИКМ30/32, который используется в коммутационной системе (КС) станции в процессе установления соединения поступает из КС на вход блока 3-1 сравнения (см. фиг. 4), на другой вход которого поступает аналогичный адрес из блока 1 входящих регистров. Если с помощью элемента сравнения 3-1 (см. фиг. 4) будет установлено, что эти адреса А одинаковы, то с выхода этого элемента поступит сигнал ш на элемент И 3-2. который пропустит с помощью сигналов со и ЗП адрес А, передаваемый из блока 1 входящих регистров в блок 3 определения каналов. При этом информация О, являющаяся адресом А временного канала, обслуживаемого

в данный момент времени, с помощью счетчика адреса 5 записывается в соответствующую ячейку памяти блока 3-5 (см. фиг. 4). Старший разряд и этой информации U инвертируется с помощью элемента НЕ 3-7

(см. фиг. 4). Таким образом, информация U благодаря инвертированию ее старшего разряда будет отличаться от адреса счетчика 5 ровно на половину цикла Т 125 мкс работы тракта ИКМ-30/32.

Блоки памяти 2, 3, 6 имеют одинаковое

число ячеек памяти, равное количеству обслуживаемых цифровых каналов. Число ячеек памяти равно 32, если эти блоки обслуживают один тракт ИКМ-30/32. При

увеличении количества обслуживаемых трактов число ячеек пропорционально увеличивается. Номера ячеек памяти блоков 2. 3 и 6 одинаковы. Эти ячейки памяти обслуживают закрепленные за ними цифровые

каналы тракта ИКМ-30/32. Ячейки памяти блока 2 входящей памятц. блока 3 определения каналов и блока 6 исходящей памяти считываются или записываются с помощью счетчика перезаписи 8, которой вырабатывает адрес А считывания и сигналы ЧТ, ЗП. Счетчик 8 перезаписи имеет шесть триггеров, пять старших из которых определяют адрес А ячеек памяти блоков 2, 3, 6, а младший триггер вырабатывает со своего право5 го плеча сигнал ЧТ, а с левого - сигнал ЗП. Это позволяет за полный цикл работы счетчика перезаписи 8 осуществить с помощью блока 3 определения каналов и элемента . сравнения 4 перезапись информации из

всех ячеек блока 2 входящей памяти в блок 6 исходящей памяти. Полный цикл работы счетчика 8 перезаписи равен длительности 3, 9 мкс работы одного временного канала тракта ИКМ-30/32. Таким образом за один временной кана может быть переписана вся информация из ячеек памяти блока 2 в аналогичные ячейки блока 6. Номера временных каналов определяет счетчик адреса 5, который имеет 5 триггеров. Счетчик 5 электрически является продолжением счетчика 8, так как выход старшего разряда счетчика 8 подключен к входу младшего разряда счетчика 5. Синхронизация работы этих счетчиков осуществляется с помощью частоты fc, поступающей из коммутационной системы (см. фиг. 1).

При перезаписи информации из блока 2 входящей памяти в блок 6 исходящей памяти производится синхронное считывание блоков 2 и 3. При этом адрес А считываемой ячейки памяти и сигнал ЧТ поступают из счетчика перезаписи 8 на элемент И 2-2 (см. фиг. 3) и на элемент И 3-3 (см. фиг. 4). С помощью элемента И 2-2, ИЛИ 2-3 информация считывается из блока памяти 2- 4 на регистр 2-5. Аналогично с помощью элемента И 3-3, ИЛИ 3-4 информация считывается из блока памяти 3-5 на регистр 3 -б. На регистрах 2-5 и 3-6 информация сохраняется в течение тактов ЧТ и ЗП. т. е. до следующего такта ЧТ. Информация из блока 2 входящей памяти поступает непосредственно в блок 6 исходящей памяти, а информация из блока 3 определения каналов подается на блоксравнения 4,в котором сравнивается с адресом временного канала из счетчика 5 адреса. Если они совпадают, то элемент сравнения 4 вырабатывает сигнал Д который обеспечивает вместе с сигналом ЗП и адресом А, поступающим из блока 8 перезаписи, запись информации из блока 2 в блок памяти 6-4 (см. фиг. 5) с помощью элементов И 6-1, ИЛИ 6-3. Считывание информации из блока 6 исходящей памяти и выдача ее через регистр 7 в параллельном коде в КС осуществляется в такты ЧТ по адресу А, поступающему из счетчика адреса 5, с помощью элементов И 6-2, ИЛИ 6-3.

Рассмотрим процесс устранения проскальзываний. Предположим, что АТС устанавливает с помощью КС соединение между абонентами. При этом используется тринадцатый временной канал тракта ИКМ-30/32, который обслуживзется с помощью предложенного устройства для приема цифровых сигналов. Тогда из КС на вход блока 3 определения каналов поступит адрес А 01101

тринадцатого временного канала, Этот ад- - рее А будет выдаваться из КС в течение одною цикла Т 125 мкс работы трактов ИКМ-30/32. т. е. будет находиться на вход- ных шинах блока 3 в течение 125 мкс. Так как блок 1 входящих регистров работает на частоте входящей линии связи тл, а остальные блоки устройства на частоте fc станции,, то эти частоты могут отличаться друг от друга. Поэтому адрес А 01101 тринадцатого канала из блока 1 входящих регистров на вход блока 3 определения каналов может поступить в любое время в течение цикла Т, например, когда на счетчике 5 адреса находится адрес А 11110 тридцатого временного канала. Это наглядно показано на фиг. 6. Элемент сравнения 3-1 (см. фиг. 4) выдаст на вход элемента И 3-2 сигнал ш, который вместе с тактом ЗП пропустят через элементы 3-3, ИЛИ 3-4 адрес А 01101. определяющий номер ячейки памяти блока 3-5, в которую записывается номер временного канала из счетчика адреса 5 При записи этой информации осуществляется с

помощью элемента НЕ 3-7 инвертирование старшего разряда а номера тридцатого А 30 (11110) временного канала из счетчика адреса 5. После инвертирования в ячейку памяти с адресом А 13 (01101) будет записан двоичный код 01110 четырнадцатого временного канала (см. фиг. 6), который ровно на половину цикла Т работы трактов ИКМ-30/32 (ДТ 0,5 Т) сдвинут относительно тридцатого временного канала. При этом

промежуток времени Л Т 0,5 Т используется для устранения проскальзывания.

При стабильности частоты работы генераторного оборудования АТС К 1 10 и ЛТ 0,5 Т продолжительность телефонного разговора без проскальзываний ч.

Формула изобретения Устройство для приема цифровых сигналов, содержащее последовательно соединенные блок входных регистров, блок входящей памяти, блок исходящей памяти и блок выходных регистров, а также блок сравнения, блок определения каналов и счетчик адреса, выход которого соединен с

входом блока определения каналов и с вторым входом блока исходящей памяти, второй выход блока входных регистров соединен со вторыми входами блока входящей памяти и блока определения каналов,

отличаю,щееся тем, что. с целью повышения устойчивости приема информации, в него введен счетчик перезаписи, вход которого является выходом коммутационной системы, первый выход счетчика перезаписи соединен с входом счетчика адреса,с выходом блока сравнения, первый вход а второй выход счетчика перезаписи - скоторого соединен с выходом счетчика ад- входом блока входных регистров и с треть-реса, а второй вход - с выходом блока опре- ими входами блока входящей памяти, блокаделения каналов, четвертый вход которого определения каналов и блока исходящей5 является адресным выходом коммутацион- памяти, четвертый вход которого соединенной системы.

Фиг. 2

85л. 2

fffa.2,3

О 6л.2J

}из 5л.8

В$л6

Фм.З

3/7

ИзБл.1А-С toSn.1

ЛГ

И 6л. 8 fw

29

26

18

19

В 5лА

JLJbfa.t

Вбл.1

Фиг. 5 А 13(01101)

31

1

18

16 W

12

11

| Устройство для приема цифровых сигналов | 1986 |

|

SU1394444A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1991-04-30—Публикация

1989-01-17—Подача