ОЭ С71

Јь

СО

оо го

Изобретение относится к технике электросвязи и может использоваться для контроля качества дискретных каналов связи.

Цель изобретения - повышение достоверности измерения.

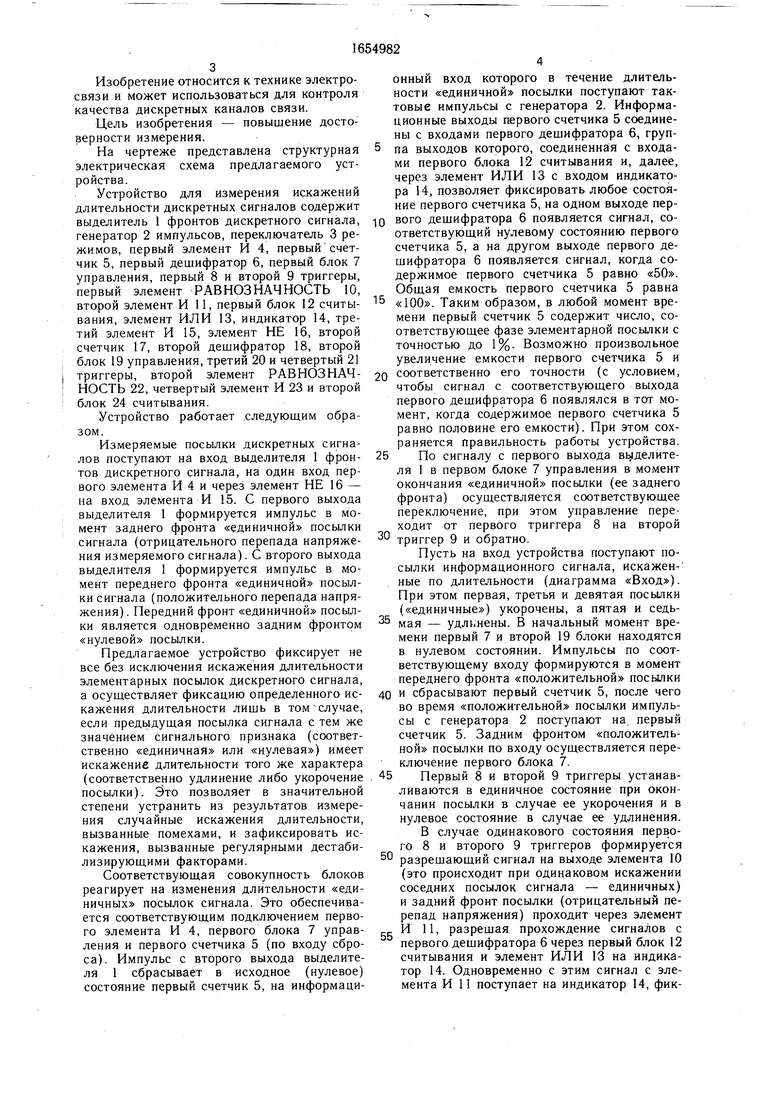

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство для измерения искажений длительности дискретных сигналов содержит выделитель 1 фронтов дискретного сигнала, генератор 2 импульсов, переключатель 3 режимов, первый элемент И 4, первый счетчик 5, первый дешифратор 6, первый блок 7 управления, первый 8 и второй 9 триггеры, первый элемент РАВНОЗНАЧНОСТЬ 10, второй элемент И 11, первый блок 12 считывания, элемент ИЛИ 13, индикатор 14, третий элемент И 15, элемент НЕ 16, второй счетчик 17, второй дешифратор 18, второй блок 19 управления, третий 20 и четвертый 21 триггеры, второй элемент РАВНОЗНАЧНОСТЬ 22, четвертый элемент И 23 и второй блок 24 считывания.

Устройство работает следующим образом.

Измеряемые посылки дискретных сигналов поступают на вход выделителя 1 фронтов дискретного сигнала, на один вход первого элемента И 4 и через элемент НЕ 16 - на вход элемента И 15. С первого выхода выделителя 1 формируется импульс в момент заднего фронта «единичной посылки сигнала (отрицательного перепада напряжения измеряемого сигнала). С второго выхода выделителя 1 формируется импульс в момент переднего фронта «единичной посылки сигнала (положительного перепада напряжения). Передний фронт «единичной посылки является одновременно задним фронтом «нулевой посылки.

Предлагаемое устройство фиксирует не все без исключения искажения длительности элементарных посылок дискретного сигнала, а осуществляет фиксацию определенного искажения длительности лишь в том4случае, если предыдущая посылка сигнала с тем же значением сигнального признака (соответственно «единичная или «нулевая) имеет искажение длительности того же характера (соответственно удлинение либо укорочение посылки). Это позволяет в значительной степени устранить из результатов измерения случайные искажения длительности, вызванные помехами, и зафиксировать искажения, вызванные регулярными дестабилизирующими факторами.

Соответствующая совокупность блоков реагирует на изменения длительности «единичных посылок сигнала. Это обеспечивается соответствующим подключением первого элемента И 4, первого блока 7 управления и первого счетчика 5 (по входу сброса). Импульс с второго выхода выделителя 1 сбрасывает в исходное (нулевое) состояние первый счетчик 5, на информационный вход которого в течение длительности «единичной посылки поступают тактовые импульсы с генератора 2. Информационные выходы первого счетчика 5 соединены с входами первого дешифратора 6, группа выходов которого, соединенная с входами первого блока 12 считывания и, далее, через элемент ИЛИ 13 с входом индикатора 14, позволяет фиксировать любое состояние первого счетчика 5, на одном выходе первого дешифратора 6 появляется сигнал, соответствующий нулевому состоянию первого счетчика 5, а на другом выходе первого дешифратора 6 появляется сигнал, когда содержимое первого счетчика 5 равно «50. Общая емкость первого счетчика 5 равна

«100. Таким образом, в любой момент времени первый счетчик 5 содержит число, соответствующее фазе элементарной посылки с точностью до 1%. Возможно произвольное увеличение емкости первого счетчика 5 и

0 соответственно его точности (с условием, чтобы сигнал с соответствующего выхода первого дешифратора 6 появлялся в тот момент, когда содержимое первого счетчика 5 равно половине его емкости). При этом сохраняется правильность работы устройства,

5 По сигналу с первого выхода выделителя 1 в первом блоке 7 управления в момент окончания «единичной посылки (ее заднего фронта) осуществляется соответствующее переключение, при этом управление переходит от первого триггера 8 на второй

0 триггер 9 и обратно.

Пусть на вход устройства поступают посылки информационного сигнала, искаженные по длительности (диаграмма «Вход). При этом первая, третья и девятая посылки («единичные) укорочены, а пятая и седь5 мая - удльнены. В начальный момент времени первый 7 и второй 19 блоки находятся в нулевом состоянии. Импульсы по соответствующему входу формируются в момент переднего фронта «положительной посылки

0 и сбрасывают первый счетчик 5, после чего во время «положительной посылки импульсы с генератора 2 поступают на первый счетчик 5. Задним фронтом «положительной посылки по входу осуществляется переключение первого блока 7.

5 Первый 8 и второй 9 триггеры устанавливаются в единичное состояние при окончании посылки в случае ее укорочения и в нулевое состояние в случае ее удлинения. В случае одинакового состояния первого 8 и второго 9 триггеров формируется

0 разрешающий сигнал на выходе элемента 10 (это происходит при одинаковом искажении соседних посылок сигнала - единичных) и задний фронт посылки (отрицательный перепад напряжения) проходит через элемент

Б И 11, разрешая прохождение сигналов с первого дешифратора 6 через первый блок 12 считывания и элемент ИЛИ 13 на индикатор 14. Одновременно с этим сигнал с элемента И 11 поступает на индикатор 14, фиксируя сигнальный признак посылки, на которой зафиксировано искажение длительности.

Второй счетчик 17 устанавливается в нулевое состояние задним фронтом «единичной посылки (т. е. передним фронтом «нулевой посылки) сигнала; импульсы с генератора 2 поступают на вход элемента И 15 в течение интервала «нулевых посылок, что обеспечивается разрешающим сигналом на элемент И 15, снимаемым с элемента НЕ 16. Переключение второго блока 19 осуществляется по переднему фронту «положительной посылки (или по заднему фронту «отрицательной, «нулевой посылки).

Переключатель 3 выполняет следующие функции, обеспечивая работу в трех режимах. В первом режиме с обоих выходов переключателя 3 на первый 4 и третий 15 элементы И поступает разрешающий сигнал, что обеспечивает фиксацию искажений дли10

15

поступает на вход элемента И 23 и далее на вход второго блока 24 считывания.

Формула изобретения

Устройство для измерения искажений длительности дискретных сигналов, содержащее выделитель фронтов дискретного, сигнала, вход которого является входом устройства, генератор импульсов, индикатор, последовательно соединенные первый элемент И, первый и второй входы которого соединены соответственно с входом выделителя фронтов дискретного сигнала, и выходом генератора импульсов, первый счетчик, второй вход которого соединен с первым выходом выделителя фронтов дискретного сигнала, первый дешифратор, первый блок управления и первый триггер, второй элемент И, второй вход которого соединен с вторым входом первого блока управления и втотельности посылок для обоих значений сиг- 20 Рым выходом выделителя фронтов дискретнального признака. Этот режим обеспечивает наиболее полную измерительную информацию. Второй режим реализует работу, снимая разрешающий сигнал с элемента И 15.

ного сигнала, второй триггер, вход и выход которого соединены соответственно с вторым выходом первого блока управления, первый блок считывания, второй вход которого соеТретий режим аналогично позволяет рабо- динен с вторым выходом первого дешифрато Р ОТ (4JIJ 1 d ГЧООПЛГТТО VMIT 1Л Ы / ТЛГЧ О ГТ i ПЛПТ1Л Э r OSbf Л tlM fl t1 fbfij n im п 1 ТЛ i-tj-411 t I

тать, снимая разрешающий сигнал с первого элемента И 4.

ра, отличающееся тем, что, с целью повышения достоверности измерения, введены переключатель режимов, элемент ИЛИ, первый элемент РАВНОЗНАЧНОСТЬ, последовательно соединенные элемент НЕ, вход котоНеобходимость в реализации второго и третьего режимов обусловлена наличием в информационных сигналах при некоторых способах передачи информации специальных посылок (так называемых стартовых и стоповых), длительность которых отличается от длительности элементарных информационных посылок в некратное число раз. Они могут также фиксироваться в первом режиме, что может при некритическом анализе исказить измерительную информацию. Знанфк факта наличия таких специальных посылок либо анализ результатов измерений позволяет переходом в соответствующий режим (второй или третий, исходя из полярности, т. е. значения сигнального признака таких посылок) исключить их влияние на результаты измерения.

40 рой блок считывания, первый и второй входы и выходы которого соединены соответственно с выходом второго дешифратора, выходом четвертого элемента И и первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом

Во втором режиме сигнал с выхода вто- первого блока считывания, и первым вхорого счетчика 17 поступает на второй дешифратор 18. С соответствующих выходов второго дешифратора 18 сигналы поступают на второй блок 19 управления и на второй блок 24 считывания. Третий 20 и четвертый 21 триггеры устанавливаются в соответствующие состояния по сигналам с выходов второго блока 19 управления. Это состояние с выхода соответствующего третьего 20 или четвертого 21 триггера через элемент 22

дом индикатора, второй и третий входы которого соединены соответственно с выходами второго и четвертого элементов И, четвертый триггер, вход и выход которого соеди- gg йены соответственно с вторым выходом блока управления и вторым входом второго элемента РАВНОЗНАЧНОСТЬ, первый и второй выходы переключателя режимов соединены соответственно с третьими входами первого и третьего элементов И.

поступает на вход элемента И 23 и далее на вход второго блока 24 считывания.

Формула изобретения

Устройство для измерения искажений длительности дискретных сигналов, содержащее выделитель фронтов дискретного, сигнала, вход которого является входом устройства, генератор импульсов, индикатор, последовательно соединенные первый элемент И, первый и второй входы которого соединены соответственно с входом выделителя фронтов дискретного сигнала, и выходом генератора импульсов, первый счетчик, второй вход которого соединен с первым выходом выделителя фронтов дискретного сигнала, первый дешифратор, первый блок управления и первый триггер, второй элемент И, второй вход которого соединен с вторым входом первого блока управления и вто0 Рым выходом выделителя фронтов дискретРым выходом выделителя фронтов дискретного сигнала, второй триггер, вход и выход которого соединены соответственно с вторым выходом первого блока управления, первый блок считывания, второй вход которого соединен с вторым выходом первого дешифратоr OSbf Л tlM fl t1 fbfij n im п 1 ТЛ i-tj-411 t I

ра, отличающееся тем, что, с целью повышения достоверности измерения, введены переключатель режимов, элемент ИЛИ, первый элемент РАВНОЗНАЧНОСТЬ, последовательно соединенные элемент НЕ, вход которого соединен с входом выделителя фронтов дискретного сигнала, третий элемент И, второй вход которого соединен с выходом генератора импульсов, второй счетчик, второй вход которого соединен с вторым выходом выделителя фронтов дискретного сигнала,

второй дешифратор, второй блок управления, третий триггер, второй элемент РАВНОЗНАЧНОСТЬ и четвертый элемент И, второй вход которого соединен с вторым входом второго блока управления и первым выходом делителя фронтов дискретного сигнала, второй блок считывания, первый и второй входы и выходы которого соединены соответственно с выходом второго дешифратора, выходом четвертого элемента И и первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом

первого блока считывания, и первым входом индикатора, второй и третий входы которого соединены соответственно с выходами второго и четвертого элементов И, четвертый триггер, вход и выход которого соеди- g йены соответственно с вторым выходом блока управления и вторым входом второго элемента РАВНОЗНАЧНОСТЬ, первый и второй выходы переключателя режимов соединены соответственно с третьими входами первого и третьего элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения искажений длительности дискретных сигналов | 1982 |

|

SU1054918A1 |

| Устройство для контроля работы трансмиттера | 1980 |

|

SU926660A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Устройство для измерения искажений дискретных сигналов | 1984 |

|

SU1172054A1 |

| Устройство для измерения преобладаний дискретных сигналов | 1979 |

|

SU879805A1 |

| Устройство для сопряжения | 1975 |

|

SU594497A1 |

| Устройство для измерения скорости телеграфирования | 1985 |

|

SU1288927A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| Цифровой демодулятор сигналовчАСТОТНОй ТЕлЕгРАфии | 1979 |

|

SU794764A1 |

Изобретение относится к технике электросвязи. Цель изобретения - повышение достоверности измерения. Устройство содержит выделитель 1 фронтов дискретного сигнала, генератор 2 импульсов, переключатель 3 режимов, четыре элемента И 4, 11, 15 и 23, два счетчика 5 и 17, два дешифратора 6 и 18, два блока 7 и 19 управления, четыре триггера 8, 9, 20 и 21, два элемента РАВНОЗНАЧНОСТЬ 10 и 22, два блока 12 и 24 считывания, элемент ИЛИ 13, элемент НЕ 16, индикатор 14. Измеряемые посылки поступают на вход выделителя 1, на вход первого элемента И 4 и через элемент НЕ 16 - на вход третьего элемента И 15. Переключатель 3 режимов обеспечивает работу устройства в трех режимах: режим измерения искажений «нулевых посылок и «единичных посылок; режим измерения искажений «нулевых посылок; режим измерения искажений «единичных посылок. Этим обеспечивается достижение поставленной цели. 1 ил ю

| Устройство для измерения искажений длительности дискретных сигналов | 1982 |

|

SU1054918A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-06-07—Публикация

1989-04-12—Подача