1

Изобретение относится к электросвязи и может использоваться для передачи данных дискретной информации. Известен цифровой демодулятор сигналов частотной телеграфии, содержащий блок ключей, дешифратор, блок определения рабочей частоты, делитель частоты, блок запуска, два ограничителя, дифференцирующую цепь, иолосовой фильтр и опорный генератор, выход которого подключен к входу первого ограничителя, выход которого соединен к первым входом делителя частоты, второй вход которого соединен с первым выходом блока запуска, второй выход которого соединен с первым входом блока определения рабочей частоты и с первым входом дешифратора, второй вход которого соединен с первым выходом делителя частоты, второй выход которого подключен к второму входу блока определения рабочей частоты, выход которого соединен с пepвы выходом блока ключей, второй вход которого соединен с первым выходом дешифратора, второй выход которого подключен к третьему входу блока ключей, кроме того, выход полосового фильтра подключен к входу второго ограничителя, выход которого соединен с входом дифференцирующей цепи, выход которой подключен к входу блока запуска 1.

Однако в известном цифровом демодуляторе имеется наличие временных искажений в разрядах принимаемых комбинаций, оиределяемых наличием в устройстве

блока сравнения, фильтра нижних частот и решающей схемы.

Цель изобретения - уменьшение временных исках ений сигналов.

Для этого в цифровой демодулятор,

содержащий блок ключей, дешифратор, блок определения рабочей частоты, делитель чаетоты, блок запуска, два ограничителя, дифференцирующую цепь, полосовой фильтр и опорный генератор, выход

которого подключен к входу первого ограничителя, выход которого соединен с первым входом делителя частоты, второй вход которого соединен с первым выходом блока запуска, второй выход которого соединен с первым входом блока определения рабочей частоты и с первым входом дешифратора, второй вход которого соединен с первым выходом делителя частоты, второй выход которого подключен к зторому

входу блока определения рабочей частоты, выход которого соединен с первым входом блока ключей, второй вход которою соединен с первым выходом депдифратора, второй выход которого подключен к третьему входу блока ключей, кроме того, вы3 ,

ход полосового фильтра подключен к входу второго ограничителя, выхо.ч кото)ого соединен с входом дифференциру101цен цепи, выход которой подключен к входу блока запуска, введены блок фо)мироваиия разрядов принимаемой информации, блок управления, решающий блок и блок определения разряда принимаемой посылки, первый вход которого соединен с выходом блока ключей, второй вход блока определения разряда принимаемой посылки соединен с первым выходом блока управления, второй выход которого подключен к первому входу решающего блока и к первому входу блока формирования разрядов принимаемой пнформации, третий выход блока управления подключен к второму входу блока формирования разрядов принимаемой информации и к второму входу решающего блока, четвертый выход блока управления соединен с третьим входом блока формирования разрядов нрмнимаемой ицформации, четвертый вход которого соединен с первым выходом )ешающего блока и с первым входом блока управления, пятый вход блока формирования разрядов п|)инимаемой информации соединен с вторым выходом решающего блока п с вторым входом блока управления, третий вход которого соединен с четвертым входом блока ключей и с первым вы.ходом блока формирования разрядов принимаемой информации, четвертый вход блока управления соединен е третьим выходом рещающего блока, пятый вход блока управления соединен с вторым выходом блока формирования разрядов принимаемой информации и с пятым входом блока ключей, шестой вход блока управления соединен с первым выходом блока определения разряда принимаемой посылки, второй выход которого соединен с третьим входом решающего блока, третий выход блока определения разряда принимаемой посылки соединен с седьмым входом блока управления, при этом выход первого ограничителя подключен к четвертому входу решающего блока, кроме того, блок определения разряда принимаемой посылки выполнен в виде двух дешифраторов, триггера, счетчика, элемента И, первый вход которого соединен с первым входом триггера, первый выход которого подключен к второму входу элемента И, выход которого соединен с первым входом счетчика, второй вход которого соединен с вторым выходом триггера, выход счетчика соединен с входами дешифраторов, при этом первый вход элемента И, второй вход трнггера и выходы дешифраторов являются соответственно входами и выходами всего блока, кроме того, решающий блок выполнен в виде трех дешифраторов, двух счетчиков, элемента ИЛИ, элемента И и двух триггеров, выход первого т|)иггера подключен

4

к пе)1юму входу элемента И, выход кочорого соединен с первым входом элемента ИЛИ, второй вход которого соединен с первым входом второго триггера и с пер5 вым входом первого счетчика, второй вход которого соединен с выходом второго триггера, выход первого счетчика соединен с входом первого дешифратора, выход элемента ИЛИ соединен с первым входом 1вто10 рого счетчика, выход которого соединен с входом второго и третьего дешифраторов, выход второго дешифратора соедииен с первым входом первого счетчика, причем входы первого триггера, второй вход второД.5 го триггера, вторые входы элемента И и второго счетчика, а также выходы дешифраторов являются соответственно вхОхЧами и выходами всего блока, кроме того, блок управления выполнен в виде трех элеменQQ тов ИЛИ, триггера и трех элементов И, выход первого элемеита И соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и с первым входом вто25 рого элемента ИЛИ, второй вход которого соединен с третьим входом первого элемента ИЛИ, с выходом третьего элемента ИЛИ и с первым входом триггера, выход которого соединен с первым входом третьgQ его элемента И, второй вход триггера соединен с первым входом второго элемента И, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ, нричем два входа первого элемента И,вто5 вход третьего элемента И, второй вход третьего элемента ИЛИ, третий и четвертый входы первого элемента ИЛИ, первый и второй входы второго элемента И и выходы первого и второго элемента ИЛИ, Q первого элемента И являются соответственно входами и выходами всего блока, кроме того, блок формирования разрядов принимаемой информации выполнен в виде двух элементов И, элемента ИЛИ, двух 5 триггеров, первый выход первого триггера подключен к первому входу первого элемента И, второй вход которого соедииен с первым входом второго элемента И, второй вход которого соединен с вторым Q выходом первого триггера, выход второго элемента И подключен к первому входу элемента ИЛИ, выход которого соединен с первым входом второго триггера, второй вход которого соединен с выходом nejjBoro r элемента И, причем входы nepBoix) триггера, вторые и третьи входы элемента ИЛИ, вход второго элемента И и первый и второй выходы первого триггера являются со- ответственно входами и выходами всего блока.

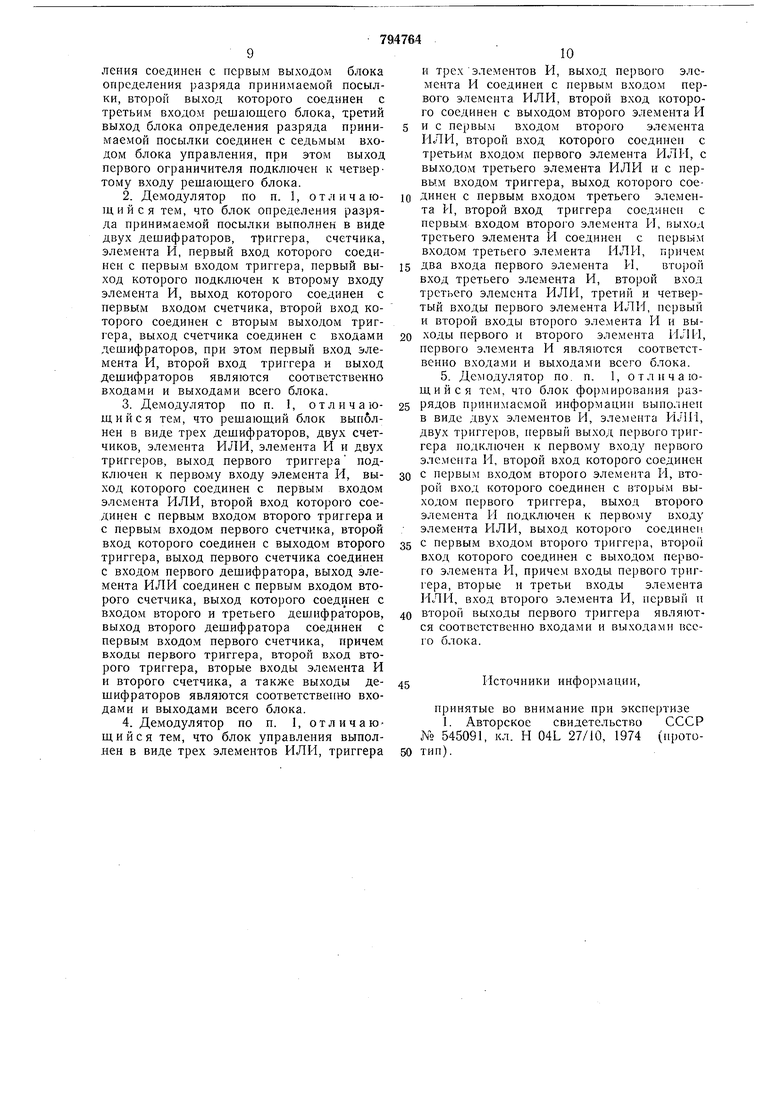

Иа чертеже приведена структурная электрическая схема предлагаемого демодулятора.

Демодулятор содержит опорный генератор 1, первый ограпичитель 2, делитель 3 частоты, полосовой фильтр 4, второй ограничитель 5, дифференцирующую цепь 6, блок 7 запуска, блок 8 определения рабочей частоты, дешифратор 9, блок 10 ключей, блок 11 определения разряда принимаемой посылки, решающий блок 12, блок 13 управления и блок 14 формирования разрядов принимаемой информации.

Блок 11 содержит счетчик 15, элемент И 16, триггер 17 и дешифраторы 18 и 19. Блок 12 содержит счетчики 20 и 21, дешифраторы 22 и 23, первый триггер 24, элемент ИЛИ 25, элемент И 26, второй триггер 27 и третий дешифратор 28.

Блок 13 содержит элементы И 29, 30 и 31, триггер 32 и элементы ИЛИ 33, 34 и 35.

Блок 14 содержит триггеры 36 и 37, элементы И 38 и 39 и элемент ИЛИ 40.

Демодулятор работает следующим образом.

Иоступающие на вход демодулятора сигналы фильтруются в фильтре 4 и ограничиваются в ограничителе 5.

Прямоугольная последовательность частотио-манипулированных импульсов с ограничителя 5 поступает на цепь 6. С выхода цепи 6 короткие импульсы, соответствующие переходам входных сигналов через нуль, поступают на блок 7.

Блоком 7 по сигналам цепи 6 вырабатываются импульсы начала деления частоты опорных колебаний генератора 1, ограниченных в ограничителе 2 делителем 3 и импульсы опроса дешифратора 9 и блока 8, следующие с периодом частоты действующего на входе сигнала. Импульсы начала деления частоты следуют непосредственно за импульсами опроса и устанавливают в исходное состояние делитель 3. После импульса начала .аеления делитель 3 начинает делить частоту опорных колебаний. Процесс деления продолжается до прихода импульса опроса, т. е. нро.межуток времени, равный периоду частоты входного сигнала.

Если на входе демодулятора действуют сигналы, соответствуюшие единичному и нулевому разрядам посылки с частотами, находящимися в рабочей полосе частот демодулятора, то за периоды входных сигналов делитель 3 будет принимать такие состояния, что блок 8 ио ним и но импульсам опроса е блока 7 будет формировать сигналы, открывающие блок 10, а дешифратор 9 дешифрировать состоянии дели-те ля 3 и сигнал импултзса опроса с блока 7 сигналами на своих выходах.,

При действии на входе демодулятора сигнала единичного разряда посылки на одном и при действии сигнала нулевого разряда на другом выходах дешифратора 9 появляются импульсы, число которых равно числу периодов характертгстических

частот, приходящихся на разряды комбинаций.

В исходном состоянии в блоке 11 счетчик 15 удерл ивается в нулевом состоянии единичным потенциалом, поданным на его установочный вход с инверсного выхода триггера 17, а основной вход счетчика 15 закрыт за счет подачи на управляющий вход элемента И 16 нулевого потенциала с пря.того выхода триггера 17. Дешифраторы 18 и 19 запрограммированы на дешифрацию состояний счетчика 15, соответствующих единичному и нулевому разрядам носылок соответственно и в зависимости от скорости передачи ииформации (от длительности разрядов посылки).

В блоке 12 счетчик 20 удерживается в нулевом состоянии единичным поте}щиалом, поданным на его установочный вход через элемент ИЛИ 25 с выхода элемента И 26, на входы которого поданы единичные потенциалы с инверсных выходов триггеров 17 и 27. Дешифраторы 22 и .23 запрограммированы на дешифрацию состояний счетчика 20, изменяемых по сигналам с выхода первого ограничителя 2, соответствующих признаков наличия и окончания разрядов комбинаций в соответствии со скоростью передачи информации. Счетчик 21 удерживается в нулевом состоянии единичным потенциалом, поданным на его установочный вход с инверсного выхода триггера 24. Программируемый дешифратор 28 запрограммирован на деш 1фрацию состояний счетчика 21, изменяемых по сигналам от дешифратора 23, соответствующих признаку окончания всей принимаемой информации в зависимости от выбранной скорости передачи информации.

В блоке 13 триггер 32 находится в исходном состоянии, при котором единичный потенциал находится на инверсном выходе триггера 32.

В блоке 14 триггеры 36 и 37 находятся в исходных состояниях, при которых единичные потенциалы находятся на инверсных выходах, при этом единичный потенциал с инверсного выхода триггера 36 нодан на дополнительный вход блока 10 и обеспечивает подключение вы.хода дешифратора 9, на котором иоявляются импульсы, соответствующие единичным разрядам посылок, к в.чоду блока 11.

При постунленни на вход демодулятора сигнала с характеристической частотой единичного разряда импульсы с выхода блока 10 поступают на в.ход блока 11. Триггер 17 от первого же импульса из.меняет свое состояние и разрешает )аботу счетчиков 15 и 20. В результате начинаются два ироцесса - опознания разрядов носылок и формирования признаков принимаемых посылок. Когда на вход блока 11 поступит число импульсов, которое установит счетчик 15 в состояние, дешифрируемое дешифратором 19, то сигналом с выхода дешифратора 19 триггер 32 блока 13 изменит состояние и тем самым обеспечит обработку единичного разряда. При дальнейшем поступлении импульсов на вход блока 11 счетчик 15 установится в такое состояние, при котором дешифратор 18 выработает сигнал, который через элемент И 29 поступит на триггеры 27, 36 л через элемент ИЛИ 34 на установку в исходное состояние триггера 17. Установка триггера 27 обеснечит работу блока )2 на продолжении всей посылки, а триггера 36-переключение блока 10, установку триггера 37 в единичное состояние через элемент И 38 по сигналам признака разряда комбинации с дешифратора 22, отпирание элемента И 30 и запирание элемента И 29.

При поступлении на вход демодулятора сигнала нулевого разряда блок 11 функционирует описанным способом, но теперь сигнал с дешифратора 19 через элемент И 30, элемент ИЛИ 34 поступает на установку в исходное состояние триггера 17 и триггера 36, что обеспечивает установку в нулевое состояние триггера 37 через элемент И 39 и элемент ИЛИ 40 по сигналу признака разряда посылок с дешифратора 22, переключение блока 10 и отпирание элемента И 29 и запирание элемента И 30.

При формировании признака окончания разряда сигнал окончания разряда с выхода дешифратора 23 через элемент ИЛИ 34 приводит блок 11 в исходное состояние, установку счетчика 20 в нулевое состояние через элемент ИЛИ 25 и разрешение подсчета числа разрядов посылок счетчиком 21 за счет установки триггера 24.

Описанным выше способом происходит демодуляция разрядов прини.адаемых посылок. Окончание формирования разрядов принимаемых посылок происходит по последнему разряду посылок, либо по сформированному сигналу дешифратором 28, подаваемому через элемент ИЛИ 35 на установку в исходное состояние блоков 12, 13 и 14, а через элемент ИЛИ 34 на установку в исходное состояние блока П.

Если будет сформирован сигнал признака разряда посылок дешифратором 22 при условии запуска триггера 17 от помех, то этот сигнал через элемент И 31 и элемент ИЛИ 35 приведет все узлы демодулятора в исходное состояние.

Введение в демодулятор блока опреде-ления разряда принимаемой посылки решаюш,его блока, а также схем управления и формирования разрядов принимаемой информации и наличие вручную либо автоматически программируемых дешифраторов позволяет полностью исключить временные искажения разрядов принимаемых посылок.

Формула изобретения

1. Цифровой демо,.:1.улято1) сигналов частотной телеграфин, содержащ1 й блок ключей, дешифратор, блок определения рабочей частоты, делитель частоты, блок запуска, два ограничителя, дифференцируюш.ую цепь, полосовой- фильтр и опорный генератор, выход которого подключен к входу первого ограничителя, выход которого соединен с первым входом делителя частоты, второй вход которого соединен с первым выходом блока запуска, второй выход которого соединен с первым входом блока определения рабочей частоты и с первым входом дешифратора, второй вход которого соединен с nejJBbiM выходом делителя частоты, второй выход которого подключен к второму входу блока определения рабочей частоты, выход KOTOpoio соединен с первы.м входом блока ключей, второй вход которого соединен с первым выходом дешифратора, второй выход которого подключен к третьему входу блока ключей, кроме того, выход полосового фи.чьтра подключен к входу второго ограничителя, выход которого соединен с входом дифференцирующей цепи, выход которой подключен к входу блока запуска, отличающийся тем, что, с целью уменьшения временных искажений сигналов, введены блок формирования разрядов принимаемой информации, блок управления, решающий блок и блок определения разряда принимаемой посылки, первый вход которого соединен с выходом блока ключей, второй вход блока определения разряда принимаемой посылки соединен с первым выходом блока управления, второй выход которою подключен к первому входу решающего блока и к первому входу блока формирования разрядов принимаемой информации, третий выход блока управления подключен к второму входу блока формирования разрядов принимаемой информации и к второму входу решающего блока, четвертый выход блока управления соединен с третьим входом блока формирования разрядов принимаемой информации, четвертый вход которого соединен с первым выходом решающего блока и с первым входом блока управления, пятый вход блока формирования разрядов принимаемой информации соединен с вторым выходом решающего блока и с вторым входом блока управления, третий вход которого соединен с четвертым входом блока ключей и с первым выходом блока формирования разрядов принимаемой информации, четвертый вход блока управления соединен с третьим выходом решающего блока, пятый вход блока управления соединен с вторым выходом блока формирования разрядов принимаемой информации и с пятым входом блока ключей, шестой вход блока управ9

ления соединен с первым выходом блока определения разряда принимаемой посылки, второй выход которого соединен с третьим входом решающего блока, третий выход блока определения разряда принимаемой посылки соединен с седьмым входом блока управления, при этом выход первого ограничителя подключен к четвертому входу решающего блока.

2.Демодзлятор по п. 1, отличающийся тем, что блок определения разряда принимаемой посылки выполнен в виде двух дешифраторов, триггера, счетчика, элемента И, первый вход которого соединен с первым входом триггера, первый выход которого подключен к второму входу элемента И, выход которого соедниен с первым входом счетчика, второй вход которого соединен с вторым выходом триггера, выход счетчика соединен с входами дешифраторов, при этом первый вход элемента И, второй вход триггера и выход дешифраторов являются соответственно входами и выходами всего блока.

3.Демодулятор по п. 1, отличающийся тем, что решающий блок выполнен в виде трех дешифраторов, двух счетчиков, элемента ИЛИ, элемента И и двух триггеров, выход первого триггера подключен к первому входу элемента И, выход которого соединен с первым входом эле.мента ИЛИ, второй вход которого соединен с первым входом второго триггера и с первым входом первого счетчика, второй вход которого соединен с выходом второго триггера, выход первого счетчика соединен с входом первого дещифратора, выход элемента ИЛИ соединен с первым входом второго счетчика, выход которого соединен с входом второго и третьего дешифраторов, выход второго дешифратора соединен с первым входом первого счетчика, причем входы первого триггера, второй вход второго триггера, вторые входы элемента И и второго счетчика, а также выходы дешифраторов являются соответственно входами и выходами всего блока.

4.Демодулятор по п. 1, отличающий с я тем, что блок управления выполнен в виде трех элементов ИЛИ, триггера

10

и трехэлементов И, выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И

и с первым входом второго элемента ИЛИ, второй вход которого соединен с третьим входом первого элемента ИЛИ, с выходом третьего элемента ИЛИ и с первым входом триггера, выход которого соединен с первым входом третьего элемента И, второй вход триггера соединен с первым входом BTOpoiO элемента И, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ, причем

два входа первого элемента И, второй вход третьего э.аемента И, второй вход третьего элемента ИЛИ, третий и четвертый входы первого элемента ИЛИ, первый и второй входы второго элемента И и выходы первого и второго элемента , первого элемента И являются соответственно вхохтами и выходами всего блока.

5. Демодулятор по. п. 1, отличающийся тем, что блок формирования разрядов принимаемой информации выполнен в виде двух элементов И, элемента ИЛИ, двух триггеров, первый выход первого триггера подключен к первому входу первого элемента И, второй вход которого соединен

с первым входом второго элемента И, второй вход которого соединен с вторЬ1М выходом первого триггера, выход второго элемента И подключен к первому входу элемента ИЛИ, выход которого соединен

с первым входом второго триггера, второй вход которого соединен с выходом первого элемента И, причем входы первого триггера, вторые и третьи входы элемента ИЛИ, вход второго элемента И, первый и

второй выходы первого триггера являются соответственно входами и выходами всего блока.

Источники информации,

45

принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 545091, кл. И 04L 27/10, 1974 (нрото50 тип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой демодулятор частотно-манипулированных сигналов | 1982 |

|

SU1058083A1 |

| Цифровой демодулятор частотно-манипулированных сигналов | 1981 |

|

SU987842A2 |

| УСТРОЙСТВО ИЗБИРАТЕЛЬНОГО ВЫЗОВА | 2005 |

|

RU2299525C1 |

| ИЗМЕРИТЕЛЬ ФАЗ ОСЦИЛЛОГРАФИЧЕСКИЙ | 2005 |

|

RU2314543C2 |

| АКУСТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2099864C1 |

| Демодулятор сигналов с минимальной частотной манипуляцией | 1985 |

|

SU1261136A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1986 |

|

SU1356253A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1985 |

|

SU1275777A1 |

| Цифровой демодулятор частотно- модулированных сигналов | 1978 |

|

SU769757A2 |

| Цифровой демодулятор частотно- модулированных сигналов | 1978 |

|

SU769758A2 |

Авторы

Даты

1981-01-07—Публикация

1979-01-08—Подача