Изобретение относится к автоматике и вычислительной технике, в частности к устройствам поиска максимального числа, и может быть использовано в блоках нормализации порядка чисел с плавающей запятой в системах с большой степенью интеграции.

Цель изобретения - повышение быстродействия устройства и сокращение аппаратурных затрат.

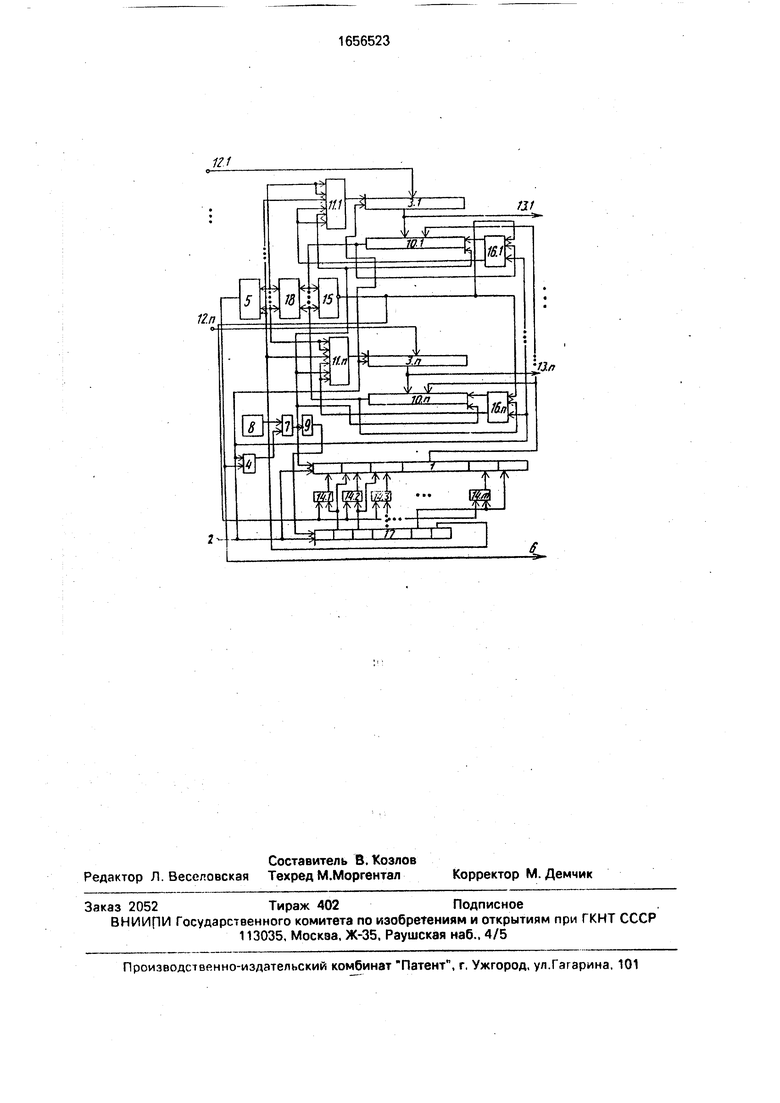

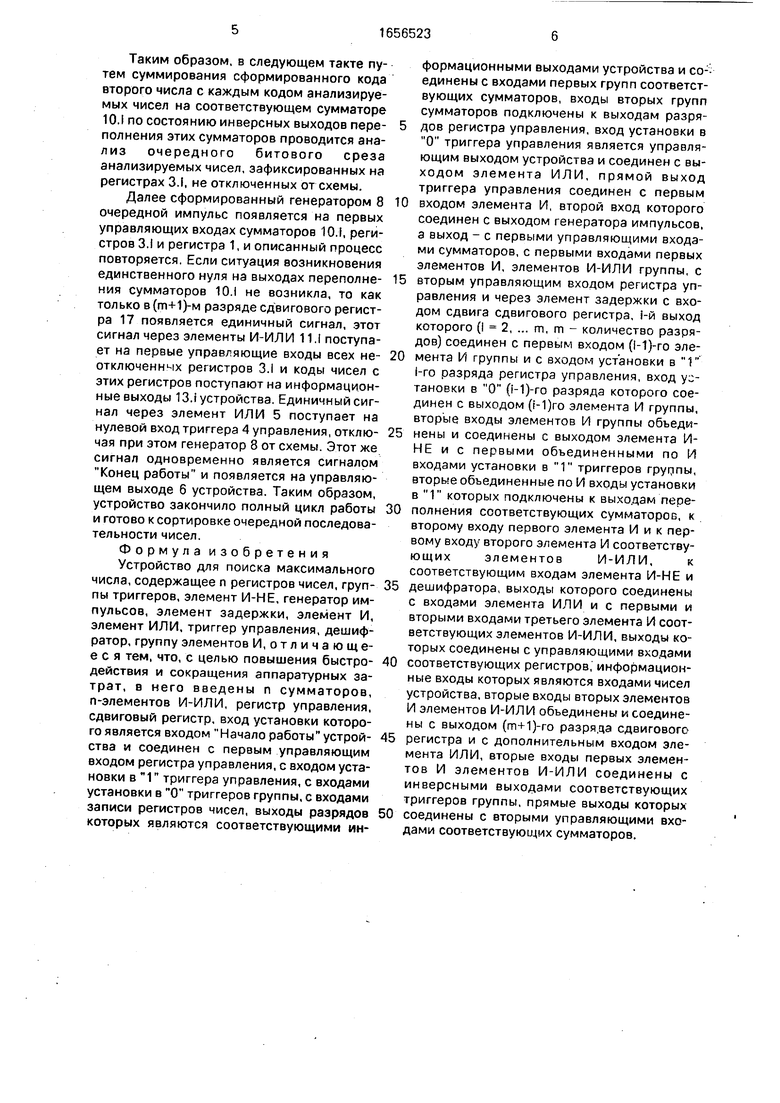

На чертеже приведена структурная схема устройства.

Устройство содержит регистр 1 управления, вход 2 Начало работы устройства, регистры 3 чисел, триггер 4 управления, элемент ИЛИ 5, управляющий выход 6 устройства, элемент И 7. генератор 8, элемент 9 задержки, сумматоры 10, элементы И-ИЛИ 11, входы 12 чисел устройства, информационные выходы 13 устройства, группу элементов И 14, элемент И-НЕ 15, группу триггеров 16, сдвиговый регистры 17 и дешифратор 18.

Устройство работает следующим образом.

По сигналу Начало работы, поступающему по входу 2, с информационных входов 12.1 устройства на регистры 3.1 чисел поступают двоичные числа, подлежащие анализу на максимум. По сигналу Начало работы : регистр 1 управления устанавливается в исходное состояние 100 ..00 ; сдвиговый регистр 17 устанавливается в исходное состояние ...dO ; триггеры 16.1 (I 1. п) устанавливаются в состояние 0 ; Триггер 4 управления устанавливается в состояние Г.

Единичный сигнал на выходе триггера 4 управления через элемент И 7 подключает генератор 8 ко всем входам разрешения

О

ел о ел ю со

суммирования (первым управляющим входам) сумматоров 10.1, I 1, п, а также к разрешающему выдачу кода входу (второму управляющему входу) регистра 1. Одновременно этот сигнал через соответствующие элементы 11.1 И-ИЛИ подключает генератор 8 к разрешающим выдачу кода входам регистров 3.1. Описанные сигналы на входах указанных элементов устройства определяют выполнение операций суммирования кодов анализируемых чисел и текущего кода второго числа на соответствующих сумматорах 10.1.

Формируемый определенным образом (описанным ниже) в течение цикла работы устройства код второго числа (на регистре 1) позволяет при суммировании его в каждом j-м такте работы устройства с кодом 1-го анализируемого числа определить в этом такте содержимое J-ro разряда 1-го числа по состоянию инверсного выхода переполнения 1-го сумматора 10.1. В зависимости от содержимого j-ro разряда соответствующего регистра 3.1 инверсный выход переполнения 1-го сумматора 10.1 в j-м такте устанавливается в 1 или О.

С инверсных выходов переполнения сумматоров сигналы поступают на входы дешифратора 18. Дешифратор 18 формирует на своих выходах сигналы, свидетельствующие о том, что в состоянии 6 в данном такте находится единственный выход переполнения 1-го сумматора 10.1, т.е. только у одного анализируемого числа данный разряд единичный.

В последнем случае это число будет максимальным, и сигнал с соответствующего выхода дешифратора 18 через соответствующий элемент И-ИЛИ подается на разрешающий выдачу кода вход регистра 3.I анализируемых чисел, и код числа с этого регистра поступает на информационные выходы 13.1 устройства. При этом сигнал с выхода дешифра,ора 13 через элемент ИЛИ 5 подается на нулевой вход триггера 4, устанавливая его в О, и тем самым отключает генератор 8 от схемы.

Одновременно этот сигнал является сигналом конца работы. Устройство заканчивает свою работу и готово к анализу следующей последовательности чисел.

В случае, если в О установлены все или несколько инверсных выходов переполнения сумматоров 10.1, происходит следующее.

Сигналы с инверсных выходов переполнения сумматоров 10.1 подаются на входы элемента И-НЕ 15, который формирует единичный сигнал, поступающий на первые объединенные по И входы установки в единичное состояние всех триггеров 16.1. Если при этом на вторые объединенные по И входы соответствующих триггеров 16.1 подается единичный сигнал с инверсных выходов

переполнения соответствующих сумматоров 10, то соответствующий триггер 16.1 устанавливается в 1 и сигнал с его единичного выхода поступает на второй управляющий вход соответствующего сумма0 тора 10.1. Тем самым блокируется работа соответствующего сумматора 10.1. и этот сумматор, а значит, и соответствующий регистр 3.1 отключаются от схемы, а именно от дешифратора, элемента И-НЕ 15 и генера5 тора 8, так как нулевой сигнал с нулевого выхода триггера 16.1 подается на входы соответствующих элементов И-ИЛИ 11.1. Таким образом, число на соответствующем регистре 3.1 исключается из анализа.

0В случае, если все инверсные выходы

переполнения сумматоров 10.1 в данном такте установятся в 1, т.е. соответствующий разряд всех анализируемых чисел нулевой, то отключения регистров 3.1 не

5 происходит, так как единичный сигнал на выходе элемента И-НЕ 15 сформирован не будет.

Код второго числа на регистре 1 формируется в начале работы устройства, как опи0 сано выше, и далее для каждого 1-го такта в каждом (1-1)-м такте следующим образом.

Одновременно с появлением на выходах элементов И-ИЛИ 11.1 сигналов, поступающих через эти элементы на первые

5 управляющие входы регистров 3.1 от генератора 8, с выхода элемента 9 задержки на второй управляющий вход сдвигового регистра 17 поступает задержанный на соответствующее время единичный сигнал.

0 Происходит сдвиг содержимого этого регистра 17 на один разряд вправо. Соответствующий разряд регистра второго числа 1 в результате этого устанавливается в 1. В зависимости от того, имело ли место пере5 полнение хотя бы одного сумматора 10.1 в данном такте работы устройства, что определяется состоянием выхода элемента И- НЕ 15.1, предыдущий разряд регистра 1 обнуляется (переполнение было) или остает0 ся единичным.

Обнуление происходит подачей на нулевой вход соответствующего разряда регистра 1 сигнала с выхода соответствующего 5 элемента 14.1, на первый вход которого (как и всех элементов 14.1) подается сигнал с выхода элемента И-НЕ 15, а на второй - сигнал с установившегося после сдвига в состояние 1 разряда сдвигового регистра 17.

Таким образом, в следующем такте путем суммирования сформированного кода второго числа с каждым кодом анализируемых чисел на соответствующем сумматоре 10.1 по состоянию инверсных выходов переполнения этих сумматоров проводится ана- лиз очередного битового среза анализируемых чисел, зафиксированных на регистрах 3.1, не отключенных от схемы.

Далее сформированный генератором 8 очередной импульс появляется на первых управляющих входах сумматоров 10.1, регистров 3.1 и регистра 1, и описанный процесс повторяется. Если ситуация возникновения единственного нуля на выходах переполнения сумматоров 10.1 не возникла, то как только в (т+1)-м разряде сдвигового регистра 17 появляется единичный сигнал, этот сигнал через элементы И-ИЛИ 11.1 поступает на первые управляющие входы всех не- отключенных регистров 3.1 и коды чисел с этих регистров поступают на информационные выходы 13.1 устройства. Единичный сигнал через элемент ИЛИ 5 поступает на нулевой вход триггера 4 управления, отключая при этом генератор 8 от схемы. Этот же сигнал одновременно является сигналом Конец работы и появляется на управляющем выходе 6 устройства. Таким образом, устройство закончило полный цикл работы и готово к сортировке очередной последовательности чисел.

Формула изобретения

Устройство для поиска максимального числа, содержащее п регистров чисел, группы триггеров, элемент И-НЕ, генератор им пульсов, элемент задержки, элемент И, элемент ИЛИ, триггер управления, дешифратор, группу элементов И.отличающе- е с я тем, что, с целью повышения быстродействия и сокращения аппаратурных затрат, в него введены п сумматоров, n-элементов И-ИЛИ, регистр управления, сдвиговый регистр, вход установки которого является входом Начало работы устройства и соединен с первым управляющим входом регистра управления, с входом установки в Г триггера управления, с входами установки в О триггеров группы, с входами записи регистров чисел, выходы разрядов которых являются соответствующими информационными выходами устройства и соединены с входами первых групп соответствующих сумматоров, входы вторых групп сумматоров подключены к выходам разря- 5 дов регистра управления, вход установки в О триггера управления является управляющим выходом устройства и соединен с выходом элемента ИЛИ, прямой выход триггера управления соединен с первым

0 входом элемента И, второй вход которого соединен с выходом генератора импульсов, а выход - с первыми управляющими входами сумматоров, с первыми входами первых элементов И, элементов И-ИЛИ группы, с

5 еторым управляющим входом регистра управления и через элемент задержки с входом сдвига сдвигового регистра, 1-й выход которого (I 2, ... т, т - количество разрядов) соединен с первым входом (И)-го эле0 мента И группы и с входом установки в 1 i-ro разряда регистра управления, вход у„- тановки в О (i-1)-ro разряда которого соединен с выходом (И)го элемента И группы, вторые входы элементов И группы объеди5 нены и соединены с выходом элемента И- НЕ и с первыми объединенными по И входами установки в 1 триггеров группы, вторые объединенные по И входы установки в 1 которых подключены к выходам пере0 полнения соответствующих сумматоров, к второму входу первого элемента И и к первому входу второго элемента И соответствующихэлементовИ-ИЛИ,к соответствующим входам элемента И-НЕ и

5 дешифратора, выходы которого соединены с входами элемента ИЛИ и с первыми и вторыми входами третьего элемента И соответствующих элементов И-ИЛИ, выходы которых соединены с управляющими входами

0 соответствующих регистров, информационные входы которых являются входами чисел устройства, вторые входы вторых элементов И элементов И-ИЛИ объединены и соединены с выходом (т+1)-го разряда сдвигового

5 регистра и с дополнительным входом элемента ИЛИ, вторые входы первых элементов И элементов И-ИЛИ соединены с инверсными выходами соответствующих триггеров группы, прямые выходы которых

0 соединены с вторыми управляющими входами соответствующих сумматоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска максимального числа | 1985 |

|

SU1314334A1 |

| Устройство для выделения среднего из нечетного количества чисел | 1988 |

|

SU1647554A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Генератор последовательности обобщенных чисел Фибоначчи с произвольными начальными условиями | 1986 |

|

SU1345181A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для обработки запросов | 1989 |

|

SU1688248A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| Устройство для умножения двоичных чисел в дополнительных кодах | 1983 |

|

SU1119008A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для поиска максимального числа, и может быть использовано в качестве составной части блока нормализации порядка чисел с плавающей запятой в ЭВМ, комплексах и системах на модулях с большой степенью интеграции. Целью изобретения является повышение быстродействия. Устройство содержит регистр 1 управления вход 2 Начало работы устройства, ры 3 чисел, триггер управления 4, элемент ИЛИ 5, управляющий выход 6 устройгтпа, элемент И 7, генератор 8, элемент задерхкн 9, сумматоры 10, элементы И-ИЛИ 11 входы 12 чисел устройства, информационные зы- ходы 13 устройства, группа элементов И Ч, элемент И-НЕ 15, группу триг героз 1Г, сдвиговый регистр 17, дешифратор 18. 1 ил.

| Устройство для определения максимального числа | 1980 |

|

SU911510A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения максимального числа из группы чисел | 1980 |

|

SU959065A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-15—Публикация

1989-02-07—Подача