(Б ) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для деления | 1988 |

|

SU1513444A1 |

| Устройство для деления чисел | 1981 |

|

SU970356A1 |

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

| Устройство для деления | 1976 |

|

SU662938A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

I

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычислительных машин последовательного действия. .

Известно устройство для деления последовательного типа, схема которого содержит сдвиговые регистры, схему округления, схему определения знака, сумматор, логические элементы, триггеры 1}

Известно также двоичное устройство для деления, содержащее сдвиговые регистры с параллельной записью информации, два одноразрядных сумма тора-вы числи теля последова тель ного действия, блок анализа знаков, блок анализа сходимости процесса, кие элементы (2j.

Принцип работы таких устройств не Позволяет в полной мере использовать в них динамические регистры с большой степенью интеграции, что

приводит к росту аппаратурных затрат и габаритов.

Наиболее близким к предлагаемому является устройство для деления чисел последовательного действия, содержащее регистры делителя, делимого и частного, последовательный сумматор, триггер, блок управления и логические элементы И, ИЛИ. В таком устройстве в каждом цикле определяется одна цифра частного, которая записывается в реверсивный статический сдвиговый регистр. Формирование знака результата и его выдача осуществляете/) автономными блоками 3J .

Недостатком известного устройства являются большие аппаратурные затраты и габариты, связанные с невозможностью использования в нем в полной мере динамических регистров с большой степенью интеграции.

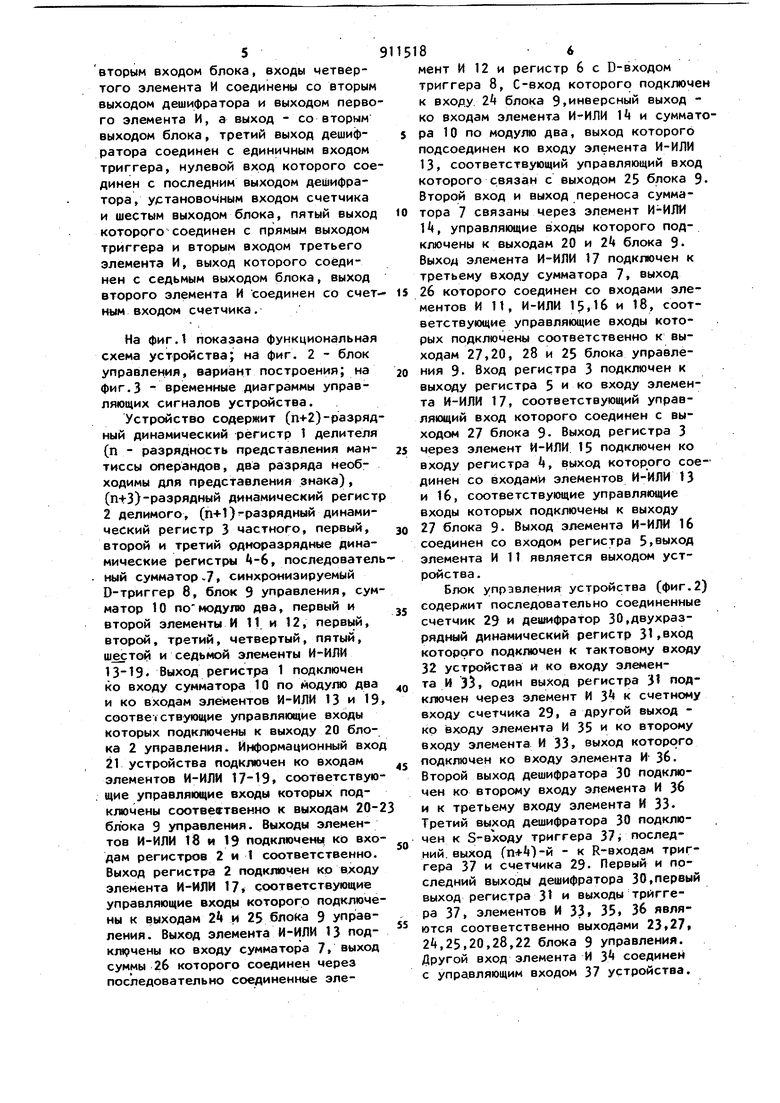

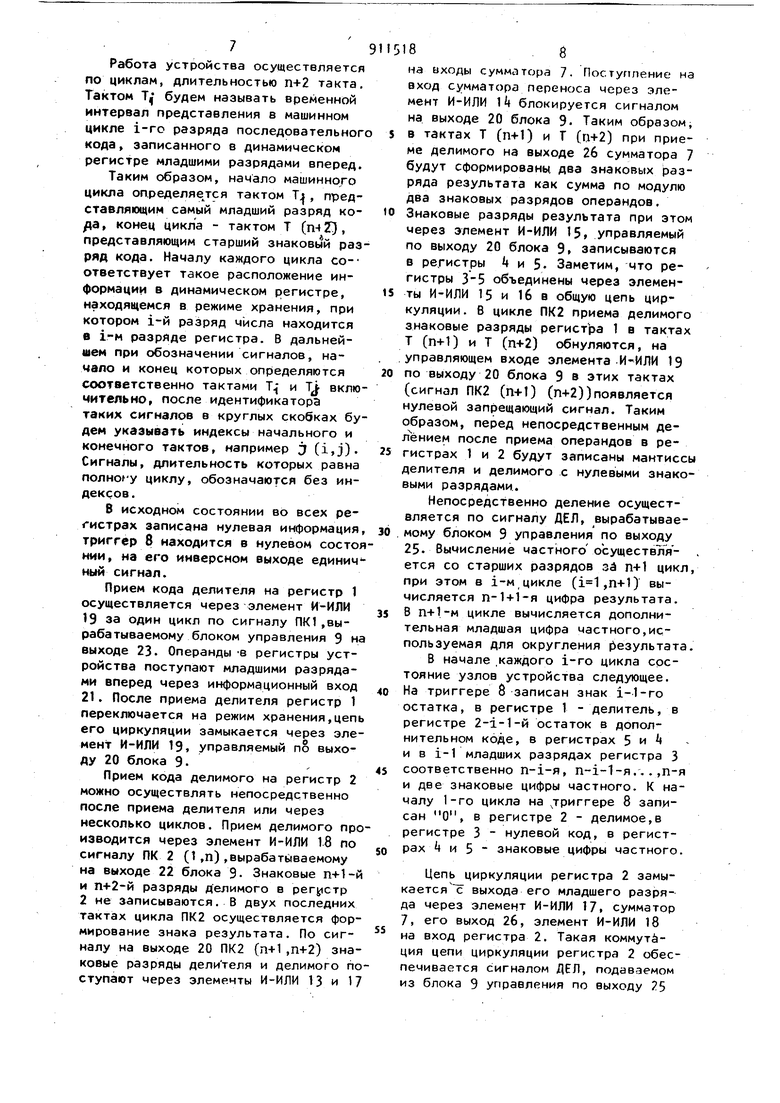

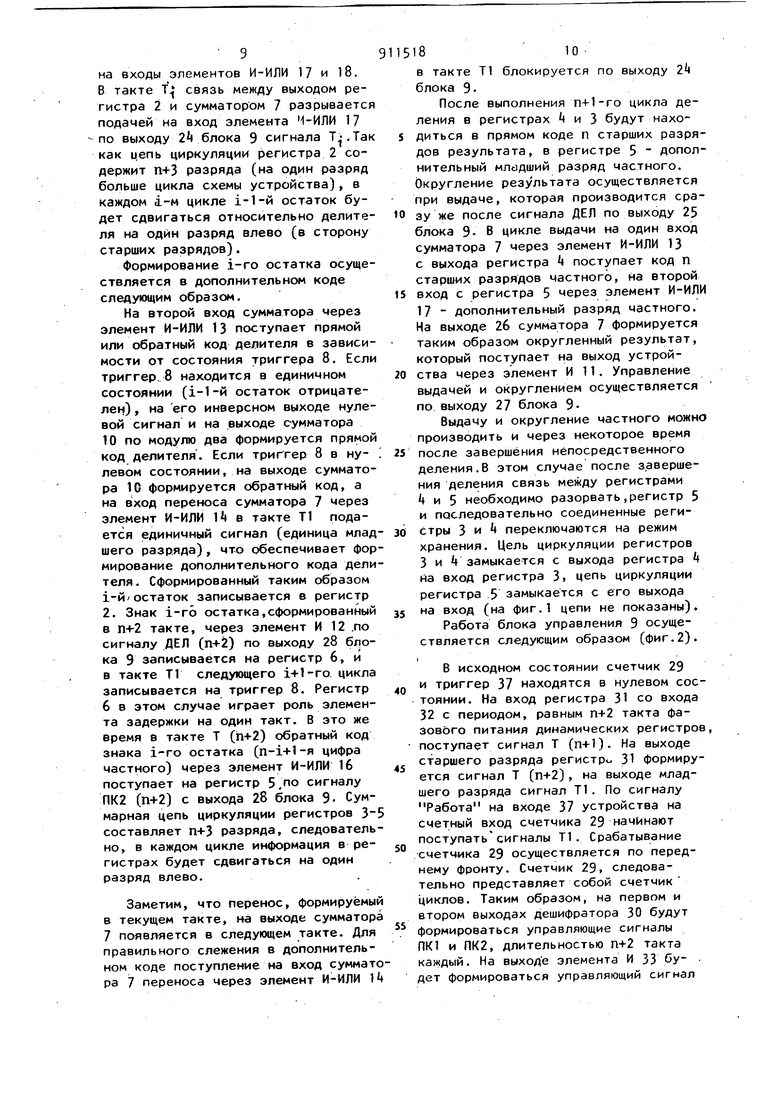

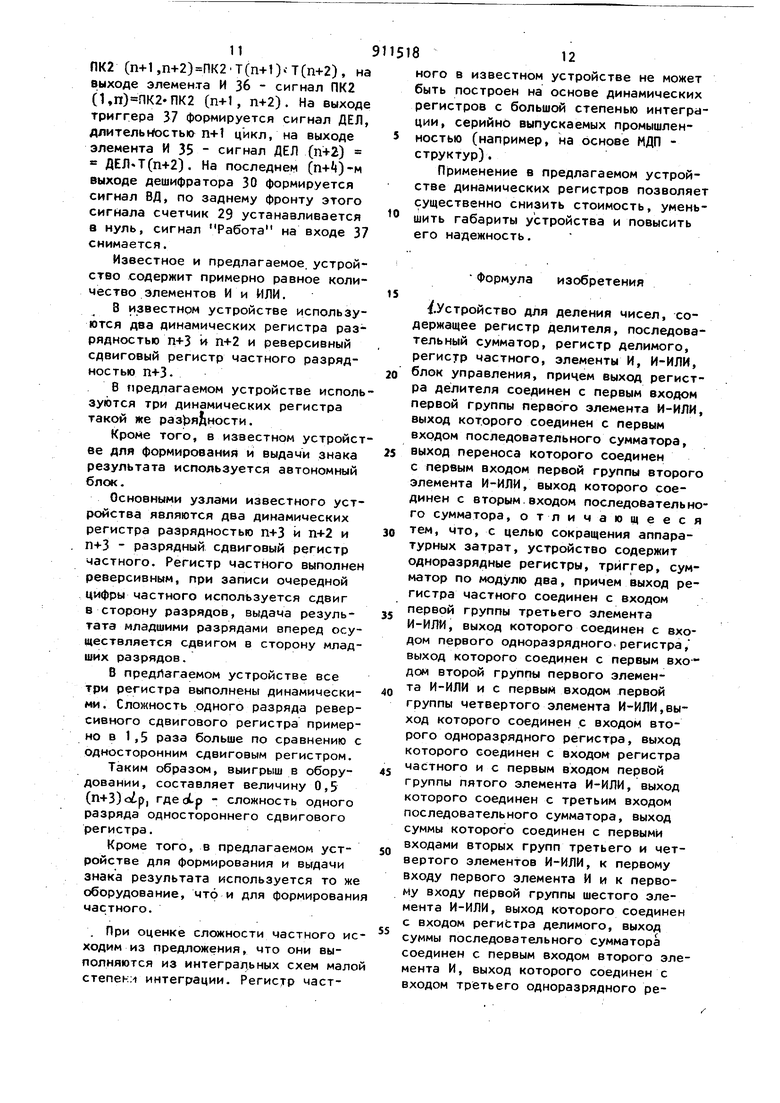

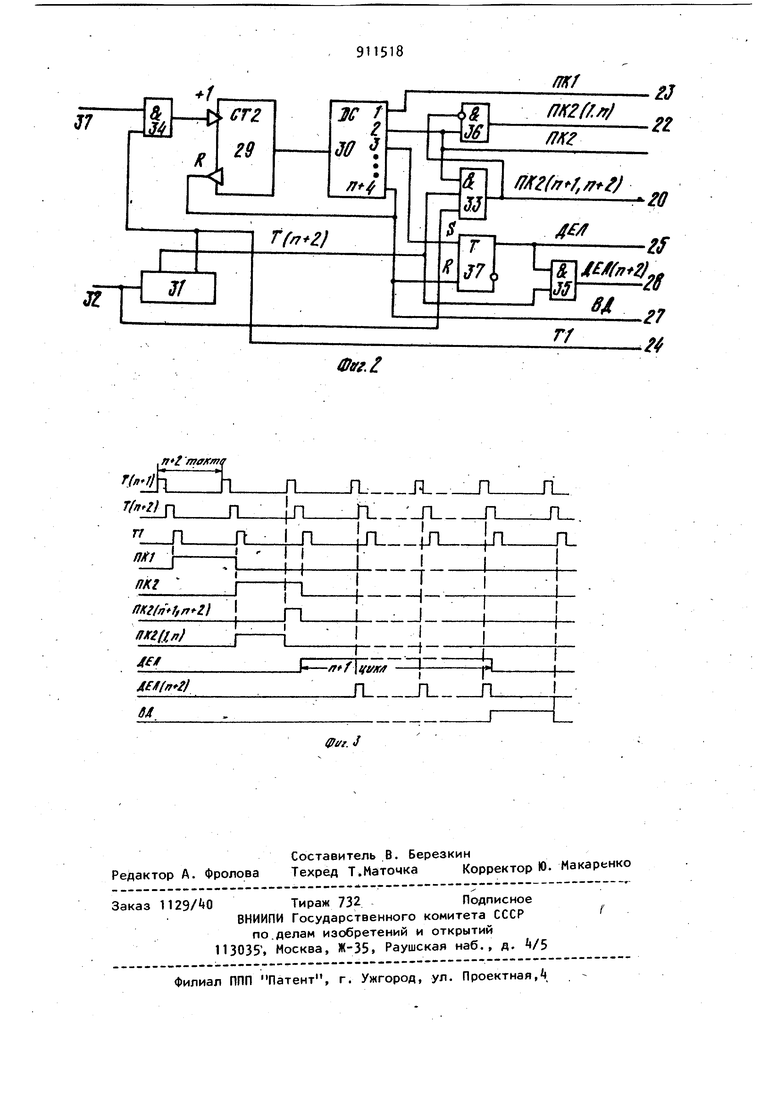

Цель изобретения - уменьшение аппаратурных затрат. Поставленная цель достигается тем что устройство для деления чисел, содержащее регистр делителя, последовательный сумматор, регистр делимого регистр частного, элементы И, И-ИЛИ, блок управления, причем выход регистра делителя соединен с первым входом первой группы первого элемента И-ИЛИ выход которого соединен с первым входом последовательного сумматора, выход переноса которого соединен с первым входом первой группы второго элемента И-ИЛИ, выход которого соединен Со вторым входом последовательного сумматора, содержит одноразрядные регистры, триггер, сумматор по модулю два, причем выход регистра частного соединен со входом первой группы третьего элемента , выход которого соединен со входом первого одноразрядного регистра, выход которого соединен с первым входом второй группы первого элемента И-ИЛИ и с первым входом первой группы четвертого элемента И-ИЛИ, выход которого соединен со входом второго одноразряд ного регистра, выход которого соединен со входом регистра частного и с первым входом первой группы пятого элемента И-ИЛИ, выход которого соедииен с третьим входом последовательного сумматора, выход суммы которого соединен с первыми входами вторых групп третьего и четвертого элементов И-И1Я1, к первому входу первого элемента Ник первому входу первой группы шестого элемента И-МЛИ, выход которого соединен со входом регистра делимого, выход суммы последовательного сумматора соединен с первым входом второго элемента И, выход которото соединенсо входом третьего одноразрядного регистра, выход которого соединен с информационным входом три гера, инверсный выход которого соединен с первым входом второй группы второго элемента И-ИЛИ и с первым входом сумматора по модулю два,выход которого соединен с первым вводом третьей группы первого элемента И-ИЛИ второй вход сумматора по модулю два соединен с выходом регистра делителя и первым входом первой группы седьмого элемента Й-ИЛИ, выходкоторого соединен со входом регистра делителя , первые входы вторых групп пятого, шестого и седьмого элементов И-ИЛИ соединены с информационным входом устройства, выход регистра делимого соединен с первым входом третьей группы пятого элемента И-ИЛИ, первый выход блока управления соединен со вторыми входами первых групп первого, второго и седьмого элементов И-ИЛИ, со вторыми входами вторых групп третьего и пятого элементов И-ИЛИ, второй выход блока управления соединен со вторым входом, второй группы шестого элемента И-ИЛИ, третий выход блока управления соединен со вторым входом второй группы седьмого элемента И-ИЛИ, четвертый выход блока управления соединен со вторым входом второй группы второго элемента И-ИЛИ, с третьим входом первой группы второго элемента И-ИЛИ, со вторым входом третьей группы пятого элемента И-ИЛИ и с тактовым входом триггера, пятый выход блока управления соединен со вторым входом третьей группы первого элемента И-ИЛИ, с третьим входом третьей группы пятого элемента И-ИЛИ и вторым входом первой группы шестого элемента И-ИЛИ, шестой выход блока управления соединен со вторым входом второй группы первого элемента И-ИЛИ, со вторыми входами первых групп 4eTBeptoro и пятого элементов И-ИЛИ и со вторым входом первого элемента И, седьмой выход блока управления соединен со вторым входом второй группы четвертого элемента И-ИЛИ и со вторым входом второго элемента И, первый и второй входы блока управления соединень с управляющим и тактовым входами устройства соответственно, выход первого элемента И соединен с выходом устройства, а также тем, что блок управления содержит счетчик, дешифратор, двухразрядный регистр, триггер и элементы И, причем выходы разрядов счетчика соединены со. входами дешифратора, первый выход которого соединен с третьим выходбм блока, второй выход - с первым входом первого элемента И, выход которого соединен с первым выходом блока, первый вход которого соединен с первым входом второго элемента И, а второй вход - со входом двухразрядного регистра, первый выход которого соединен со вторым входом первого элемента И и первым входом третьего элемента И, а второй выход - со вторым входом втррого элемента И и четвертым ёыходом блока, третий вход первого элемента И соединен со вторым входом блока, входы четвертого элемента И соединены со вторым выходом дешифратора и выходом перво го элемента И, а выход - со вторым выходом блока, третий выход дешифратора соединен с единичным входом триггера, нулевой вход которого сое динен с последним выходом дешифратора, установочным входом счетчика и шестым выходом блока, пятый выход которого соединен с прямым выходом триггера и вторым входом третьего элемента И, выход которого соединен с седьмым выходом блока, выход второго элемента И соединен со счет ным входом счетчика. На ф14Г,1 показана функциональная схема устройства; на фиг. 2 - блок управления, вариант построения; на фиг.З - временные диаграммы управляющих сигналов устройства. Устройство содержит (ii-f2)-разряд ный динамический регистр 1 делителя (п - разрядность представления мантиссы операндов, два разряда необходимы для представления знака), (п+3)-разрядный динамический регист 2 делимого, ()-разрядный динамический регистр 3 частного, первый, второй и третий одноразрядные динамические регистры «-б, последовател ный сумматор .7, синхронизируемый D-триггер 8, блок 9 управления, сум матор 10 подмодулю два, первый и второй элементы И 11. и 12, первый, второй, третий, четвертый, пятый, шестой и седьгюй элементы И-ИЛИ 13-19. Выход регистра 1 подключен ко входу сумматора 10 по модулю два и ко входам элементов И-ИЛИ V3 и 19 соответствующие управляющие входы которых подключены к выходу 20 блока 2 управления. Информационный вхо 21 устройства подключен ко входам элементов И-ИЛИ 17-19 соответствую щие управляющие входы которых подключены соотвехтвенно к выходам 20блока 9 управления. Выходы элементов И-ИЛИ 18 и 19 подключена ко вхо дам регистров 2 и 1 соответственно. Выход регистра 2 подключен ко входу элемента И-ИЛИ 17 соответствующие управляющие входы которого подключены к выходам 24 и 25 6лoka 9 управления. Выход элемента И-ИЛИ 13 подкл19чены ко входу сумматора 7 выход суммы 2б которого соединен через последовательно соединенные эле186мент И 12 и регистр 6 с D-входом триггера 8, С-вход которого подключен к входу 2А блока 9 инверсный выход ко входам элемента И-ИЛИ I и сумматора 10 по модулю два, выход которого подсоединен ко входу элемента И-ИЛИ 13, соответствующий управляющий вход которого связан с выходом 25 блока 9Второй вход и выход переноса сумматора 7 связаны через элемент И-ИЛИ И, управляющие входы которого подключены к выходам 20 и 2 блока 9 Выхо/4 элемента И-ИЛИ 17 подключен к третьему входу сумматора 7 выход 26которого соединен со входами элементов И 11, И-ИЛИ 15,16 и 18, соответствующие управляющие входы которых подключены соответственно к выходам 27,20, 28 и 25 блока управления 9. Вход регистра 3 подключен к выхсэду регистра 5 и ко входу элемента И-ИЛИ 17, соответствующий управляющий вход которого соединен с выходом 27 блока 9- Выход регистра 3 через элемент И-ИЛИ 15 подкхдачен ко входу регистра Ц, выход которого соединен со входами элементов И-ИЛИ 13 и 16, соответствующие управляющие входы которых подключены к выходу 27блока 9- Выход элемента И-ИЛИ 16 соединен со входом регистра 5,выход элемента И 11 является выходом устройства. Блок управления устройства (фиг.2) содержит последовательно соединенные счетчик 29 и дешифратор 30,двухразрядный динамический регистр которого подключен к тактовому входу 32 устройства и ко входу элемента И ЗЗ, один выход регистра 31 подключен через элемент И 3 к счетному входу счетчика 29 а другой выход ко входу элемента И 35 и ко второму ВХОДУ элемента И 33 выход которого подключен ко входу элемента И 36. Второй выход дешифратора 30 подключен ко второму входу элемента И 36 и к третьему входу элемента И 33. Третий выход дешифратора 30 подключен к S-входу триггера 37, последний, выход (( - к R-входам триггера 37 и счетчика 29. Первый и последний выходы дешифратора 30,первый выход регистра 31 и выходы трйггере 37, элементов И 33 35 36 являтся соответственно выходами 24,25,20,28,22 блока 9 управления. ругой вход элемента И З соединен с управляющим входом 37 устройства.

79

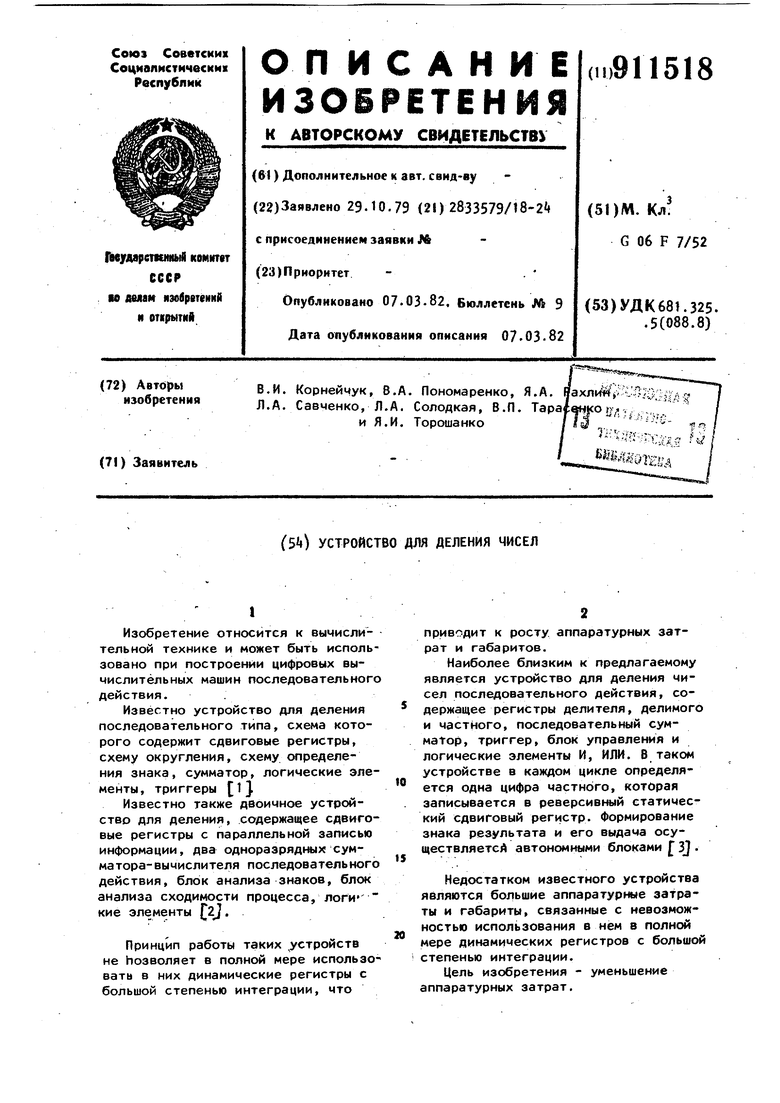

Работа устройства осуществляется по циклам, длительностью п+2 такта, Тактом будем называть временной интервал представления в машинном цикле i-rc разряда последовательного кода, записанного в динамическом регистре младшими разрядами вперед. Таким образом, начало машинно/о цикла определяемся тактом Т, представляющим самый младший разряд кора, конец цикла - тактом Т (), представляющим старший знаковый разряд кода. Началу каждого цикла соответствует такое расположение информации в динамическом регистре, находящемся в режиме хранения, при котором i-й разряд числа находится в i-M разряде регистра. В дальнейшем при обозначении сигналов, начало и конец которых определяются соответственно тактами Т и TJ включительно, после идентификатора таких сигналов в круглых скобках будем указывать индексы начального и конечного тактов, например j (i,j). Сигналы, длительность которых равна полному циклу, обозначаются без индексов .

В исходном состоянии во всех ре«истрах записана нулевая информация, триггер 8 находится в нулевом состоянии, на его инверсном выходе единичный сигнал.

Прием кода делителя на регистр 1 осуществляется через элемент И-ИЛИ 19 за один цикл по сигналу ПК1,вырабатываемому блоком управления 9 на выходе 23. Операнды В регистры устройства поступают младшими разрядами вперед через информационный вход 21. После приема делителя регистр 1 переключается на режим хранения,цепь его циркуляции замыкается через элемент И-ИЛИ 19, управляемый по выходу 20 блока 9.

Прием кода делимого на регистр 2 можно осуществлять непосредственно после приема делителя или через несколько циклов. Прием делимого производится через элемент И-ИЛИ 18 по сигналу ПК 2 (1,п),вырабатываемому на выходе 22 блока 9- Знаковые n+1-й и п+2-й разряды делимого в регистр 2 не записываются. В двух последних тактах цикла ПК2 осуществляется формирование знака результата. По сигналу на выходе 20 ПК2 (п+1,п+2) знаковые разряды делителя и делимого поступают через элементы И-ИЛИ 13 и 17

8- 8

на аходы суммдтора 7. Поступление на вход сумматора переноса через элемент И-ИЛИ 1 блокируется сигналом на выходе 20 блока 9. Таким образомi в тактах Т (п+1) и Т (г,и-2) при приеме делимого на выходе 26 сумматора 7 будут сформированы, два знаковых разряда результата как сумма по модулю два знаковых разрядов операндов. Знаковые разряды результата при этом через элемент И-ИЛИ 15, управляемый по выходу 20 блока 9, записываются в регистры и 5 Заметим, что регистры 3-5 объединены через элементы И-ИЛИ 15 и 16 в общую цепь циркуляции . В цикле ПК2 приема делимого знаковые разряды регистра 1 в тактах Т (п+1) и Т (п+2) обнуляются, на управляющем входе элемента И-ИЛИ 19 по выходу 20 блока 9 в этих тактах (сигнал ПК2 (п+1) (п+2))появляется нулевой запрещающий сигнал. Таким образом, перед непосредственным дел ёнием после приема операндов в регистрах 1 и 2 будут записаны мантиссы делителя и делимого с нулевыми знаковыми разрядами.

Непосредственно деление осуществляется по сигналу ДЕЛ, вырабатываемому блоком 9 управления по выходу 25. Вычисление частного осуществля- , ется со старших разрядов зй п+1 цикл, при этом в i-M цикле (,П+1) вычисляется П-1+1-Я цифра результата. В n+1-M цикле вычисляется дополнительная младшая цифра частного,используемая для округления результата.

В начале каждого i-ro цикла состояние узлов устройства следующее. На триггере 8 записан знак i-1-го остатка, в регистре 1 - делитель, в регистре 2-1-1-й остаток в дополнительном коде, в регистрах 5 и и в 1-1 младших разрядах регистра 3 соответственно п-1-я, n-i-1-я...,п-я и две знаковые цифры частного. К началу 1-го цикла на jpHrrepe 8 записан О, в регистре 2 - делимое,в регистре 3 - нулевой код, в регистрах 4 и 5 знаковые цифры частного.

Цепь циркуляции регистра 2 замыкается Т выхода его младшего разряда через элемент И-ИЛИ 17. сумматор 7, его выход 26, элемент И-ИЛИ 18 на вход регистра 2. Такая коммутйция цепи циркуляции регистра 2 обеспечивается сигналом ДЕЛ, подаваемом из блока 9 управления по выходу 25 на входы элементов И-ИЛИ 17 и 18. В такте Т связь между выходом регистра 2 и сумматором 7 разрываетс подачей на вход элемента М-ИЛИ 17 -по выходу 2 блока 9 сигнала .Так как цепь циркуляции регистра 2 содержит п+3 разряда (на один разряд больше цикла схемы устройства), в каждом i-M цикле i-1-й остаток будет сдвигаться относительно делите ля на один разряд влево (в сторону старших разрядов). Формирование i-ro остатка осуществляется в дополнительном коде следующим образом. На второй вход сумматора через элемент И-ИЛИ 13 поступает прямой или обратный код делителя в зависимости от состояния триггера 8, Если триггер.8 находится в единичном состоянии (i-1-й остаток отрицателен) , на его инверсном выходе нулевой сигнал и на выходе сумматора 10 по модулю два формируется прямой код делителя. Если триггер 8 в нулевом состоянии, на выходе сумматора 1C формируется обратный код, а на вход переноса сумматора 7 через элемент И-ИЛИ I в такте Т1 подается единичный сигнал (единица млад шего разряда), что обеспечивает фор мирование дополнительного кода дели теля. Сформированный таким образом i-йостаток записывается в регистр 2. Знак i-ro остатка,сформированный в п-12 такте, через элемент И 12 .по сигналу ДЕЛ (п+2) по выходу 28 блока 9 записывается на регистр 6, и в такте Т1 следующего i+1-го цикла записывается на триггер 8. Регистр 6в этом случае играет роль элемента задержки на один такт. В это же время в такте Т (h+2) обратный код знака i-ro остатка (n-i+1-я цифра частного) через элемент И-ИЛИ 16 поступает на регистр 5,по сигналу ПК2 (п+2) с выхода 28 блока 9- Суммарная цепь циркуляции регистров 3составляет п+3 разряда, следователь но, в каждом цикле информация в регистрах будет сдвигаться на один разряд влево. Занетим, что перенос, формируемый в текущем такте, на выходе сумматора 7появляется в следующем такте. Для правильного слежения в дополнительном коде поступление на вход суммато ра 7 переноса через элемент И-ИЛИ 1k 1810 в такте Т1 блокируется по выходу 2 блока 9. После выполнения п+1-го цикла деления в регистрах и 3 будут находиться в прямом коде п старших разрядов результата, в регистре 5 - дополнительный млйдший разряд частного. Округление результата осуществляется при выдаче, которая производится сраЗУ же после сигнала ДЕЛ по выходу 25 блока 9- В цикле выдачи на один вход сумматора 7 через элемент И-ИЛИ 13 с выхода регистра поступает код п старших разрядов частного. На второй вход с регистра 5 через элемент И-ИЛИ 17 - дополнительный разряд частного. На выходе 2б сумматора 7 формируется таким образом округленный результат, который поступает на выход устройства через элемент И 11. Управление выдачей и округлением осуществляется по выходу 27 блока 9 Выдачу и округление частного можно производить и через некоторое время после завершения непосредственного деления.В этом случае после завершения деления связь между регистрами t и 5 необходимо разорвать .регистр 5 и последовательно соединенные регистры 3 и переключаются на режим хранения. Цель циркуляции регистров 3 и t замыкается с выхода регистра Ц на вход регистра 3, цепь циркуляции регистра 5 замыкается с его выхода на вход (на фиг.1 цепи не показаны). Работа блока управления 9 осуществляется следующим образом (фиг.2). В исходном состоянии счетчик 29 и триггер 37 находятся в нулевом состоянии. На вход регистра 31 со входа 32 с периодом, равным п+2 такта фазового питания динамических регистров, поступает сигнал Т (п+1). На выходе старшего разряда регистре, 3 формируется сигнал Т (п+2), на выходе младшего разряда сигнал Т1. По сигналу Работа на входе 37 устройства на четный вход счетчика 29 начинают оступатьсигналы Т1. Срабатывание четчика 29 осуществляется по передему фронту. Счетчик 29, следоваельно представляет собой счетчик иклов. Таким образом, на первом и тором выходах дешифратора 30 будут ормироваться управляющие сигналы К1 и ПК2, длительностью п+2 такта аждый. На выходе элемента И 33 бует формироваться управляющий сигнал

11

ПК2 (п+1,п+2)ПК2Т(п+1)Т(п+2), на выходе элемента И 36 - сигнал ПК2 (1,П)ПК2.ПК2 (п+1, п+2). На выходе триггера 37 формируется сигнал ДЕЛ, длитель Л)стыа п+1 цикл, на выходе элемента И 35 - сигнал ДЕЛ (п+2) ДЕЛ«Т(п+2). На последнем (п+4)-м выходе дешифратора 30 формируется сигнал ВД, по заднему фронту этого сигнала счетчик 29 устанавливается в нуль, сигнал Работа на входе 37 снимается.

Известное и предлагаемое, устройство содержит примерно равное количество элементов И и ИЛИ.

В известном устройстве используются два динамических регистра разрядностью n-fj и п+2 и реверсивный сдвиговый регистр частного разрядностью п+ЗВ предлагаемом устройстве используются три динамических регистра такой же раз;ря ности.

Кроме того, в известном устройстве для формирования и выдачи знака результата используется автономный блок.

Основными узлами известного устройства являются два динамических регистра разрядностью п+З и п+2 и п+З - разрядный сдвиговый регистр частного. Регистр мастного выполнен реверсивным, при записи очередной цифры частного используется сдвиг в сторону разрядов, выдача результата младшими разрядами вперед осуществляется сдвигом в сторону младших разрядов.

В пред11агаемом устройстве все три регистра выполнены динамическими. Сложность одного разряда реверсивного сдвигового регистра примерно в 1,5 раза больше по сравнению с односторонним сдвиговым регистром.

Таким образом, выигрыш в оборудовании, составляет величину 0,5 (п+З) Clip, где oLp - сложность одного разряда одностороннего сдвигового регистра.

Кроме того, в предлагаемом устройстве для формирования и знака результата используется то же оборудование, что и для формировани частного.

При оценке сложности частного исходим из предложения, что они выполняются из интеграл,ьных схем мало степен:1 интеграции. Регистр част1518

12

ного в известном устройстве не может быть построен на основе динамических регистров с большой степенью интеграции, серийно выпускаемых промышленностью (например, на основе МДП структур).

Применение в предлагаемом устройстве динамических регистров позволяет существенно снизить стоимость, уменьшить габариты устройства и повысить его надежность.

Формула изобретения

.Устройство для деления чисел, содержащее регистр делителя, последовательный сумматор, регистр делимого, регистр частного, элементы И, И-ИЛИ,

блок управления, причем выход регистра делителя соединен с первым входом первой группы первого элемента И-ИЛИ, выход которого соединен с первым входом последовательного сумматора,

5 выход переноса которого соединен

с первым входом первой группы второго элемента И-ИЛИ, выход которого соединен с вторым.входом последовательного сумматора, отличающееся

0 тем, что, с целью сокращения аппаратурных затрат, устройство содержит одноразрядные регистры, триггер, сумматор по модулю два, причем выход регистра частного соединен с входом

первой группы третьего элемента

И-ИЛИ, выход которого соединен с входом первого одноразрядного, регистра, выход которого соединен с первым вхо- дом второй группы первого элеменQ та И-ИЛИ и с первым входом первой группы четвертого элемента И-ИЛИ,выход которого соединен с входом второго одноразрядного регистра, выход которого соединен с входом регистра

. частного и с первым входом первой группы пятого элемента И-ИЛИ, выход которого соединен с третьим входом последовательного сумматора, выход суммы которого соединен с первыми входами вторых групп третьего и четвертого элементов И-ИЛИ, к первому входу первого элемента И и к первому входу Первой группы шестого элемента И-ИЛИ, выход которого соединен с входом регистра делимого, выход суммы последовательного сумматора соединен с первым входом второго элемента И, выход которого соединен с входом третьего одноразрядного регистра, выход которого соединен с информационным входом триггера, инверсный выход которого соединен с первым входом второй группы второго элемента И-ИЛИ и с первым входом сумматора по модулю два, выход которого соединен с первым входомтретьей группы первого элемента И-ИЛИ, второй вход сумматора по модулю два соединен с выходом регистра делителя и первым входом первой группы седьмого элемента И-ИЛИ, выход которого соединен с входом регистра делителя, первые входы вторых групп пятого,шестого и седьмого элементов И-ИЛИ соединены с информационным входом устройства, выход регистра делимого соединен с первым входом третьей группы пятого элемента И-ИЛИ, первый выход блока управления соединен с вторыми входами первых групп первого, второго и седьмого элементов И-ИЛИ, с вторыми входами вторых групп третьего и пятого элементов И-ИЛИ, второй выход |6лока управления соединен с вторым входом второй группы шестого элемента И-ИЛИ, третий Выход блока управления соединен с вторым входом второй группы седьмого элемента И-ИЛИ,четвертый выход блока управления соединен с вторым входом второй группы второго элемента И-ИПИ, с третьим входом первой группы второго элемента И-ИЛИ, с вторым входом третьей группы пятого элемента И-ИЛИ и с TaKтовым входом триггера, пятый выход блока управления соединен с вторым |Входом третьей группы первого элемента И-ИЛИ, с третьим входом третьей группы пятого элемента Й-ИЛИ и вторым входом первой группы шестого элемента И-ИЛИ, шестой выход блока управления соединен с вторым входом второй группы первого элемента И-ИЛИ, с вторыми входами первых групп четвер того и пятого элементов И-ИЛИ и с вторым входом первого элемента И, седьмой выход блока управления соединен с вторым входом второй группы четвертого элемента И-ИЛИ и ,с вто-: рым входом второго элемента И, первый

и второй входы блока управления соединены с управляющим и тактовым входами устройстве, соответственно, выхо первого элемента ,И соединен с выходо устройства,

Источники информации, принятые во внимание при экспертизе

ФУГ/

ffKf

.//

nf(2f/./r/

-гг /7/r/

, го

-/cf

C j4

/a

&

/

./7

Г/ /

Авторы

Даты

1982-03-07—Публикация

1979-10-29—Подача