Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ. Известно устройство для умножения двоичных чисел в дополнительных кодах,, содержащее регистры множителя, множимого и результата, дешифратор, сумматор, элементы И С JНедостаток данного устройства невысокая точность вычисления. Наиболее близким по технической сущности к изобретению является устройство для умножения двоичных чисел в дополнительных кодах, содержащее регистр множимого, сдвиговый регистр множителя, трехвходрвой сумматор, регистр поразрядных сумм, регистр порязрядных переносов, дешифратор цифр множителя, триггер запоминания результата дешифрации, три группы элементов И, группу элементов ИЛИ, триггер запоминания единицы дополнительного кода, триггер запоминания переноса и дополнительный сумматор, причем выходы двух младших разрядов сдвигового регистра множителя соединены с nepBbfM и вторым входами дешиф ратора цифр множителя, первый и второй выходы которого соединены с первыми входами элементов И первой и второй групп соответственно, третий выход дешифратора цифр множителя через триггер запоминания результатов дешифрации соединен с третьим входом дешифратора цифр множителя, вторые входы элементов И цервой группы соединены с прямыми выходами соответствующих разрядов регистра множимого, первые входы элементов И третьей группы соединены с инверсными выходами соответствующих разрядов регист ра множимого, вторые входы элементов И второй группы соединены со сдвигом влево на один разряд с прямыми выходами разрядов регистра множимого, выходы элементов И первой, второй и .третьей групп соединены с входами соответствующих элементов ИЛИ группы выходы которых соединены с входами соответствуюш 1х разрядов первого вхо да сумматора, первый и второй выходы .сумматора соединены с входами регист ,ра поразрядных сумм и регистра пораз рядных переносовсоответственно, выходы которых соединены соответственно с вторым и третьим входами суммаТора, установочньй вход триггера запоминания единицы дополнительного кода и вторые входы элементов И второй группы соединены с четвертым выходом дешифратора цифр множителя, выход триггера запоминания единицы дополнительного кода соединен с младшим разрядом первого входа дополнительного сумматора, выход младшего разряда регистра поразрядных переносов соединен со старшим разрядом первого входа дополнительного сумматора, выход младшего разряда поразрядных переносов соединен со старшим разрядом первого входа дополнительного сумматора, разряды второго входа дополнительного сумматора соединены с выходами дополнительных разрядов регистра поразрядных сумм, входы которых соединены с выходами разрядов дополнительного сумматора, выход переноса дополнительного сумматора через триггер запоминания переноса соединен с третьим входом дополнительного сумматора РЗНедостатком данного устройства является большой объем оборудования. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в устройстве для умножения двоичных чисел в дополнительных кодах, содержащем регистр множимого, сдвиговый регистр множителя, трехвходовой сумматор, регистр поразрядных сумм, дешифратор цифр множителя, первьй и второй триггеры, первую, вторую и третью группы элементов И, группу элементов ИЛИ, причем выходы первого и второго разрядов сдвигового регистра множителя соединены с первым и вторым входами дешифратора цифр множителя, первьй, второй и третий выходы которого соединены с первыми входами элементов И первой, второй и третьей групп соответственно, четвертый выход дешифратора цифр множителя через первый триггер соединен с третьим входом дешифратора цифр множителя, вторые входы элементов И первой группы соединены соответственно с прямыми выходами регистра множимого, вторые входы элементов И второй группы соединены соответственно с прямыми выходами регистра множимого со сдвигом на один разряд влево, вторые входы элементов И третьей группы соединены соответственно с инверсными выходами регистра множимого, выходы элер ентов И первой,

jBTopOH и третьей групп соединены с входами соответствующих элементов ИЛИ группы, выходы которых соединены с соответствующими входными разрядами первого входа сумматора, первый вькод которого- соединен с разрядными входами регистра поразрядных сумм, выход регистра поразрядных сумм соединен с соответствующими разрядами второго входа сумматора со сдвигом вправо на два разряда, пятый выход дешифратора цифр множителя через второй триггер соединен с четвертым входом дешифратора цифр множителя, выход нулевого разряда сдвигового регистра множителя соединен с пятьй1 Входом дешифратора цифр множителя, третий выход которого соединен с третьим входом сумматора, выходы двух первых младших разрядов сумматора соединены соответственно с входами первого и второго знаковых разрядов сдвигового регистра множителя, выход второго триггера соединен, с входом установки в ноль первого триггера.

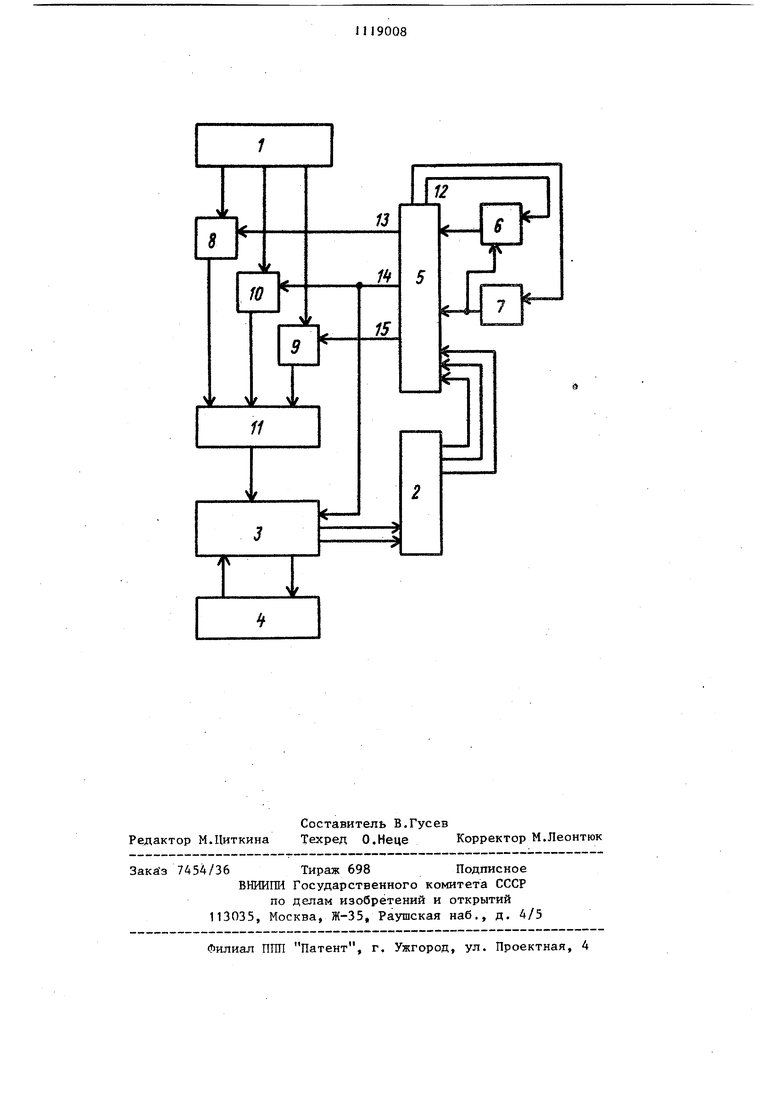

Функциональная схема устройства Для.умножения двоичных чисел в дополнительных кодах представлена на чертеже.

Устройство содержит регистр 1 множимого, сдвиговый регистр 2 множителя, трехвходовой. сумматор 3, регистр 4 поразрядных сумм, дешифратор 5 цифр множителя, триггеры 6 и 7, первую, вторую и третью группы элементов И 8-10 и группу элементов . ИЛИ It, причем выходы первого и втор го разрядов сдвигового регистра 2 множителя соединены с первым и вторым входами дешифратора 5 цифр множителя, nepBbrfi, второй и третий выходы которого соединены с первыми входами элементов И 8-10 групп соответственно, четвертый выход 12, дешифратора 5 цифр множителя через триггер 6 соединен с третьим входом дешифратора 5 цифр множителя, вторые входы элементов И 8 групп соединены соответственно с прямыми выходами регистра 1 множимого, вторые входы элементов И 9 группы соединены соот:ветственно с прямыми вькодами регистра 1 множимого со СДВИГОМ на один разряд влево, вторые входы элементов И 10 группы соединены соответственно с инверсными выходами регистра 1 множимого, выходы элементов И 8-10 груп соединены с соответствующими входами

элементов ИЛИ 11 группы, выходы котоpbtx соединены с соответствующими входными разрядами первого входа сумматора 3, первый выход которого соединен соответственно с разрядными входами регистра 4 поразрядных сумм, выход регистра 4 поразрядных сумм соединен с соответствующими разрядами второго входа сумматора 3 со сдвигом вправо на два разряда, пятый выход дешифратора 5 цифр множителя через триггер 7 соединен с четвертым входом дешифратора 5 цифр множителя, выход нулевого разряда сдвигового регистра 2 множителя соединен с пятым входом дешифратора 5 цифр множителя, третий выход которого соединен с третьим входом сумматора 3, выходы двух первых младших разрядов сумматора 3 соединены соответственно с входами первого и второго знаковых разрядов сдвигового регистра 2 множителя, выход триггера 7 соединен с входом установки в ноль триггера 6,

Устройство работает следующим образом.

Перед выполнением умножителя в регистре 1 множимого хранится множимое, представленное в дополнительном коде с h-разрядной мантиссой и одним знаковым разрядом, а в сдвиговом регистре 2 множителя хранится п младших разрядов множителя, представленного в дополнительном коде с 2празрядной мантиссой и двумя знаковыми разрядами. Регистр 4 поразрядных сумм обнулен.

В каждом такте умножения в дешифраторе 5 анализируются первьгй и второй младшие разряды регистра 2 и значение триггера 7, которое в исходном положении равно нулю. При нулевых значениях второго разряда регистра 2 и триггера 7 и единичном значении первого разряда регистра 2, а также при единичном значении триггера 7 и нулевых значениях первого и второго разрядов регистра 2 дешифратора 5 формирует управляющий сигнал на выходе 13 и нулевое значение на вход триггера 7. При единичных значениях первого.и второго разрядов регистра 2 и нулевом значрнии триггера 7, а такде при нулевом значении первого разряда регистра 2 и единичных значениях второго разряда регистра 2 и триггера 7 дешифратор 5 формирует управляющий сигнал на выходе 14 и единичное значение на вход 51 триггера 7, При единичном значении второго разряда регистра 2 и нулевых значениях первого разряда регистра 2 и триггера 7, а также при единичных значениях первого разряда регист ра 2 и триггера 7 и нулевом значении второго разря/,а регистра 2 дешиф ратор 5 формирует управляющий сигнал на выходе 15 и нулевое значение на вход триггера 7. При нулевых значениях первого и второго разрядов регистра 2 и триггера 7 дешифратор 5 формирует нулевое значение на вход триггера 7. При единичных значениях первого и второго разрядов регистра 2 и триггера 7 дешифратор 5 формирует единичное значение на вход триггера 7. При сформированном управляющем сигнале на выходе 13 дешифратора 5 разрешается прохождение прямого значения множимого на вход сумматора 3. При сформированном управляющем сигнале на выходе 14 дешифратора 5 разрешается прохождение инверсного значения множимйго на вход сумматора 3, одновременно единичное значение поступает на вход переноса младшего разряда сумматора 3. При сформирован ном управляющем сигнале на выходе 15 дешифратора 5 разрешается прохождение прямого значения множимого на вход сумматора 3 со сдвигом на один разряд влево. При отсутствии управляющих сигналов на выходах 13-15 дешифратора 5 на вход сумматора 3 прохождение множимого не разрешается, что соответствует подаче на вход сумматора 3 нулевого значения. На другой вход сумматора 3 подается зна чение регистра 4 со сдвигом на два разряда вправо, В сумматоре 3 производится поразрядное суммирование преобразованного множимого, содержимого регистра 4, сдвинутого на два разряда вправо, и значения, сформиро ванного дешифратором 5 и поданного на вход переноса младшего разряда сумматора 3. В результате суммирования на выходе сумматора 3 в каждом 86 разряде формируется значение суммы с учетом сквозного переноса, которое к началу второго такта записывается поразрядно в регистр 4. Значение регистра 2 сдвигается на два разряда вправо, так что значение третьего разряда передается на второй разряд и т.д. Значение первого и второго разрядов регистра 4 заносится соответственно в h-и и ( п - 1)-й разряды регистра 2. В триггер 7 заносится значение, сформированное дешифратором 5. Во втором такте цикл формирования промежуточного результата повторяется. Количество однотипных тактов формирования промежуточных результаTOB-i- 1-. в i. 1)-м такте п -и разряд регистра 2 переписывается в нулевой разряд регистра 2. Значение триггера 7 передается на вход триггера 6. Во все разряды регистра 2 из внешнего устройства заносится старшая часть мантиссы (п разр рядов) и знак (два разряда) множителя. в следуюп1их тактах происходит формирование промежуточных результатов аналогично первым п - 1 тактам, но в дешифраторе 5 вместо значений первого и второго разрядов регистра 2 анализируются значения нулевого и первого разрядов регистра 2 соответственно, вместо значения триггера 7 анализируется значение триггера 6, дешифратор 5 формирует значение на вход триггера 6. В результате умножения произведение формируется в регистре 4 (старшие п разрядов и знак) и в регистре 2 (младшие п разрядов). Таким образом, устройство позволяет умножать п-разрядное множимое (для п нечетных) на 2 -разрядный множитель с вычислением 2п-разрядного произведения, используя при этом уменьшенное по сравнению с известным устройством количество оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичныхчиСЕл B дОпОлНиТЕльНыХ КОдАХ | 1979 |

|

SU813420A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| Последовательное множительное устройство | 1981 |

|

SU1067500A1 |

| Устройство для ускоренного умножения | 1977 |

|

SU714395A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Устройство для умножения | 1983 |

|

SU1129606A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

УСТРОЙСТВО ДЛЯ УМН05ЧЕНИЯ ДВОИЧНЫХ ЧИСЕЛ В ДОПОЛНИТЕЛЬНЫХ КО,ТАХ, содержащее регистр множимого, сдвиговый регистр множителя, трехвходовой сумматор, регистр поразрядных сумм, дешифратор циФр множителя, первый и второй триггеры,первую, вторую и третью группы элементов И, группу элементов ИЛИ, причем выходы первого и второго разрядов сдвигового регистра множителя соединены с первым и вторым входами дешифратора цифр множителя, первый, второй и третий выходы которого соединены с первыми входами элементов И первой, второй и третьей групп соответственно, четвертый выход дешифратора цифр множителя через первый триггер соединен с третьим входом дешифратора цифр множителя, вторые входы элементов if первой группы соединены соответственно с прямыми выходами регист ра множимого, вторые входы элементов И второй группы соединены соответственно с прямыми выходами регистра множимого со сдвигом на один разряд влево, вторые входы, элементов И третьей группы соединены соответственно с инверсными выходят регистра множимого, вькоды элементов И первой, второй и третьей групп соединены с входами соответствующих элементов ИЛИ группы, выходы которых соединены с соответствующими входными разрядами первого входа сумматора, первый выход которого соединен с разрядными входами регистра поразрядных сумм, выход регистра поразрядных сумм соединен с соответствующими разрядами второго входа сумматора со сдвигом вправо на два разряда, отличающееся тем, что, с целью упрощения устройства, пятьй выход дешифратора цифр множителя через второй триггер соединен с четвертым входом дешифратора цифр множителя, выход нулевого разряда сдвигового регистра СО множителя соединен с пятым входом дешифратора цифр множителя, третий о о выход которого соединен с третьим входом сумматора, выходы двух первых СХ) младших разрядов сумматора соединены соответственно с входами первого и второго знаковых разрядов сдвигового регистра множителя, выход второго триггера соединен с входом установки в ноль первого триггера.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-15—Публикация

1983-06-16—Подача