Изобретение относится к вычислительной технике и может быть использовано в специализированных цифровых вычислительных машинах и вычислительных устройствах.

Цель изобретения - увеличение быстродействия и точности вычисления функций и х.

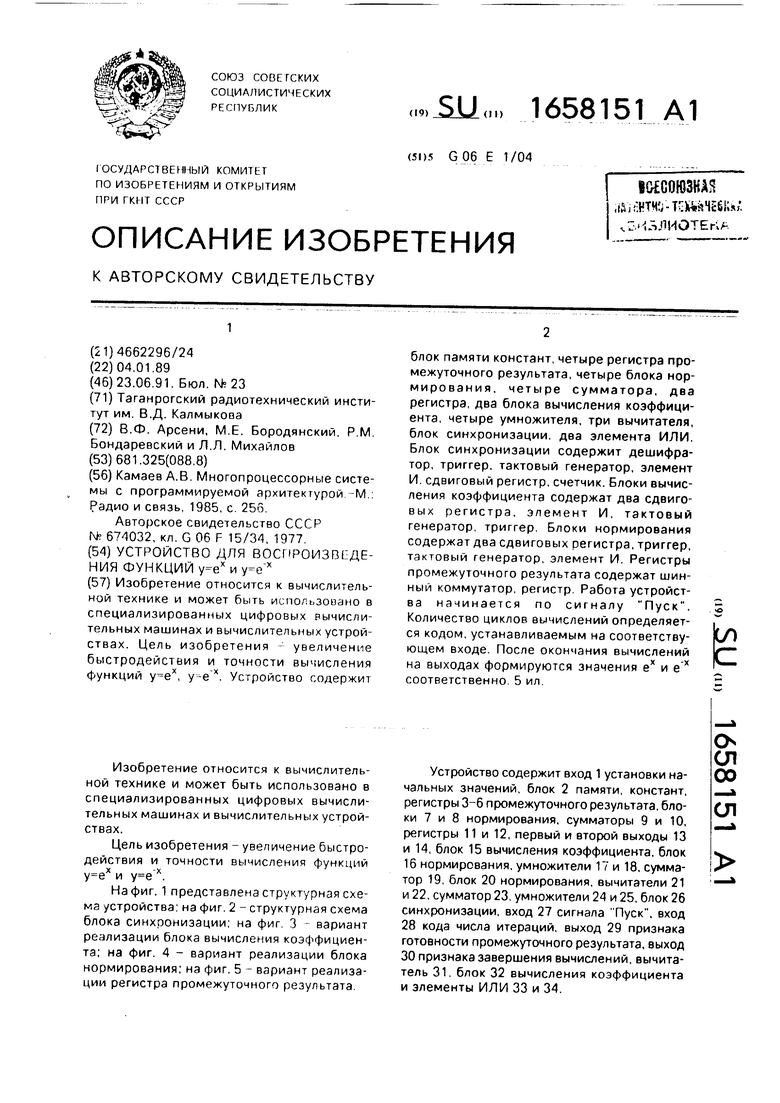

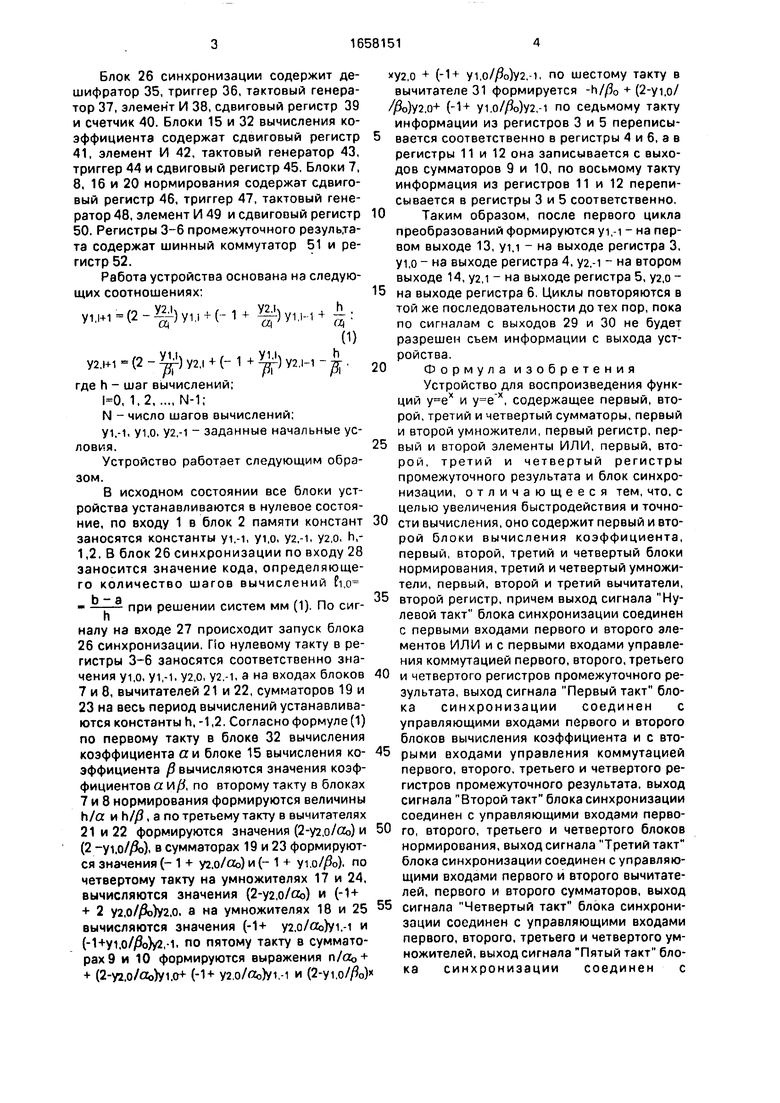

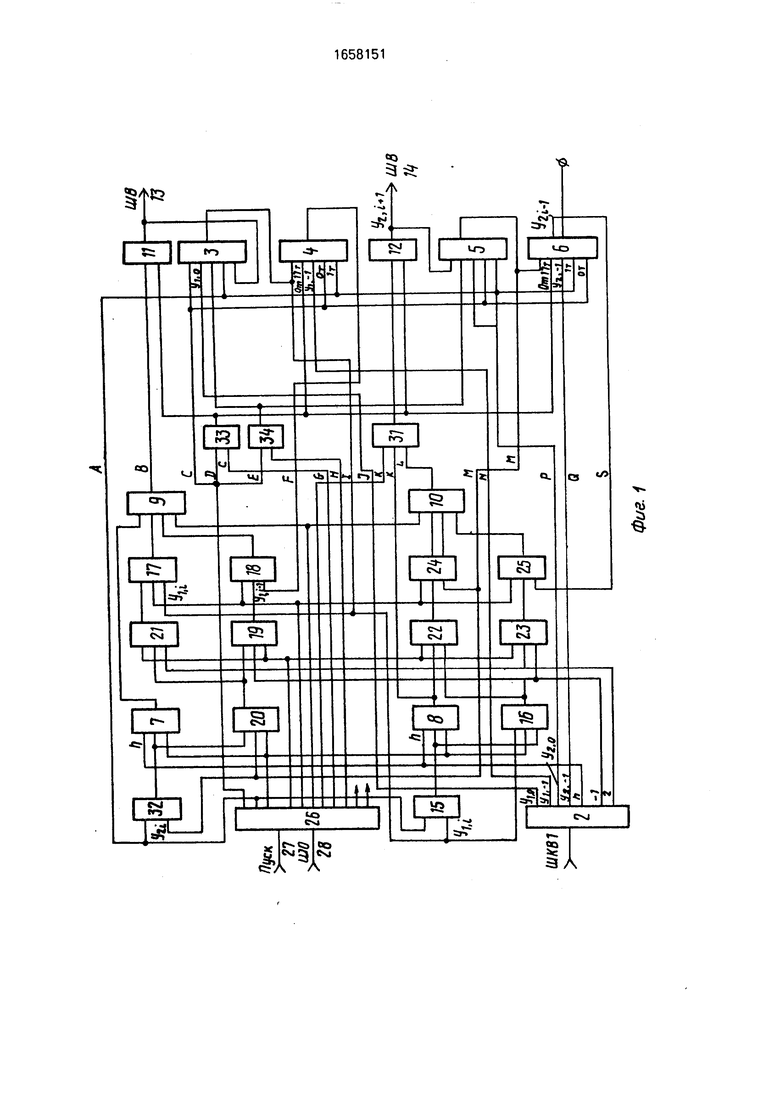

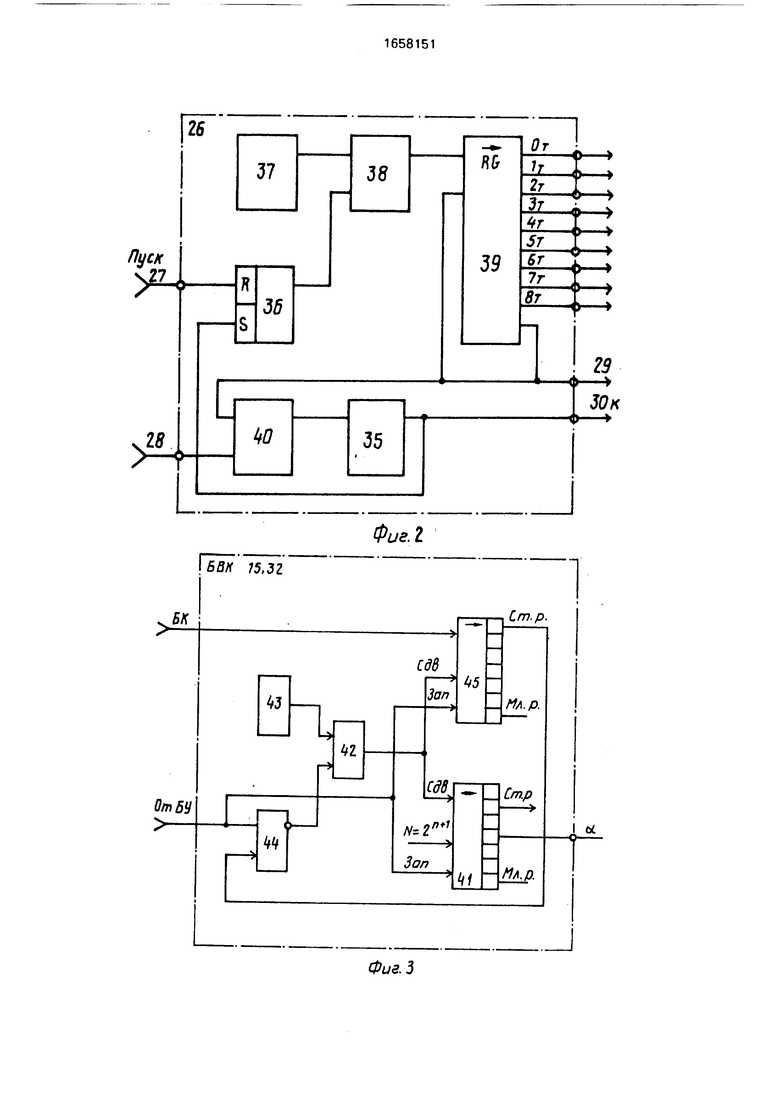

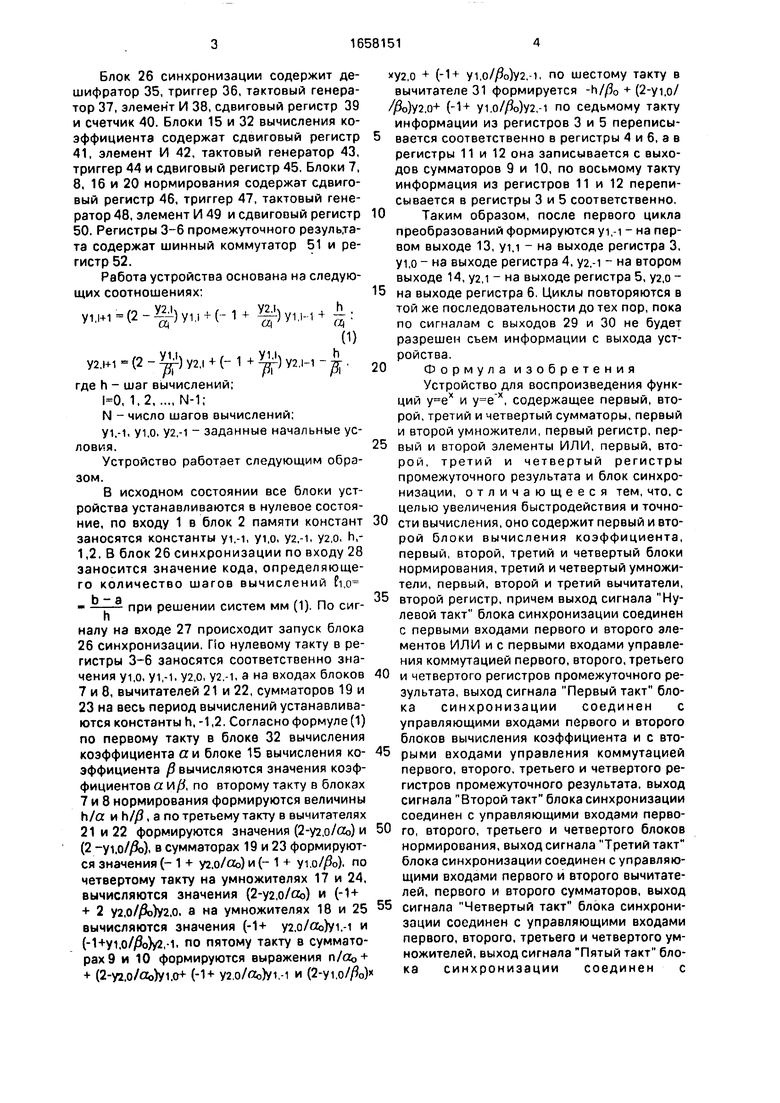

На фиг. 1 представлена структурная схема устройства на фиг 2-структурная схема блока синхоонизации, на фиг 3 - вариант реализации блока вычисления коэффициента; на фиг 4 - вариант реализации блока нормирования; на фиг. 5 - вариант реализации регистра промежуточного результата

Устройство содержит вход 1 установки начальных значений, блок 2 памяти, констант, регистры 3-6 промежуточного результата, блоки 7 и 8 нормирования, сумматоры 9 и 10, регистры 11 и 12, первый и второй выходы 13 и 14, блок 15 вычисления коэффициента, блок 16 нормирования, умножители 17 и 18, сумматор 19 блок 20 нормирования, вычитатели 21 и 22, сумматор 23 умножители 24 и 25, блок 26 синхронизации, вход 27 сигнала Пуск, вход 28 кода числа итераций, выход 29 признака готовности промежуточного результата, выход 30 признака завершения вычислений, вычита- тель 31 блок 32 вычисления коэффициента и элементы ИЛИ 33 и 34

О

ел

00

сл

Блок 26 синхронизации содержит дешифратор 35, триггер 36, тактовый генератор 37, элемент И 38, сдвиговый регистр 39 и счетчик 40. Блоки 15 и 32 вычисления коэффициента содержат сдвиговый регистр 41, элемент И 42, тактовый генератор 43, триггер 44 и сдвиговый регистр 45. Блоки 7, 8, 16 и 20 нормирования содержат сдвиговый регистр 46, триггер 47, тактовый генератор 48, элемент И 49 и сдвиговый регистр 50. Регистры 3-6 промежуточного результата содержат шинный коммутатор 51 и регистр 52.

Работа устройства основана на следующих соотношениях:

У2.1

УШ1(2-)У1,1 + (-1 +

)У1М+

а у 0|

(D

У2.Н-1-()У2.1+()У2.Мгде h - шаг вычислений;

, 1.2N-1;

N - число шагов вычислений;

У1.-1, У1,о. У2.-1 - заданные начальные условия.

Устройство работает следующим образом.

В исходном состоянии все блоки устройства устанавливаются в нулевое состояние, по входу 1 в блок 2 памяти констант заносятся константы yi,-i, yi.o. У2.-1, У2,о, h,- 1,2. В блок 26 синхронизации по входу 28 заносится значение кода, определяющего количество шагов вычислений fi,o

- --- при решении систем мм (1). По сиг- п

налу на входе 27 происходит запуск блока 26 синхронизации. По нулевому такту в регистры 3-6 заносятся соответственно значения yi.o, У1.-1. У2,о, У2.-1. а на входах блоков 7 и 8, вычитателей 21 и 22, сумматоров 19 и 23 на весь период вычислений устанавливаются константы h,-1,2. Согласно формуле (1) по первому такту в блоке 32 вычисления коэффициента аи блоке 15 вычисления коэффициента / вычисляются значения коэффициентов а и/У, по второму такту в блоках 7 и 8 нормирования формируются величины h/a и h//, а по третьему такту в вычитателях 21 и 22 формируются значения (2-у2,о/Оо) и (2 -yi.o//3o), в сумматорах 19 и 23 формируются значения (- 1 + уг.о/Оо) и (- 1 + yi.o//30). по четвертому такту на умножителях 17 и 24, вычисляются значения (2-у2,о/Оо) и (-1+ + 2 У2,0/Д)у2,о, а на умножителях 18 и 25 вычисляются значения (-1+ y2,o/Oo)yi,-i и (-1+У1,0//Зо)у2,-1, по пятому такту в сумматорах 9 и 10 формируются выражения п/оь +

+ (2-у2.0/Оо)У1.0+ (-1+ У2,0/«о)У1.-1 И (2-yi.O/A))

У2,о + (-1+ У1,)у2,-1, по шестому такту в

вычитателе 31 формируется -h//30 + (2-yi,o/

//30)у2.о+ (-1+ У1.)у2,-1 по седьмому такту

информации из регистров 3 и 5 переписывается соответственно в регистры 4 и 6, а в регистры 11 и 12 она записывается с выходов сумматоров 9 и 10, по восьмому такту информация из регистров 11 и 12 переписывается в регистры 3 и 5 соответственно,

Таким образом, после первого цикла преобразований формируются yi,-i - на первом выходе 13, yi,i - на выходе регистра 3, У1,о на выходе регистра 4, у2,-1 - на втором выходе 14, у2,1 - на выходе регистра 5, уа.о на выходе регистра 6. Циклы повторяются в той же последовательности до тех пор, пока по сигналам с выходов 29 и 30 не будет разрешен съем информации с выхода устройства,

Формула изобретения

Устройство для воспроизведения функций и , содержащее первый, второй, третий и четвертый сумматоры, первый и второй умножители, первый регистр, первый и второй элементы ИЛИ, первый, второй, третий и четвертый регистры промежуточного результата и блок синхронизации, отличающееся тем, что, с целью увеличения быстродействия и точности вычисления, оно содержит первый и второй блоки вычисления коэффициента, первый, второй, третий и четвертый блоки нормирования, третий и четвертый умножители, первый, второй и третий вычитатели,

второй регистр, причем выход сигнала Нулевой такт блока синхронизации соединен с первыми входами первого и второго элементов ИЛИ и с первыми входами управления коммутацией первого, второго, третьего

и четвертого регистров промежуточного результата, выход сигнала Первый такт блока синхронизации соединен с управляющими входами первого и второго блоков вычисления коэффициента и с вторыми входами управления коммутацией первого, второго, третьего и четвертого регистров промежуточного результата, выход сигнала Второй такт блока синхронизации соединен с управляющими входами первого, второго, третьего и четвертого блоков нормирования, выход сигнала Третий такт блока синхронизации соединен с управляющими входами первого и второго вычитателей, первого и второго сумматоров, выход

сигнала Четвертый такт блока синхронизации соединен с управляющими входами первого, второго, третьего и четвертого умножителей, выход сигнала Пятый такт блока синхронизации соединен с

управляющими входами третьего и четвертого сумматоров, выход сигнала Шестой такт блока синхронизации соединен с управляющим входом третьего вычитателя. выход которого соединен с информационным входом второго регистра, управляющий вход которого соединен с управляющим входом первого регистра, с входами управления записью второго и четвертого регистров промежуточного результата и с выходом первого элемента ИЛИ, второй вход которого соединен с выходом сигнала Седьмой такт блока синхронизации, выход сигнала Восьмой такт блока синхронизации соединен с вторым входом второго элемента ИЛИ, выход которого соединен с входами управления записью первого и третьего регистров промежуточного результата, выход первого регистра соединен с первым информационным выходом устройства и с первым информационным входом первого регистра промежуточного результата, выход которого соединен с первыми информационными входами первого умножителя и четвертого блока нормирования, с информационным входом второго блока вычисления коэффициента и с первым информационным входом второго рпги- стра промежуточного результата выход которого соединен с первым информационным ВХОДОМ ВТОРОГО уМНОЖИТеЛЯ, ВЫлОД

которого соединен с первым информационным входом третьего сумматора, выход которого соединен с информационным входом первого регистра, выход второго регистра соединен с вторым информационным выходом устройства и с первым инфор- мационным входом третьего регистра промежуточного результата, выход которого соединен с информационным входом первого блока вычисления коэффициента, с первыми информационными входами второго блока нормирования, третьего умножителя и четвертого регистра промежуточного результата, выход которого соединен с первым информационным входом четвертого умножителя, выход которого соединен с первым информационным входом четвертого сумматора, выход которого соединен с входом уменьшаемого третьего вычитателя, вход уменьшаемого которого соединен с выходом третьего блока нормирования, первый информационный вход которого соединен с выходом второго блока вычисления коэффициента и с вторым информационным входом четвертого блока нормирования, выход которого соединен с

первым информационным входом второго сумматора и с входом вычитаемого второго вычитателя, выход которого соединен с вторым информационным входом третьего умножителя, выход которого соединен с

0 вторым информационным входом четвертого сумматора, второй информационный вход четвертого умножителя соединен с выходом второго сумматора, второй информационный вход которого соединен с входом

5 константы Минус один устройства и с первым информационным входом первого сумматора, выход которого соединен с вторым информационным входом второго умножителя, второй информационный вход первого

0 сумматора соединен с входом вычитаемого первого вычитателя и с выходом второго блока нормирования, второй информационный вход которого соединен с выходом первого блока вычисления коэффициента и с

5 первым входом первого блока нормирования, выход которого соединен с вторым информационным входом третьего сумматора, третий информационный вход которого соединен с выходом первого умножителя, вто0 рой информационный вход которого гоединен с выходом первого вычитателя, пход уменьшаемого которого соединен с входом уменьшаемого второго вычитателя и с входом константы два устройства, второй

5 информационный вход первого блока нормирования соединен с входом задания шага вычислений устройства и с вторым информационным входом третьего блока нормирования, вторые информационные входы

0 первого, второго, третьего и четвертого регистров промежуточного результата соединены с первым, вторым, третьим и четвертым входами начальных значений устройства соответственно, вход сигнала

5 Пуск блока синхронизации является входом запуска устройства, вход задания числа циклов блока синхронизации является входом кода числа итераций устройства, первый и второй управляющие выходы блока

0 синхронизации являются выходами признака готовности промежуточного результата и признака завершения вычислений устройства.

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифмической функции | 1988 |

|

SU1596323A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1434427A1 |

| Устройство для вычисления арктангенса | 1985 |

|

SU1314336A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Устройство для матричных операций | 1989 |

|

SU1777154A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| Устройство для прогнозирования длительности производственных операций | 1990 |

|

SU1781685A1 |

| Цифровой адаптивный фильтр | 1990 |

|

SU1837322A1 |

Изобретение относится к вычислительной технике и может быть испогьзосано в специализированных цифровых вычислительных машинах и вычислительных устройствах. Цель изобретения - увеличение быстродействия и точности вычисления Функций , у-е х Устройство содержит блок памяти констант, четыре регистра промежуточного результата, четыре блока нормирования, четыре сумматора, два регистра, два блока вычисления коэффициента, четыре умножителя, три вычитателя, блок синхронизации два элемента ИЛИ. Блок синхронизации содержит дешифратор, триггер, тактовый генератор, элемент И сдвиговый регистр, счетчик. Блоки вычисления коэффициента содержат два сдвиговых регистра, элемент И, тактовый генератор триггер Блоки нормирования содержат два сдвиговых регистра, триггер, тактовый генератор, элемент И Регистры промежуточного результата содержат шинный коммутатор регистр Работа устройства начинается по сигналу Пуск. Количество циклов вычислений определяется кодом, устанавливаемым на соответствующем входе После окончания вычислений на выходах формируются значения ех и е х соответственно 5 ил Ё

lrai«

be

3

Фиг. 2

Физ.З

БН 7.8.16,20

От Я6

Запись

ОтБУ

Го47

«

0т5йг

БУ26

57

61/26

П

я

mp.

ot

-

5ff

Я6

W

f/77.p.

ЯС ЗЛ,5,5

52

t

| Камзев А.В Многопроцессорные системы с программируемой архитектурой -М Радио и связь, 1985,с 256 Авторское свидетельство СССР № 674032,кл G 06 F 15/34,1977 |

Авторы

Даты

1991-06-23—Публикация

1989-01-04—Подача