Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах воспроизведения логарифмических функций.

Цель изобретения - расширение области применения за счет увеличения диапазона изменения аргумента.

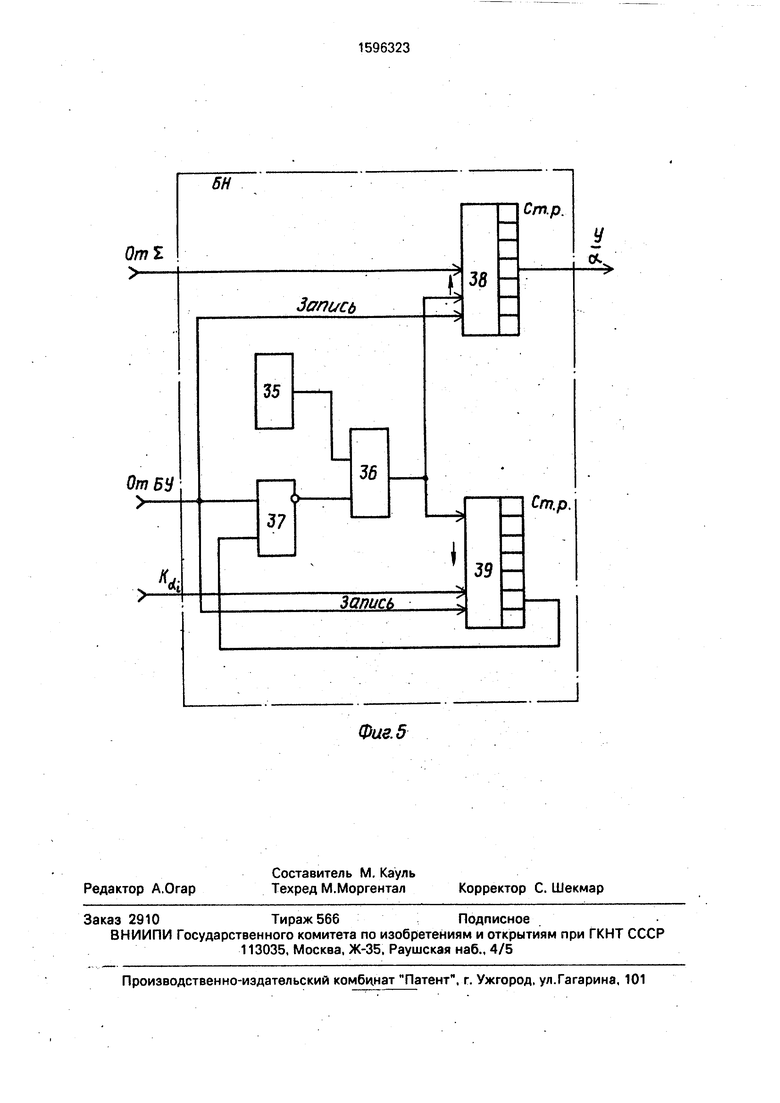

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - схема блока синхронизации, пример исполнения; на фиг. 3 временная диаграмма работы блока синхронизации; на фиг. 4 - схема блока формирования коэффициента, пример исполнения; на фиг. 5 - схема блока нормирования, пример исполнения.

Устройство.содержит вход 1 начального значения аргумента, блок 2 формирования коэффициента, первый и второй блоки 3 и 4 нормирования, первый и второй вычитатели 5 и 6, первый умножитель 7, третий вычитатель 8, сумматор 9, выход 10 результата. второй шинный коммутатор 11, первый регистр 12. первый шинный коммутатор 13. второй регистр 14, вход 15 задания констант, блок 16 памяти констант, блок 17 сравнения, блок 18 синхронизации, вход 19 сигнала Пуск, второй умножитель 20. накапливающий сумматор 21, а также первый и второй элементы ИЛИ 22 и 23. Блок синхронизации образуют генератор 24 тактовых импульсов, триггер 25, первый и второй элементы И 26 и 27, элемент ИЛИ 28 и сдвиговый регистр 29. Блок формирования коэффициента включает генератор 30, элемент И 31, триггер 32, а также первый и второй сдвиговые регистры 33 и 34. Блок нормирования содержит генератор 35, элемент И 36, триггер 37, первый и второй сдвиговые регистры 38 и 39. Устройство работает следующим образом. Для воспроизведения значений функции у 1пх использован модифицированный алгоритм Эмбла dy(a.-x)dy + dx,(1) где а-определенный параметр. Решением (1) является функция у 1пх. Уравнению (1) соответствует разностный аналог l y-i- ум (2-§)у. -0I 1.2...,N;.(2) Каноническая форма (2) имеет вид |У| 4-1 А| У| + fi уо задан Параметр Oi вырабатывается в устройстве согласно условию II xi II 01, поэтому в интервале а,Ь норма оператора AI, определяемая по формуле (3), не превосходит единицы, С целью увеличения быстродействия (2) параметр сц должен быть числом, ближайшим к X и кратным 2 . Например, х 0,126, .125 2, k 3. Формула методической погрешноЬти для (2) имеет вид h (х - 1),,.,4 У В исходном состоянии по входу 15 задания констант заносятся величины h, уо. у 1, Xk. Шинные коммутаторы 13 и 11 устанавливаются в состояние, обеспечивающее подключение выходов блока 16 памяти констант к входам регистров 14 и 12 соответственно. По приходу импульса по входу 19 сигнала Пуск в регистры 14 и 12 соответственно заносятся величины уо. и yi, а блок 18 синхронизации начинает вырабатывать последовательность импульсов. В блоке 2 формирования коэффициента по первому импульсу оЬуществляется формирование коэффициента а , по второму импульсу в блоках 3 и 4 нормирования формируются величины х/а и h/da , по третьему импульсу в вычитателе 5 формируется величина (2 - ), а в вычитателе 6 величина (I - ), по четвертому импульсу в умножителе 20 формируется произведение yi(2 - ), а в умножителе 7 - произведение II Х|.. Уо(1 - ), ПО пятому импульсу в вычитателе ViXl 8 формируется разность yi(2 ) Уо О ж ) по шестому импульсу в сумматоре 9 формируется значение у2, по седьмому импульсу шинный коммутатор 13 переключается в положение, при котором выход регистра 12 подключается к входу регистра 14 и информация ji3 регистра 12 заносится в регистр 14, т,е. вместо уо записывается yi. По восьмому импульсу шинный коммутатор 11 переключается в положение, при котором выход сумматора 9 подключается к. входу регистра 12 и происходит перезапись значения у2 в регистр 12 вместо у1. Одновременно в накапливающем сумматоре 21 осуществляется увеличение числа xi на величину h, которая на девятом такте сравнивается C-XR в блоке 17 сравнения. Если выполняется равенство xk ih + х, то на выходе блока сравнения появляется сигнал, останавливав ющий устройство и являющийся признаком окончания вычислений. В противном случае блок 18 синхронизации вырабатывает новую последовательность из девяти импульсов, причем по шестому импульсу на выходе 10 результата формируется очередное значение функции согласно алгоритму (1). Формула изобретения Устройство для вычисления логарифмической функции, содержащее первый и второй регистры, первый и второй элементы ИЛ И, сумматор и блок синхронизации, причем вход запуска блока синхронизации соединен с входом Пуск устройства, о т л и чающееся тем, что, с целью расширения области применения за счет увеличения диапазона изменения аргумента, оно содержит блок формирования коэффициента, первый и второй блоки нормирования, первый и второй шинные коммутаторы, блок сравнения, первый, второй и третий вычитатели, первый и второй умножители, накапливающий сумматор и блок памяти констант, причем вход задания констант ус-

тройства соединен с информационным входом блока памяти констант, выход конечного ;значения аргумента которого соединен с первым информационным входом.блока сравнения, выход которого соединен с входом останова блока синхронизации, вход задания константы два устройства соединен с первым информационным входом первого вычитателя, вход задания константы один устройства соединен с первым информационным входом второго вычитателя, второй информационный вход которого соединен с вторым информационным входом первого вычитателя и с выходом первого блока нормирования, первый информационный вход которого соединен с первым информационным входом второго блока нормирования и с выходом блока формирования коэффициента, информационный вход которого соединен с вторым информационным входом первого блока нормирования, с вторым информационным входом блока сравнения и с выходом накапливающего сумматора, установочный вход которого соединен с входом начального значения аргумента устройства, информационный вход накапливающего сумматора соединен с выходом значения шага аргумента блока памяти констант и с вторым информационным входом второго блока нормирования, выход которого соединен с первым информационным входом сумматора, второй информационный вход которого соединен с выходом третьего вычитателй, первый информационный вход которого соединен с выходом первого умножителя, первый информационный вход которого соединен с выходом второго регистра, информационный вход которого соединен с выходом первого шинного коммутатора, первый информационный вход которого соединен с выходом значения функции в нулевой точке блока памяти констант, второй информационный вход первого шинного коммутатора соединен с первым входом второго умножителя и с выходом первого регистра, информационный вход которого соединен с выходом второго шинного коммутатора, первый информационный вход которого соединен с выходом значения функции в первой точке памяти констант, второй информационный вход второго шинного коммутатора соединен с выходом сумматора и с выходои результата устройства, выход первого вычитателя соединен с вторым информационным входом второго умножителя, выход которого соединен с вторым информационным входом третьего вычитателя, выход второго вычитателя соединен с вторым информационным входом второго умножителя, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый выходы блока синхронизации соединены соответственно с входом управления блока формирования коэффициента, входами управления первого и второго блоков нормирования, с входами управления первого и второго вычитателей, с входами управления первого и второго умножителей, с входом управления третьего вычитателя, с входом управления первого шинного х:оммутатора и первым входом первого элемента ИЛИ, с входами управления накапливающего сумматора и второго шинного коммутатора и с первым входом второго элемента ИЛИ, с входом управления блока сравнения, вход управления первого регистра - с выходом второго элемента ИЛИ, второй вход которого соединен с входом Пуск устройства и с вторымвходом первого элемента ИЛИ, выход которого соединен с входом управления второго регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления арктангенса | 1985 |

|

SU1314336A1 |

| Устройство для воспроизведения функций @ и @ | 1989 |

|

SU1658151A1 |

| Устройство для вычисления тригонометрического тангенса | 1986 |

|

SU1334144A1 |

| Устройство для умножения | 1986 |

|

SU1388852A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Устройство для вычисления квадратного корня | 1984 |

|

SU1191908A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Устройство для вычисления функций | 1987 |

|

SU1411775A1 |

| Устройство для коррекции изображений объектов | 1989 |

|

SU1711206A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах для воспроизведения логарифмических функций. Цель изобретения - расширение области применения за счет увеличения диапазона изменения аргумента. Поставленная цель достигается тем, что устройство содержит вход начального значения аргумента, блок формирования коэффициента, первый и второй блоки нормирования, три вычитателя, два умножителя, сумматор, выход результата, два шинных коммутатора, два регистра, вход задания констант, блок памяти констант, блок сравнения, блок синхронизации, вход сигнала "пуск", накапливающий сумматор, первый и второй элементы ИЛИ. Блок синхронизации содержит генератор тактовых импульсов, триггер, первый и второй элементы И, элемент ИЛИ, сдвиговый регистр. Блок формирования констант содержит генератор, элемент И, триггер, первый и второй сдвиговые регистры. Блок нормирования содержит генератор, элемент И, триггер, первый и второй сдвиговые регистры. Работа устройства основана на соотношении Y I+1 = (2 - X I/Α I) Y I - (1- X I/Α I) Y I-1 + H/Α I, I= 1,2 ...,K

Y 0, Y 1, X 1, H, X K - заданные значения. 5 ил.

Фиг. 2

Фиг.З

ФигЛ

От г

-

Запись

ОтБУ

1 37

-i«I

Запись

л

38

Ст.р.

39

-5

Фие.5

| Цифровое устройство для логарифмирования двоичных чисел | 1972 |

|

SU448459A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1990-09-30—Публикация

1988-02-15—Подача