113

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и структурах для вычисления и воспроизведения значений тригонометрических обратных функций.

Цель изобретения - расширение области применения за счет расширения пределов изменения аргумента.

В .основу работы предлагаемого устройства положен следующий разностный алгоритм;

(1)

(i 0,1,...,N-0

где h - шаг решения; у,, Уо - начальные условия, XjE ГО,МЗ, параметр (X.; определенным образом получается в устройстве.

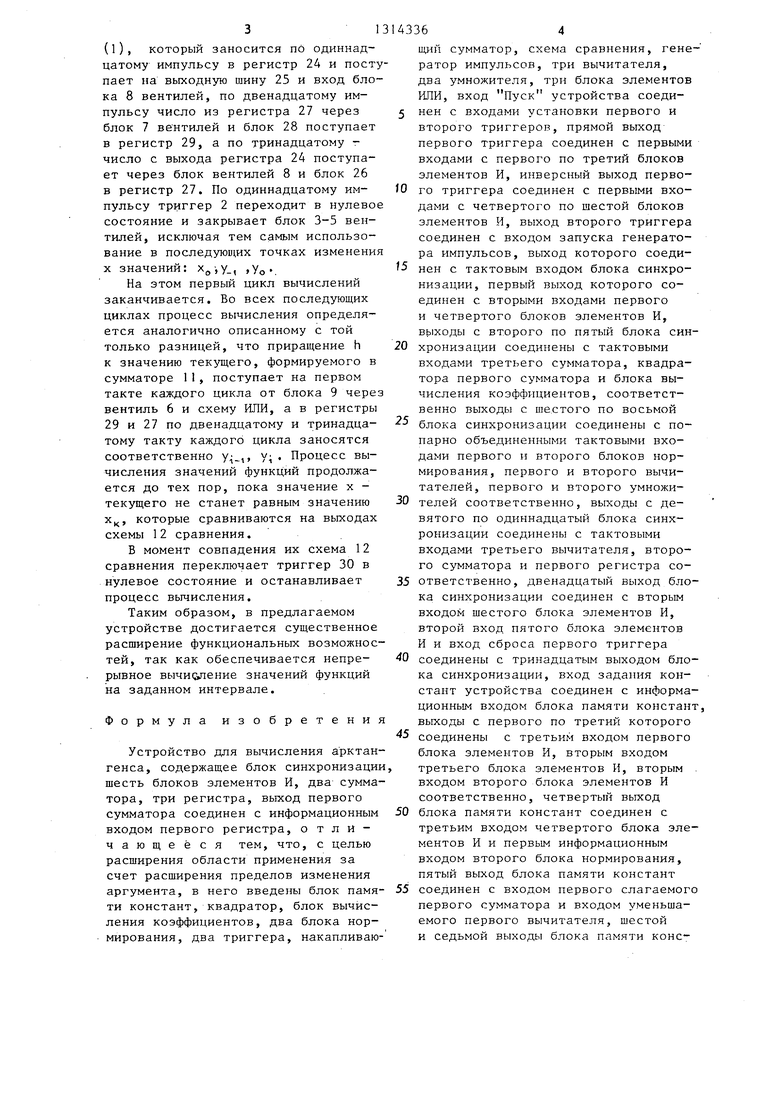

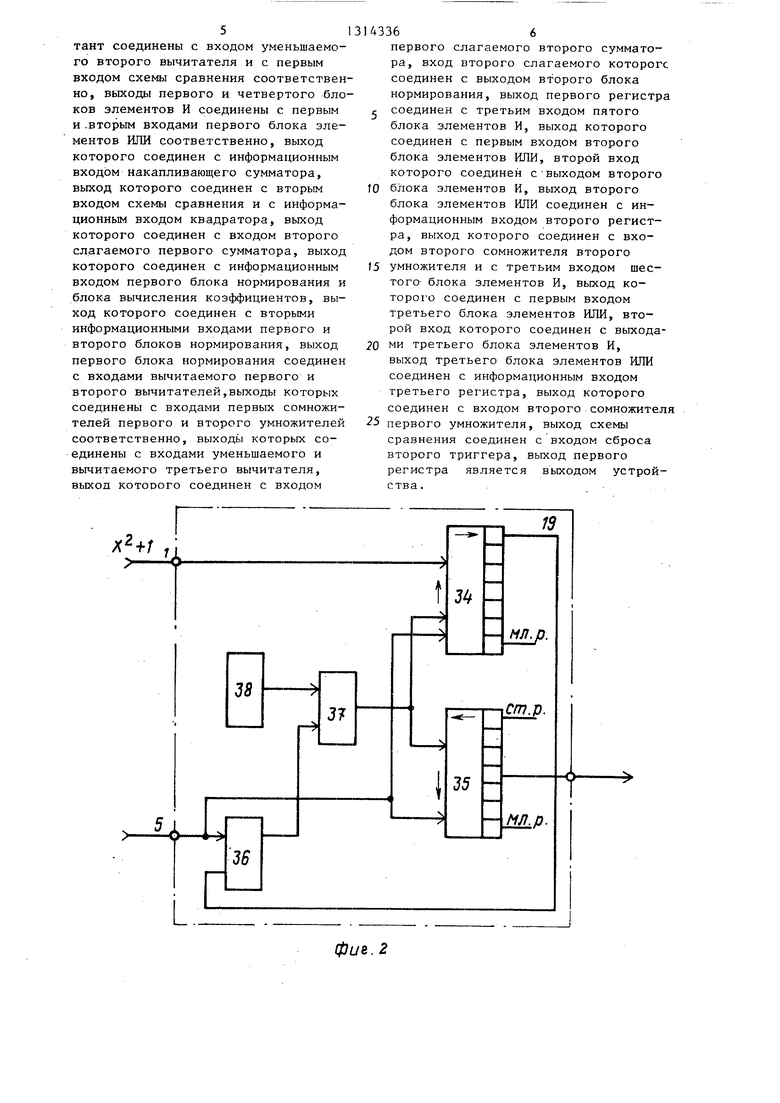

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - схема блока вычисления коэффициента; на фиг.З - то же, блока нормирования.

Устройство содержит (фиг.О шину 1 Пуск, триггер 2, блоки элементов И 3-8, блок 9 памяти констант, блок элементов ИЛИ 10, сумматор 11, схему 12 сравнения, квадратор 13, сумматор 14, блок 15 вычисления коэффициентов, блок 16 нормирования, вычитатели 17-18, умножители 19 и 20, вычитатель 21, сумматор 22, блок 23 нормирования, регистр 24, выход 25 устройства, блок элементов ИЛИ 26, регистр 27, блок элементов ИЛИ 28, регистр 29, триггер 30, генератор 31 импульсов, блок 32 синхронизации, вход 33 задания коэффициентов устройства.

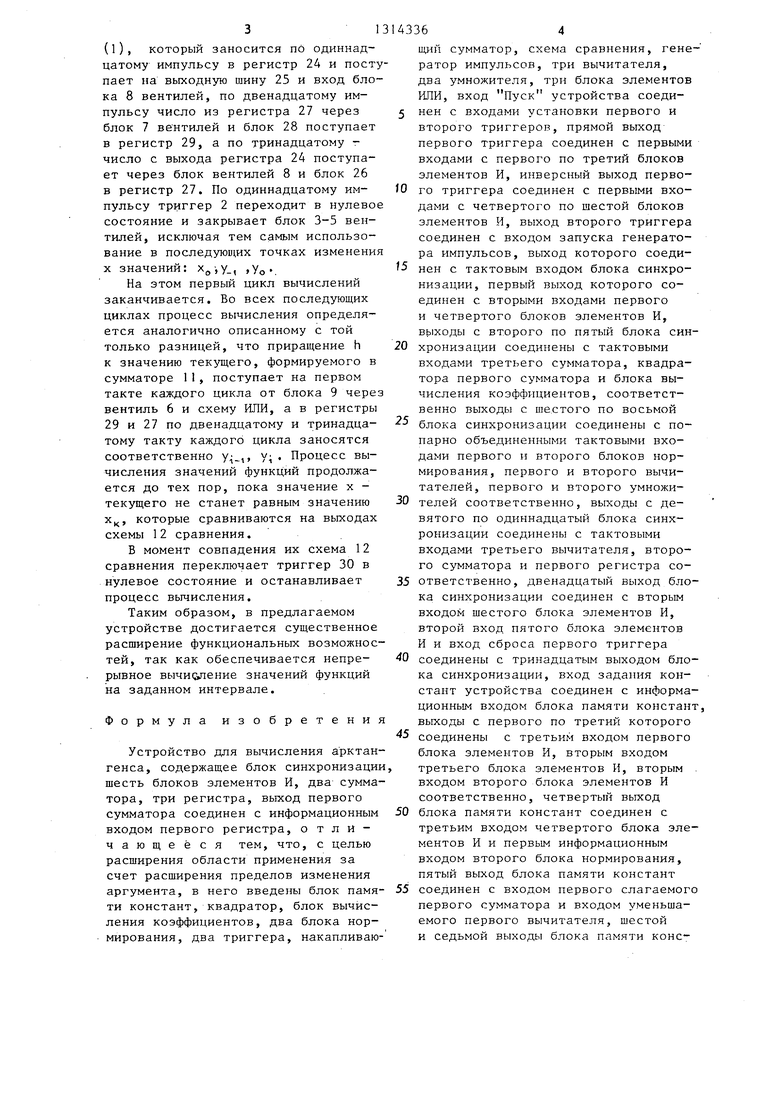

В состав блока 15 вычисления входят следующие узлы: сдвиговые регистры 34 и 35, триггер 36, элемент И 37, генератор 38.

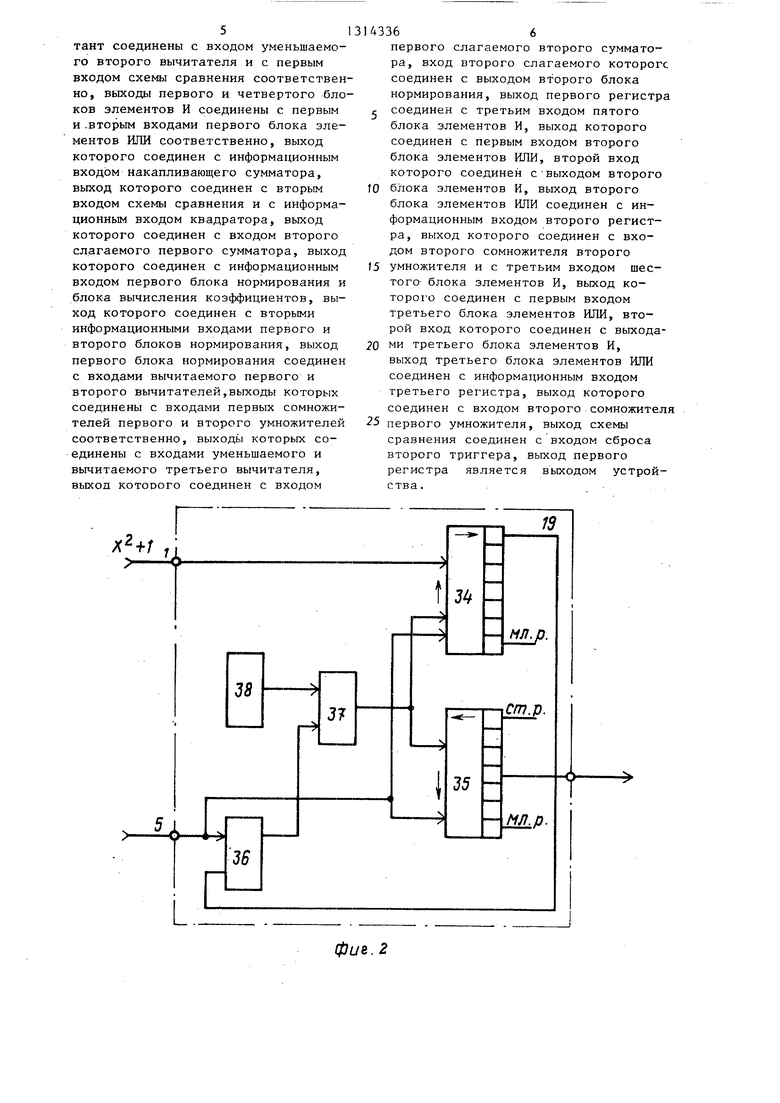

В состав, блоков 16 и 23 нормирования входят следующие узлы: сдвиговые регистры 39 и 40, триггер 41, элемент И 42, генератор 43.

Блок 15 вычисления коэффициента oi (фиг.З) служит для получения коэффициента oi из поступающего в десятичном коде числа 1 + х путем выделения старшего разряда числа, что легко реализуется на сдвиговых регистрах 34 и 35 подсчетом количест62

ва разрядов сдвигаемого числа до появления старшего разряда преобразуемого числа.

Блоки 16 и 23 нормирования представляют собой сдвиговые регистры 39 и 40, обеспечивающие деление величин х + 1 и h наоб , путем сдвига этих чисел на количество разрядов числа 0 .

Блок 9 памяти констант служит для .хранения констант и начальных данных:

УО которые располагаются соответственно на первом, втором, третьем, четвертом, пятом, шестом, седьмом выходах.

Устройство работает следующим образом.

Перед началом работы по шине 33 в блок 9 поступают величины х, у, ,

у„, h,

2, х, триггеры и регистры установлены в нулевое состояние. По приходу сигнала Пуск по ине 1 триггеры 2 и 30 устанавливаются в единичное состояние, а в регистры 29 и 27 заносятся начальные значения у.,, , у, поступающие с блока 9, через блоки 4,28 и 5, 26, и генератор 31 начинает вырабатывать последовательность импульсов, поступающих в блок 32 управления. По первому импульсу блока 32 управления х, с блока 9 через блоки 3 и 10 поступает на вход сумматора 11, по второму импульсу это число

регистрируется в сумматоре I1, где формируется величина х, по третьему импульсу в блоке 13 производится операция возведения в квадрат числа X, по четвертому - на выходе блока

14 формируется число 1 + х, а по пятому в блоке 15 формируется величина об, по шестому импульсу в блоках 16 и 23 формируются числа (1+)/с6 и h/ui, а по седьмому импульсу в блоках 17 и 18 вычисляются соответственно значения величин: 1 1+х

1+х

-V- «

2 - , по восьмому - результаты

полученные в блоках 17 и 18, умножаются соответственно на значение у, , поступающее с регистра 29 и на значение Уд, поступающее с регистра 27. По девятому импульсу на вычитателе

21 формируется разность (2-(х +1)/

-2

/oi) - УО ( рТ -)у, , а по десятому импульсу в сумматоре,22 формируется окончание результата (см.

31

(l), который заносится пО одиннадцатому импульсу в регистр 24 и поступает на выходную шину 25 и вход блока 8 вентилей, по двенадцатому импульсу число из регистра 27 через блок 7 вентилей и блок 28 поступает в регистр 29, а по тринадцатому - число с выхода регистра 24 поступает через блок вентилей 8 и блок 26 в регистр 27. По одиннадцатому импульсу триггер 2 переходит в нулевое состояние и закрывает блок 3-5 вентилей, исключая тем самым использование в последующих точках изменения X значений: ,у, ,Уо.

На этом первый цикл вычислений заканчивается. Во всех последующих циклах процесс вычисления определяется аналогично описанному с той только разницей, что приращение h к значению текущего, формируемого в сумматоре 11, поступает на первом такте каждого цикла от блока 9 через вентиль 6 и схему ИЛИ, а в регистры 29 и 27 по двенадцатому и тринадцатому такту каждого цикла заносятся соответственно у,, У;. Процесс вычисления значений функций продолжается до тех пор, пока значение х - текущего не станет равным значению х, которые сравниваются на выходах схемы 12 сравнения.

В момент совпадения их схема 12 сравнения переключает триггер 30 в нулевое состояние и останавливает процесс вычисления.

Таким образом, в предлагаемом устройстве достигается существенное расширение функциональных возможностей, так как обеспечивается непрерывное вычийпение значений функций на заданном интервале.

Формула изобретения

Устройство для вычисления арктангенса, содержащее блок синхронизации шесть блоков элементов И, два сумматора, три регистра, выход первого сумматора соединен с информационным входом первого регистра, отличающееся тем, что, с целью расширения области применения за счет расширения пределов изменения аргумента, в него введены блок памяти констант, квадратор, блок вычисления коэффициентов, два блока нормирования, два триггера, накапливаю64

щий сумматор, схема сравнения, гене- ратор импульсов, три вычитателя, два умножителя, три блока элементов ИЛИ, вход Пуск устройства соединен с входами установки первого и второго триггеров, прямой выход первого триггера соединен с первыми входами с первого по третий блоков элементов И, инверсный выход первого триггера соединен с первыми входами с четвертого по шестой блоков элементов И, выход второго триггера соединен с входом запуска генератора импульсов, выход которого соединен с тактовым входом блока синхронизации, первый выход которого соединен с вторыми входами первого и четвертого блоков элементов И, вь1ходы с второго по пятый блока синхронизации соединены с тактовыми входами третьего сумматора, квадратора первого сумматора и блока вычисления коэффициентов, соответственно выходы с ше.стого по восьмой

блока синхронизации соединены с попарно объединенными тактовыми входами первого и второго блоков нормирования, первого и второго вычи- тателей, первого и второго умножи

телеи соответственно, выходы с де

вятого по одиннадцатый блока синхронизации соединены с тактовыми входами третьего вычитателя, второго сумматора и первого регистра соответственно, двенадцатый выход блока синхронизации соединен с вторым входом шестого блока элементов И, второй вход пятого блока элементов И и вход сброса первого триггера

соединены с тринадцатым выходом блока синхронизации, вход констант устройства соединен с информационным входом блока памяти констант, выходы с первого по третий которого

соединены с третьим входом первого

блока элементов И, вторым входом третьего блока элементов И, вторым , входом второго блока элементов И соответственно, четвертый выход

блока памяти констант соединен с

третьим входом четвертого блока элементов И и первым информационным входом второго блока нормирования, пятый выход блока памяти констант

соединен с входом первого слагаемого первого сумматора и входом уменьшаемого первого вычитателя, шестой и седьмой выходы блока памяти коне5

тант соединены с входом уменьшаемого второго вычитателя и с первым входом схемы сравнения соответственно, выходы первого и четвертого блоков элементов И соединены с первым и .вторым входами первого блока элементов ИЛИ соответственно, выход которого соединен с информационным входом накапливающего сумматора, выход которого соединен с вторым входом схемы сравнения и с информационным входом квадратора, выход которого соединен с входом второго слагаемого первого сумматора, выход которого соединен с информационным входом первого блока нормирования и блока вычисления коэффициентов, выход которого соединен с вторыми информационными входами первого и второго блоков нормирования, выход первого блока нормирования соединен с входами вычитаемого первого и второго вычитателей,выходы которых соединены с входами первых сомножителей первого и второго умножителей соответственно, выходы которых соединены с входами уменьшаемого и вычитаемого третьего вычитателя, выхоп которого соединен с входом

фиг. 2

143366

первого слагаемого второго сумматора, вход второго слагаемого которого соединен с выходом второго блока нормирования, выход первого регистра

г соединен с третьим входом пятого блока элементов И, выход которого соединен с первым входом второго блока элементов ИЛИ, второй вход которого соединен с выходом второго

10 блока элементов И, выход второго блока элементов ИЛИ соединен с информационным входом второго регистра, выход которого соединен с входом второго сомножителя второго

(5 умножителя и с третьим входом шестого- блока элементов И, выход ко- Topoi o соединен с первым входом третьего блока элементов ИЛИ, второй вход которого соединен с выхода20 ми третьего блока элементов И,

выход третьего блока элементов ИЛИ соединен с информационным входом третьего регистра, выход которого соединен с входом второго сомножителя

25 первого умножителя, выход схемы сравнения соединен с входом сброса второго триггера, выход первого регистра является выходом устройства.

41)

/

офиг.З

20 и 21 I

-W

42

С т. p.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифмической функции | 1988 |

|

SU1596323A1 |

| Устройство для воспроизведения функций @ и @ | 1989 |

|

SU1658151A1 |

| Устройство для контроля достоверности телеметрической информации | 1982 |

|

SU1042063A1 |

| Устройство для прогнозирования длительности производственных операций | 1990 |

|

SU1781685A1 |

| Генератор стационарного случайного процесса | 1989 |

|

SU1644129A1 |

| Сглаживающее устройство | 1984 |

|

SU1265797A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| Генератор случайных чисел | 1986 |

|

SU1397907A1 |

| Устройство для анализа характеристик спектра | 1983 |

|

SU1142844A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и структурах для вычисления и непрерывного воспроизведения функции. Цель изобретения - расширение функциональных возможностей за счет расширения пределов изменения функции. Устройство содержит шину 1 пуска, триггеры 2, 30, блоки элементов И 3-8, блок 9 памяти констант, элементы ШШ 10, 26, 28, сумматоры 11, 14, 22, схему 12 сравнения, квадратор 13, блок 15 вычисления коэффициентов, блоки 16 и 23 нормирования, регистры 24, 27, 29, вычитатели 17, 18, 21, умножители 19, 20, выход 25, генератор 31 импульсов, блок 32 синхронизации, вход 33 задания коэффициентов устройства. 3 ил. (Л ;и ее со 05

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство выбора канала с экстремальным средним напряжением | 1979 |

|

SU788418A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-30—Публикация

1985-06-26—Подача